Изобретение относится к технике связи при передаче цифровых сигналов для получения уплотненного передаваемого сигнала и синхронизации с ним приемного уплотненного сигнала.

Известны способ и устройство передачи и приема цифровых сигналов, содержащее на стороне передачи вспомогательный тактовый генератор, параллельный регистр и первый делитель частоты, к входу которого подключен выход вспомогательного тактового генератора, а на стороне приема - параллельный регистр и последовательно соединенные блок подстройки фазы и первый делитель частоты [1]

Недостатком известного устройства является наличие перекрестных искажений, возникающих при асинхронной обработке сигнала.

Технический результат повышение помехоустойчивости.

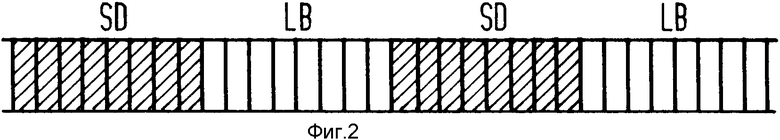

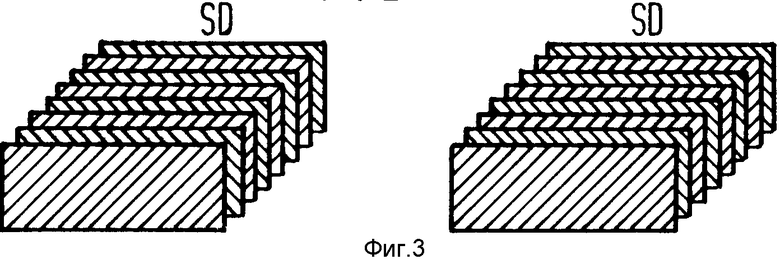

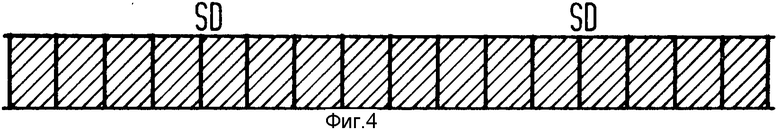

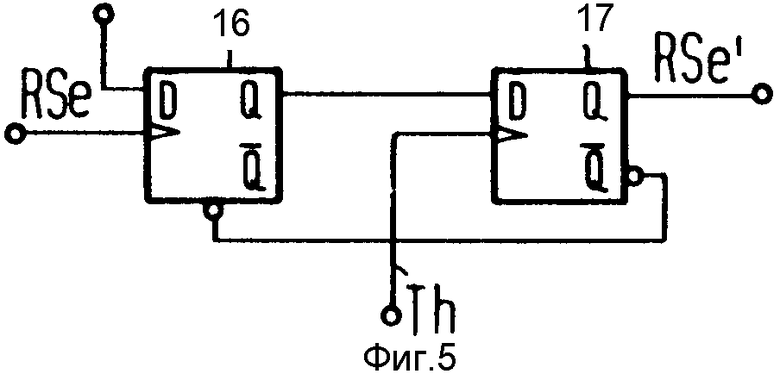

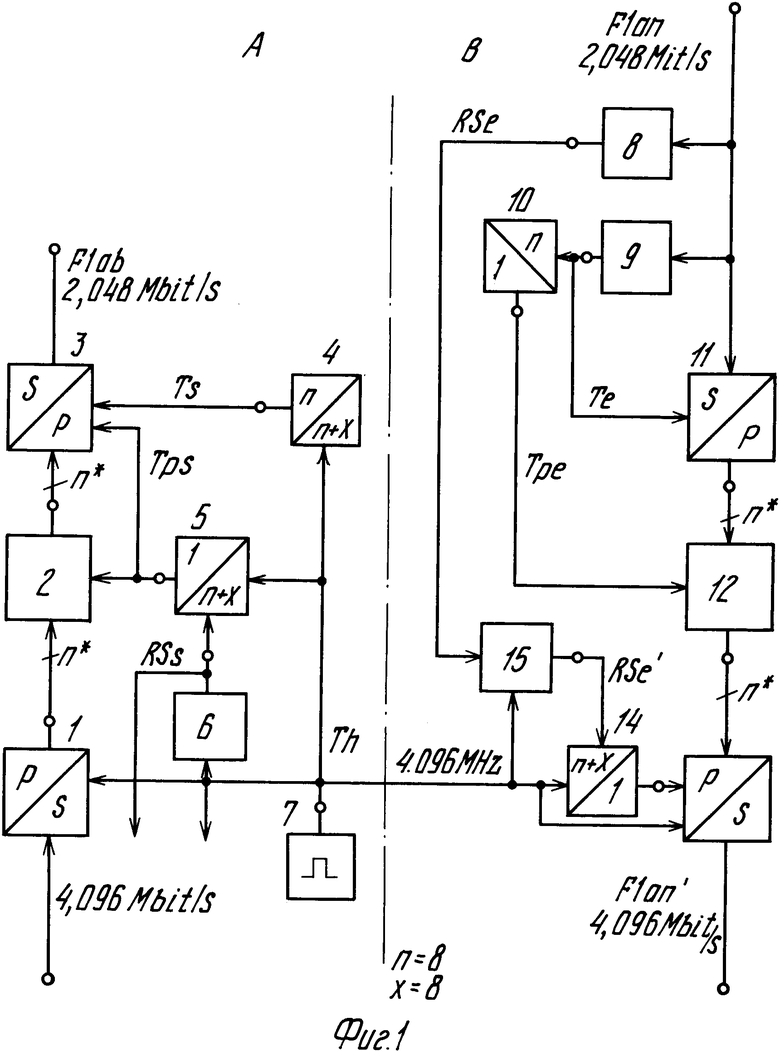

На фиг. 1 представлена структурная электрическая схема устройства передачи и приема цифрового сигнала с временным уплотнением и устройство для его осуществления, на фиг. 2 представлены входные и выходные данные во вспомогательной группе, на фиг.3 параллельные внутренние данные, на фиг.4 - выходные данные или синхронизированные входные данные, на фиг.5 представлена схема блока подстройки фазы.

Устройство передачи и приема цифрового сигнала с временным уплотнением содержит на стороне передачи А последовательно-параллельный преобразователь 1 кода, параллельный регистр 2, параллельно-последовательный преобразователь 3 кода, первый и второй делители 5, 4 частоты, блок 6 формирования сигнала цикловой синхронизации, вспомогательный тактовый генератор 7, на стороне приема В блок 8 выделения сигнала цикловой синхронизации, блок 9 восстановления тактовой частоты, второй делитель 10 частоты, последовательно-параллельный преобразователь 11 кода, параллельный регистр 12, параллельно-последовательный преобразователь 13 кода, первый делитель 14 частоты, блок 15 подстройки фазы, содержащий первый и второй дифференциальные триггеры 16, 17.

Устройство передачи и приема цифрового сигнала с временным уплотнением работает следующим образом.

На вход передающей части А подаются сериями передаваемые данные в форме 8-битного байта СД во вспомогательной группе (фиг.2), в которой за каждым заштрихованным 8-битным байтом следует 8 нулевых бит. Эти передаваемые данные получают с помощью вспомогательного тактового сигнала Th частотой 4,096 МГц от тактового вспомогательного генератора 7 и синхронного сигнала группы на выходе блока 6 формирования сигнала цикловой синхронизации. Передаваемые данные преобразуются с помощью вспомогательного генератора 7 и синхронного сигнала группы на выходе блока 6 формирования сигнала цикловой синхронизации. Передаваемые данные преобразуются с помощью вспомогательного тактового сигнала Th в параллельно-последовательном преобразователе 1 кода.

На стороне передачи А преобразованные данные только 8-битные байты с помощью вспомогательного тактового сигнала передачи Tps, поступающего с выхода первого делителя 5 частоты, поступают в параллельный регистр 2. Эти записанные данные с выхода параллельного регистра 2 с помощью вспомогательного тактового сигнала передачи Tps поступают в параллельно-последовательный преобразователь 3 кода и посредством тактового сигнала передачи Ts, поступающего с выхода второго делителя частоты 4, выдаются на выход в виде последовательного сигнала передачи с временным уплотнением сигнала Flab (фиг.4), при этом тактовый сигнал передачи Ts получают путем деления вспомогательного тактового сигнала Th на n+X/n с помощью второго делителя частоты 4, а вспомогательный тактовый сигнал передачи Tps получают путем деления вспомогательного тактового сигнала Th на n + X с помощью первого делителя частоты 5 при одновременном регулировании на синхронизирующем выходе блока 6 сигнала цикловой синхронизации RSs.

На стороне приема В принимается уплотненный сигнал Flan (фиг.4). Блок 8 выделения сигнала цикловой синхронизации выделяет из принятого последовательного сигнала приема с временным уплотнением сигнал цикловой синхронизации RSe. Блок 9 восстановления тактовой частоты из последовательного сигнала приема с временным уплотнением Flan восстанавливает тактовый сигнал приема Te, тактовая частота которого соответствует частоте тактового сигнала передачи. Принятый последовательный сигнал приема с временным уплотнением Flan с тактовым сигналом приема Te преобразуется (фиг.3) в последовательно-параллельном преобразователе 11 кода. Тактовый сигнал приема Te во втором делителе 10 частоты делится на n, в результате чего получают первый вспомогательный сигнал приема Tpe. С выхода последовательно-параллельного преобразователя 11 кода параллельные преобразованные данные (в соответствии с фиг.3) передаются с помощью первого вспомогательного тактового приема Tpe в параллельный регистр 12 и считываются в параллельно-последовательный преобразователь 13 кода. С помощью второго вспомогательного тактового сигнала приема TL и вспомогательного тактового сигнала Th приемные данные преобразуются и последовательностями в виде синхронизированного сигнала Flan посредством вспомогательных групп (фиг.2) подаются на выход на стороне приема.

В зависимости от того, что частота тактового сигнала приема Te больше или меньше номинальной, для постройки по мере надобности вместо восьми вводят меньше или больше нулевых бит между двумя 8-битными байтами.

Блок 15 подстройки фазы работает следующим образом.

Приемный сигнал цикловой синхронизации RSe устанавливает первый дифференциальный триггер 16 в асинхронное состояние. Второй дифференциальный триггер 17 принимает сигнал 0 первого дифференциального триггера 16 вместе с вспомогательным тактовым сигналом Th и выдает его на свой выход 0 в виде синхронизированного сигнала цикловой синхронизации RSe'.

Изобретение относится к технике связи при передаче цифровых сигналов для получения уплотненного сигнала и синхронизации с ним приемного уплотненного сигнала. В плезиохронно-цифровой иерархии сигналы одного уровня лишь приблизительно имеют одинаковые тактовые частоты и поэтому подлежат обязательной плезиохронной обработке. Однако необходимо синхронное взаимодействие передаваемого и приемного уплотненных сигналов. Это возможно, если в предыдущей и приемной частях устройства создаются вспомогательные группы, при которых между байтами данных (SD) пропускаются нулевые биты (LB). Эти нулевые биты устраняются с помощью последовательно-параллельного преобразования, накоплением и параллельно-последовательным преобразованием при участии вспомогательного тактового сигнала Th. Подстройка тактового сигнала приема к передаваемому осуществляется соответственно введением или исключением одного или нескольких нулевых бит между двумя байтами данных (SD) на стороне приема. Устройство содержит на стороне передачи А последовательно-параллельный преобразователь 1 кода, параллельный регистр 2, параллельно-последовательный преобразователь 3 кода, первый и второй делители 5, 4 частоты, блок 6 формирования сигнала цикловой синхронизации, вспомогательный тактовый генератор 7, на стороне приема В - блок 8 выделения сигнала цикловой синхронизации, блок 9 восстановления тактовой частоты, второй делитель 10 частоты, последовательно-параллельный преобразователь 11 кода, параллельный регистр 12, параллельно-последовательный преобразователь 13 кода, первый делитель 14 частоты, блок 15 подстройки фазы. 2 с. и 3 з.п. ф-лы, 5 ил.

| ЕР, заявка, 0275406 А1, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-12-20—Публикация

1992-01-29—Подача