Изобретение относится к способу и устройству выделения тактового сигнала.

В цифровых системах передачи данных тактовая частота битов может выделяться на стороне приемника схемами восстановления такта из принятого цифрового сигнала данных. В контурах подстройки фазы (Phase Locked Loop) для восстановления такта из цифрового потока данных могут использоваться только чистые компараторы фаз (фазочувствительные фазовые детекторы), так как не с каждым битовым тактом в распоряжении имеется фронт фазовой коррекции, а в зависимости от предусмотренного кодирования, например, в середине только каждых трех битовых тактов. Эти чистые компараторы фаз имеют, как известно, недостаток, что выполненные на них схемы заскакивают также на частотах гармоники или пытаются это (безуспешно) сделать также на других частотах. Чтобы избежать этих недостатков, до сих пор использовали управляемые напряжением генераторы с точно определенной средней частотой, которая соответствует номинальному значению тактовой частоты битов, и очень малым уходом частоты, причем для реализации таких управляемых напряжением генераторов требуются точные определяющие частоту элементы (сравни Unterrichtsblatter der Deutschen Bundespost, год выпуска 34/1981, Nr. 2, стр. 81).

В цифровых сетях передачи данных, например, в синхронных цифровых иерархических системах передачи (SDH(Synchron Digital Hierarchy) ) для получения такта передачи применяют контуры подстройки фазы (PLL (Phase Locked Loop)). Контур подстройки фазы сравнивает уровень наполнения буферного накопителя с его заданным значением и соответственно корригирует частоту передачи. Номинальная частота передачи является жестко заданной, она определена средней частотой контура подстройки фазы. Фактическая частота передачи определяется затягиванием контура подстройки фазы через его управляющее напряжение вследствие появляющегося количества данных. Сигнал, который указывает отклонение уровня наполнения буферного накопителя от заданного значения, представлен дискретным сигналом с более низкой по сравнению с частотой передачи скоростью изменения состояний. Известные сами по себе интегральные управляемые напряжением генераторы (VCO (Voltage Controlled Oscillator) при этом применении вследствие редкой коррекции не могут использоваться, так как их кратковременная стабильность является далеко не достаточной относительно требований точности для синхронных сетей данных.

Также при этом применении обычно используются схемы, в которых контур подстройки фазы регулирует управляемый напряжением, стабилизированный кварцем генератор (VCXO (Voltage Controlled Xtal (=crystal) Oscillator)). Эти управляемые напряжением, стабилизированные кварцем генераторы нуждаются для стабилизации в точных определяющих частоту элементах.

Названные определяющие частоту элементы, которые могут быть представлены узкополосными фильтрами или колебательными контурами, и могут быть реализованы, например, фильтрами на поверхностных волнах, кварцевыми или керамическими фильтрами, не могут быть просто интегрированы вместе с остальной схемой в один модуль, так что определяющие частоту элементы должны располагаться вне модуля, для чего должны предусматриваться дополнительные выводы на модуле, требуется дополнительная площадь в функциональной группе и необходимы повышенные затраты при монтаже функциональной группы.

В цифровых системах передачи, в которых одновременно должно приниматься или передаваться множество сигналов данных, которые не являются жесткими по фазе относительно друг друга, особенно мешающими становятся расходы, что для каждого сигнала данных должен быть предусмотрен особый контур подстройки фазы с соответствующими точными определяющими частоту элементами.

B основе изобретения лежит проблема указания способа и схемы выделения тактового сигнала, при которых исключаются точные внешние или настроечные определяющие частоту элементы.

Существенные признаки для решения проблемы при этом даны тем, что

- дано несколько содержащих соответственно управляемую линию задержки (VCD0, VCD1), компаратор фаз (PV0, PV1), и фильтр с регулируемой обратной связью (LF0, LF1) фазорегуляторов (PR0, PR1), управляющие напряжения которых (VC0, VC1) имеют возможность управления в диапазоне регулирования между верхней (UH) и нижней (UL) границей,

- к входам линий задержки фазорегуляторов подведен опорный тактовый сигнал (CREF0, CREF1),

- выбран фазорегулятор, выдаваемый на стороне выхода сигнал которого действует в качестве тактового сигнала,

- оказывают воздействие на длительность задержки выбранного фазорегулятора в соответствии с сигналом управления,

- при управлении к верхней или нижней границе диапазона регулирования как раз выбранного фазорегулятора является выбираемым соответственно другой фазорегулятор, управляющее напряжение которого не управляется к этой границе.

Предмет заявки является полностью применимым в одном интегральном модуле. Предмет заявки избегает трудно интегрируемых, точных определяющих частоту конструктивных элементов, за счет чего экономятся затраты на сами определяющие частоту конструктивные элементы, расходы на дополнительно предусматриваемые в противном случае выводы интегрального модуля, расходы на площадь встраивания определяющих частоту конструктивных элементов в группу и расходы на необходимый в противном случае монтаж группы с определяющими частоту конструктивными элементами. Предмет заявки принципиально превосходит обычные устройства выделения тактового сигнала, так как он использует и без того локально имеющийся тактовый сигнал передачи в качестве опорного тактового сигнала, так как тактовый сигнал передачи, как правило, является существенно более стабильным относительно поддержания частоты, чем тактовый сигнал, выдаваемый управляемым напряжением генератором (Voltage Controlled Oszillator), за счет чего тактовый сигнал CLKOUT, выдаваемый соответствующим изобретению устройством восстановления тактового сигнала, в целом является более стабильным по частоте.

В случае применения восстановления тактового сигнала из потока данных с длинными последовательностями одинаковых двоичных знаков с обычным устройством восстановления тактового сигнала отклонения частоты управляемого напряжением генератора могут интегрироваться в любые разности фаз; в соответствующем изобретению устройства выделения тактового сигнала вызванное вследствие тока утечки выполненного в виде фильтра с регулируемой обратной связью конденсатора изменение управляющего напряжения приводит в этом случае к разности фаз, которая ограничена максимально 180 градусами относительно опорного тактового сигнала.

Изобретение поясняется более подробно в необходимом для понимания объеме на примере выполнения с помощью фигур, на которых показано:

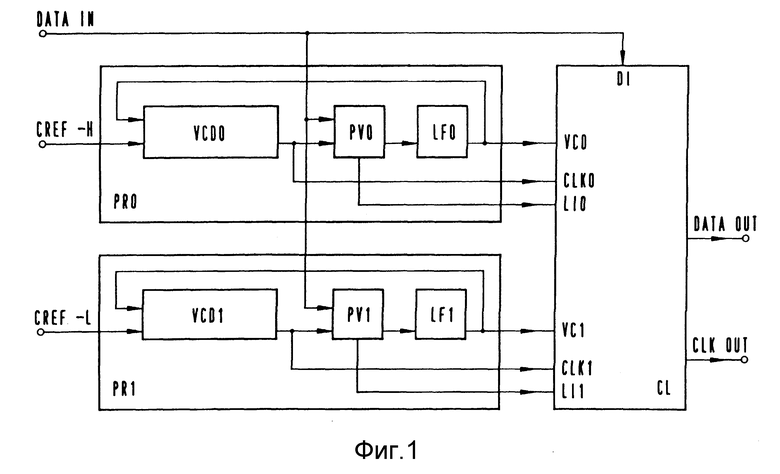

на фиг. 1 - блок-схема соответствующей изобретению схемы выделения тактового сигнала для восстановления тактового сигнала из сигнала данных,

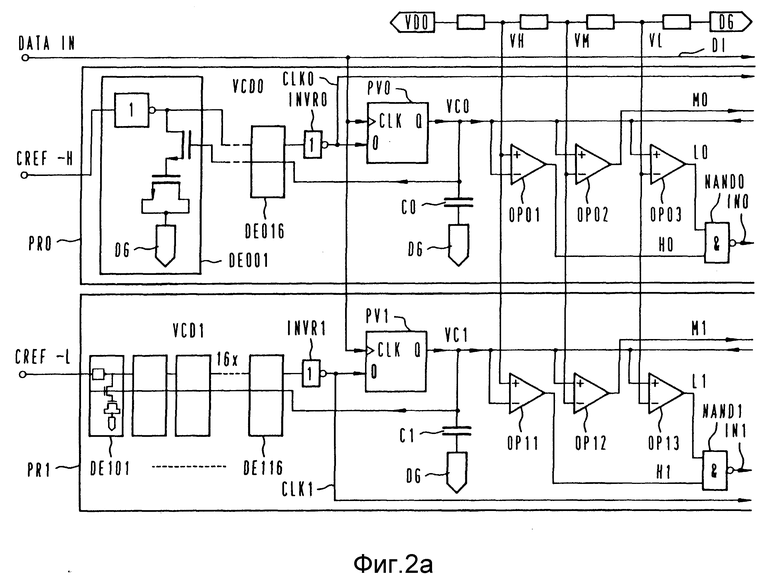

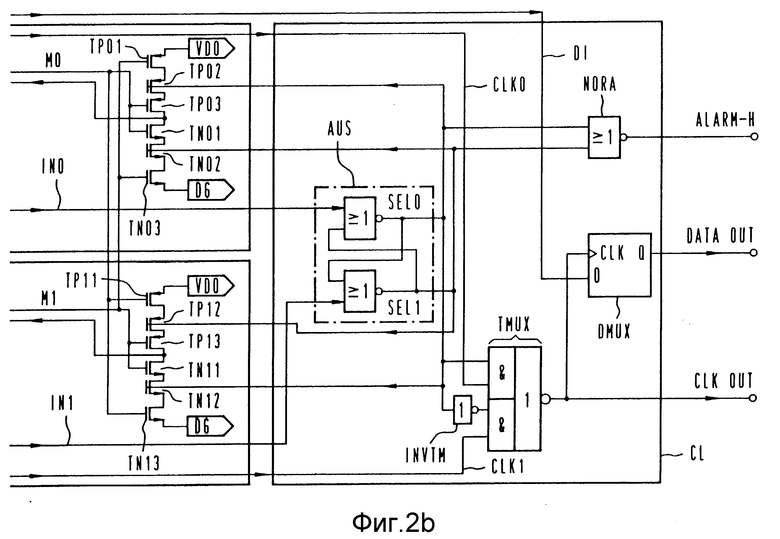

на фиг. 2a, 2b - более подробные детали схемы выделения тактового сигнала согласно фиг. 1,

на фиг. 3 и фиг. 4 - типичные характеристики сигнала в схеме вы деления тактового сигнала для отношений опорного тактового сигнала к содержащемуся в потоке данных тактовому сигналу больше 1 или соответственно меньше 1,

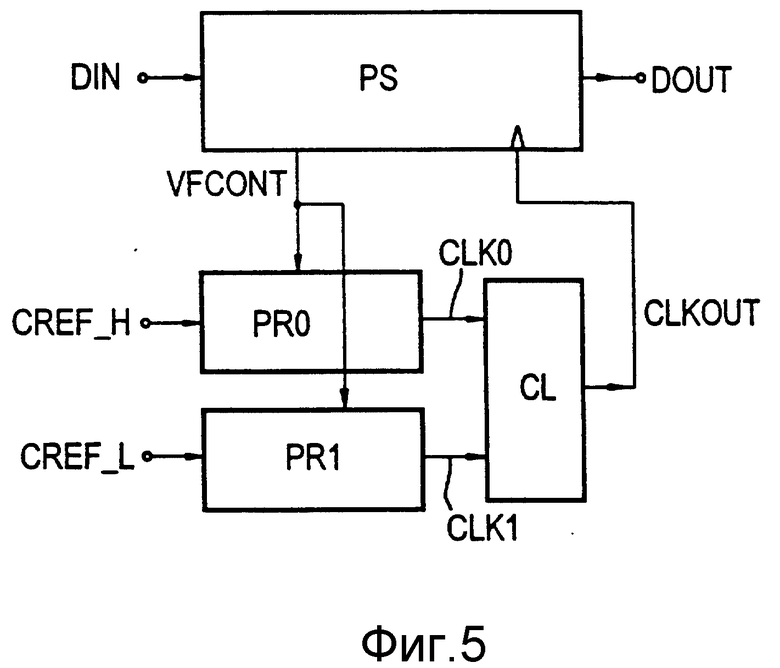

на фиг. 5 блок-схема - соответствующей изобретению схемы для выделения тактового сигнала для передачи сигнала данных,

на фиг. 6 - принципиальная схема блок-схемы из фиг. 5,

на фиг. 7a, 7b - более подробные детали схемы согласно фиг. 6.

Блок-схема на фиг. 1 содержит два фазорегулятора PR0, PR1 и блок контроля CL (для: Control-Logic). К регуляторам фазы и блоку контроля через соединительный зажим DATAIN подводят в качестве входного сигнала последовательный поток данных. В случае потока данных речь может идти о двоичных знаках с заданной номинальной скоростью следования. В качестве следующего входного сигнала к фазорегуляторам подводят опорный тактовый сигнал CREF, который приблизительно имеет свойственную потоку данных тактовую частоту. Опорный тактовый сигнал может быть представлен и без того имеющимся локальным тактовым сигналом, который требуется для передачи потока данных. В предпочтительной форме выполнения к фазорегуляторам подводят соответственно комплементарные друг к другу опорные тактовые сигналы (CREF_H, CREF_L). В фазорегуляторе соответствующий опорный тактовый сигнал подводят к управляемой напряжением линии задержки VCD0, VCD1. В линии задержки опорный тактовый сигнал задерживается в соответствии с подведенным управляющим напряжением VC0, VC1. Выданный линией задержки опорный тактовый сигнал и поток данных подводят к компаратору фаз PV0, PV1 в качестве входных сигналов. Компаратор фаз поставляет по мере совпадения подведенных к нему входных сигналов выходной сигнал, который подводят к фильтру с регулируемой обратной связью LF0, LF1. В фильтре с регулируемой обратной связью этот выходной сигнал претерпевает известную саму по себе для контуров фазовой подстройки (Phase-Loocked-Loop) обработку с интегрирующим действием. Выдаваемый фильтром с регулируемой обратной связью выходной сигнал подводят, с одной стороны, к линии задержки в качестве управляющего напряжения а, с другой стороны, к блоку контроля к его зажимам VC0, VC1. Наряду с выходным сигналом к зажиму VC0, VC1 каждый фазорегулятор блока контроля подает к зажиму CLK0, CLK1 задержанный соответствующей линией задержки опорный тактовый сигнал, а также к зажиму LI0, LI1 поставленный компаратором фаз информационный сигнал. Этот информационный сигнал образован в соответствии с отклонением фаз между подведенными к компаратору фаз сигналами. Блок контроля при оценке подведенных к нему на стороне входа сигналов выдает на зажиме DATAOUT поток данных и на зажиме CKLOUT скоррелированный с этим потоком данных тактовый сигнал. Выданный на зажиме CKLOUT тактовый сигнал может таким образом по сравнению с опорным тактовым сигналом иметь длительно несколько более высокую или несколько более низкую частоту. Для выравнивания разницы частот между опорным тактовым сигналом и тактовым сигналом CKLOUT опорный тактовый сигнал возрастающе сдвигают по фазе в линии задержки.

Каждый из фазорегуляторов может заскакивать на подведенный к зажиму DATAIN поток данных и компенсировать разницы фаз между опорным тактовым сигналом и потоком данных за счет последующего подведения времени задержки линии задержки, пока линия задержки не достигнет границы своего диапазона регулирования. Блок контроля имеет задачей постоянно выбирать фазорегулятор, который работает внутри своего диапазона регулирования, и одновременно держать в готовности как раз не выбранный фазорегулятор в такой установке своего диапазона регулирования, что он может принять на себя работу тогда, когда как раз выбранный фазорегулятор достигает границы своего диапазона регулирования. Для выбора фазорегулятора, с одной стороны, и для удержания в готовности как раз не выбранного фазорегулятора в состоянии подходящей установки своего диапазона регулирования, с другой стороны, блок контроля оценивает управляющие напряжения VC0, VC1 для линий задержки и дополнительно к этому, при необходимости, выданные компараторами фаз информационные сигналы. Блок контроля содержит тактовый мультиплексор, который подключает один из подведенных от блока контроля к зажимам CLK0, CLK1 тактовых сигналов на зажим CLKOUT. В зависимости от вида используемого компаратора фаз блок контроля имеет считывающий триггер для считывания сигнала данных с восстановленным тактовым сигналом; при использовании известного из литературного источника T. H. LEE, J.F. Buizacchelli "A 155-MHz-Clock Recovery Delay-and Phase-Locked-loop, IEEE J. of Solid-State-circuis, том 27, Nr. 12, дек. 1992, стр. 1736-1745 компаратора фаз согласно Хогге блок контроля содержит мультиплексор данных.

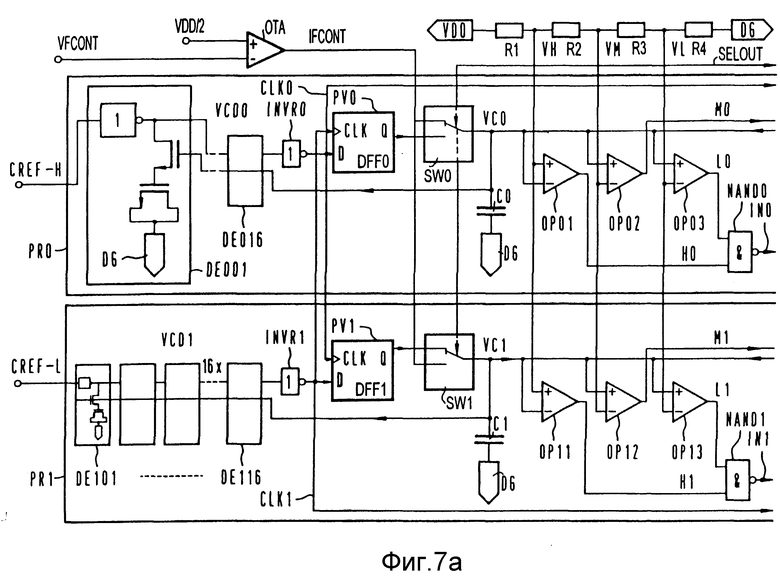

Фиг. 2 показывает простую форму выполнения реализованной по КМОП-технологии (Complementary Metal Oxid Silicium) схемы на детальном уровне. Линии задержки образованы соответственно 16 элементами задержки DE001.. DE016, или соответственно DE101. . DE116 (для: Delay Element). Каждый элемент задержки образован инвертором, который на стороне выхода через регулируемое сопротивление нагружен нагрузочной емкостью. Оба вывода нагрузочного участка регулируемого сопротивления представлены обоими главными электродами первого N-канального полевого транзистора, причем управляющий электрод полевого транзистора нагружен управляющим напряжением. Нагрузочная емкость образована емкостью между управляющим электродом и нагрузочным участком второго N-канального полевого транзистора, причем управляющий электрод второго полевого транзистора соединен с электродом истока первого полевого транзистора, а оба главных электрода второго полевого транзистора соединены с имеющим низкий потенциал зажимом DG не показанного более подробно источника рабочего напряжения VDD - DG. Выход элемента задержки представлен нагруженным управляемой нагрузочной емкостью выходом инвертора. Выход элемента задержки соединен с входом соответственно следующего элемента задержки; выход последнего элемента задержки линии задержки соединен с инвертором INVR0, INVR1 для восстановления формы импульса. Выход рассмотренного инвертора INVR0, INVR1 соединен с D-входом D-триггера DFF0, DFF1, который образует соответствующий компаратор фаз PV0, PV1. К CLK-входу D-триггера подведен поток данных. С каждым возрастающим фронтом потока данных принимается мгновенное состояние задержанного опорного тактового сигнала на выходе D-триггера. В этом примере выполнения фильтр с регулируемой обратной связью образован конденсатором C0, C1, который соединен, с одной стороны, с выходом компаратора фаз и, с другой стороны, с имеющим низкий потенциал зажимом DG источника рабочего напряжения VDD - DG. Конденсатор C0, C1 интегрирует поставляемый соответствующим компаратором фаз выходной ток. Напряжение через конденсатор C0, C1 подведено ко всем элементам задержки соответствующей линии задержки. В случаях применения с небольшим количеством изменений состояний потока данных отнесенным к промежутку времени рассмотрения вместо конденсатора C0, C1 могут применяться другие, например, известные из R. Best "Theorie und Anwendung des Phase-locked Loops" AT издательство Aarau-Stuttgart ISBN 3-85502-123-6 фильтры с регулируемой обратной связью. Линия задержки, компаратор фаз и фильтр с регулируемой обратной связью образуют контур регулирования, причем компаратор фаз регулирует так, что возрастающий фронт в потоке данных совпадает с возрастающим фронтом задержанного опорного тактового сигнала.

Для каждого фазорегулятора управляющее напряжение контролируют на то, имеет ли оно значение выше или ниже высокого напряжения UH, среднего напряжения UM или соответственно низкого напряжения UL. Образованный четырьмя резисторами R1, R2, R3 и R4 делитель напряжения соединен с обоими зажимами источника рабочего напряжения VDD - DG. Делитель напряжения ставит в распоряжение высокое напряжение UH, среднее напряжение UM и низкое напряжение UL. Каждому фазорегулятору поставлены в соответствие 3 дифференциальных усилителя OP01, OP02, OP03 или соответственно OP11, OP12, OP13. Дифференциальные усилители OP01 и OP11 нагружены на своем неинвертирующем входе (+) высоким напряжением UH, а на своем инвертирующем входе (-) соответствующим управляющим напряжением VC0, VC1. Дифференциальные усилители OP02 и OP12 нагружены на своем инвертирующем входе (-) средним напряжением UM, а на своем неинвертирующем входе (+) соответствующим управляющим напряжением VC0, VC1. Дифференциальные усилители OP03 и OP13 нагружены на своем инвертирующем входе (-) низким напряжением UL, а на своем неинвертирующем входе (+) соответствующим управляющим напряжением VC0, VC1. Выдаваемые дифференциальными усилителями OP01 и OP03 или соответственно OP11 и OP13 выходные сигналы H0, L0 или соответственно H1, L1 подведены ко входам реализующей логическую операцию И-НЕ логической схемы NAND0 или соответственно NAND1. Дифференциальные усилители OP01 и OP03 или соответственно OP11 и OP13 образуют вместе с И-НЕ-логической схемой NAND0 или соответственно NAND1 компаратор двухстороннего ограничения, причем И-НЕ - логическая схема NAND0 или соответственно NAND1 на своем выходе выдает сигнал IN0, IN1 с низким уровнем (LOW) тогда, когда управляющее напряжение является ниже, чем высокое напряжение UH и выше, чем низкое напряжение UL. Сигнал IN0, IN1 с низким уровнем (LOW) таким образом указывает, что соответствующий фазорегулятор имеет состояние внутри своего диапазона регулирования, в то время как сигнал IN0, IN1 с высоким уровнем (HIGH) указывает, что соответствующий фазорегулятор занял состояние вне своего диапазона регулирования. Напряжение UH и напряжение UL образуют таким образом границы определенного диапазона регулирования.

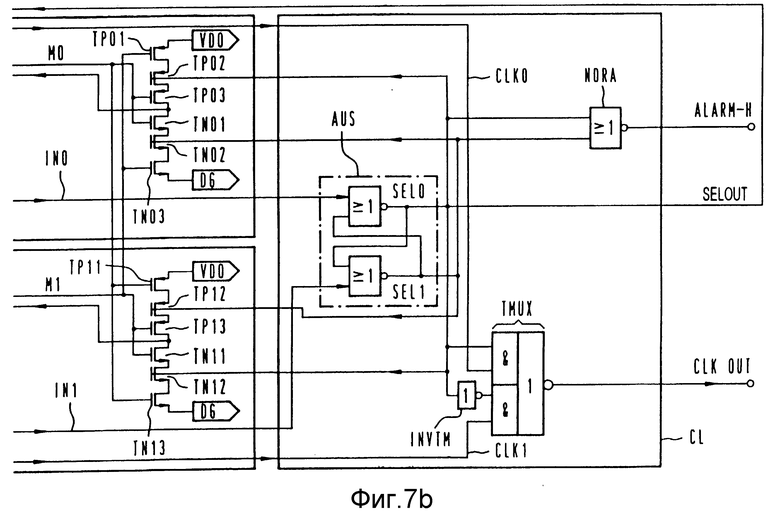

Выдаваемые компараторами двустороннего ограничения сигналы IN0 и IN1 подведены к устройству выбора AUS. Устройство выбора выбирает для случая, что покидание диапазона регулирования только что выбранного фазорегулятора показывается соответствующим сигналом IN0, IN1 с высоким уровнем (HIGH), другой фазорегулятор, который занял состояние внутри своего диапазона регулирования. В примере выполнения устройство выбора образовано двумя реализующими логическую операцию ИЛИ-НЕ (NOR) логическими схемами ИЛИ-НЕ, которые включены известным образом в RS-триггер. Таким образом устройство выбора может на своих выходах SEL0, SEL1 (для: SELECT) принимать состояния RS-триггера.

Тактовый мультиплексор TMUX управляется устройством выбора в соответствии с состоянием сигнала на выходе SELO. Тактовый мультиплексор образован двумя реализующими логическую операцию И логическими схемами И, выходы которых связаны через реализующую логическую операцию ИЛИ-НЕ (NOR) логическую схему ИЛИ-НЕ. К логическим схемам И подведены, с одной стороны, задержанные линиями задержки опорные тактовые сигналы CLK0, CLK1 и, с другой стороны, состояние сигнала на выходе SEL устройства выбора или соответственно инвертированное через инвертор INVTM инвертированное состояние этого сигнала. Тактовый мультиплексор таким образом подключает при высоком состоянии сигнала на выходе SELO устройства выбора задержанный линией задержки VCD0 опорный тактовый сигнал CLK0 в инвертированной форме на зажим CLKOUT блока контроля, в то время как при низком состоянии сигнала на выходе SEL0 устройства выбора задержанный линией задержки VCD1 опорный тактовый сигнал CLK1 в инвертированной форме подключают на зажим CLKOUT. Обусловленный инвертированием в тактовом мультиплексоре тактовый сигнал появляется на зажиме CLKOUT по сравнению с тактовым сигналом на входе только что выбранного компаратора фаз со смещением на половину периода такта. Мультиплексор данных DMUX образован D-триггером, причем к D-входу подведен поток данных DATAIN и к CLK-входу тактовый сигнал на зажиме CLKOUT. Возрастающим фронтом тактового сигнала на зажиме CLKOUT поток данных тактируют в середине последующего промежутка времени передачи бита.

Для каждого фазорегулятора дана последовательная схема трех включенных друг за другом P-канальных полевых транзисторов TP01, TP02, TP03 или соответственно TP11, TP12, TP13 и трех включенных друг за другом N-канальных полевых транзисторов TN01, TN02, TN03 или соответственно TN11, TN12, TN13. Электрод истока внешнего P-канального полевого транзистора TP01 или соответственно TP11 соединен с находящимся на высоком потенциале зажимом VDD и электрод истока внешнего N-канального полевого транзистора TN03 или соответственно TN13 соединен с находящимся на низком потенциале зажимом DG источника рабочего напряжения. Средний отвод последовательной схемы соединен с соответствующим управляющим напряжением.

Дифференциальный усилитель OP02 или соответственно OP12 выдает на своем выходе сигнал с высоким уровнем (HIGH), если соответствующее управляющее напряжение выше, чем среднее напряжение UM. Выход дифференциального усилителя OP02 или соответственно OP12 соединен с управляющими электродами полевых транзисторов TP03 и TN01 или соответственно TP13 и TN11 соответствующей последовательной схемы, а также с управляющими электродами полевых транзисторов TP11 и TN13 или соответственно TP01 и TN03 соответствующей последовательной схемы, принадлежащей другому фазорегулятору. Выход SEL0 устройства выбора соединен с управляющими электродами полевых транзисторов TP02 и TN12. Выход SEL1 устройства выбора соединен с управляющими электродами полевых транзисторов TN02 и TP12. Если фазорегулятор PR0 как раз выбран сигналом с высоким уровнем на выходе SEL0 устройства выбора, то полевые транзисторы TP02 и TN02 заперты, а полевые транзисторы TP12 и TN12 включены проводяще. Последовательная схема как раз выбранного фазорегулятора таким образом заперта, она не имеет тем самым никакого влияния на соответствующее управляющее напряжение. Последовательная схема как раз не выбранного фазорегулятора включается проводяще таким образом, что оказывается влияние на высоту управляющего напряжения этого фазорегулятора в направлении другой относительно среднего напряжения UM стороны диапазона регулирования, чем сторона диапазона регулирования, на которую падает мгновенная высота управляющего напряжения как раз выбранного фазорегулятора. Это воздействие продолжается так долго, пока управляющее напряжение превысит среднее напряжение и путем изменения состояния на выходе дифференциального усилителя OP02 или соответственно OP12 как раз не выбранного фазорегулятора соответствующая последовательная схема запирается для последующего воздействия на управляющее напряжение. Если управляющее напряжение как раз не выбранного фазорегулятора имеет высоту, которая относительно среднего напряжения UM падает на другую сторону диапазона регулирования, чем сторона диапазона регулирования, в которую падает мгновенная высота управляющего напряжения как раз выбранного фазорегулятора, то последовательная схема как раз не выбранного фазорегулятора остается запертой, за счет чего на соответствующее управляющее напряжение влияния не оказывается.

Для случая, когда управляющие напряжения всех фазорегуляторов приняли состояние вне их области регулирования, все подведенные к устройству выбора сигналы IN0, IN1 имеют высокий уровень (HIGH), за счет чего устройство выбора на своих выходах SEL0, SEL1 принимает низкий уровень (LOW). Это оценивается реализующей логическую операцию ИЛИ-НЕ (NOR) логической схемой ИЛИ-НЕ и индицируется на зажиме ALARM сигналом с высоким уровнем (HIGT).

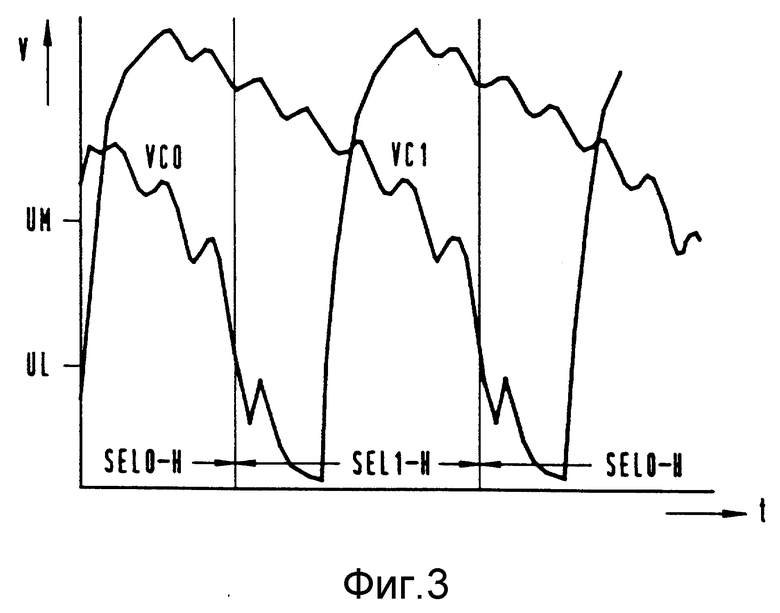

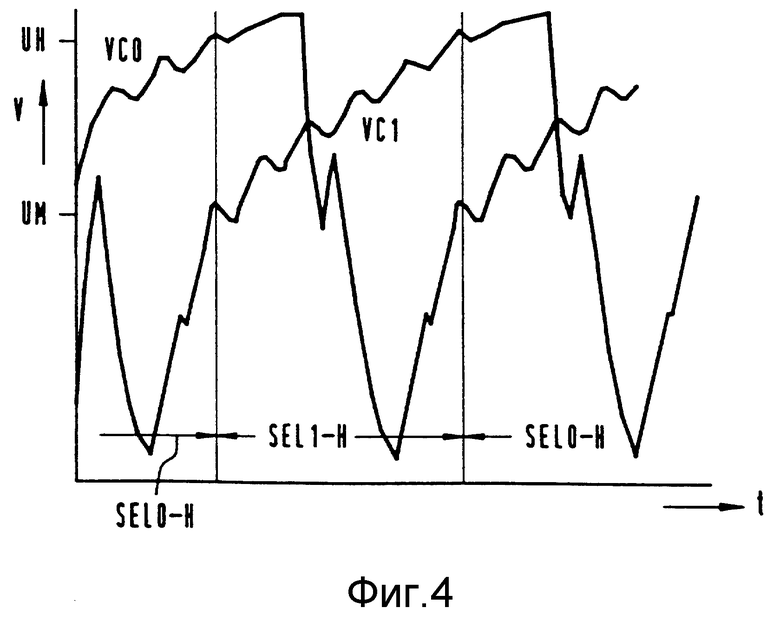

На фиг. 3 и 4 представлены полученные в ходе моделирования схемы характеристики управляющих напряжений VC0, VC1 и сигналов SEL0, SEL1, приложенных к выходам устройства выбора. Отклонение между скоростью передачи битов потока данных и тактовой скоростью опорного тактового сигнала в обоих случаях составляет 1 промилле.

На фиг. 3 скорость передачи битов потока данных является выше, чем тактовая скорость опорного тактового сигнала, за счет чего как раз выбранный фазорегулятор поступательно уменьшает задержку опорного тактового сигнала, в то время как раз не выбранный фазорегулятор удерживается в готовности в мгновенном состоянии с длинной задержкой.

На фиг. 4 скорость передачи битов потока данных является ниже, чем тактовая скорость опорного тактового сигнала, за счет чего как раз выбранный фазорегулятор поступательно увеличивает задержку опорного тактового сигнала, в то время как не выбранный как раз фазорегулятор удерживается в готовности в мгновенном состоянии с короткой задержкой.

В основе представлений на фиг. 3 и фиг. 4 лежит модулированный по фазе поток данных с частотой модуляции 2 Мгц. Фазовая модуляция обуславливает в ходе управляющих напряжений помехи, которые легко различить по волнистому ходу управляющих напряжений.

Фиг. 5 показывает схему для передачи сигнала данных в цифровой системе передачи. Сигнал данных подведен ко входу DIN буферного накопителя PS. К двум фазорегуляторам PR0, PR1 на стороне входа подведен соответственно один из комплементарных друг к другу опорных тактовых сигналов CREF_H, CREF_L. Блок контроля CL выбирает фазорегулятор, выданный на выходе тактовый сигнал которого CLK0, CLK1 служит в качестве тактового сигнала CLKOUT для передачи сигнала данных на линию на выходе DOUT буферного накопителя. Частота выдаваемого выбранным фазорегулятором тактового сигнала подвергается воздействию в соответствии с выдаваемым буферным накопителем сигналом уровня наполнения.

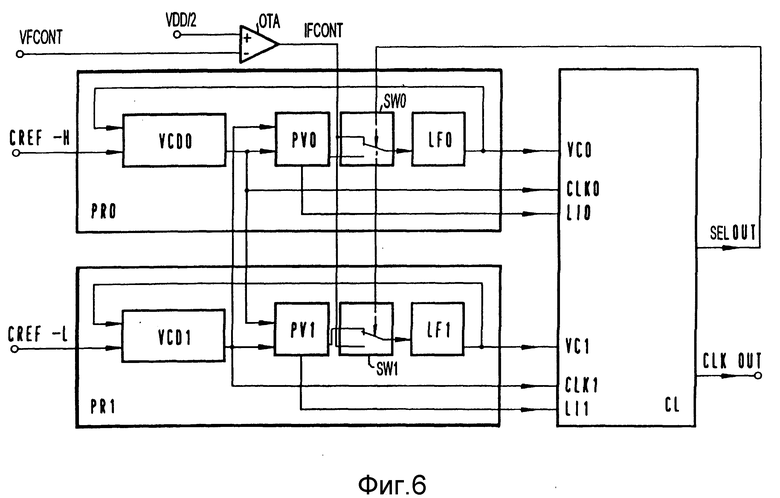

Блок-схема на фиг. 6 содержит два фазорегулятора PR0, PR1 блок контроля CL (для: Control-Logic) К фазорегуляторам подведен в качестве входного сигнала опорный тактовый сигнал CREF с данной, в высокой мере стабильной частотой. Опорный тактовый сигнал может быть представлен также и без того локально имеющимся тактовым сигналом. К фазорегуляторам подводят комплементарные друг к другу опорные тактовые сигналы CREF_H, CREF_L. В фазорегуляторе соответствующий опорный тактовый сигнал подводят к управляемой напряжением линии задержки VCD0, VCD1. В линии задержки опорный тактовый сигнал задерживается в соответствии с подведенным управляющим напряжением VC0, VC1. Выданный линией задержки тактовый сигнал и выданный линией задержки другого фазорегулятора тактовый сигнал подводят к компаратору фаз PV0, PV1 в качестве входных сигналов. Компаратор фаз поставляет в зависимости от совпадения подведенных к нему входных сигналов ток в качестве выходного сигнала. Поставляемый компаратором фаз ток подведен к первому входу управляемого переключателя SW0, SW1. Ко второму входу всех управляемых переключателей подведен поставляемый преобразователем напряжения в ток OTA (для: Operatinal Transconductance Amplifier) ток IFCONT. Не инвертирующий вход преобразователя напряжения в ток соединен со средним потенциалом UDD/2 не показанного более подробно источника рабочего напряжения, который на своих обоих зажимах ставит в распоряжение потенциалы UDD, DG. К инвертирующему входу преобразователя напряжения в ток подведен сигнал напряжения VFCONT. Преобразователь напряжения в ток преобразует сигнал напряжения VFCONT в соответственно высокий положительный или отрицательный ток. Сигнал напряжения VFCONT может быть дан дискретным сигналом, который указывает отклонение уровня наполнения буферного накопителя от заданного значения. Частота изменения состояния сигнала напряжения VFCONT может быть меньше по сравнению с частотой опорного тактового сигнала. Поставляемый на стороне выхода управляемым переключателем сигнал подводят к фильтру с регулируемой обратной связью LF0, LF1. В фильтре с регулируемой обратной связью подведенный сигнал претерпевает известную по себе для контуров подстройки фаз (Phase-Locked-Loop) обработку с интегрирующим действием. В настоящем случае в фильтре с регулируемой обратной связью поставленный от компаратора фаз или к преобразователю напряжения в ток ток постоянной высоты преобразуется в линейно возрастающий сигнал напряжения. Выданный фильтром с регулируемой обратной связью сигнал напряжения подводят в качестве управляющего напряжения VC0, VC1, с одной стороны, к линии задержки и, с другой стороны, к блоку контроля через одинаково обозначенные выводы. Блок контроля выдает при оценке подведенных к нему на стороне входа сигналов на зажиме CLKOUT тактовый сигнал, который может иметь более низкую, одинаковую или более высокую тактовую частоту, чем опорный тактовый сигнал CREF. Выданный на зажиме CLKOUT тактовый сигнал может таким образом иметь по сравнению с опорным тактовым сигналом длительно несколько более высокую или несколько более низкую частоту. Для выравнивания разницы частот между опорным тактовым сигналом и тактовым сигналом CLKOUT опорный тактовый сигнал в линии задержки сдвигают с возрастанием по фазе. Выданный на зажиме CLKOUT тактовый сигнал подведен к буферному накопителю, содержание которого считывают с частотой тактового сигнала.

Блоком контроля постоянно выбирается фазорегулятор, тактовый сигнал которого проключают на зажим CLKOUT. На фиг. 6 и фиг. 7 в качестве выбранного фазорегулятора представлен фазорегулятор PR1. В выбранном фазорегуляторе выходной сигнал преобразователя напряжения в ток через управляемый переключатель SW подведен к соответствующему фильтру с регулируемой обратной связью. Частота выдаваемого выбранным фазорегулятором тактового сигнала таким образом управляется в соответствии с подведенным к преобразователю напряжения в ток сигналом напряжения VFCONT. На фиг. 6 и фиг. 7 представлен в качестве не выбранного в настоящий момент фазорегулятора фазорегулятор PR2. В случае не выбранного фазорегулятора контур подстройки фазы замкнут через управляемый переключатель, причем контур подстройки фазы заскакивает на частоту выбранного в настоящий момент фазорегулятора. Заскакивание не выбранного фазорегулятора на частоту выбранного фазорегулятора позволяет переключение без фазового скачка. Так как оба фазорегулятора на стороне входа нагружены комплементарными относительно друг друга опорными тактовыми сигналами, выбранный фазорегулятор и не выбранный фазорегулятор имеют в общем отклоняющиеся друг от друга управляющие напряжения VC0, VC1.

В остальном для блока контроля на фиг. 6 справедливо сказанное для блока контроля на фиг. 1 соответственно со следующим дополнением. Блок контроля выдает сигнал SELOUT, который изменяет свое состояние с состоянием выбора блока контроля и обуславливает переключение управляемого переключателя.

Для фиг. 7a, b справедливо сказанное для фиг. 2a, 2b со следующими отклонениями. Ко входу CLK D-триггера (DFF0, DFF1) подведен выдаваемый линией задержки соответственно другого фазорегулятора тактовый сигнал. С каждым возрастающим фронтом выдаваемого соответственно другим фазорегулятором тактового сигнала мгновенное состояние соответствующего тактового сигнала принимается на выходе D-триггера. Выход фазорегулятора подведен к входу управляемого переключателя, который может быть реализован известным по себе образом на транзисторных ключах. Сигнал на выходе компаратора фаз выбранного в настоящий момент фазорегулятора является не используемым. Выходной ток компаратора фаз не выбранного в настоящий момент фазорегулятора подведен через соответствующий управляемый переключатель к образованному конденсатором C0, C1 фильтру с регулируемой обратной связью там интегрируется. Напряжение через конденсатор C0, C1 подведено ко всем элементам задержки соответствующих линий задержки. В случае не выбранного фазорегулятора линия задержки, компаратор фаз и фильтр с регулируемой обратной связью через управляемый переключатель образуют замкнутый контур регулирования, причем компаратор фаз регулирует таким образом, что на его входе возрастающие фронты тактового сигнала CLK0 и тактового сигнала CLK0 являются синхронными.

Выданный на выходе SEL0 устройства выбора сигнал подведен в

качестве сигнала переключения SELOUT к управляемым переключателям SW0, SW1.

Блок контроля вынуждает, чтобы управляющее напряжение не выбранного в настоящий момент фазорегулятора удерживалось в диаметральном относительно среднего напряжения рабочем диапазоне относительно рабочего диапазона как раз выбранного фазорегулятора так, что не выбранный в настоящий момент фазорегулятор может заскакивать только в этом состоянии.

Влияние помех на зажимах источника рабочего напряжения является тем меньше, чем короче время задержки в линии задержки. В предпочтительной форме выполнения фазорегуляторы разделены на две группы, причем к группам подведены соответственно комплементарные друг к другу опорные тактовые сигналы. Эти меры, наряду с уменьшением влияния вызванных помехами на зажимах источника рабочего напряжения помех, влекут за собой возможность применения более коротких и таким образом связанных с меньшими затратами линий задержки. Линия задержки тогда выполнена таким образом, что она может и должна выравнивать только половину периода тактового сигнала.

Изобретение относится к способу и устройству выделения тактового сигнала для восстановления тактового сигнала из потока данных. К двум группам фазорегуляторов подводят локально имеющийся опорный тактовый сигнал, предпочтительно один из комплементарных друг к другу опорных тактовых сигналов. Соответственно один фазорегулятор, который принял состояние внутри своего рабочего диапазона, выбирают для подготовки восстановленного тактового сигнала, в то время как невыбранный фазорегулятор поддерживают в готовности в диаметральном состоянии внутри своего рабочего диапазона относительно выбранного фазорегулятора. По достижении границы рабочего диапазона как раз выбранного фазорегулятора производят переключение на поддерживаемый до сих пор в готовности фазорегулятор. При этом достигается технический результат, заключающийся в исключении точных внешних или настроенных элементов, определяющих частоту, и в повышении стабильности по частоте. 4 с. и 5 з.п. ф-лы, 7 ил.

| УЗЕЛ НЕПОДВИЖНОГО КРЕПЛЕНИЯ АГРЕГАТА | 1972 |

|

SU418641A1 |

| US 4805195 A, 14.02.89 | |||

| РЕГУЛЯТОР РОСТА И СПОСОБ ПОВЫШЕНИЯ БИОХИМИЧЕСКОЙ АКТИВНОСТИ МИКРООРГАНИЗМОВ И РАСТЕНИЙ | 2000 |

|

RU2171577C1 |

| Способ приготовления катализатора для полимеризации олефинов | 1974 |

|

SU520127A1 |

| Устройство тактовой синхронизации | 1991 |

|

SU1807578A1 |

Авторы

Даты

1999-03-20—Публикация

1995-08-08—Подача