Изобретение относится к импульсной технике и может быть использовано в различных устройствах вычислительной техники и систем управления, работающих в условиях воздействия помех.

Известно устройство для счета импульсов (авт. св. СССР N 797078 от 23.02.79, МКИ: H 03 K 23/00, "Устройство для счета импульсов", С.И.Ткаченко, Р. В. Коровин и А.С.Черепнев, опубл. 15.01.81, БИ N 2), содержащее счетчик, выходы которого соединены с входами блока фиксации изменения кода, с входами первой группы вентильных элементов и с входами разрядом первого слагаемого комбинационного сумматора, входы разрядов второго слагаемого которого соединены с входами второй группы вентильных элементов и с выходами регистра памяти. Входы регистра памяти соединены с выходами первой группы вентильных элементов. Установочные входы счетчика соединены с выходами второй группы вентильных элементов. Выход комбинационного сумматора через нуль-орган соединен с входом элемента НЕ и с первым входом первого элемента совпадения, выход которого соединен с управляющим входом первой группы вентильных элементов и с первым входом элемента ИЛИ. Второй вход элемента ИЛИ соединен с управляющим входом второй группы вентильных элементов и с выходом второго элемента совпадения, первый вход которого соединен с выходом элемента НЕ, второй вход - с вторым входом первого элемента совпадения и с выходом первого элемента задержки. Третьи входы первого и второго элементов совпадения соединены с выходом триггера, вход установки в единицу которого соединен с входом первого элемента задержки и с выходом блока фиксации изменения кода. Вход установки в ноль триггера соединен с выходом второго элемента задержки, вход которого соединен с выходом элемента ИЛИ. Входная шина соединена с тактовым входом счетчика.

Недостатками данного устройства являются:

1) сложность схемы, обусловленная необходимостью использования большого количества функциональных блоков и элементов;

2) низкая помехоустойчивость, определяемая помехоустойчивостью регистра памяти.

Известно устройство для счета импульсов в виде накапливающего сумматора (см. книгу: Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств, М., Радио и связь, 1990 г., с. 310, рис. 8.20), которое является прототипом и в режиме счета импульсов содержит n-разрядный комбинационный сумматор, n-разрядный регистр суммы, n-разрядный регистр второго слагаемого (регистр памяти), инвертор и входную шину, которая подключена к тактовому входу регистра памяти, входу младшего разряда первого слагаемого комбинационного сумматора и через инвертор к тактовому входу регистра суммы. Выходы разрядов комбинационного сумматора подключены к соответствующим информационным входам регистра суммы, выходы разрядов которого соединены с соответствующими информационными входами регистра памяти, выходы разрядов которого соединены с входами соответствующих разрядов второго слагаемого комбинационного сумматора, входы старших разрядов, начиная со второго, первого слагаемого которого соединены с общей шиной устройства.

Недостатком этого устройства является низкая помехоустойчивость, определяемая помехоустойчивостью регистра памяти и регистра слагаемого.

Достигаемым техническим результатом является повышение помехоустойчивости устройства для счета импульсов.

Указанный технический результат достигается тем, что в устройство для счета импульсов, содержащее n-разрядный комбинационный сумматор, вход младшего разряда первого слагаемого которого соединен с входной шиной, входы остальных разрядов первого слагаемого соединены с общей шиной, входы разрядов второго слагаемого - с выходами соответствующих разрядов n-разрядного регистра памяти, и инвертор, вход которого соединен с входной шиной, введены n RC-элементов, входы которых соединены с выходами соответствующих разрядов комбинационного сумматора, выхода - с информационными входами соответствующих разрядов регистра памяти, тактовый вход которого соединен с выходом инвертора, а каждый из разрядов выполнен в виде тактируемого уровнем D-триггера.

Указанная совокупность признаков позволяет повысить помехоустойчивость устройства за счет порогового контроля длительности счетных импульсов (с помощью RC-элементов) и поддержания текущих состояний устройства в интервалах между счетными импульсами по замкнутым цепям: выходы комбинационного сумматора - RC-элементы - информационные входы и выходы регистра памяти - входы второго слагаемого комбинационного сумматора.

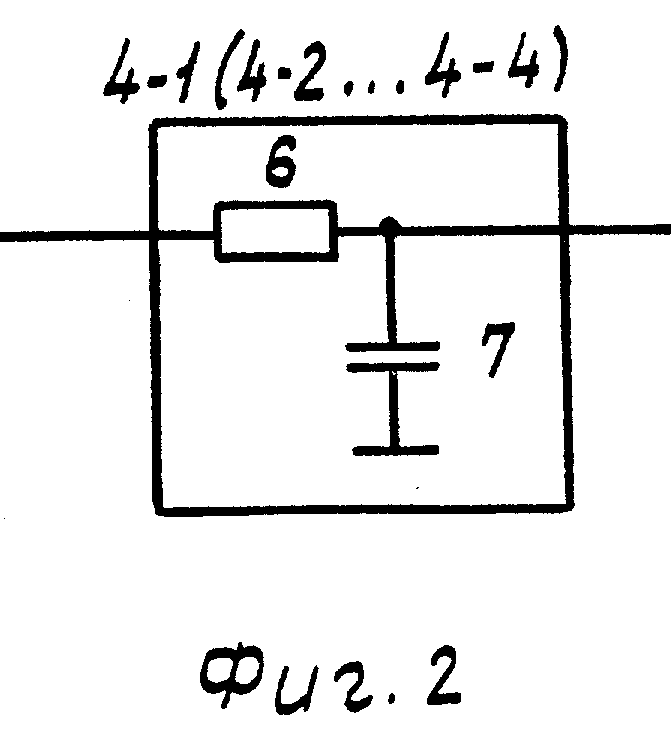

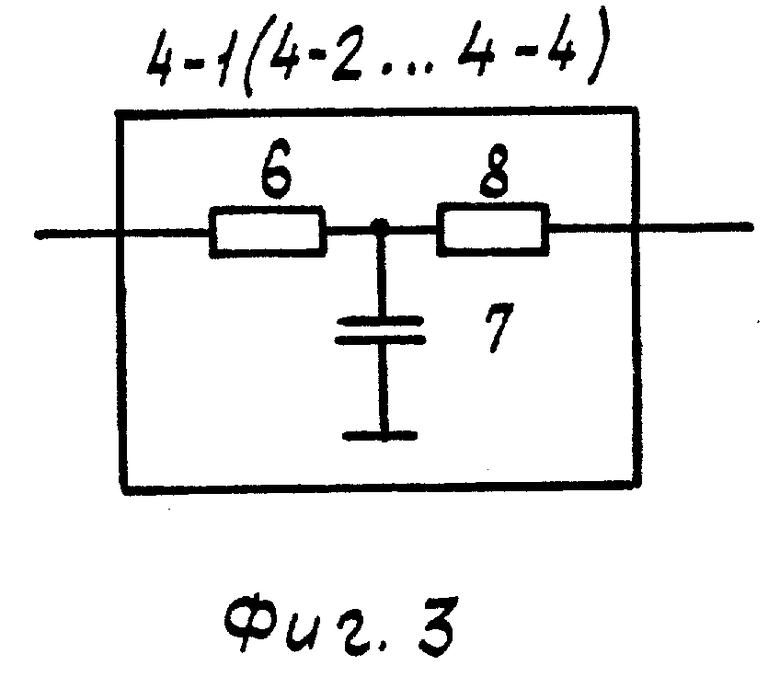

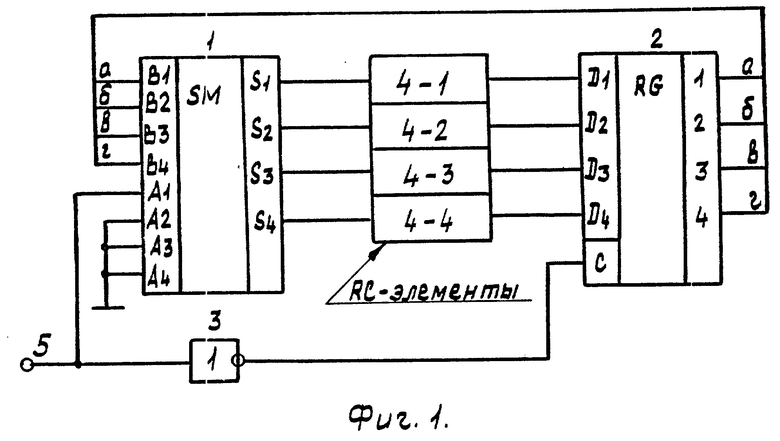

На фиг. 1 приведена схема устройства для счета импульсов в четырехразрядном (n = 4) исполнении; на фиг. 2 и 3 - схемы возможных вариантов выполнения RC-элементов.

Устройство для счета импульсов содержит (фиг. 1) четырехразрядный комбинационный сумматор 1, четырехразрядный регистр памяти 2, инвертор 3, RC-элементы 4-1...4-4. Вход младшего разряда первого слагаемого комбинационного сумматора 1 соединен с входной шиной 5, входы остальных разрядов первого слагаемого соединены с общей шиной, а входы разрядов второго слагаемого - с выходами соответствующих разрядов регистра памяти 2. Выходы разрядов комбинационного сумматора 1 через соответствующие RC-элементы 4-1...4-4 соединены с информационными входами соответствующих разрядов регистра памяти 2. Вход инвертора 3 соединен с входной шиной 5, а выход - с тактовым входом регистра памяти 2.

Регистр памяти 2 выполнен на тактируемых уровнем однотактных D-триггерах с объединением их тактовых входов. Информация в эти D-триггеры записывается высоким уровнем сигнала на их тактовых входах.

RC-элементы 4-1...4-4 выполнены по одинаковой схеме, приведенной на фиг. 2, на резисторе 6 и конденсаторе 7. Могут быть также выполнены, при необходимости, по схеме фиг. 3 на двух резисторах 6, 8 и конденсаторе 7, обеспечивающей защиту информационных входов регистра памяти 2 от больших входных токов (например при выключении питания) при реализации устройства на базе интегральных микросхем, изготовленных по КМОП-технологии.

Информация о текущих состояниях устройства может сниматься, при необходимости, с выходов регистра памяти, где сигналы имеют крутые фронты и срезы.

Устройство для счета импульсов работает следующим образом.

В исходном состоянии на входной шине 5 поддерживается уровень логического нуля, регистр памяти 2 находится в нулевом состоянии, поэтому на выходах всех его разрядов - уровни логического нуля. На входах всех разрядов первого и второго слагаемых сумматора 1 (A1...A4 и B1...B4 соответственно) - уровни логического нуля, поэтому на выходах всех его разрядов поддерживается уровень логического нуля. Конденсаторы 7 RC-элементов 4-1...4-4 разряжены, поэтому на информационных входах разрядов регистра памяти 2 присутствуют уровни логического нуля.

В указанное исходное (нулевое) состояние устройство устанавливается автоматически при включении питания, и происходит это следующим образом.

В выключенном состоянии устройства конденсаторы 7 RC-элементов 4-1...4-4 разряжены, и при включении питания низкий уровень сигналов (логические нули) с этих конденсаторов записывается в D-триггеры разрядов регистра памяти 2, поскольку в регистр информация записывается уровнем логической единицы на его тактовом входе (при уровне логического нуля на входной шине 5). Уровни логического нуля с выходов разрядов регистра памяти 2 поступают на входы соответствующих разрядов второго слагаемого сумматора 1, на входах всех разрядов первого слагаемого которого присутствуют также уровни логического нуля. Поэтому на выходах всех разрядов сумматора 1 будут уровни логического нуля, чем поддерживается разряженное состояние конденсаторов 7 RC-элементов 4-1... 4-4 и, следовательно, уровни логического нуля на информационных входах всех разрядов регистра памяти 2. Тем самым поддерживается нулевое состояние D-триггеров всех разрядов регистра памяти 2, поскольку на тактовом входе последнего поддерживается уровень логической единицы с выхода инвертора 3 - сигнал записи информации. Таким образом, после включения питания устройство само устанавливается в нулевое состояние и "держит" себя в этом состоянии по замкнутой цепи: выходы RC-элементов 4-1...4-4 - информационные входы и выходы регистра памяти 2- входы второго слагаемого 4 выходы сумматора 1 - входы RC-элементов 4-1...4-4.

В указанное исходное нулевое состояние устройство, при необходимости, может быть установлено, притом из любого состояния, путем подачи импульсного сигнала на вход сброса регистра памяти 2, который на схеме фиг. 1 не показан.

Рассмотрим работу устройства в режиме счета импульсов, полагая, что перед началом работы устройство находится в нулевом состоянии.

При поступлении по входной шине 5 первого счетного импульса (импульса с уровнем логической единицы) на входах первого слагаемого (A1...A4) сумматора 1 в течение этого импульса оказывается приложенным двоичный позиционный код (код) 0001 - код десятичного числа 1 (младший разряд кода здесь и далее в тексте - справа). Поскольку на всех входах второго слагаемого (B1...B4) сумматора 1 в это время поддерживается уровень логического нуля (с выходов регистра памяти 2), то есть код 0000, то в течение первого счетного импульса на его выходах будет поддерживаться код числа 1 - 0001, и будет заряжаться конденсатор 7 RC-элемента 4-1 (через соответствующий резистор 6). Конденсаторы 7 RC-элементов 4-2...4-4 остаются при этом разряженными.

Постоянные интегрирующих RC-элементов 4-1...4-4 выбраны так, чтобы конденсаторы 7 последних успели зарядиться до уровня логической единицы (или разрядиться до уровня логического нуля) до окончания счетного импульса.

Следовательно, до окончания первого счетного импульса с конденсаторов 7 RC-элементов 4-1. ..4-4 на информационные входы регистра памяти 2 уже будет подан код числа 1 - 0001. После окончания первого счетного импульса этот код записывается в D-триггеры разрядов регистра памяти 2 и с выходов последнего поступает на соответствующие входы второго слагаемого сумматора 1. Так как после окончания первого счетного импульса на входах первого слагаемого сумматора 1 вновь восстанавливается код числа 0 - 0000, то на выходах сумматора 1 будет код числа 1 - 0001, которым будут поддерживаться (до поступления второго счетного импульса) заряженное состояние конденсатора 7 RC-элемента 4-1 и разряженное состояние конденсаторов 7 RC-элементов 4-2...4-4, то есть будет поддерживаться код 0001 нового состояния устройства, "запомненный" конденсаторами 7 RC-элементов 4-1...4-4 в течение первого счетного импульса. Таким образом, после окончания первого счетного импульса новое состояние 0001 устройства само себя поддерживает по замкнутой цепи: выходы RC-элементов 4-1...4-4 - информационные входы и выходы регистра памяти 2 - входы второго слагаемого и выходы сумматора 1 - входы RC-элементов 4-1...4-4.

При поступлении второго счетного импульса на входах первого слагаемого сумматора 1 в течение этого импульса опять оказывается приложенным код числа 1 - 0001, то есть код счетного импульса. Поскольку на входах второго слагаемого сумматора 1 в это время поддерживается код предыдущего состояния, то есть код числа 1 - 0001, то на выходах сумматора 1 в течение второго счетного импульса будет поддерживаться код числа 2 - 0010. В результате разряжается конденсатор 7 RC-элемента 4-1, заряжается конденсатор 7 RC-элемента 4-1, а конденсаторы 7 RC-элементов 4-3, 4-4 остаются разряженными, то есть в течение второго счетного импульса конденсаторами 7 RC-элементов 4-1...4-4 запоминается код нового состояния устройства - 0010.

После окончания второго счетного импульса код 0010 нового состояния устройства записывается в регистр памяти 2, с выходов которого поступает на входы второго слагаемого сумматора 1. Поскольку после окончания второго счетного импульса, как и после окончания первого счетного импульса, на входах первого слагаемого сумматора 1 опять будет поддерживаться код числа 0 - 0000, то на его выходах будет иметь место код числа 2 - 0010, которым до поступления третьего счетного импульса будет поддерживаться заряженное состояние конденсатора 7 RC-элемента 4-2 и разряженное состояние конденсаторов 7 RC-элементов 4-1, 4-3, 4-4. Таким образом, после окончания второго счетного импульса новое состояние 0010 устройства, "запомненное" в течение этого импульса конденсаторами 7 RC-элементов 4-1...4-4, само себя поддерживает по указанной выше замкнутой цепи: выходы RC-элементов 4-1...4-4 - информационные входы и выходы регистра памяти 2 - входы второго слагаемого и выходы сумматора 1 - входы RC-элементов 4-1...4-4.

Аналогично работает устройство при поступлении последующих счетных импульсов. После пятнадцатого счетного импульса устройство принимает состояние 1111, а после шестнадцатого - состояние 0000, то есть исходное состояние.

Если какой-либо из поступающих по входной шине 5 импульсов имеет длительность короче требуемой (является помехой), то на короткое время, равное длительности этого импульса (помехи), на выходах сумматора 1 появляется код следующего состояния устройства, поскольку сумматор 1 всегда выполняет свою функцию суммирования (при условии, что длительность сигнала на входной шине 5 превышает задержку сигнала в сумматоре 1). Однако этот кратковременный код не приведет к заряду или разряду конденсаторов 7 RC-элементов 4-1...4-4 до соответствующих логических уровней, и после окончания этого импульса (помехи) устройство не переключится в новое состояние, а сохранит старое.

Уровень помехоустойчивости устройства может регулироваться в широких пределах путем изменения номиналов резисторов 6 или конденсаторов 7 RC-элементов 4-1...4-4. При этом увеличение длительности фронта и среза сигналов на информационных входах регистра памяти 2 (длительности заряда и разряда конденсаторов 11 RC-элементов 4-1...4-4) при повышении уровня помехоустойчивости устройства не приводит к нарушению работоспособности устройства или электрических режимов его элементов, поскольку переключения D-триггеров регистра памяти 2 происходят после окончания счетных импульсов, то есть после завершения переходных процессов заряда и разряда конденсаторов 7 RC-элементов 4-1...4-4.

Повышение помехоустойчивости устройства повышает его функциональную надежность и расширяет область его применения.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в Институте построен и испытан в диапазоне температур от минус 50oC до +50oC лабораторный макет, выполненный на базе интегральных микросхем серии 564, резисторов типа С2-33Н и конденсаторов типа К10-17. Проведенные испытания показали осуществимость заявляемого устройства для счета импульсов и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ПОМЕХОУСТОЙЧИВЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | 2000 |

|

RU2168856C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| ПОМЕХОУСТОЙЧИВЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | 2000 |

|

RU2168855C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Достигаемый технический результат - повышение помехоустойчивости. Устройство для счета импульсов содержит комбинационный сумматор 1, регистр памяти 2, инвертор 3, RC-элементы 4-1...4-4 и входную шину 5. Технический результат достигнут введением RC-элементов 4-1...4-4, новых связей между функциональными элементами и выполнением разрядов регистра памяти 2 в виде тактируемых уровнем D-триггеров. 3 ил.

Устройство для счета импульсов, содержащее n-разрядный комбинационный сумматор, вход младшего разряда первого слагаемого которого соединен с входной шиной, входы остальных разрядов первого слагаемого соединены с общей шиной, а входы разрядов второго слагаемого - с выходами соответствующих разрядов n-разрядного регистра памяти, и инвертор, вход которого соединен с входной шиной, отличающееся тем, что в него введены n интегрирующих RC-элементов, входы которых соединены с выходами соответствувющих разрядов коммутационного сумматора, выходы - с информационными входами соответствующих разрядов регистра памяти, тактовый вход которого соединен с выходом инвертора, а каждый из разрядов выполнен в виде тактируемого уровнем D-триггера.

| RU, авторское свидетельство, 797078, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| RU, авторское свидетельство, 1572383, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| RU, авторское свидетельство, 1785407, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Букреев И.Н | |||

| и др | |||

| "Микроэлектронные схемы цифровых устройств", М., Радио и связь, 1990, с | |||

| Приспособление для съемки жилетно-карманным фотографическим аппаратом со штатива | 1921 |

|

SU310A1 |

Авторы

Даты

1998-03-10—Публикация

1995-08-16—Подача