Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известна энергонезависимая ячейка памяти (см. авторское свидетельство СССР 845287 от 02.07.79, МКИ: Н 03 К 19/16 "Энергонезависимая ячейка памяти", Н. М. Лукманов, опубликовано 07.07.81, БИ 25), содержащая сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой подключена через резистор к источнику питания. Конец обмотки подключен к выходу второго элемента И-НЕ и к одному из входов третьего элемента И-НЕ, второй вход которого подключен к шине разрешения, а выход - к единичному входу триггера, нулевой вход которого подключен к шине сброса, счетный вход - к информационной шине, а прямой и инверсный выходы - к первым входам, соответственно, первого и второго элементов И-НЕ, вторые входы которых подключены к шине перемагничивания.

Недостатком данной энергонезависимой ячейки памяти является низкая информационная емкость, так как данная ячейка памяти может хранить только один бит информации. Другим недостатком данной ячейки памяти является низкая помехоустойчивость, так как счетный триггер, входящий в ее состав, чувствителен к помехам на информационной шине, а инерционность сердечника для подавления указанных помех не используется.

Известна энергонезависимая ячейка памяти (см. патент России 2030094 от 07.12.92, МПК6 Н 03 К 3/037, "Энергонезависимая ячейка памяти", Л.Б. Егоров, И. В. Цетлин, опубликовано 27.02.95, БИ 6), содержащая N магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой каждый блок коммутации, первый, второй и третий логические элементы, триггер, резистор, транзистор, диод, адресные шины, шины сброса, информационную, выходную и питания. Информационный вход блока коммутации соединен с выходом первого логического элемента, выход второго логического элемента соединен с первыми выводами обмоток сердечников, вторые выводы которых подключены к соответствующим выходам блока коммутации, адресные входы которого соединены с соответствующими адресными шинами. Первый вывод резистора соединен с шиной питания, а второй - с коллектором транзистора, эмиттер которого соединен с выходом второго логического элемента и анодом диода, а база - с катодом диода и информационным выходом блока коммутации. Коллектор транзистора соединен с единичным входом триггера, нулевой вход которого подключен к шине сброса, инверсный выход - к одному входу третьего логического элемента и выходной шине. Информационная шина подключена к другому входу третьего логического элемента, выход которого соединен с входом первого логического элемента, выход которого соединен с входом второго логического элемента. Триггер выполнен в виде асинхронного RS-триггера, первый и второй логические элементы - в виде инверторов, а третий логический элемент - в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Недостатком данной энергонезависимой ячейки памяти является низкая помехоустойчивость, так как триггер чувствителен к помехам на шинах сброса и питания, которые во время записи или считывания информации могут приводить к искажению информации в соответствующем разряде энергонезависимой ячейки памяти.

Достигаемым техническим результатом является повышение помехоустойчивости энергонезависимой ячейки памяти путем защиты ее состояния от помех во время записи или считывания с помощью конденсатора.

Указанной технический результат достигается тем, что в энергонезависимую ячейку памяти, содержащую N магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой каждый блок коммутации, информационный вход которого соединен с выходом первого логического элемента, выход второго логического элемента соединен с первыми выводами обмоток сердечников, вторые выводы которых подключены к соответствующим выходам блока коммутации, адресные входы которого соединены с соответствующими адресными шинами, шины сброса, информационную, выходную и питания, с которой соединен первый вывод первого резистора, вновь введены конденсатор, второй и третий резисторы, ключ, шины управления и опроса, первый логический элемент выполнен в виде элемента ИЛИ-НЕ, первый вход которого соединен с шиной опроса, а второй вход соединен с информационным входом ключа и, через второй резистор, с выходом второго логического элемента, который соединен через конденсатор со вторым выводом первого резистора и через третий резистор с входом первого логического элемента, который соединен с выходной шиной, информационная и управляющая шины подключены к информационному и управляющему входам ключа соответственно, шина сброса соединена с входом второго логического элемента, выполненного в виде инвертора с открытым коллектором на выходе.

Блок коммутации содержит N ключей и инвертор, вход которого является информационным входом блока коммутации, а выход соединен с информационными входами ключей, управляющие входы которых являются адресными входами блока коммутации, а выходы являются выходами блока коммутации.

Указанная совокупность признаков позволяет повысить помехоустойчивость энергонезависимой ячейки памяти путем защиты ее состояния от помех во время записи или считывания за счет введения конденсатора в цепь обратной связи триггерной структуры, образуемой первым логическим элементом и выбранным каналом блока коммутации.

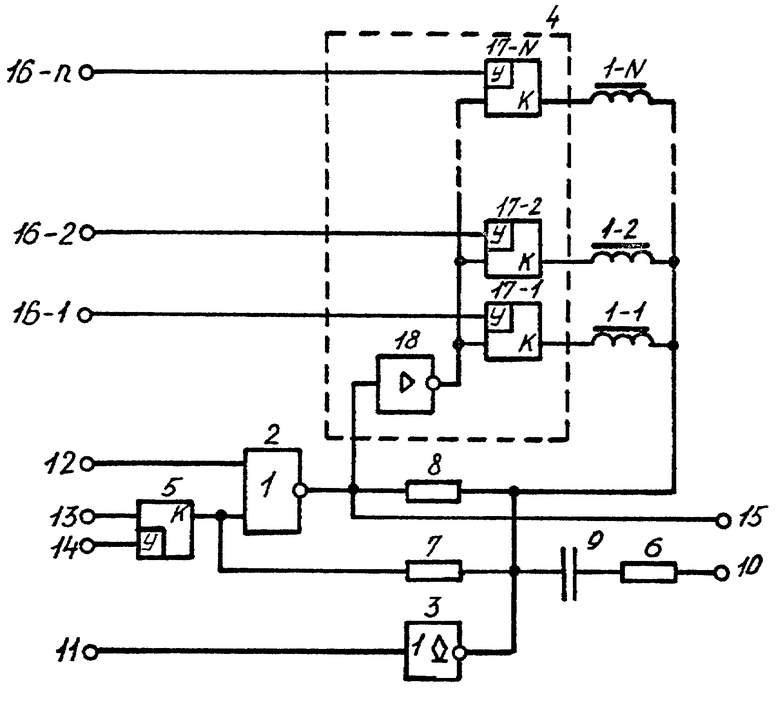

На чертеже приведена схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти (см. чертеж) содержит N магнитных сердечников 1-1, 1-2, ..., 1-N с прямоугольной петлей гистерезиса и обмоткой каждый, первый 2 и второй 3 логические элементы, блок 4 коммутации, ключ 5, первый 6, второй 7 и третий 8 резисторы, конденсатор 9, шины питания 10, сброса 11, опроса 12, информационную 13, управляющую 14, выходную 15 и адресные 16-1, 16-2, ..., 16-N. Информационный вход блока 4 коммутации соединен с выходом первого логического элемента 2, выходной шиной 15 и, через третий резистор 8, с выходом второго логического элемента 3, который соединен с первыми выводами обмоток сердечников 1-1, 1-2, ..., 1-N, через второй резистор 7 с выходом ключа 5, а через конденсатор 9 с выводом первого резистора 6, другой вывод которого подключен к шине 10 питания. Вторые выводы обмоток сердечников 1-1, 1-2, ..., 1-N подключены к соответствующим выходам блока 4 коммутации, адресные входы которого соединены с соответствующими адресными шинами 16-1, 16-2, ..., 16-N. Первый вход первого логического элемента 2 соединен с шиной 12 опроса, а второй вход - с выходом ключа 5, информационный вход которого соединен с информационной шиной 13, а управляющий вход - с управляющей шиной 14. Шина 11 сброса подключена к входу второго логического элемента 3.

Блок 4 коммутации содержит N ключей 17-1, 17-2,..., 17-N и инвертор 18, вход которого является информационным входом блока 4 коммутации, а выход соединен с информационными входами ключей 17-1, 17-2, ..., 17-N, управляющие входы которых являются адресными входами блока 4 коммутации, а выходы являются выходами блока 4 коммутации.

Энергонезависимая ячейка памяти работает следующим образом. В режиме записи на шине опроса 12 и сброса 11 подаются низкие уровни напряжения, на адресные шины 16-1, 16-2, ..., 16-N подаются уровни напряжения, соответствующие адресу сердечника (1-1, 1-2, ... или 1-N), в который производится запись, на управляющую шину 14 - высокий уровень напряжения, а на информационную шину 13 - уровень напряжения, соответствующий записываемой информации (лог. "0" или лог. "1"). При записи логического "0" на информационную шину 13 поступает высокий уровень напряжения, ток записи протекает с выхода инвертора 18 через ключ 17-i, обмотку сердечника 1-i, резистор 8 на выход логического элемента 2 (где i=1, 2, ..., N). При записи логической "1" на информационную шину 13 поступает низкий уровень напряжения и ток записи через обмотку сердечника 1-i протекает по той же цепи, но в обратном направлении.

В режиме хранения на шине 12 опроса присутствует высокий уровень напряжения, а на шине 14 управления, шине 11 сброса и всех адресных шинах 16-1, 16-2, ..., 16-N - низкие уровни напряжения. При этом все ключи 17-1, 17-2, . .., 17-N блока 4 коммутации закрыты, ток через обмотки сердечников 1-1, 1-2, . .., 1-N не протекает, на выходной шине 15 удерживается низкий уровень напряжения, а конденсатор 9 заряжен. Это состояние конденсатора 9 является исходным для считывания информации из сердечников 1-1, 1-2, ..., 1-N.

В режиме считывания на шинах сброса 11 и управляющей 14 удерживаются низкие уровни напряжения, на шине 12 опроса некоторое время сохраняется высокий уровень напряжения, а на шины 16-1, 16-2, ..., 16-N адреса выставляются уровни напряжения, соответствующие адресу сердечника 1-i, из которого производится считывание. При этом через обмотку сердечника 1-i начинает протекать ток с выхода инвертора 18 через ключ 17-i, обмотку сердечника 1-i, конденсатор 9 и резистор 6 на шину 10 питания. Этим током конденсатор 9 разряжается, и потенциал на его левой по рисунку (см. чертеж) обкладке повышается, приближаясь к порогу переключения логического элемента 2. Пока сердечник 1-i указанным током перемагничивается, сопротивление его обмотки велико, и ток незначителен, конденсатор 9 разряжается медленно. Как только сердечник 1-i входит в насыщение, ток резко возрастает и конденсатор 9 быстро разряжается. Если сердечник 1-i намагничен в состояние, соответствующее логическому "0", то ток считывания подтверждает это состояние и быстро вводит сердечник 1-i в насыщение, что приводит к быстрому разряду конденсатора 9 и повышению потенциала на входе логического элемента 2 до высокого уровня раньше, чем произойдет переход напряжения на шине 12 опроса с высокого на низкий уровень (сигнал опроса). Триггерная структура, образованная логическим элементом 2 и инвертором 18 с обратной связью через ключ 17-i, обмотку сердечника 1-i и резистор 7 сохранит исходное (нулевое) состояние, и на выходной шине 15 будет присутствовать низкий уровень напряжения.

Если же сердечник 1-i намагничен в состояние, соответствующее логической "1", то ток считывания начнет его перемагничивать. Процесс разряда конденсатора 9 будет протекать медленно (из-за высокого сопротивления обмотки сердечника 1-i), и к моменту появления на шине 12 сигнала опроса потенциал на входе логического элемента 2 (поступающий через резистор 7 с левой по рисунку обкладки конденсатора 9) будет ниже порога переключения логического элемента 2. В результате появление сигнала опроса приведет к переключению триггерной структуры в единичное состояние. На выходной шине 15 появится высокий уровень напряжения. Ток, протекающий с выхода логического элемента 2 через резистор 8, обмотку сердечника 1-i, ключ 17-i на выход инвертора 18, начнет восстанавливать состояние сердечника 1-i, частично размагниченного током считывания. Одновременно будет происходить дозарядка конденсатора 9 током, протекающим с шины 10 питания через резистор 6, конденсатор 9, обмотку сердечника 1-i, ключ 17-i на выход инвертора 18. Указанный ток также способствует восстановлению состояния сердечника 1-i.

Если во время считывания информации на энергозависимую ячейку памяти воздействуют помехи, например, по шине 10 питания в виде кратковременных перерывов питания, то заряд на конденсаторе 9 благодаря наличию резистора 6 изменится незначительно. После прекращения действия помехи, потенциал с левой по рисунку обкладки конденсатора 9 (см. чертеж) через резистор 7 поступает на вход логического элемента 2 и восстанавливает состояние триггерной структуры, образованной логическим элементом 2 и инвертором 18.

Режим считывания завершается установкой низких уровней напряжения на всех адресных шинах 16-1, 16-2, ..., 16-N и высокого уровня напряжения на шине 12 опроса. При этом коммутатор 4 запирается, а на выходе логического элемента 2 устанавливается низкий уровень напряжения. В этот момент времени конденсатор 9 находится в заряженном (исходном) состоянии, если считывалась логическая "1", или в разряженном состоянии, если считывался логический "0". В последнем случае заряд конденсатора 9 будет происходить током, протекающим с шины 10 питания через резистор 6, конденсатор 9, резистор 8 на выход логического элемента 2, и исходное состояние восстановится. Для ускорения восстановления исходного состояния конденсатора 9 следует подать высокий уровень напряжения на шину 11 сброса. При этом ток заряда конденсатора 9 будет протекать на выход элемента 3, минуя резистор 8, сопротивление которого на порядок больше сопротивления резистора 6, остающегося в цепи заряда конденсатора 9.

Изготовлен лабораторный макет энергонезависимой ячейки памяти на микросхемах серии 1526. Кроме того, ячейка памяти использовалась в составе действующих макетов приборов автоматики. Испытания указанных макетов подтвердили работоспособность заявляемого устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| МНОГОКАНАЛЬНЫЙ ДАТЧИК ОДИНОЧНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2118042C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2129331C1 |

Изобретение относится к автоматике и вычислительной технике. Его использование позволяет получить технический результат в виде повышения помехоустойчивости энергонезависимой ячейки. Технический результат достигается за счет введения в ячейку памяти конденсатора для защиты от помех во время записи и считывания. Энергонезависимая ячейка памяти состоит из N магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой каждый, двух логических элементов, блока коммутации, ключа, трех резисторов, конденсатора и шин питания, сброса, опроса, информационной, управляющей, входной и адресной. 1 з.п. ф-лы, 1 ил.

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| US 5995412 A, 30.11.1999 | |||

| US 6317359 B1, 13.11.2001. | |||

Авторы

Даты

2003-10-27—Публикация

1999-11-26—Подача