Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве многоканального счетчика импульсов и запоминающего устройства.

Известен многоканальный счетчик импульсов (см. авторское свидетельство СССР N 1170610 от 30.09.83, МКИ: H 03 K 23/66, "Многоканальный счетчик импульсов", А. А. Сенюта, А.Г. Далингер и Н.И. Левашев, опубликовано 30.07.85 г. , бюл. N 28), содержащий сумматор, оперативное запоминающее устройство, блок начальной установки, устройство управления, буферное запоминающее устройство, RS-триггер, коммутирующий элемент и буферный регистр. Информационный вход сумматора соединен с входом оперативного запоминающего устройства. Один вход сумматора соединен с первым выходом блока начальной установки, второй выход которого соединен с другим информационным входом сумматора. Первый вход блока начальной установки соединен с шиной начальной установки, а второй вход через буферный регистр соединен с выходом оперативного запоминающего устройства. Управляющие выходы устройства управления соединены соответственно с управляющими входами буферного запоминающего устройства, блока начальной установки, оперативного запоминающего устройства, коммутирующего элемента, буферного регистра и входом сброса RS-триггера. Тактовый вход устройства управления соединен с тактовой шиной, а информационные шины подключены к информационным входам буферного запоминающего элемента, выход которого соединен с входом установки RS-триггера. Выход RS-триггера соединен с входом переноса сумматора и первым входом коммутирующего элемента, второй вход которого соединен с дополнительным выходом блока начальной установки. Выход коммутирующего элемента соединен с входом записи оперативного запоминающего устройства. Выход переполнения сумматора соединен с входом переполнения блока начальной установки и с выходной шиной переполнения. Адресный выход устройства управления соединен с адресным входом оперативного запоминающего устройства и выходной адресной шиной.

Недостатком данного устройства является низкая помехоустойчивость, что связано с большой ценой сбоя при совпадении помехи с моментом переключения счетчика. Другим недостатком является отсутствие возможности программного увеличения разрядности каналов счетчика путем использования избыточной емкости оперативного запоминающего устройства, что существенно ограничивает возможность миниатюризации счетчика.

Известен многоканальный счетчик импульсов (см. авторское свидетельство СССР N 1508342 от 09.04.87 г., МКИ: H 03 K 23/66, "Многоканальный счетчик импульсов", А.Н. Миронов и В.C. Нестеренко, опубликовано 15.09.89 г., бюл. N 34), который является наиболее близким по технической сущности и выбран в качестве прототипа. Он содержит блок оперативного запоминающего устройства, блок начальной установки, первый вход которого соединен с шиной начальной установки, устройство управления, шину адреса, сумматор, регистр, коммутатор кодов, элемент ИЛИ и устройство для обслуживания запросов в порядке поступления, информационные входы которого являются информационными входами многоканального счетчика импульсов, тактовый вход соединен с первым выходом устройства управления, первый дополнительный выход соединен с первым входом коммутатора кодов, а вторые дополнительные выходы подключены к входам элемента ИЛИ. Второй и третий выходы устройства управления соединены соответственно с управляющими входами регистра и блока начальной установки. Выход элемента ИЛИ соединен с первым входом устройства управления, второй вход которого соединен с шиной начальной установки. Второй и управляющий входы коммутатора кодов соединены соответственно с шиной адреса (входящей в состав шины начальной установки) и с четвертым выходом устройства управления, а выход - с адресным входом оперативного запоминающего устройства. Входы записи и управления оперативного запоминающего устройства соединены соответственно с вторым и третьим выходами устройства управления. Четвертый выход устройства управления соединен с входом переноса сумматора. Выход сумматора соединен с информационным входом регистра, первый выход которого соединен с информационным входом оперативного запоминающего устройства, а второй выход - с выходной шиной переполнения. Второй вход блока начальной установки соединен с выходом оперативного запоминающего устройства, а выход - с входом сумматора.

Недостатком данного устройства является низкая помехоустойчивость, что связано с большой ценой сбоя при совпадении помехи с моментом переключения счетчика. Другим недостатком является отсутствие возможности программного увеличения разрядности каналов счетчика путем использования избыточной емкости оперативного запоминающего устройства, что существенно ограничивает возможность миниатюризации счетчика.

Достигаемым техническим результатом является повышение помехоустойчивости и расширение функциональных возможностей многоканального счетчика импульсов.

Указанный технический результат достигается тем, что многоканальный счетчик импульсов содержит блок оперативного запоминающего устройства (ОЗУ), блок начальной установки, первый вход которого соединен с шиной начальной установки, устройство управления и шину адреса. Новым является то, что дополнительно введены триггер четности, триггер переноса, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, N элементов ИЛИ и N элементов ИЛИ-НЕ, блок ОЗУ выполнен в виде N ячеек ОЗУ, адресные входы которых соединены с шиной адреса, входы выборки соединены с управляющим выходом блока начальной установки, а первые входы записи ячеек соединены со вторым входом блока начальной установки и шиной записи, первые информационные входы ячеек соединены с соответствующими информационными выходами блока начальной установки, второй информационный вход и прямой выход каждой ячейки соединены соответственно с первым и вторым входами соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход записи ячеек - с выходом соответствующего элемента ИЛИ-НЕ, инверсный выход каждой i-ой ячейки, кроме последней, соединен с первым входом (i+1)-го элемента ИЛИ-НЕ, первый вход каждого i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме последнего, соединен с выходом (i+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом устройства управления, а выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом устройства управления и информационным входом триггера четности, тактовый вход и выход которого соединены соответственно со вторым и третьим входами устройства управления, шина признака старшей строки и тактовая шина соединены соответственно со вторым и четвертым входами устройства управления, второй и третий выходы которого соединены с первыми входами первых элементов ИЛИ и ИЛИ-НЕ соответственно, вторые входы которых соединены с четвертым выходом устройства управления, прямой выход каждой i-ой ячейки, кроме последней, соединен с первым входом (i+1)-го элемента ИЛИ, второй вход которого соединен с выходом i-го элемента ИЛИ и вторым входом (i+1)-го элемента ИЛИ-НЕ, выход последнего элемента ИЛИ соединен с информационным входом триггера переноса, тактовый вход которого соединен с шиной признака младшей строки, а выход - с пятым входом устройства управления, шина выборки и шина блокировки соединены соответственно с третьим и четвертым входами блока начальной установки.

Ячейка ОЗУ содержит одноразрядное ОЗУ, элемент ИЛИ-НЕ, повторитель, инвертор, ключ, информационный вход которого является вторым информационным входом ячейки, а управляющий вход является вторым входом записи ячейки и соединен с первым входом элемента ИЛИ-НЕ, второй вход которого является первым входом записи ячейки, а выход соединен с входом записи одноразрядного ОЗУ, адресные входы которого являются адресными входами ячейки, а вход выборки является входом выборки ячейки и, по крайней мере, в одной ячейке через резистор соединен с шиной автономного питания, вход повторителя является первым информационным входом ячейки и соединен с информационными выходами одноразрядного ОЗУ и ключа и через резистор соединен с информационным входом одноразрядного ОЗУ, входом инвертора и выходом повторителя, который является прямым выходом ячейки, инверсным выходом которой является выход инвертора.

Блок начальной установки содержит регистр с третьим состоянием выходов и элемент И-НЕ с открытым коллектором на выходе, выход которого является управляющим выходом, а первый и второй входы - соответственно третьим и четвертым входами блока начальной установки, информационные выходы регистра являются информационными выходами, информационные входы являются первым входом, а вход управления третьим состоянием является вторым входом блока начальной установки.

Устройство управления содержит триггер управления и триггер блокировки, элементы ИЛИ-НЕ, И-НЕ и ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым выходом устройства управления, первый вход соединен с шиной реверса, а второй вход является третьим входом устройства управления, прямой и инверсный выходы триггера управления являются соответственно вторым и третьим выходами устройства управления, информационный вход является первым входом устройства управления, а тактовый вход соединен с выходом элемента И-НЕ, являющимся четвертым выходом устройства управления, тактовый вход триггера блокировки является четвертым входом устройства управления и соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом триггера блокировки, информационный вход которого соединен с шиной питания, а вход сброса соединен с выходом элемента ИЛИ-НЕ, первый и второй входы которого являются соответственно вторым и четвертым входами устройства управления.

Указанная совокупность признаков позволяет повысить помехоустойчивость многоканального счетчика импульсов за счет организации его работы в однопеременном коде Грея, имеющем минимальную цену сбоя (одну дискрету счета), и обеспечить возможность программного изменения разрядности счетных каналов за счет организации временной связи между младшей и старшей частями счетного канала с помощью триггеров переноса и четности, что позволяет при минимальных схемных затратах обеспечить удвоенную разрядность счетных каналов.

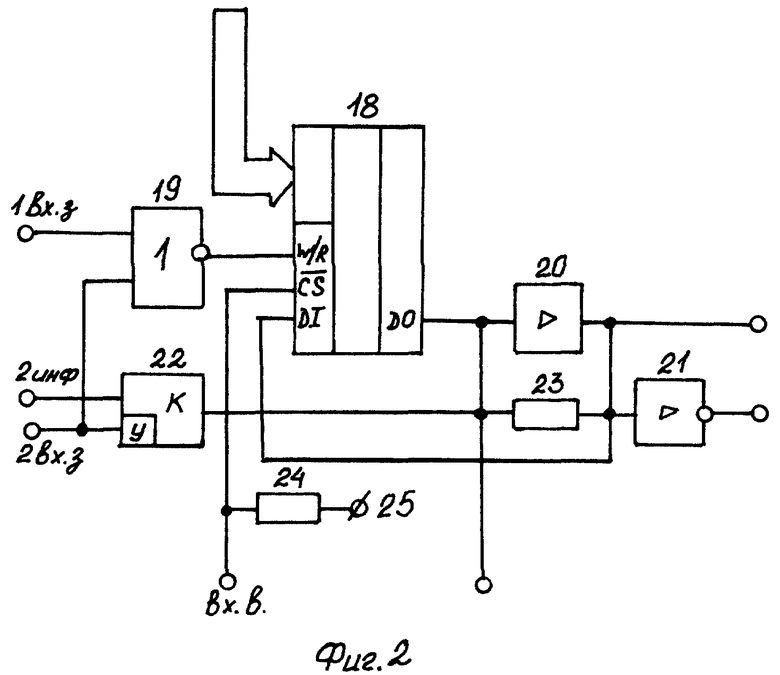

На фиг.1 приведена схема многоканального счетчика импульсов, на фиг.2 - схема ячейки ОЗУ.

Многоканальный счетчик импульсов (см. фиг.1) содержит блок 1 ОЗУ, блок 2 начальной установки, устройство 3 управления, шины начальной установки 4 и адреса 5, триггер 6 четности, триггер 7 переноса, N элементов 8-1, 8-2,..., 8-N ИСКЛЮЧАЮЩЕЕ ИЛИ, N элементов 9-1, 9-2,..., 9-N ИЛИ и N элементов 10-1, 10-2, . . ., 10-N ИЛИ-НЕ. Блок 1 ОЗУ выполнен в виде N ячеек 11-1, 11-2,..., 11-N ОЗУ, адресные входы которых соединены с шиной 5 адреса, входы выборки соединены с управляющим выходом блока 2 начальной установки.

Первые входы записи ячеек 11-1, 11-2,..., 11-N соединены со вторым входом блока 2 начальной установки и шиной 12 записи. Первые информационные входы ячеек 11-1, 11-2,..., 11-N соединены с соответствующими информационными выходами блока 2 начальной установки, второй информационный вход и прямой выход каждой ячейки (11-1, 11-2, ..., 11-N) соединен соответственно с первым и вторым входами соответствующего элемента (8-1, 8-2, ..., 8-N) ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход записи ячеек 11-1, 11-2, ..., 11-N - с выходом соответствующего элемента (10-1, 10-2, ..., 10-N) ИЛИ-НЕ. Инверсный выход каждой i-ой ячейки (11-1, 11-2, ..., 11-(N-1)), кроме последней (11-N), соединен с первым входом (i+1)-ro элемента (10-2, 10-3, ..., 10-N) ИЛИ-НЕ. Первый вход каждого i-го элемента (8-1, 8-2, ..., 8-(N-1)) ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме последнего (8-N), соединен с выходом (i+1)-ro элемента (8-2, 8-3, ..., 8-N) ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход последнего элемента 8-N ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом устройства 3 управления, а выход первого элемента 8-1 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом устройства 3 управления и информационным входом триггера 6 четности. Тактовый вход и выход триггера 6 четности соединены соответственно со вторым и третьим входами устройства 3 управления. Шина 13 признака старшей строки и тактовая шина 14 соединены соответственно со вторым и четвертым входами устройства 3 управления, второй и третий выходы которого соединены с первыми входами первых элементов ИЛИ 9-1 и ИЛИ-НЕ 10-1 соответственно, вторые входы которых соединены с четвертым выходом устройства 3 управления. Прямой выход каждой i-ой ячейки (11-1, 11-2, .. ., 11-(N-1)), кроме последней 11-N, соединен с первым входом (i+1)-ro элемента ИЛИ (9-2, 9-3, ..., 9-N), второй вход которого соединен с выходом i-го элемента ИЛИ (9-1, 9-2, ..., 9-(N-1)) и вторым входом (i+1)-ro элемента ИЛИ-НЕ (10-2, 10-3, ..., 10-N). Выход последнего элемента ИЛИ 9-N соединен с информационным входом триггера 7 переноса, тактовый вход которого соединен с шиной 15 признака младшей строки, а выход - с пятым входом устройства 3 управления. Шина 16 выборки и шина 17 блокировки соединены соответственно с третьим и четвертым входами блока 2 начальной установки.

Ячейка ОЗУ (11-1, 11-2, ..., 11-N) содержит (см. фиг.2) одноразрядное ОЗУ 18, элемент 19 ИЛИ-НЕ, повторитель 20, инвертор 21, ключ 22 и резистор 23. Информационный вход ключа 22 является вторым информационным входом ячейки ОЗУ, а управляющий вход является вторым входом записи ячейки ОЗУ и соединен с первым входом элемента 19 ИЛИ-НЕ.

Второй вход элемента 19 ИЛИ-НЕ является первым входом записи ячейки, а выход соединен с входом записи одноразрядного ОЗУ, адресные входы которого являются адресными входами ячейки, а вход выборки является входом выборки ячейки и, по крайней мере, в одной ячейке через резистор 24 соединен с шиной 25 автономного питания. Вход повторителя 20 является первым информационным входом ячейки и соединен с информационными выходами одноразрядного ОЗУ 18 и ключа 22 и через резистор 23 соединен с информационным входом одноразрядного ОЗУ 18, входом инвертора 21 и выходом повторителя 20, являющимся прямым выходом ячейки, инверсным выходом которой является выход инвертора 21.

Блок 2 начальной установки содержит регистр 26 с третьим состоянием выходов и элемент 27 И-НЕ с открытым коллектором на выходе, выход которого является управляющим выходом, а первый и второй входы - соответственно третьим и четвертым входами блока 2 начальной установки. Информационные выходы регистра 26 являются информационными выходами, информационные входы являются первым входом, а вход управления третьим состоянием является вторым входом блока 2 начальной установки.

Устройство 3 управления содержит триггер 28 управления и триггер 29 блокировки, элементы ИЛИ-НЕ 30, И-НЕ 31 и ИСКЛЮЧАЮЩЕЕ ИЛИ 32. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 32 является первым выходом устройства 3 управления, первый вход соединен с шиной 33 реверса, а второй вход является третьим входом устройства 3 управления. Прямой и инверсный выходы триггера 28 управления являются соответственно вторым и третьим выходами, а информационный вход является первым входом устройства 3 управления. Тактовый вход триггера 28 управления соединен с выходом элемента 31 И-НЕ, являющимся четвертым выходом устройства 3 управления, четвертым входом которого является тактовый вход триггера 29 блокировки, соединенный с первым входом элемента 31 И-НЕ, второй вход которого соединен с выходом триггера 29 блокировки. Информационный вход триггера 29 блокировки соединен с шиной 34 питания, а вход сброса - с выходом элемента 30 ИЛИ-НЕ, первый и второй входы которого являются соответственно вторым и пятым входами устройства 3 управления.

Многоканальный счетчик импульсов работает следующим образом. После подачи напряжений питания (основного и автономного) производится начальная установка каналов счетчика путем записи исходной информации в ячейки 11-1, 11-2, ..., 11-N блока 1 ОЗУ. При этом на шину 5 адреса подается код адреса, на шину 4 начальной установки - исходная информация в коде Грея, а на шину 12 записи и шину 17 блокировки - высокий уровень напряжения. Информация через повторители 20 поступает на информационные входы одноразрядных ОЗУ 18, на входы записи-считывания которых с выходов элементов ИЛИ-НЕ 19 поступает низкий уровень напряжения, соответствующий режиму "запись". Затем на шину 16 выборки подается высокий уровень напряжения. При этом сигнал выборки поступает на входы выборки одноразрядных ОЗУ 18 всех ячеек 11-1, 11-2, ..., 11-N, и производится запись информации по выбранному адресу. Далее на шину 16 подается низкий уровень напряжения, на шину 5 адреса подается код следующего адреса, а на шину 4 начальной установки - соответствующая ему информация в коде Грея, и процесс записи повторяется. После того, как в блок 1 ОЗУ будет записана вся исходная информация, многоканальный счетчик импульсов может быть переведен в режим хранения. В режиме хранения на шине 17 блокировки присутствует низкий уровень напряжения, основное напряжение питания снято, от автономного источника питания запитаны только одноразрядные ОЗУ 18 ячеек 11-1, 11-2, . .., 11-N. Так как выход элемента 27 И-НЕ находится в третьем состоянии, то потенциал высокого уровня с шины 25 автономного питания через резистор 24 поступает на входы выборки одноразрядных ОЗУ 18, удерживая их в режиме хранения.

В режиме счета импульсов многоканальный счетчик работает следующим образом. Подается основное напряжение питания (автономное подключено постоянно), а на шину 17 блокировки и шину 13 признака старшей строки - высокий уровень напряжения. Затем на шину 5 адреса подается код адреса старшей строки (декады), а на шину 16 выборки - высокий уровень напряжения. На входах выборки ячеек ОЗУ 11-1, 11-2, ..., 11-N устанавливается напряжение низкого уровня, поступающее на входы выборки одноразрядных ОЗУ (18), на выходах которых появляется записанная по данному адресу информация в коде Грея, которая через повторители (20) поступает на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (8-1, 8-2, ..., 8-N), образующих линейку анализа четности. Информация с выхода элемента 8-1, свидетельствующая о четности текущего кода старшей декады (строки) выбранного канала, записывается в триггер 6 четности. Затем на шину 13 признака старшей строки подается потенциал низкого уровня, на шину 15 признака младшей строки - потенциал высокого уровня, а на шину 5 адреса - адрес младшей декады (строки). На время смены адреса на шине выборки 16 устанавливается низкий уровень, а после смены адреса - снова высокий уровень напряжения. На выходах одноразрядных ОЗУ появляется код состояния младшей декады (строки) в виде кода Грея, который через повторители (20) и инверторы (21), а также через триггер 28 управления поступает на входы элементов ИЛИ-НЕ (10-1, 10-2, ..., 10-N) и ИЛИ (9-1, 9-2, ..., 9-N), образующих линейку распределения счетных импульсов. Затем на тактовую шину 14 поступает счетный импульс, который устанавливает триггер 29 блокировки в единичное состояние и проходит на выход элемента 31 И-НЕ и далее через линейку распределения импульсов на второй вход записи соответствующей ячейки ОЗУ (11-1, 11-2, ..., 11-N). Так как код Грея относится к классу однопеременных кодов, то переключение счетного канала происходит только в одном из разрядов, то есть информация по выбранному адресу изменяется только в одном из одноразрядных ОЗУ (18). При этом выход данного одноразрядного ОЗУ (18) переводится в высокоимпедансное состояние, а считанная из него информация сохраняется триггерной структурой, временно образуемой повторителем 20 и резистором 23, что необходимо для нормальной работы линейки распределения счетных импульсов (9-1, 9-2, ..., 9-N; 10-1, 10-2, ..., 10-N). Пока младшая строка (декада) не переполнилась на D-входе триггера 7 переполнения сохраняется уровень высокого напряжения, который запоминается данным триггером, и при обращении к старшей строке (декаде) с инверсного выхода триггера 7 переполнения через элемент 30 проходит сигнал, удерживающий триггер 29 блокировки в нулевом состоянии, которое блокирует прохождение счетных импульсов через элемент 31 И-НЕ. Если же младшая строка (декада) оказалась переполненной, то переключения в ней не происходит, а счетный импульс поступает на D-вход триггера 7 переполнения, запоминается им, и, при последующем обращении к старшей строке (декаде), триггер 29 блокировки счетным импульсом переключается в единичное состояние, при котором данный счетный импульс проходит через элемент И-НЕ 31 на вход линейки распределения импульсов. В результате происходит переключение в старшей строке (декаде). Уровнем низкого потенциала на шине 33 реверса счетчик может быть переведен в режим реверса. Управление счетчиком может осуществляться с помощью микроЭВМ.

Изготовлен лабораторный макет многоканального счетчика импульсов. Испытания макета подтвердили работоспособность заявляемого устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| РЕЛЕ ВРЕМЕНИ | 1996 |

|

RU2124265C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

Изобретение относится к автоматике и вычислительной технике и позволяет повысить помехоустойчивость многоканального счетчика импульсов, что является техническим результатом, за счет организации его работы в коде Грея и введения энергонезависимого оперативного запоминающего устройства (ОЗУ) и обеспечить возможность программного изменения разрядности счетных каналов за счет организации временной связи между младшей и старшей частями счетного канала с помощью триггеров переноса и четности. Многоканальный счетчик импульсов содержит блок 1 ОЗУ, блок начальной установки (БНУ) 2, устройство управления (УУ) 3, шины начальной установки 4 и адреса 5, триггер 6 четности, триггер 7 переноса, N элементов 8-1, 8-2,..., 8-N ИСКЛЮЧАЮЩЕЕ ИЛИ, N элементов 9-1, 9-2,... 9-N ИЛИ и N элементов 10-1, 10-2,... , 10-N ИЛИ-НЕ. Блок 1 ОЗУ выполнен в виде N ячеек 11-1, 11-2,...11-N ОЗУ, адресные входы которых соединены с шиной 5 адреса, входы выборки соединены с управляющим выходом БНУ 2. Первые входы записи ячеек 11-1, 11-2,...11-N соединены со вторым входом БНУ 2 и шиной 12 записи. Первые информационные входы ячеек 11-1, 11-2,.. . , 11-N соединены с соответствующими информационными выходами БНУ 2, второй информационный вход и прямой выход каждой ячейки (11-1, 11-2,..., 11-N) соединен соответственно с первым и вторым входами соответствующего элемента (8-1, 8-2,..., 8-N ) ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход записи ячеек 11-1, 11-2, . . . , 11-N - с выходом соответствующего элемента (10-1, 10-2,..., 10-N) ИЛИ-НЕ. Инверсный выход каждой i-й ячейки ( 11-1, 11-2,..., 11-(N-1)), кроме последней (11-N), соединен с первым входом (i+1)-ro элемента (10-2, 10-3,... , 10-N) ИЛИ-НЕ. Первый вход каждого i-го элемента (8-1, 8-2,..., 8-(N-1)) ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме последнего (8-N), соединен с выходом (i+1)-го элемента (8-2, 8-3,..., 8-N) ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход последнего элемента 8-N ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом УУ 3, а выход первого элемента 8-1 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом УУ 3 и информационным входом триггера 6 четности. Тактовый вход и выход триггера 6 четности соединены соответственно со вторым и третьим входами УУ 3. Шина 13 признака старшей строки и тактовая шина 14 соединены соответственно со вторым и четвертым входами УУ 3, второй и третий выходы которого соединены с первыми входами первых элементов ИЛИ 9-1 и ИЛИ-НЕ 10-1 соответственно, вторые входы которых соединены с четвертыми выходами УУ 3. Прямой выход каждой i-й ячейки (11-1, 11-2,..., 11-(N-1)), кроме последней (11-N), соединен с первым входом (i+1)-го элемента ИЛИ (9-2, 9-3, ..., 9-N), второй вход которого соединен с выходом i-го элемента ИЛИ (9-1, 9-2, . . ., 9-(N-1)) и вторым входом (i+1)-го элемента ИЛИ-НЕ (10,2, 10-3, ..., 10-N). Выход последнего элемента ИЛИ 9-N соединен с информационным входом триггера 7 переноса, тактовый вход которого соединен с шиной 15 признака младшей строки, а выход - с пятым входом УУ 3. Шина 12 выборки и шина 17 блокировки соединены соответственно с третьим и четвертым входами БНУ 2. 3 з.п.ф-лы, 2 ил.

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| RU 2004074 C1, 30.11.1993 | |||

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| Устройство автоматической балансировки радиометра | 1985 |

|

SU1397874A1 |

Авторы

Даты

2000-07-10—Публикация

1999-01-19—Подача