Изобретение относится к автоматике и импульсной технике, используется для формирования исполнительной команды через определенный интервал времени. Задание кода указанного интервала (кода уставки) и оперативный контроль работоспособности таймера с заданным кодом уставки осуществляется с помощью пульта управления.

Известно программное реле времени (см. книгу Шполянского В.А., Курицкого А. М. Программно-временные задатчики. - М.: Машиностроение, 1984, с. 377, рис. 5.88), содержащее блок управления, блок временных интервалов и блок ввода программ. Блок управления содержит триггер управления и адресный коммутатор. Блок временных интервалов содержит соединенные последовательно хронизатор, ключ тактовых импульсов и счетчик импульсов, а также оперативное запоминающее устройство, импульсные усилители. Входы управления блока временных интервалов соединены с соответствующими выходами блока управления, входы которого соединены с соответствующими входными шинами. Выходы блока ввода программ соединены с соответствующими входами временных интервалов.

Недостатком устройства является низкая достоверность функционирования, связанная с отсутствием оперативного контроля работоспособности устройства с заданной ему уставкой.

Известен таймер с контролем (см. авт. св. СССР N 1769611 от 31.01.91, кл. G 06 F 1/14, "Таймер с контролем", авторы И.И. Дикарев, А.Н. Еремин, Г. И. Шишкин, разрешено для открытого опубликования дд.N 3214 от 16.11.93), содержащий генератор тактовых импульсов, делитель частоты, два формирователя импульсов, счетчик импульсов, контрольный счетчик импульсов, блок сравнения, два логических элемента, выполненных в виде элементов И-НЕ. Вход и выход первого формирователя импульсов соединены соответственно с первым входом управления устройства и первым входом первого элемента И-НЕ. Вход и выход второго формирователя импульсов соединены соответственно с вторым входом управления устройства и первым входом второго элемента И-НЕ. Выход генератора тактовых импульсов соединен с информационным входом делителя частоты, вход обнуления которого соединен с выходом второго элемента И-НЕ, а выход - с вторым входом первого элемента И-НЕ. Второй вход второго элемента И-НЕ соединен с выходом первого формирователя импульсов. Выход второго формирователя импульсов соединен с счетным входом контрольного счетчика импульсов. Вход начальной установки устройства соединен с входом начальной установки контрольного счетчика импульсов и первым входом начальной установки счетчика импульсов, счетный вход которого соединен с выходом первого элемента И-НЕ. Информационные выходы счетчика импульсов и контрольного счетчика импульсов соединены соответственно с первым и вторым информационными входами блока сравнения, первый и второй входы разрешения которого подключены соответственно к первому и второму входам разрешения устройства. Выход блока сравнения является контрольным выходом устройства и соединен с вторым входом начальной установки счетчика импульсов, информационный выход которого является информационным выходом устройства.

Одним из недостатков устройства является низкая достоверность функционирования, обусловленная тем, что при проведении оперативного контроля устройства отсутствует проверка работоспособности генератора тактовых импульсов и делителя частоты. Другим недостатком рассматриваемого устройства является его низкая помехоустойчивость и высокая помехоизлучаемость, связанные с подачей на входы управления устройства пачек прямоугольных кодовых импульсов. Учитывая то обстоятельство, что управление таймером осуществляется дистанционно и линии связи его входов с аппаратурой управления могут быть достаточно протяженными, передача импульсных сигналов по указанным линиям, с одной стороны, является причиной повышенного электромагнитного излучения, с другой стороны, не позволяет на приемной стороне организовать эффективную частотную фильтрацию полезного сигнала от низкочастотных помех.

Задачей, решаемой предлагаемым техническим решением, является создание таймера с большой глубиной контроля, низким уровнем помехоизлучаемости и высокой помехоустойчивостью.

Технический результат, заключающийся в повышении достоверности функционирования устройства, снижении уровня его помехоизлучаемости и повышении помехоустойчивости, достигается тем, что в таймер с контролем, содержащий генератор тактовых импульсов, выход которого соединен с информационным входом делителя частоты, выход которого соединен с одним из входов логического элемента, выход которого соединен с счетным входом счетчика импульсов, включающего контрольный выход, вход начальной установки устройства соединен со входом начальной установки счетчика импульсов, а также вход управления и контрольный выход, введен резистор, один вывод которого соединен с плюсовой шиной питания устройства, другой вывод - с входом управления устройства и другим входом логического элемента, вход начальной установки устройства подключен к входу обнуления делителя частоты, контрольный выход счетчика импульсов является контрольным выходом устройства, а логический элемент выполнен в виде элемента И. Кроме того, счетчик импульсов содержит два управляющих D-триггера с статическим управлением, D-триггер с инверсным тактовым входом, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, элемент И, схему анализа четности, счетные разрядные триггеры, логический элемент и схему управления, причем тактовый вход первого управляющего D-триггера является счетным входом счетчика импульсов и через инвертор соединен с тактовым входом второго управляющего D-триггера и первыми входами логического элемента и схемы управления, прямой выход первого управляющего D-триггера соединен с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, прямой выход второго управляющего D-триггера соединен с вторыми входами логического элемента и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с счетным входом счетчика, а выход соединен с инверсным тактовым входом D-триггера, S-вход которого соединен с третьим входом логического элемента и первым выходом схемы управления, а прямой выход - с вторым входом элемента И, выход которого является контрольным выходом счетчика импульсов, инверсный выход второго управляющего D-триггера соединен с вторым входом схемы управления, третий вход которой соединен с выходом логического элемента, четвертые входы - с соответствующими первыми выходами счетных разрядных триггеров, а вторые выходы - с соответствующими входами счетных разрядных триггеров, вторые выходы которых соединены с соответствующими входами схемы анализа четности, выход которой соединен с информационными входами первого и второго управляющих D-триггеров, информационный вход D-триггера соединен с общей шиной питания, вход начальной установки счетчика импульсов соединен с четвертым входом логического элемента и входами начальной установки счетных разрядных триггеров, первого управляющего D-триггера и D-триггера.

Указанная совокупность признаков позволяет, во-первых, повысить достоверность функционирования устройства за счет организации оперативного контроля, при которой осуществляется контроль функционирования генератора тактовых импульсов и делителя частоты; во-вторых, снизить уровень помехоизлучаемости и повысить помехоустойчивость устройства за счет его организации, при которой на входах управления отсутствуют периодические импульсные сигналы, а частота импульсных сигналов, передаваемых по контрольному выходу устройства, снижена в два и более раз.

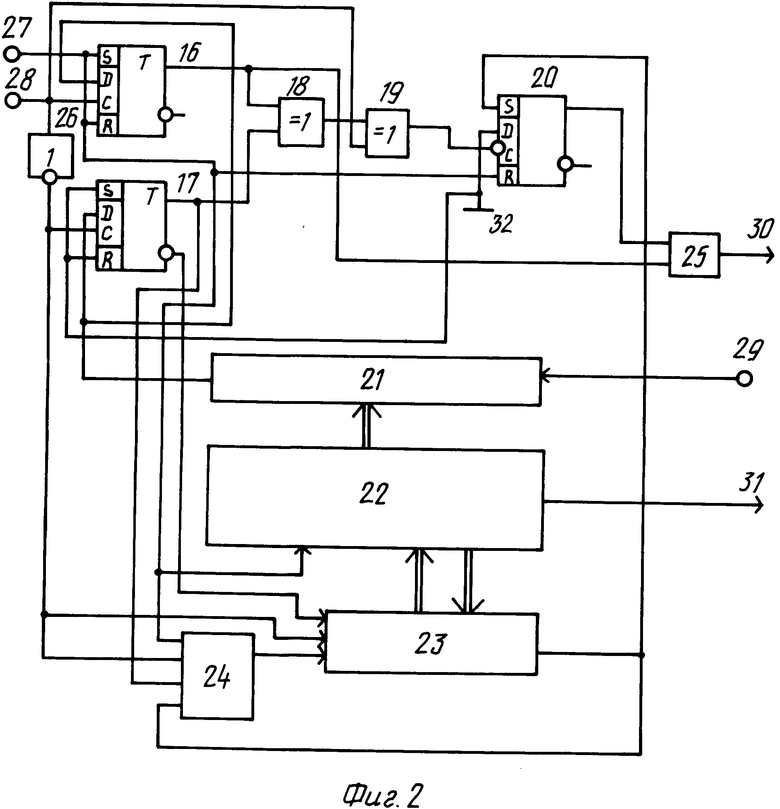

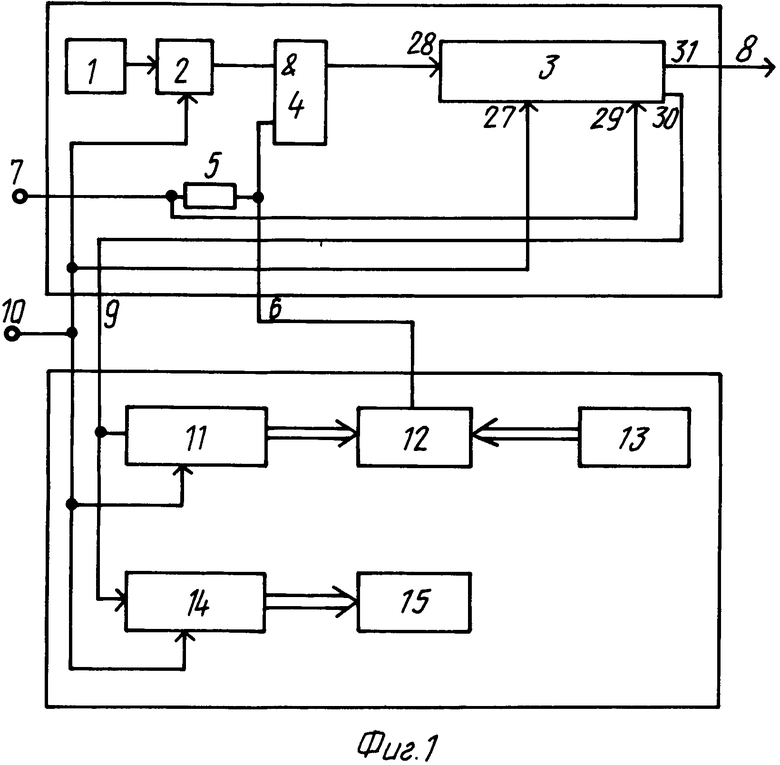

На фиг.1 представлена схема таймера с контролем совместно с пультом управления таймером; на фиг.2 - один из вариантов схемной реализации счетчика импульсов в одновременном коде со встроенной схемой контроля функционирования.

Таймер с контролем содержит (см. фиг.1) генератор 1 тактовых импульсов, делитель 2 частоты, счетчик 3 импульсов, логический элемент 4, выполненный в виде двухвходового элемента И, резистор 5. Выход генератора 1 соединен с информационным входом делителя 2 частоты, выход которого соединен с первым входом элемента 4 И. Второй вход элемента 4 И соединен непосредственно с входом 6 управления таймера и через резистор 5 - с плюсовой шиной питания таймера, выход - с счетным входом счетчика 3. Информационный выход счетчика 3 соединен с выходной шиной 8 таймера, контрольный выход счетчика 3 является контрольным выходом 9 таймера. Вход обнуления делителя 2 и начальной установки счетчика 3 соединены с входом 10 начальной установки таймера. Вход управления счетчика 3 импульсов соединен с плюсовой шиной 7 питания таймера. Пульт управления таймером содержит контрольный счетчик 11 импульсов, блок 12 сравнения, блок 13 ввода уставок, двоично-десятичный счетчик 14, блок 15 индикации. Счетные входы счетчиков 11 и 14 объединены и соединены с контрольным выходом 9 таймера. Группа информационных выходов счетчика 11 соединена соответственно с группой первых информационных входов блока 12 сравнения, группа вторых информационных входов которого соединена соответственно с группой информационных выходов блока 13 ввода уставок. Выход блока 12 сравнения соединен с входом 6 управления таймера. Группа информационных выходов двоично-десятичного счетчика 14 соединена соответственно с группой информационных входов блока 15 индикации. Входы начальной установки счетчиков 11 и 14 соединены с входом 10 начальной установки таймера. Счетчик 3 импульсов содержит (см. фиг.2) первый 16 и второй 17 управляющие D-триггеры со статическим управлением, первый 18 и второй 19 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, D-триггер 20 с инверсным тактовым входом, схему 21 анализа четности, счетные разрядные триггеры 22, схему 23 управления, логический элемент 24, элемент 25 И, инвертор 26. R- и S-входы D-триггера 16 соединены с R-входом D-триггера 20, входом начальной установки счетных разрядных триггеров 22, первым входом логического элемента 24 и с входом 27 начальной установки счетчика 3 импульсов. Тактовый вход D-триггера 16 соединен непосредственно с счетным входом 28 счетчика 3 импульсов, первым входом элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ и через инвертор 26 - с тактовым входом D-триггера 17, с вторым входом логического элемента 24 и с первым входом схемы 23 управления. Информационные входы D-триггеров 16 и 17 объединены и соединены с выходом схемы 21 анализа четности. Прямой выход D-триггера 16 соединен с первыми входами элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента 25 И. Прямой выход D-триггера 17 соединен со вторым входом элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ и с третьим входом логического элемента 24. Второй вход логического элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с инверсным тактовым входом D-триггера 20, прямой выход которого соединен со вторым входом элемента 25 И. S-вход D-триггера 20 соединен с первым выходом схемы 23 управления и с четвертым входом логического элемента 24. Инверсный выход D-триггера 17 соединен со вторым входом схемы 23 управления, третий вход которой соединен с выходом логического элемента 24, а группа четвертых входов соединена соответственно с группой первых выходов счетных разрядных триггеров 22. Группа информационных входов счетных разрядных триггеров 22 соединена соответственно с группой вторых выходов схемы 23 управления. Группа вторых выходов счетных разрядных триггеров 22 соединена соответственно с группой первых входов схемы 21 анализа четности, второй вход которой является входом 29 управления счетчика 3 импульсов. Выход элемента 25 И является контрольным выходом 30 счетчика 3 импульсов. Третий выход счетных разрядных триггеров 22 является информационным выходом 31 счетчика 3 импульсов. R- и S-входы D-триггера 17 и информационный вход D-триггера 20 объединены и соединены с общей шиной 32 питания таймера и пульта управления таймером. Представленный в примере конкретного выполнения счетчик 3 импульсов (фиг.2) построен на базе технического решения, описанного в авт. св. СССР N 1697583, кл. H 03 K 21/40 "Счетчик импульсов в коде Грея с контролем" авторов И.И. Дикарева, Л.Б. Егорова, Г. И. Шишкина, разрешенном для открытого опубликования дд. N 47 от 17.01.94). Наряду с контролем функционирования в процессе счета импульсов, в счетчике 3 обнаруживается неустановка в исходное состояние любого количества разрядных триггеров, что также повышает достоверность функционирования таймера.

Контрольный счетчик 11 импульсов работает в позиционном коде (ПДК), соответственно в ПДК представлена информация на выходе блока 13 ввода уставок, который в простейшем случае представляет собой набор переключателей (тумблеров), с помощью которых задается двоичный код требуемой величины временной уставки таймера.

Примеры конкретного выполнения генератора 1 тактовых импульсов представлены в книге Альтшуллера Г.Б. и др. Кварцевые генераторы.- М.: Радио и связь, 1984, с. 63, рис. 5.6 а, б. Делитель 2 частоты и контрольный счетчик 11 импульсов могут быть выполнены на основе четырехразрядных двоичных счетчиков-делителей К561ИЕ10, представленных в книге Шило В.Л. Популярные цифровые микросхемы, -М.: Радио и связь, 1987, с. 241, рис. 2.42. В качестве входов начальной установки делителя 2 и счетчика 11 используется R-вход счетчика-делителя. В качестве информационного входа делителя 2 и счетного входа счетчика 11 используется C-вход или  -вход счетчика-делителя, при этом неиспользуемый вход счетчика-делителя подключается к одной из шин питания. Двоично-десятичный счетчик 14 может быть выполнен на основе четырехразрядного счетчика К561ИЕ14 (см. Шило В.Л. Популярные цифровые микросхемы. -М.: Радио и связь, 1987, стр. 245, рис.2.45а). Для записи в счетчик начального кода его входы Sо-Sз подключаются к соответствующим шинам питания, вход разрешения предварительной записи SE является входом начальной установки. Для организации счета в двоично-десятичном коде вход

-вход счетчика-делителя, при этом неиспользуемый вход счетчика-делителя подключается к одной из шин питания. Двоично-десятичный счетчик 14 может быть выполнен на основе четырехразрядного счетчика К561ИЕ14 (см. Шило В.Л. Популярные цифровые микросхемы. -М.: Радио и связь, 1987, стр. 245, рис.2.45а). Для записи в счетчик начального кода его входы Sо-Sз подключаются к соответствующим шинам питания, вход разрешения предварительной записи SE является входом начальной установки. Для организации счета в двоично-десятичном коде вход  подключается к общей шине питания. Работа счетчика в режиме вычитания организуется подключением входа

подключается к общей шине питания. Работа счетчика в режиме вычитания организуется подключением входа  также к общей шине питания ("лог. 0"). С общей шиной питания соединяются также входы Cвх и Cвых микросхемы. Пример конкретного выполнения блока 15 индикации приведен в книге Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 265, рис. 2.61, где в качестве преобразователя четырехразрядного двоично-десятичного кода в семисегментный использована микросхема К564ИД5, в качестве элемента индикации - жидкокристаллический семисегментный индикатор. Входы E и F микросхемы К564ИД5 подключаются к соответствующим шинам питания.

также к общей шине питания ("лог. 0"). С общей шиной питания соединяются также входы Cвх и Cвых микросхемы. Пример конкретного выполнения блока 15 индикации приведен в книге Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 265, рис. 2.61, где в качестве преобразователя четырехразрядного двоично-десятичного кода в семисегментный использована микросхема К564ИД5, в качестве элемента индикации - жидкокристаллический семисегментный индикатор. Входы E и F микросхемы К564ИД5 подключаются к соответствующим шинам питания.

Блок 12 сравнения может быть выполнен на основе цифрового четырехразрядного компаратора К561ИП2 (см. Шило В.Л. Популярные цифровые микросхемы. -М. : Радио и связь, 1987, с.271, рис.2.67). В качестве выхода блока 12 сравнения используется выход QA=B; выходы A<B, A>B подключены к общей шине питания, вход A = B - к плюсовой шине питания.

Пример конкретного выполнения блока 13 ввода уставок представлен в описании к авт. св. СССР N 661755 от 01.07.77, кл. H 03 K 5/153, "Устройство защиты от дребезга контактов" авторов В.М. Крючкова и Л.Б. Власовой, опубликовано 05.05.79, БИ N 17. Контакты 5 тумблеров (переключателей) и резисторы 8 (см. чертеж описания), подключенные соответствующим образом к плюсовой и общей шинам питания, позволяют задавать требуемые уровни логических сигналов ("лог. 0" или "лог. 1") на выходе блока 13 ввода уставок.

Таймер с контролем работает следующим образом. Перед включением таймера в режим задания уставки на блоке 13 ввода уставок набирается код требуемой уставки. В режим задания и контроля заданной уставки после подачи напряжения питания таймера и пульта управления (шины 7, 32) производится приведение в исходное состояние по входу 10 начальной установки делителя 2 частоты, счетчиков 3, 11, 14. Импульс начальной установки, действуя на один из входов логического элемента 24 счетчика 3, в случае, если все счетные разрядные триггеры 22 установились в нулевое исходное состояние, вызывает на выходе схемы 23 управления, связанном с S-входом D-триггера 20, сигнал "лог.1". После окончания импульса начальной установки и выхода на режим генератора 1 тактовых импульсов на выходе делителя 2 частоты периодически формируются счетные импульсы, которые проходят через элемент 4 И на счетный вход 28 счетчика 3 импульсов, поскольку на входе 6 управления таймера присутствует сигнал разрешения ("лог. 1"), формируемый с выхода блока 12 сравнения пульта управления. D-триггер 20 после окончания импульса начальной установки устанавливается в состояние "лог.1", разрешая прохождение контрольных импульсов с прямого выхода D-триггера 16 через элемент 25 И на контрольный выход 9 таймера. Счетные разрядные триггеры 22 переключаются в соответствии с логикой кода Грея: нечетными счетными импульсами переключается триггер 1-го разряда, четными - триггеры 2-N разрядов, при этом переключение осуществляется в разряде, следующем за самым младшим разрядом, находящимся в состоянии "лог. 1". Указанная логика переключения обеспечивается схемой 23 управления, совместно со схемой 21 анализа четности, D-триггером 17 и логическим элементом 24. D-триггер 17 запоминает информацию на выходе схемы 21 анализа четности в паузе между счетными импульсами и сохраняет ее на время счетного импульса, благодаря чему обеспечивается устойчивое переключение счетных разрядных триггеров 22. D-триггер 16 запоминает информацию на выходе схемы 21 анализа четности во время счетного импульса и сохраняет ее в паузе между счетными импульсами. С помощью схем 18, 19 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется сигнал ошибки, поступающий на инверсный тактовый вход D-триггера 20: в случае, если с поступлением на вход счетчика 3 каждого счетного импульса уровень сигнала на выходе схемы 21 анализа четности изменяется на противоположный, сигнал ошибки поступает в виде уровня "лог.1", что соответствует нормальному функционированию счетчика, разряды которого переключаются по логике однопеременного кода; в случае, если с поступлением на вход счетчика 3 очередного импульса уровень сигнала на выходе схемы 21 не изменяется, сигнал ошибки поступает в виде уровня "лог.0", что свидетельствует о непереключении разрядного триггера, либо о переключении одновременно двух разрядных триггеров, что является следствием отказов элементов схемы счетчика 3. Так как после прохождения первого счетного импульса и переключения счетного триггера 1-го разряда сигнал "лог.1" на S-входе D-триггера 20 снимается, указанный триггер готов к переключению в состояние "лог. 0" под действием сигнала ошибки (сигнала "лог.0"), поступающего на его инверсный тактовый вход. Переключение D-триггера 20 под действием сигнала ошибки может осуществляться также и в паузе между счетными импульсами, что является следствием несанкционированного переключения одного из разрядных триггеров 21 в результате отказа элементов схемы. В случае, если счетные разрядные триггеры 22 под действием импульса начальной установки обнулены, а счетчик 3 в процессе задания кода уставки функционирует нормально, на контрольном выходе 30 счетчика 3 присутствуют контрольные импульсы, которые поступают на счетные входы счетчиков 11 и 14. Блок 12 сравнения осуществляет сравнение двоичных кодов, поступающих на него со счетчика 11 и блока 13 ввода уставок. При досчете счетчика 11 до состояния, когда двоичный код, соответствующий состоянию его разрядов, сравниваются с кодом, задаваемым блоком 13 ввода уставок, на выходе блока 12 сравнения формируется сигнал "лог. 0", запрещающий дальнейшее прохождение счетных импульсов на вход счетчика 3 импульсов. Количество счетных импульсов (Nз), прошедших на вход счетчика 3, соответствует коду заданной уставки и связано с временем отработки уставки (tу) соотношением:

tу=Tсч(K-Nз) (1),

где

Tсч - период счетных импульсов на входе счетчика 3, K - коэффициент пересчета счетчика 3 по выходу 31. Контрольные импульсы, поступившие с выхода 30 счетчика 3, фиксируются также двоично-десятичным счетчиком 14, преобразуясь в код, удобный для отражения на цифровом табло блока 15 индикации. Таким образом, после задания уставки таймеру на цифровом табло блока 15 индикации высветится число, соответствующее коду заданной уставки, причем этот результат появится только в случае правильного функционирования схемы таймера.

Для включения таймера в режим отработки уставки необходимо отключить его вход 6 управления от пульта управления таймером. В этом случае на входе элемента 4 И, связанном с резистором 5, формируется сигнал "лог.1" и счетные сигналы с выхода делителя 2 частоты поступают на счетный вход счетчика 3 импульсов. Переполнение счетчика 3 по выходу 31 происходит через время tу, отсчитываемое с момента включения таймера в режим отработки уставки, в результате, на выходной шине 8 таймера формируется командный импульс, временное положение которого соответствует коду заданной уставки.

На практике перед включением таймера в режим отработки уставки снимается напряжение питания с пульта управления таймером, затем пульт отстыковывается от таймера по всем линиям связи, при этом питание таймера осуществляется от автономного источника. Цепи питания элементов и схем, входящих в состав таймера и пульта управления таймером, на фиг.1 не представлены.

В случае отсутствия в составе счетных разрядных триггеров 22 элементов энергонезависимой памяти питание таймера при переходе из режима задания и контроля в режим отработки уставки должно быть организовано без перерыва. В случае, если в составе счетных разрядных триггеров 22 имеются элементы энергонезависимой памяти, напряжение питания таймера после задания и контроля уставки может быть снято на неограниченное время. Включение таймера в режим отработки уставки осуществляется в этом случае подачей на него напряжения питания при отключенном пульте управления таймером; по входу 10 начальной установки таймера одновременно с подачей напряжения питания должен быть подан импульс начальной установки.

Как следует из описания работы таймера с контролем, при задании и контроле уставки формирование контрольных импульсов на выходе 9 таймера возможно только при работоспособных генераторе 1, делителе 2 частоты, следовательно, указанные схемы охвачены контролем, благодаря чему повышена достоверность функционирования устройства. По входу 6 управления таймера передается однократный перепад напряжения питания, частота сигналов на контрольном выходе 9 таймера в два раза ниже частоты тактового сигнала на счетном входе 28 счетчика 3 импульсов, благодаря этому снижен уровень помехоизлучаемости и повышена помехоустойчивость таймера с контролем.

В институте изготовлен лабораторный макет таймера с контролем и пульта управления таймером, испытания которых подтвердили осуществимость и практическую ценность заявленного объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| РЕЛЕ ВРЕМЕНИ | 1996 |

|

RU2124265C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

Изобретение относится к автоматике и импульсной технике и может быть использовано для задания определенного интервала времени. Цель изобретения - повышение достоверности функционирования и помехоустойчивости. Таймер с контролем содержит генератор тактовых импульсов, делитель частоты, счетчик импульсов, элемент И, резистор. 1 з.п.ф-лы, 2 ил.

Авторы

Даты

1998-06-10—Публикация

1995-08-16—Подача