Изобретение относится к импульсной технике и может быть использовано в различных устройствах вычислительной техники и систем управления.

Известно устройство для счета импульсов (авт. св. СССР N 797078 от 23.02.79, МКИ: H 03 К 23/00 "Устройство для счета импульсов", авторы С.И. Ткаченко, Р.В. Коровин и A.C. Черенков, опубл. в БИ N 2, 1981 г.), содержащее счетчик, выходы которого соединены с входами блока фиксации изменения кода, с входами первой группы вентильных элементов и с входами разрядов первого слагаемого комбинационного сумматора, входы разрядов второго слагаемого которого соединены с входами второй группы вентильных элементов и с выходами регистра памяти. Входы регистра памяти соединены с выходами первой группы вентильных элементов. Установочные входы счетчика соединены с выходами второй группы вентильных элементов. Выход комбинационного сумматора через нуль-орган соединен с входом элемента НЕ и с первым входом первого элемента совпадения, выход которого соединен с управляющим входом первой группы вентильных элементов и с первым входом элемента ИЛИ. Второй вход элемента ИЛИ соединен с управляющим входом второй группы вентильных элементов и с выходом второго элемента совпадения, первый вход которого соединен с выходом элемента НЕ, второй вход - с вторым входом первого элемента совпадения и с выходом первого элемента задержки, третьи входы первого и второго элементов совпадения соединены с выходом триггера, вход установки в единицу которого соединен с входом первого элемента задержки и с выходом блока фиксации изменения кода. Вход установки в ноль триггера соединен с выходом второго элемента задержки, вход которого соединен с выходом элемента ИЛИ. Входная шина соединена с тактовым входом счетчика.

Недостатками данного устройства являются:

1) сложность схемной реализации, обусловленная сложностью алгоритма работы;

2) относительно низкая помехоустойчивость, определяемая помехоустойчивостью регистра памяти и основного счетчика, при этом последний не защищен от одиночных помех;

3) постоянный коэффициент пересчета, определяемый разрядностью основного счетчика, что не позволяет использовать устройство в качестве делителя частоты с произвольным (в пределах объема основного счетчика) коэффициентом деления (пересчета).

Указанные недостатки устройства ограничивают область его применения.

Известно устройство для счета импульсов в виде накапливающего сумматора (см. книгу: Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств, М., Радио и связь, 1990 г., стр. 310, рис. 8.20), которое является прототипом и в режиме счета импульсов содержит n-разрядный комбинационный сумматор, n-разрядный регистр суммы в виде регистра памяти, n-разрядный регистр второго слагаемого, инвертор и входную шину, соединенную с тактовым входом регистра второго слагаемого, со входом младшего разряда второго слагаемого комбинационного сумматора и через инвертор - с тактовым входом регистра суммы. Входы разрядов комбинационного сумматора соединены с информационными входами соответствующих разрядов регистра суммы, выходы разрядов которого соединены с информационными входами соответствующих разрядов регистра второго слагаемого, выходы разрядов которого соединены с соответствующими входами второго слагаемого комбинационного сумматора. Входы старших разрядов, начиная со второго, первого слагаемого комбинационного сумматора соединены с общей шиной устройства.

Недостатками данного устройства являются:

1) низкая помехоустойчивость, определяемая помехоустойчивостью регистра второго слагаемого и регистра суммы;

2) постоянный коэффициент пересчета, определяемый разрядностью регистра суммы и регистра второго слагаемого, что не позволяет использовать устройство в качестве делителя частоты с произвольным (в пределах объема счетного устройства) коэффициентом деления (пересчета).

Указанные недостатки устройства ограничивают область его применения.

Достигаемым техническим результатом является расширение области применения устройства.

Указанный технический результат достигается тем, что в устройство для счета импульсов, содержащее n-разрядный комбинационный сумматор, регистр памяти и инвертор, вход которого соединен со входной шиной устройства, выход - с тактовым входом регистра памяти, введены n RC-элементов и формирователь коэффициента пересчета, тактовый вход которого соединен со входной шиной устройства, выходы разрядов соединены со входами соответствующих разрядов первого слагаемого комбинационного сумматора, а информационные входы - с выходами соответствующих разрядов регистра памяти и со входами соответствующих разрядов второго слагаемого комбинационного сумматора, выходы разрядов которого через соответствующие RC-элементы соединены с информационными входами соответствующих разрядов регистра памяти, каждый из разрядов которого выполнен в виде тактируемого уровнем одноступенчатого Д-триггера.

Указанная совокупность признаков позволяет повысить уровень помехоустойчивости устройства за счет возможности порогового контроля длительности счетных импульсов и обеспечивает деление частоты следования импульсов с произвольным коэффициентом деления (в пределах количества состояний устройства) за счет возможности установки (выбора) требуемого коэффициента деления, что в итоге позволяет расширить область применения устройства.

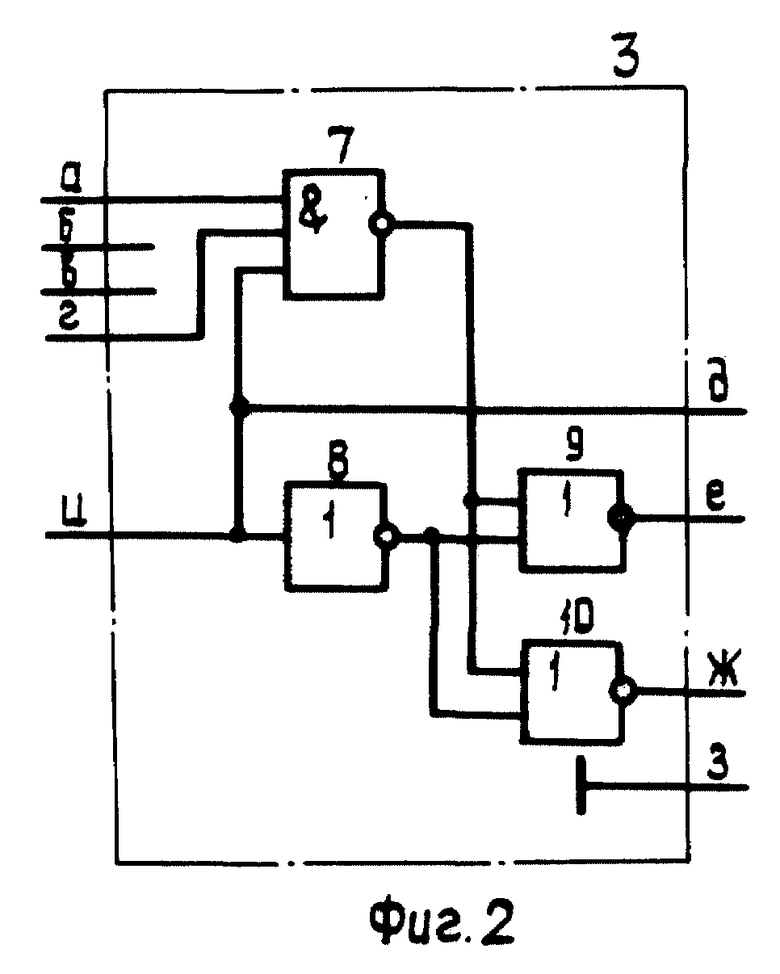

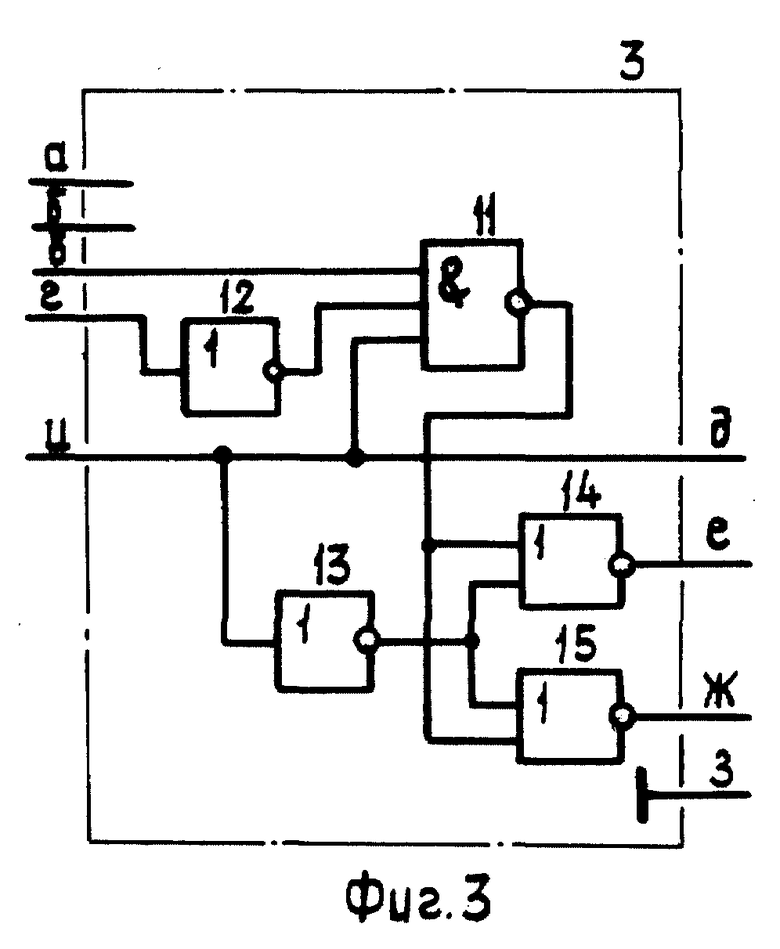

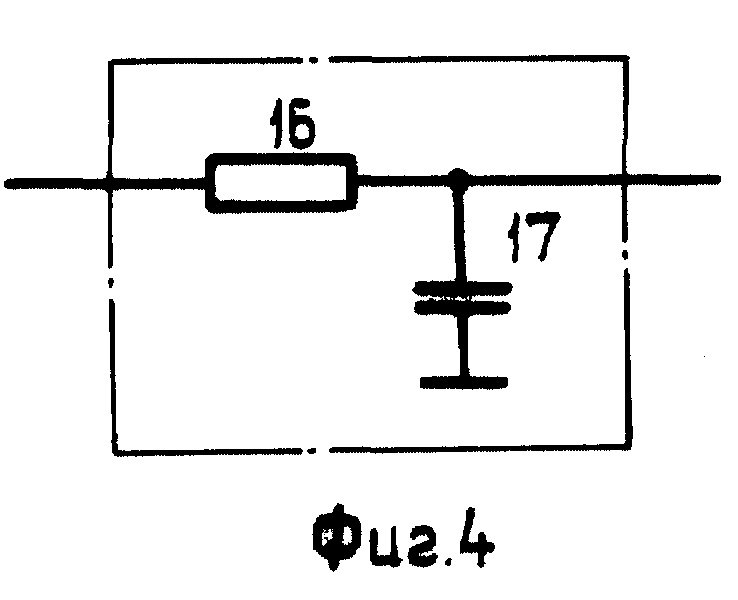

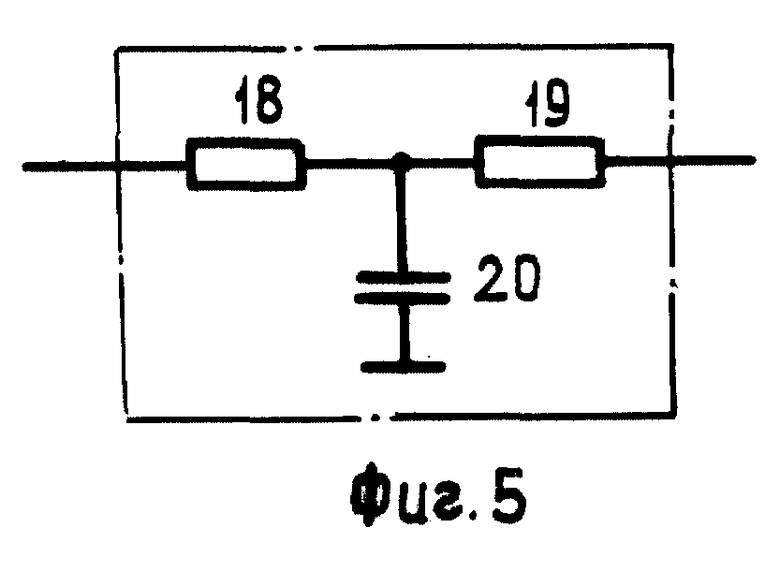

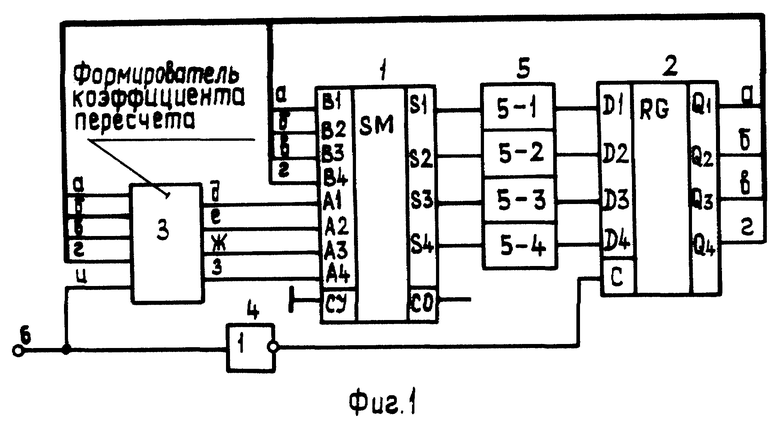

На фиг. 1 приведена схема устройства для счета импульсов в четырехразрядном варианте, на фиг. 2 и фиг. 3 - схемы вариантов реализации формирователя коэффициента пересчета для коэффициента 10, а на фиг. 4 и фиг. 5 - схемы возможных вариантов реализации RC-элементов.

Устройство для счета импульсов (см. фиг. 1) содержит четырехразрядный комбинационный сумматор 1, четырехразрядный регистр памяти 2, формирователь 3 коэффициента пересчета, инвертор 4 и четыре RC-элемента 5-1...5-4. Тактовый вход формирователя 3 соединен с входной шиной 6 устройства, выходы разрядов соединены со входами соответствующих разрядов первого слагаемого (А1.. .А4) сумматора 1, а информационные входы - с выходами соответствующих разрядов регистра 2 и со входами соответствующих разрядов второго слагаемого (В1. . . В4) сумматора 1. Входы RC-элементов 5-1...5-4 соединены с выходами соответствующих разрядов сумматора 1, а выходы - с информационными входами соответствующих разрядов регистра 2. Тактовый вход регистра 2 соединен с выходом инвертора 4, вход которого подключен к входной шине 6 устройства.

Регистр 2 выполнен на тактируемых уровнем одноступенчатых Д-триггерах с объединением их тактовых входов. Информация в указанные триггеры записывается высоким уровнем сигнала на их тактовых входах, то есть на тактовом входе регистра 2.

Формирователь 3 выполнен по схеме фиг. 2 на элементе 7И, инверторе 8 и элементах 9, 10 ИЛИ-НЕ и обеспечивает коэффициент пересчета К = 10. Конкретное схемотехническое решение формирователя 3 зависит от способа формирования выбранного коэффициента пересчета. Таких способов два:

1) в процессе работы устройства в формирователе 3 дешифрируется (К-1)-е состояние устройства и при поступлении следующего (К-го) счетного импульса на тактовый вход устройства на выходы разрядов формирователя 3 с помощью соответствующих логических элементов выдается двоичный код числа 2n - (К-1), где n - количество разрядов устройства, приводящий устройство к переполнению и, тем самым, к исключению лишних состояний;

2) в формирователе 3 дешифрируется состояние устройства, меньшее чем (К-1), и при поступлении следующего счетного импульса на выходы разрядов формирователя 3 выдается двоичный код числа, приводящий к исключению последующих 2n - (К-1) состояний устройства, после чего устройство до переполнения работает в обычном режиме.

Схема формирователя 3, приведенная на фиг. 2, реализует первый из указанных способов формирования коэффициента пересчета, а на схеме фиг. 3 приведена схема, выполненная на элементе 11И, инверторах 12, 13 и элементах 14, 15 ИЛИ-НЕ, реализующая второй из указанных способов при том же выбранном коэффициенте пересчета К = 10. Формирователь 3 может содержать дешифратор и логические элементы как для выбора одного коэффициента пересчета, так и дешифраторы и соответствующие им логические элементы для нескольких или для всех возможных для конкретного устройства (в зависимости от количества разрядов) коэффициентов пересчета, объединенных на выходе по схеме ИЛИ. В последнем случае нужный коэффициент пересчета устройства может быть выбран путем подачи внешнего разрешающего сигнала на дополнительный вход соответствующего дешифратора формирователя 3.

RC-элементы 5-1...5-3 выполнены по одинаковой схеме, приведенной на фиг. 4 (на резисторе 16 и конденсаторе 17), представляющей собой интегрирующую RC-цепь. Могут быть выполнены, при необходимости, по схеме, приведенной на фиг. 5, на двух резисторах 18, 19 и конденсаторе 20, обеспечивающей защиту информационных входов Д-триггеров регистра 2 от перегрузки по входному току (например, от токов разряда конденсаторов RC-элементов при выключении питания) при реализации устройства на базе микросхем, изготовленных по КМОП-технологии.

Информация о текущих состояниях устройства снимается, при необходимости, с выходов регистра 2, где сигналы имеют крутые фронты и срезы, а сигнал переполнения устройства - с выхода переноса сумматора 1.

Построение устройства с количеством разрядов больше, чем показано на фиг. 1, может быть выполнено двумя способами:

1) увеличением количества разрядов сумматора 1 и регистра 2, количества RC-элементов 5, количества информационных выходов, выходов разрядов формирователя 3 при соответствующем изменении схемы последнего;

2) последовательным соединением устройств, реализованных на базе стандартных малоразрядных регистров 2 и малоразрядных сумматоров 1, имеющих входы (CJ) и выходы (CO) переноса; при этом вход переноса сумматора 1 последующего устройства подключается к выходу переноса сумматора 1 предыдущего устройства.

Устройство для счета импульсов работает следующим образом.

В исходном состоянии на входной шине 6 поддерживается уровень логического нуля, следовательно, на тактовом входе формирователя 3 - уровень логического нуля, а на тактовом входе регистра 2 - уровень логической единицы, то есть сигнал записи информации. Конденсаторы 17 RC-элементов 5-1...5-4 разряжены, поэтому на информационных входах (Д1...Д4) регистра 2 присутствуют уровни логического нуля. Поскольку на тактовом входе регистра 2 присутствует уровень логической единицы, уровни логического нуля с конденсаторов соответствующих RC-элементов 5-1. . .5-4 "записываются" в тактируемые уровнем Д-триггеры разрядов регистра 2, при этом на выходах всех разрядов последнего поддерживаются уровни логического нуля. Эти уровни логического нуля поступают на входы разрядов второго слагаемого (В1...В4) сумматора 1 и на информационные входы формирователя 3. При этом на выходе элемента 7И (см. фиг. 2) поддерживается уровень логической единицы, а на выходах элементов 9, 10 ИЛИ-НЕ - уровни логического нуля. Выход старшего разряда формирователя 3 постоянно подключен к общей шине устройства (то есть к уровню логического нуля), а на тактовом входе поддерживается уровень логического нуля, поэтому на его выходах и, следовательно, на входах разрядов первого слагаемого (А1...А4) сумматора 1 поддерживаются уровни логического нуля. На входах разрядов обоих слагаемых сумматора 1 оказываются приложенными уровни логического нуля. Поэтому на выходах всех его разрядов также поддерживаются уровни логического нуля, которые поддерживают исходное разряженное состояние конденсаторов 17 RC-элементов 5-1...5-4 и, тем самым, исходное нулевое состояние Д-триггеров регистра 2, так как на тактовом входе последнего присутствует уровень логической единицы (сигнал записи). Таким образом, в исходном состоянии устройство само себя поддерживает по замкнутым цепям: выходы RC-элементов 5-1...5-4 - информационные входы и выходы регистра 2 - входы второго слагаемого и выходы сумматора 1 - входы RC-элементов 5-1...5-4.

В указанное исходное состояние устройство при включении питания устанавливается самостоятельно.

Рассмотрим работу устройства в процессе счета импульсов, предполагая, что перед началом работы устройство находится в исходном состоянии.

При поступлении по входной шине 6 первого счетного импульса (с уровнем логической единицы) на тактовом входе формирователя 3 на время действия этого импульса устанавливается уровень логической единицы, на тактовом входе регистра 2 - уровень логического нуля. При логическом нуле на тактовом входе регистр 2 становится нечувствительным к изменению уровней сигналов на информационных входах, но сохраняет свое исходное (нулевое) состояние, поэтому на всех входах второго слагаемого сумматора 1 и на всех информационных входах формирователя 3 также сохраняются уровни логического нуля. При этом на выходе элемента 7 И-НЕ формирователя 3 (см. фиг. 2) поддерживается уровень логической единицы, поэтому на выходах элементов 9, 10 ИЛИ-НЕ - уровни логического нуля. На выходе младшего разряда (∂) формирователя 3 во время действия первого счетного импульса поддерживается уровень логической единицы, а на выходах остальных разрядов - уровни логического нуля. Следовательно, в течение первого счетного импульса на входах первого слагаемого сумматора 1 присутствует двоичный позиционный код 0001 (код числа 1). Так как на входах второго слагаемого сумматора 1 в это же время имеются уровни логического нуля, на выходах разрядов сумматора 1 в течение первого счетного импульса будет поддерживаться код 0001. При этом заряжается конденсатор 17 RC-элемента 5-1, а конденсаторы 17 остальных RC-элементов остаются разряженными. Время заряда до уровня логической единицы (разряда до уровня логического нуля) конденсаторов 17 RC-элементов 5-1...5-4 выбирается таким образом, чтобы заряд (разряд) конденсаторов завершался до окончания счетного импульса (интервала между счетными импульсами). Заряд конденсатора 17 RC-элемента 5-1 не приводит к изменению состояния Д-триггера младшего разряда регистра 2, поскольку последний в течение счетного импульса нечувствителен к изменениям уровней сигналов на информационных входах.

После окончания первого счетного импульса на входной шине 6 восстанавливается исходный уровень логического нуля, на тактовом входе регистра 2 - уровень логической единицы (сигнал записи). При этом уровень логической единицы с заряженного конденсатора 17 RC-элемента 5-1 записывается в Д-триггер младшего разряда регистра 2. В результате после окончания первого счетного импульса на выходах разрядов регистра 2 устанавливается двоичный код 0001 числа 1, который поступает на входы разрядов второго слагаемого сумматора 1 и на информационные входы формирователя 3. На выходах последнего устанавливаются уровни логического нуля, то есть код 0000, который поступает на входы разрядов первого слагаемого сумматора 1, на входах разрядов второго слагаемого которого уже присутствует код 0001. В итоге на выходах разрядов сумматора 1 после окончания первого счетного импульса устанавливается также двоичный код 0001 числа 1, который поддерживает заряженное состояние конденсатора 17 RC-элемента 5-1 и разряженное состояние конденсаторов 17 RC-элементов 5-2...5-3. Указанные уровни сигналов конденсаторов RC-элементов 5-1.. .5-4 поддерживают, в свою очередь, новое состояние регистра 2, в которое тот переключился после окончания первого счетного импульса уровнем логической единицы на своем тактовом входе.

Таким образом, после первого счетного импульса устройство переключается в соответствующее состояние (код - 0001) и само активно поддерживает это состояние по замкнутым цепям: выходы разрядов регистра 2 - входы разрядов второго слагаемого и выходы разрядов сумматора 1 - RC-элементы 5-1...5-4 - информационные входы регистра 2. Следует отметить, что в указанное новое состояние устройство переключается только в том случае, если длительность счетного импульса достаточна для заряда конденсатора 17 RC-элемента 5-1 до уровня логической единицы, то есть сигнал, поступивший по входной шине 6, не является помехой. В противном случае устройство сохраняет свое исходное (нулевое) состояние.

При поступлении второго счетного импульса на тактовый вход формирователя 3 снова оказывается приложенным (в течение импульса) сигнал с уровнем логической единицы, а на тактовый вход регистра 2 - с уровнем логического нуля. Регистр 2 снова становится нечувствительным к изменениям уровней сигналов на информационных входах, но сохраняет свое состояние. Поэтому в течение второго счетного импульса на входах разрядов второго слагаемого сумматора 1 присутствует код 0001. При этом на выходы формирователя 3 (фиг. 2) выдается, как и в течение первого счетного импульса, код 0001, а сумматор 1 складывает коды на входах первого и второго слагаемых и на его выходах появляется код 0010 числа 2. Это приводит к тому, что в течение второго счетного импульса разряжается конденсатор 17 RC-элемента 5-1 и заряжается конденсатор 17 RC-элемента 5-2, а конденсаторы остальных RC-элементов остаются в разряженном состоянии.

После окончания второго счетного импульса новые уровни сигналов на информационных входах регистра 2 записываются в этот регистр, то есть на выходах его разрядов устанавливается код 0010 числа 2. Это новое состояние регистра 2 само себя поддерживает по указанным выше замкнутым цепям: выходы регистра 2 - входы второго слагаемого и выходы сумматора 1 - RC-элемента 5-1...5-4 - информационные входы регистра 2.

Аналогично устройство работает при поступлении третьего и последующих счетных импульсов вплоть до поступления К-го импульса: в течение очередного счетного импульса на выходах формирователя 3 поддерживается код 0001 (код числа 1), на входах второго слагаемого сумматора 1 - код состояния устройства, соответствующий предыдущему счетному импульсу, на выходах сумматора 1 - код нового состояния устройства, а после окончания счетного импульса это новое состояние устройства, "запомненное" конденсаторами 17 RC-элементов 5-1. ..5-4, записывается в регистр 2 и активно поддерживается до поступления следующего счетного импульса по упомянутым выше замкнутым цепям.

При поступлении К-го счетного импульса (в нашем случае - десятого) на выходы формирователя 3 в течение этого импульса выдается не код 0001 счетного импульса (код числа 1), а код числа 2n - (К-1). В нашем случае это код 0111 числа 7, который формируется следующим образом: после девятого счетного импульса на информационных входах формирователя 3 присутствует код 1001 числа 9, на выходе элемента 7И (см. фиг. 2) - уровень логического нуля, на входе и выходе инвертора 8 соответственно уровни логического нуля и логической единицы, на выходах элементов 9, 10 ИЛИ-НЕ - уровень логического нуля. Поэтому при поступлении десятого счетного импульса (в течение этого импульса) с выходов формирователя 3 на входы первого слагаемого сумматора 1 выдается код 0111 числа 7. Поскольку в течение десятого счетного импульса на входах второго слагаемого сумматора 1 поддерживается код 1001 предыдущего состояния устройства (код числа 9), на выходы сумматора 1 в течение этого импульса выдается код 0000 исходного нулевого состояния устройства. При этом разряжаются конденсаторы 17 RС-элементов 5-1 и 5-4, конденсаторы 17 остальных RC-элементов остаются разряженными.

После окончания десятого счетного импульса код 0000 исходного нулевого состояния устройства, запомненного конденсаторами 17 RC-элементов 5-1...5-4, записывается в регистр 2 и далее оно само себя активно поддерживает по упомянутым выше замкнутым цепям.

При поступлении последующих счетных импульсов начинается новый цикл работы устройства.

Устройство нормально функционирует, если длительность тактового импульса достаточна для заряда до уровня логической единицы (разряда до уровня логического нуля) конденсаторов 17 RC-элементов 5-1...5-4. Если по входной шине 6 поступает помеха, то после ее окончания устройство сохраняет свое текущее состояние. Устройство также сохраняет свое состояние и при "делении" счетного импульса на части короткими помехами. Уровень помехоустойчивости устройства легко может регулироваться в широких пределах путем изменения сопротивления резисторов 16 или (и) емкости конденсаторов 17 RC-элементов 5-1. ..5-4.

Устройство обеспечивает деление частоты импульсов, поступающих по входной шине 6, с произвольным (в пределах количества состояний устройства) коэффициентом деления. Конкретный коэффициент деления устройства и соответствующая схемотехническая реализация формирователя 3 по известным правилам алгебры логики с использованием указанных выше способов его реализации выбираются потребителем устройства.

Указанные преимущества предлагаемого устройства перед прототипом (более высокая помехоустойчивость с возможностью регулирования ее уровня и деление частоты следования импульсов с произвольным, в пределах количества состояний устройства, коэффициентом деления) расширяют область его применения.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в институте построен и испытан в диапазоне рабочих температур от минус 50oC до плюс 50oC лабораторный макет, выполненный по схеме фиг. 1 (при этом формирователь 3 был реализован по схеме фиг. 2) на базе интегральных микросхем серии 564 и дискретных резисторов типа С2-33Н и конденсаторов типа К10-17а. При этом сумматор 1 был реализован на одном корпусе микросхемы 564ИМ1, регистр 2 - на одном корпусе микросхемы 564ТМ3.

Испытания показали осуществимость заявляемого устройства для счета импульсов и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| МНОГОКАНАЛЬНЫЙ ДАТЧИК ОДИНОЧНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2118042C1 |

| ПОМЕХОУСТОЙЧИВЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | 2000 |

|

RU2168856C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| ПОМЕХОУСТОЙЧИВЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | 2000 |

|

RU2168855C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех. Достигаемый технический результат - расширение области применения. Устройство для счета импульсов содержит комбинационный сумматор 1, регистр памяти 2, формирователь 3 коэффициента пересчета, инвертор 4, RC-элементы 5-1 ... 5-4 и входную шину 6. Технический результат достигнут введением RC-элементов, формирователя 3, новых связей между функциональными элементами и выполнением каждого разряда регистра памяти 2 в виде тактируемого уровнем одноступенчатого Д-триггера. 5 ил.

Устройство для счета импульсов, содержащее n-разрядный комбинационный сумматор, регистр памяти и инвертор, вход которого соединен с входной шиной устройства, выход - с тактовым входом регистра памяти, отличающееся тем, что в него введены n RC-элементов и формирователь коэффициента пересчета, тактовый вход которого соединен с входной шиной устройства, выходы разрядов - с входами соответствующих разрядов первого слагаемого комбинационного сумматора, а информационные входы - с выходами соответствующих разрядов регистра памяти и с входами соответствующих разрядов второго слагаемого комбинационного сумматора, выходы разрядов которого через соответствующие RC-элементы соединены с информационными входами соответствующих разрядов регистра памяти, каждый из разрядов которого выполнен в виде тактируемого уровнем одноступенчатого Д-триггера.

| БУКРЕЕВ И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Радио и связь, 1990, с | |||

| Приспособление для съемки жилетно-карманным фотографическим аппаратом со штатива | 1921 |

|

SU310A1 |

| Ручной насос для двух жидкостей | 1923 |

|

SU820A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| US 3521036 А, 21.07.1970 | |||

| ЮЗНАЯ .п-г:йГ1<9"Т?ХНЙЧЕ1Нй^|^.^^. | 0 |

|

SU281094A1 |

Авторы

Даты

2000-06-20—Публикация

1997-09-23—Подача