Изобретение относится к области цифровой вычислительной техники и может быть использовано при организации многомашинных комплексов и многопроцессорных систем и для решения задач сопряжения вычислительных машин в сложных многомашинных комплексах, например в узлах связи.

Известно многоканальное устройство для сопряжения вычислительных машин [1] , содержащее две группы каналов, каждый из которых содержит триггер заявок, узел приоритета, коммутатор, дешифратор адреса, элементы ИЛИ, И, НЕ и выходной триггер, в каждом канале выход триггера заявок соединен с входом узла приоритета, выход которого соединен с управляющим входом коммутатора, выходы дешифратора адреса и элемента ИЛИ соединены с входами элемента И, выход которого соединен с первым входом выходного триггера и с входом элемента НЕ, выход которого соединен с вторым входом выходного триггера, управляющие и адресные выходы-входы первой группы каналов соединены с соответствующими управляющими и адресными выходами-входами второй группы каналов.

Признаками, которые совпадают с признаками заявляемого изобретения, являются наличие триггера заявок, узла приоритета, коммутатора, дешифратора адреса, элементов ИЛИ, И, НЕ и выходного триггера, а также наличие сходных информационных связей между группами каналов и коммутатором.

Недостаток этого устройства состоит в больших аппаратурных затратах, которые необходимы для организации двухстороннего обмена в многомашинном комплексе в асинхронном режиме.

Наиболее близким к заявляемому является многоканальное устройство для сопряжения вычислительных машин [2], содержащее две группы, каждая из которых содержит n каналов и два арбитра магистрали, а каждый канал содержит триггер заявок, элемент ИЛИ, два элемента НЕ, три элемента И, коммутатор, дешифратор адреса, выходной триггер, триггер захвата, элемент ИЛИ-НЕ, в каждом канале информационный и стробирующий входы триггера заявок соединены соответственно с входом запроса и первым синхронизирующим входом канала, приоритетный вход канала соединен с первым входом элемента ИЛИ и с входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с выходом запроса канала, первая группа адресных входов канала соединена с входами дешифратора адреса, выход которого соединен с первым входом выходного триггера и с входом второго элемента НЕ, второй синхронизирующий вход канала соединен с управляющим входом дешифратора адреса, вторая группа адресных входов соединена с информационными входами коммутатора, выходы которого соединены с группой выходов канала, выход элемента ИЛИ соединен с приоритетным выходом канала, выходы и входы каждого из арбитров магистрали соединены с соответствующими управляющими входами каналов первой и второй групп.

Общими признаками, которые совпадают с признаками заявляемого изобретения, являются наличие элементов ИЛИ, И, НЕ, триггера заявок, коммутатора, дешифратора адреса, выходного триггера захвата, а также общей коммутационно-приоритетной структуры. Приоритетный вход канала соединен с первым входом элемента ИЛИ и с входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с выходом запроса канала, первая группа адресных входов канала соединена с входами дешифратора адреса, выход которого соединен с первым входом выходного триггера и с входом второго элемента НЕ, второй синхронизирующий вход канала соединен с управляющим входом дешифратора адреса, вторая группа адресных входов соединена с информационными входами коммутатора, выходы которого соединены с группой выходов канала.

Из схемы устройства следует, что недостатком этого устройства являются большие аппаратурные затраты и недостаточное быстродействие из-за усложненной логики управления информационным обменом.

При решении задач сопряжения вычислительных машин в сложных многомашинных комплексах, например в узлах связи, с целью увеличения полезного ресурса ЭВМ при решении специализированных программ одной из основных задач является обеспечение двухстороннего асинхронного обмена между любыми двумя ЭВМ с упрощенной логикой управления их информационного обмена при минимальных затратах на реализацию.

Задачей изобретения является сокращение оборудования устройства и, как следствие, сокращение аппаратурных затрат. В многоканальное устройство для сопряжения вычислительных машин, содержащее группу из N каналов, каждый из которых содержит триггер заявок, элемент ИЛИ, элемент И, коммутатор, дешифратор адреса, введен узел коммутации, а в каждый канал устройства введен дополнительный элемент И, дополнительный элемент ИЛИ и элемент НЕ, при этом узел коммутации содержит триггер заявок, элемент НЕ, два элемента И, коммутатор, дешифратор адреса, в узле коммутации первый вход подтверждения захвата узла коммутации соединен с выходом подтверждения захвата узла коммутации, вход запроса узла коммутации соединен с входом элемента НЕ и с первым входом первого элемента И, выход которого соединен с входом установки в единицу триггера заявок, выход элемента НЕ соединен с входом установки в ноль триггера заявок, инверсный вход которого соединен с первым выходом захвата узла коммутации и с вторым входом первого элемента И, прямой выход триггера заявок соединен с первым входом второго элемента И и с управляющим входом коммутатора, второй вход второго элемента И соединен с вторым входом подтверждения захвата узла коммутации, выход второго элемента И соединен с выходом разрешения обмена узла коммутации, первая группа адресных входов узла коммутации соединена с дешифратором адреса, синхронизирующий вход которого соединен с синхронизирующим входом узла коммутации, выход дешифратора адреса соединен с вторым выходом захвата узла коммутации, вторая группа адресных входов узла коммутации соединена с информационными входами коммутатора, выходы которого соединены с адресными выходами узла коммутации, в каждом канале вход запроса канала соединен с входом элемента НЕ и с первым входом дополнительного элемента И, выход которого соединен с первым входом триггера заявок, выход элемента НЕ соединен с первым входом дополнительного элемента ИЛИ, выход которого соединен с вторым входом триггера заявок, второй вход дополнительного элемента ИЛИ соединен с приоритетным входом канала, инверсный выход триггера заявок соединен с вторым входом дополнительного элемента И, выходы подтверждения захвата каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с вторым входом подтверждения захвата узла коммутации, выход подтверждения захвата узла коммутации соединен с вторым входом подтверждения захвата каждого канала, первые выходы захвата каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с синхронизирующим входом узла коммутации, первый выход захвата узла коммутации соединен с синхронизирующим входом каждого канала, адресные выходы каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с первой группой адресных входов узла коммутации, адресные выходы узла коммутации соединены с первой группой адресных входов каждого канала.

Введенные в изобретение узел коммутации, а также в каждый канал устройства дополнительные элементы И, ИЛИ, НЕ широко известны в вычислительной технике (см., например, В. Г. Лазарев и др. "Проектирование дискретных устройств автоматики". М. : Радио и связь, 1985) и используются по их прямому функциональному назначению.

Однако введенные новые элементы и их связи позволяют получить такой технический результат, как реализация двухстороннего асинхронного обмена между двумя ЭВМ в многоканальной системе с возможностью выбора приоритетных запросов, а также с упрощением логики управления информационным обменом.

Сущность изобретения заключается в том, что за счет введения дополнительных элементов И, ИЛИ, НЕ и новых связей в каждый канал устройства упростилась организация хранения запросов и логика управления триггером захвата и, кроме того, за счет введения узла коммутации упростился алгоритм двустороннего обмена между одним из абонентов, подключенных к каналам, и одним из абонентов, подключенных к узлу коммутации.

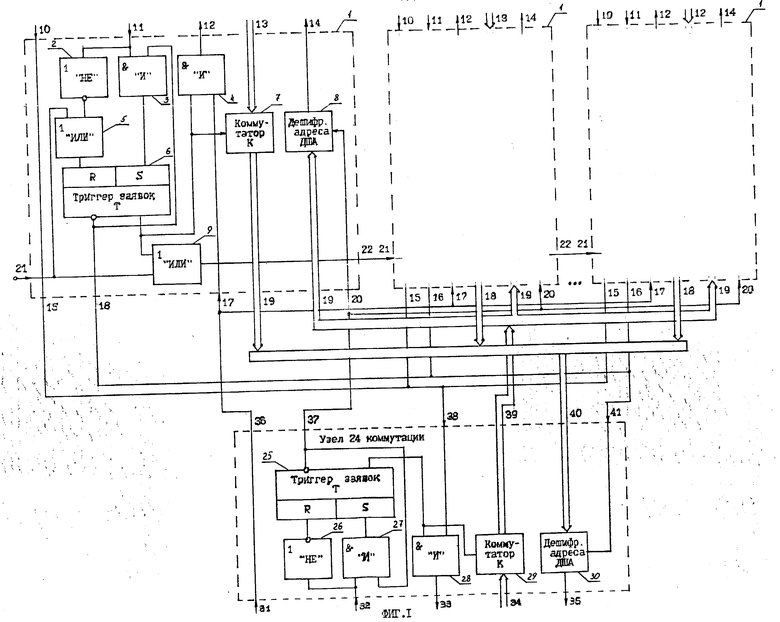

На фиг. 1 представлена функциональная схема устройства.

Устройство содержит каналы 1, каждый из которых включает элемент НЕ 2, элементы И 3,4, элемент ИЛИ 5, триггер заявок 6, коммутатор 7, дешифратор 8 адреса, элемент ИЛИ 9, каждый канал 1 содержит первый вход 10 подтверждения захвата, вход 11 запроса, выход 12 разрешения обмена, вторую группу адресных входов 13, второй выход 14 захвата, выход 15 подтверждения захвата, первый выход 16 захвата, второй вход 17 подтверждения захвата, адресные выходы 18, первую группу адресных входов 19, синхронизирующий вход 20, приоритетный вход 21, приоритетный выход 22, узел 24 коммутации, включающий триггер заявок 25, элемент НЕ 26, элементы И 27,28, коммутатор 29, дешифратор 30 адреса, первый вход 31 подтверждения захвата, вход 32 запроса, выход 33 разрешения обмена, вторую группу адресных входов 34, второй выход 35 захвата, выход 36 подтверждения захвата, первый выход 37 захвата, второй вход 38 подтверждения захвата, адресные выходы 39, первую группу адресных входов 40, синхронизирующий вход 41. Выход 15 подтверждения захвата соединен с вторым входом 38 подтверждения захвата узла 24 коммутации. Первый выход 16 захвата соединен с синхронизирующим входом 41 узла 24 коммутации. Выход 36 подтверждения захвата узла 24 коммутации соединен с вторым входом 17 подтверждения захвата канала 1. Адресные выходы 18 канала 1 соединены с первой группой адресных входов 40 узла 24 коммутации. Адресные выходы 39 узла 24 коммутации соединены с первой группой адресных входов 19 канала 1. Первый выход 37 захвата узла 24 коммутации соединен с синхронизирующим входом 20 канала 1.

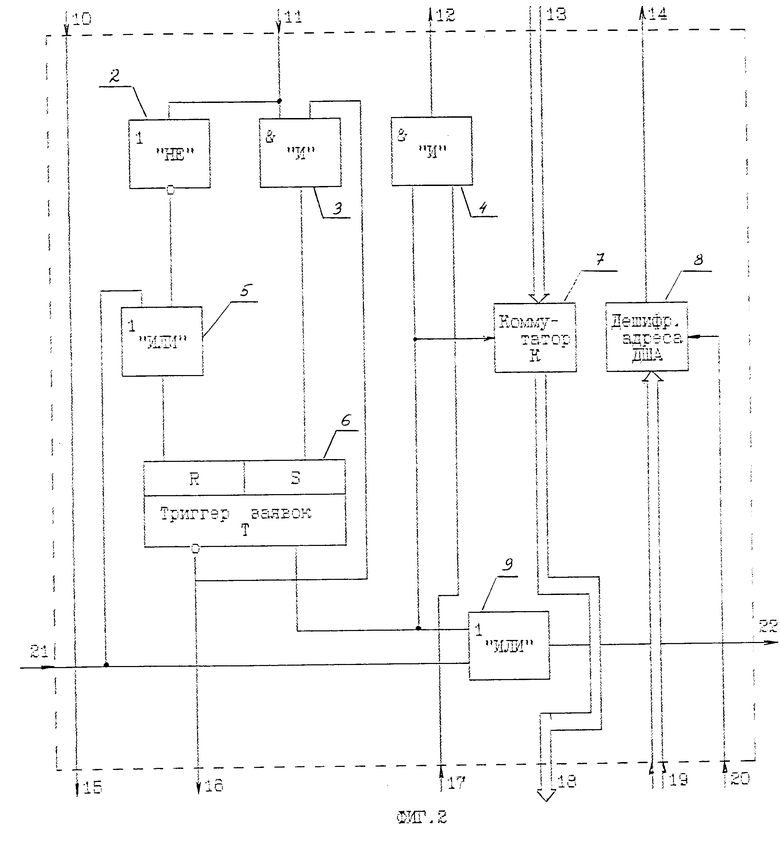

На фиг. 2 представлена функциональная схема канала 1.

В каждом канале выход элемента НЕ 2 соединен с входом элемента ИЛИ 5, выход которого соединен с R-входом триггера заявок 6, а выход элемента И 3 соединен с S-входом триггера 6, единичный выход которого соединен с соответствующим входом элемента ИЛИ 9, входом элемента И 4 и управляющим входом коммутатора 7. Дешифратор адреса 8 соединен по входу с первой группой адресных входов 19 устройства, а по выходу - с выходом 14 захвата устройства. В узле 24 коммутации R-вход триггера 25 соединен с выходом элемента НЕ 26, а S-вход триггера 25 соединен с выходом элемента И 27. Единичный выход триггера 25 соединен с элементом И 28 и с управляющим входом коммутатора 29, вход дешифратора адреса 30 соединен с адресным входом 40 устройства, а выход-с выходом 35 захвата устройства.

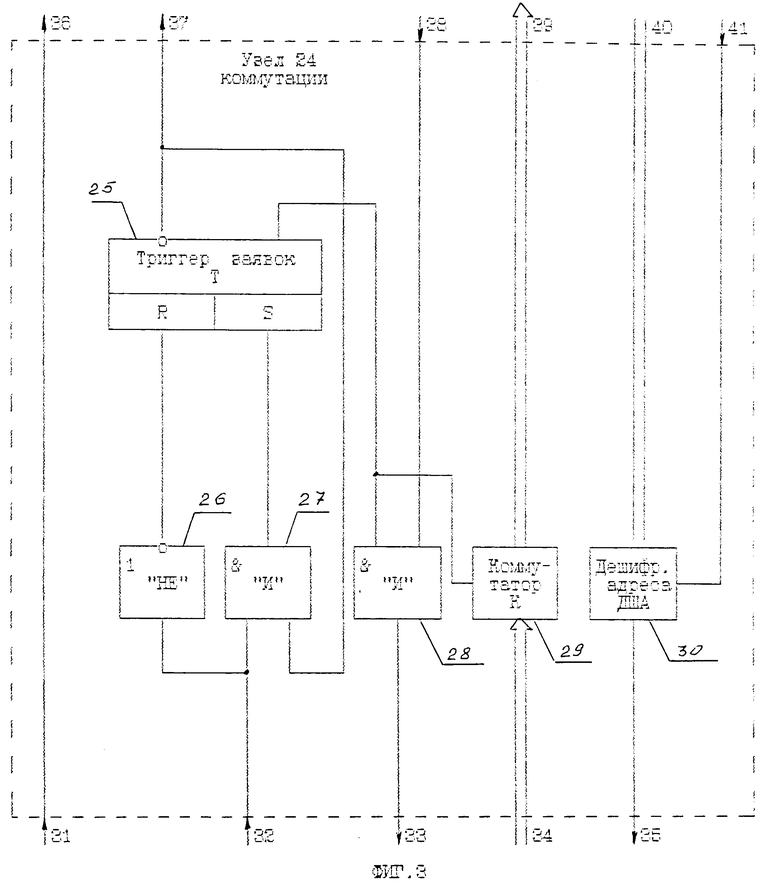

На фиг. 3 представлена функциональная схема узла коммутации.

Устройство содержит включающий триггер заявок 25, элемент НЕ 26, элементы И 27,28, коммутатор 29, дешифратор 30 адреса, первый вход 31 подтверждения захвата, вход 32 запроса, выход 33 разрешения обмена, вторую группу адресных входов 34, второй выход 35 захвата, выход 36 подтверждения захвата, первый выход 37 захвата, второй вход 38 подтверждения захвата, адресные выходы 39, первую группу адресных входов 40, синхронизирующий вход 41.

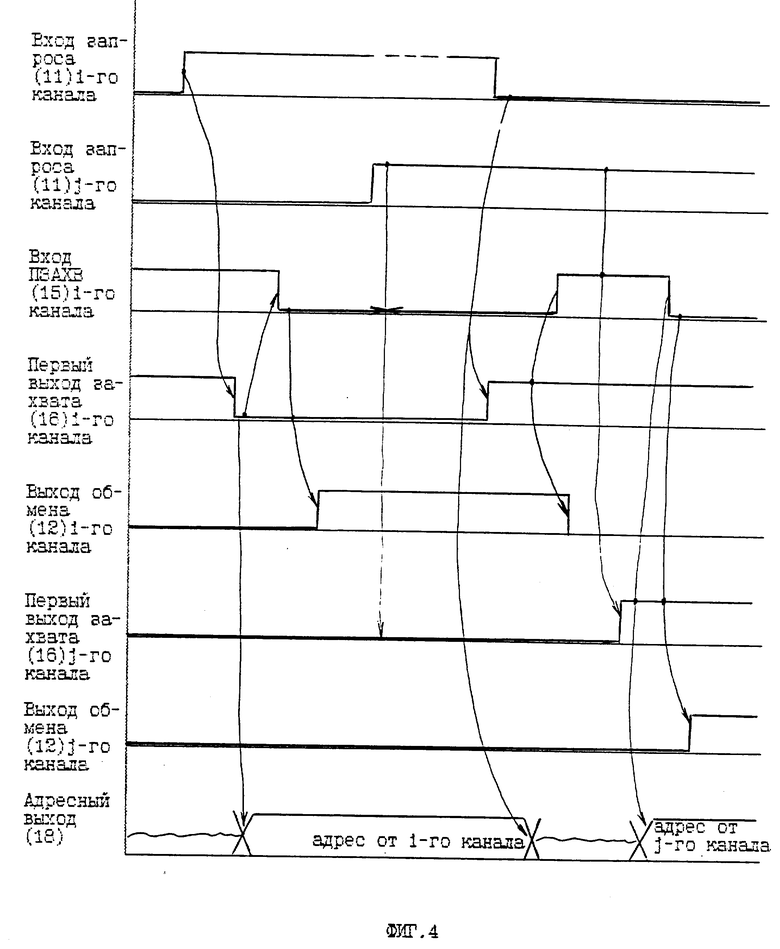

На фиг. 4 представлена временная диаграмма работы устройства.

Абоненты (ЭВМ) подключаются к многоканальному устройству сопряжения через группу входов 10,11,13 и выходов 12,14 и через группу входов 31,32,34 и выходов 33,35.

Устройство работает следующим образом. При работе система, в которую входит устройство, осуществляет обмен между одной из ЭВМ, подключенной к каналу 1, и ЭВМ, подключенной к узлу 24 коммутации. На фиг. 1,2,3 не показаны средства для передачи информационных сигналов. Такими средствами могут быть, например, две коммутируемые системы шин для ЭВМ, способные работать в дуплексе, к которым ЭВМ-источник подключается сигналом с выхода 16 (либо сигналом с выхода 37 для случая передачи информации от узла 24 коммутации в канал 1), а ЭВМ- приемник - сигналом с выхода 14 (либо с выхода 35 для обратной передачи).

В исходном состоянии (нет заявок на входе 11) триггеры 6 находятся в нулевом состоянии. Предположим, что на i-й канал 1 приходит заявка на обмен и устанавливает через элемент И 3 триггер 6 в единицу (см. фиг. 4). При этом единица с выхода триггера 6 канала с более высоким приоритетом через элемент ИЛИ 9 по выходу 22 поступает на один из входов элемента ИЛИ 5 канала с более низким приоритетом. Кроме того, с выхода триггера 6 заявка проходит на выход 16 захвата и управляющий вход коммутатора 7, выходы которого в исходном состоянии отключены от адресных шин 13. Активный сигнал на управляющем входе коммутатора 7 переводит их в режим передачи, т.е. адрес, который поступает с входов 13 через коммутатор 7, передается на выходы 18. Этот адрес далее через адресные шины поступает на вход 40 узла 24 коммутации, а заявка с выхода 16 запрашивающего (i-го) канала 1 поступает на входы 41 узла 24 коммутации. В соответствии с адресом на шинах 19 в узле 24 коммутации срабатывает дешифратор 30 адреса, на выходе которого появляется логическая "1", которая поступает на выход 35 захвата и далее в ЭВМ-приемник. Для организации связи ЭВМ-приемник выставляет сигнал подтверждения захвата, который через вход 31 и выход 36 узла 24 коммутации поступает на вход 17 каждого канала 1 и только в i-ом канале 1 сработает элемент И 4 и сигнал через выход 12 разрешения обмена информирует ЭВМ-источник о готовности обмена.

После окончания сеанса связи ЭВМ-источник снимает запрос с входа 11, при этом триггер 6 устанавливается в ноль, а коммутатор 7 отключает входы 13 от выхода 18.

Если в момент сеанса связи появится запрос на входе 11 в j-ом канале 1, то дальнейшее ее прохождение блокируется управляющим сигналом приоритетного входа 21. После окончания сеанса связи через i-канал 1 прохождение запроса в j-ом канале 1 разблокируется и, если приоритет j-го канала в данный момент выше (или отсутствуют заявки в других каналах 1), то на выходе 16 запроса появится активный сигнал в виде логического "0".

Если в исходном состоянии на два канала 1 приходит одновременно два запроса, то при этом единица с выхода 11 канала 1 с более высоким приоритетом через элемент И 3 устанавливает в единицу триггер 6.

Аналогично ЭВМ, подключенная к узлу 24 коммутации, может выходить с инициативой обмена. Для этого по входу 32 устанавливается запрос на обмен, который устанавливает триггер 25 запроса в активное состояние. Срабатывает коммутатор 29, который подключает входы 34 к выходам 38, и адрес поступает на дешифратор 8 через входы 19. И, как следствие, в выбранном канале 1 с выхода 14 захвата сигнал поступает в ЭВМ- приемник, который формирует сигнал подтверждения захвата, поступающий через вход 10, выход 15 и вход 38 в узел 24 коммутации. На выходе 33 формируется сигнал разрешения обмена, по которому ЭВМ-источник приступает к передаче информации. По завершении обмена срабатывает триггер 25 по входу 32.

Таким образом, устройство позволяет осуществить двухсторонний выбор и обмен между одной из ЭВМ, подключенной к каналу 1, и ЭВМ, подключенной к узлу 24 коммутации.

Коммутационно-приоритетная структура позволяет обеспечить наиболее скоростной обмен важным абонентам или абонентам с частными сообщениями. Этим же достигается снижение количества конфликтных ситуаций и уменьшение очереди ожидания для приоритетных абонентов. На работоспособность и надежность устройства в целом это не влияет, так как используются одни и те же элементы для подключения как приоритетных, так и обычных абонентов.

Реализация предлагаемого устройства в промышленных условиях не вызовет трудностей, так как в схеме используются типовые элементы, выпускаемые серийно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения вычислительных машин | 1986 |

|

SU1322302A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2014732C1 |

| Многоканальное устройство сопряжения вычислительных машин | 1987 |

|

SU1474661A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1985 |

|

SU1312597A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ИНТЕГРАЛЬНОЙ ЦИФРОВОЙ СВЯЗИ | 2000 |

|

RU2188511C2 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для сопряжения телеграфных каналов с электронной вычислительной машиной | 1982 |

|

SU1067494A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано при организации многомашинных комплексов и многопроцессорных систем. Устройство состоит из N каналов, каждый из которых содержит элементы НЕ, два элемента ИЛИ, два элемента И, коммутатор, триггер заявок и дешифратор адреса, узла коммутации, который содержит элемент НЕ, два элемента И, коммутатор, дешифратор адреса и триггер заявок. За счет введения дополнительных элементов И, ИЛИ, НЕ и новых связей в каждый канал устройства упростилась организация хранения запросов и логика управления триггером захвата, что позволило сохранить объем оборудования. 4 ил.

Многоканальное устройство для сопряжения вычислительных машин, содержащее группу из N каналов, каждый из которых содержит триггер заявок, элемент ИЛИ, элемент И, коммутатор, дешифратор адреса, в каждом канале приоритетный вход канала соединен с первым входом элемента ИЛИ, вход которого соединен с приоритетным выходом канала, инверсный выход триггера заявок соединен с первым выходом захвата канала, прямой выход триггера заявок соединен с вторым входом элемента ИЛИ, с первым входом элемента И и с управляющим входом коммутатора, первый вход подтверждения захвата канала соединен с выходом подтверждения захвата канала, второй вход подтверждения захвата канала соединен с вторым входом элемента И, выход которого соединен с выходом разрешения обмена канала, первая группа адресных входов канала соединена с адресными входами дешифратора адреса, управляющий вход которого соединен с синхронизирующим входом канала, выход дешифратора адреса соединен с вторым выходом захвата канала, вторая группа адресных входов канала соединена с информационными входами коммутатора, выходы которого соединены с адресными выходами канала, приоритетный выход каждого канала, кроме последнего, соединен с приоритетным входом последующего канала, приоритетный вход первого канала соединен с логическим нулем устройства, отличающееся тем, что в него введен узел коммутации, а в каждый канал устройства введен дополнительный элемент И, дополнительный элемент ИЛИ и элемент НЕ, при этом узел коммутации содержит триггер заявок, элемент НЕ, два элемента И, коммутатор, дешифратор адреса, в узле коммутации первый вход подтверждения захвата узла коммутации соединен с выходом подтверждения захвата узла коммутации, вход запроса узла коммутации соединен с входом элемента НЕ и с первым входом первого элемента И, выход которого соединен с входом установки в единицу триггера заявок, выход элемента НЕ соединен с входом установки в ноль триггера заявок, инверсный вход которого соединен с первым выходом захвата узла коммутации и с вторым входом первого элемента И, прямой выход триггера заявок соединен с первым входом второго элемента И и с управляющим входом коммутатора, второй вход второго элемента И соединен с вторым входом подтверждения захвата узла коммутации, выход второго элемента И соединен с выходом разрешения обмена узла коммутации, первая группа адресных входов узла коммутации соединена с дешифратором адреса, синхронизирующий вход которого соединен с синхронизирующим входом узла коммутации, выход дешифратора адреса соединен с вторым выходом захвата узла коммутации, вторая группа адресных входов узла коммутации соединена с информационными входами коммутатора, выходы которого соединены с адресными выходами узла коммутации, в каждом канале вход запроса канала соединен с входом элемента НЕ и с первым входом дополнительного элемента И, выход которого соединен с первым входом триггера заявок, выход элемента НЕ соединен с первым входом дополнительного элемента ИЛИ, выход которого соединен с вторым входом триггера заявок, второй вход дополнительного элемента ИЛИ соединен с приоритетным входом канала, инверсный выход триггера заявок соединен с вторым входом дополнительного элемента И, выходы подтверждения захвата каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с вторым входом подтверждения захвата узла коммутации, выход подтверждения захвата узла коммутации соединен с вторым входом подтверждения захвата каждого канала, первые выходы захвата каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с синхронизирующим входом узла коммутации, первый выход захвата узла коммутации соединен с синхронизирующим входом каждого канала, адресные выходы каждого канала объединены по схеме "Монтажное ИЛИ" и соединены с первой группой адресных входов узла коммутации, адресные выходы узла коммутации соединены с первой группой адресных входов каждого канала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1043622, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1322302, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-04-20—Публикация

1995-01-10—Подача