1

jop oTCHHC относится к вычислительной : . I л;ожет быть использовано при по- ij):;;-; ::; ысокопроизводительных вычисли- i .,i;i.; licrt M для организации процедур oopaoDTKi; и обмена информацией между отдельными ЭВМ.

Цель и: ,обрстения - расширение функциональных возможностей вычислительных систем за счет организации конвейерного и циркулярного обмена информацией.

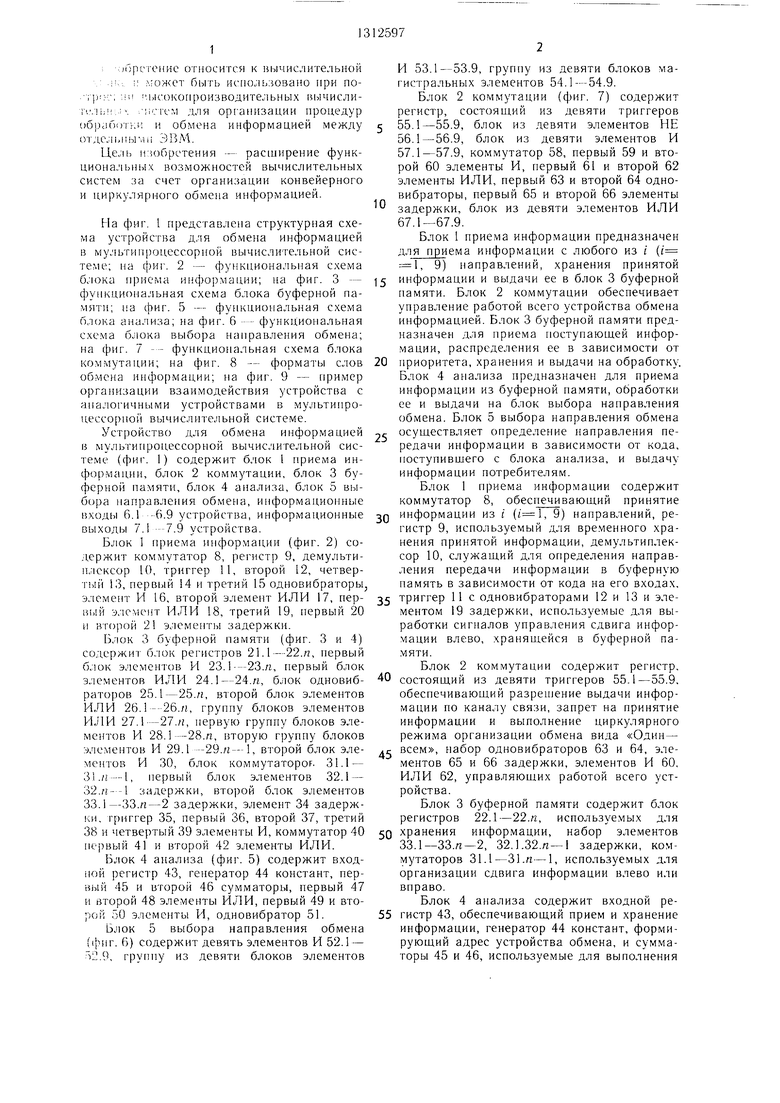

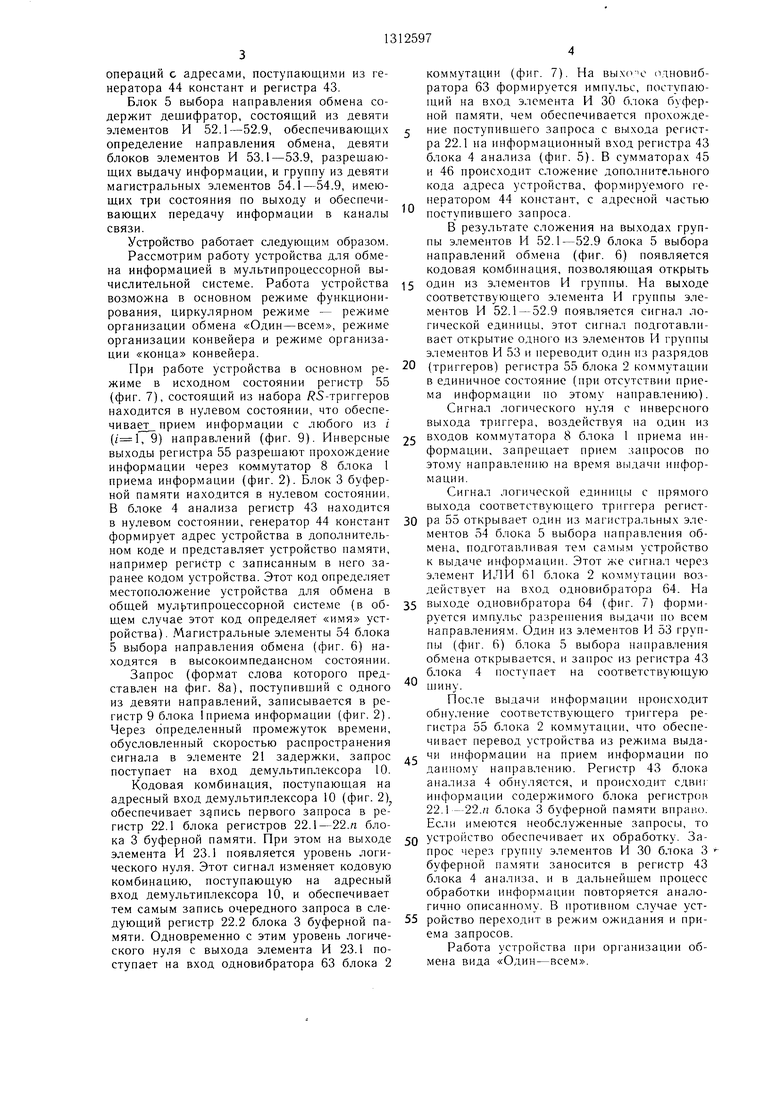

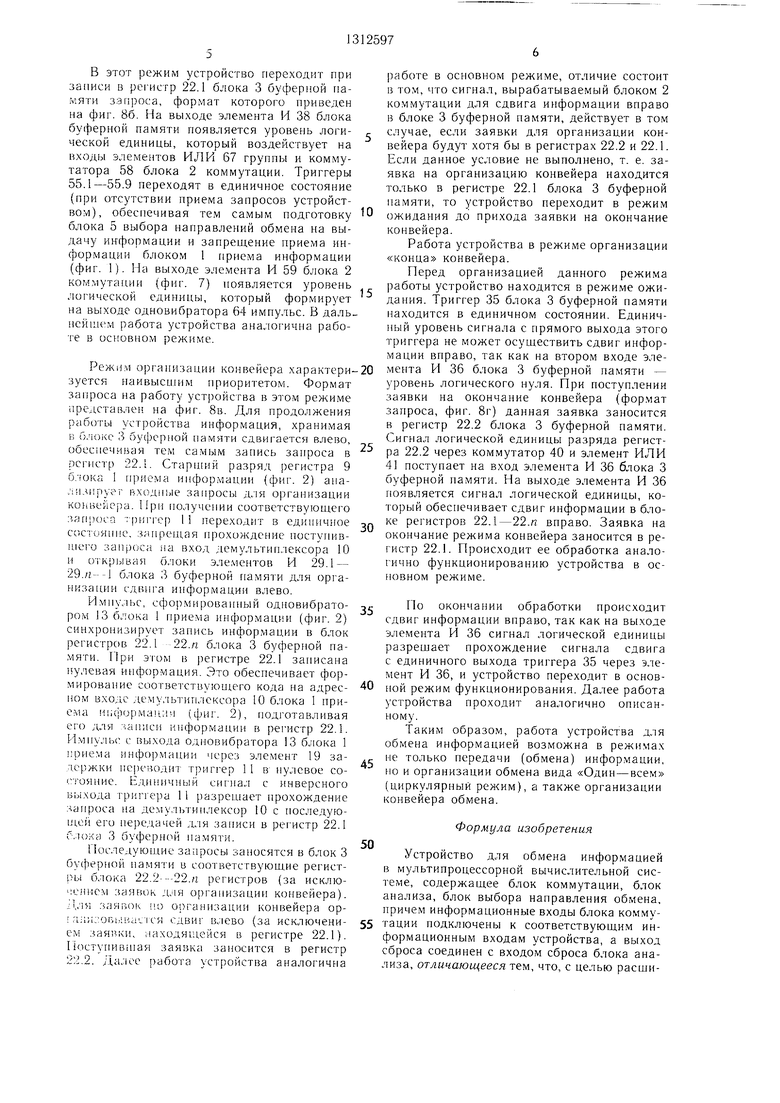

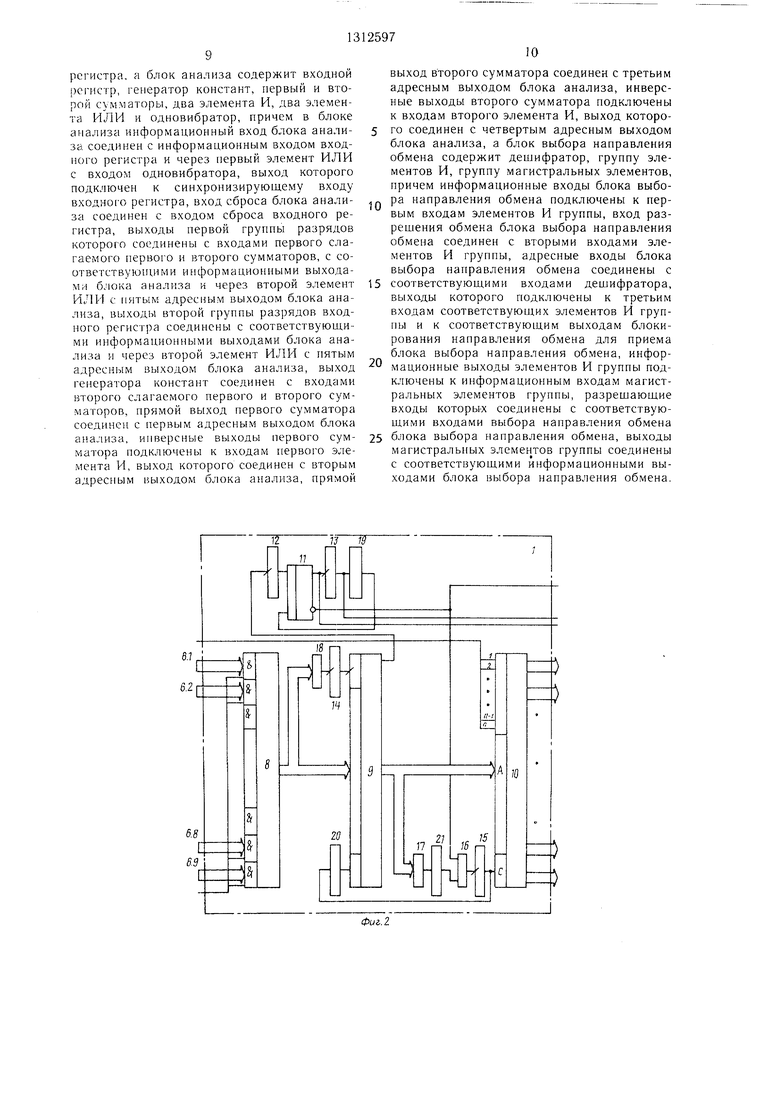

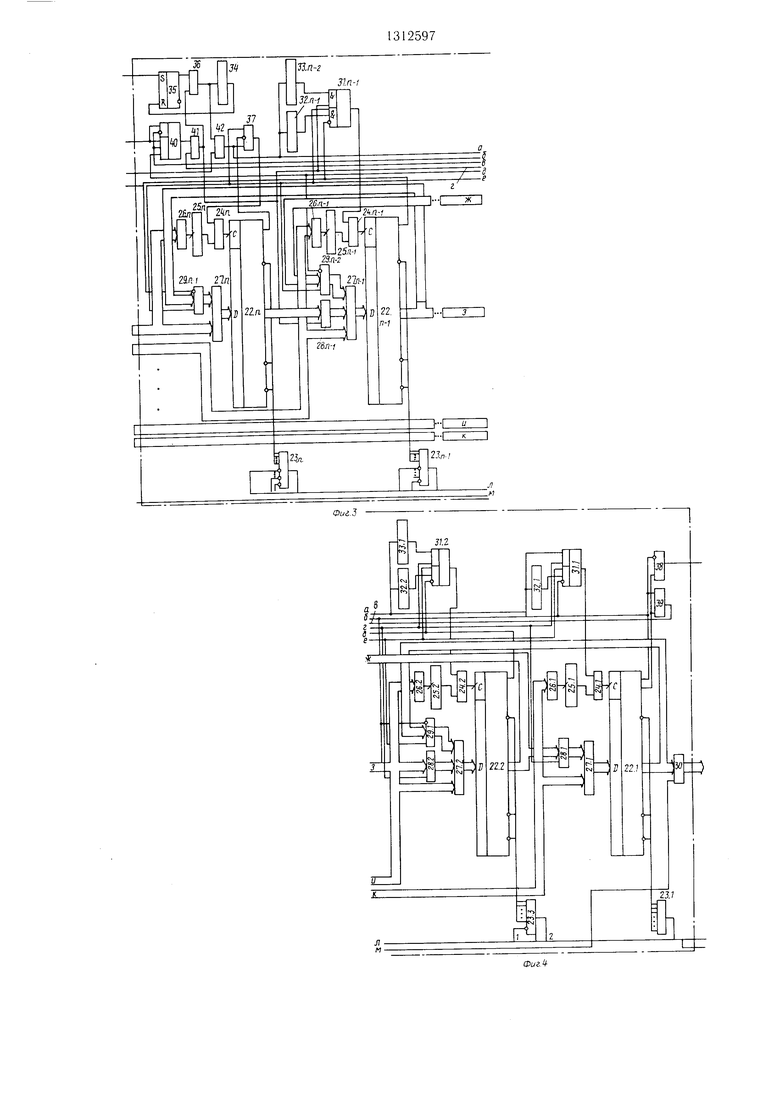

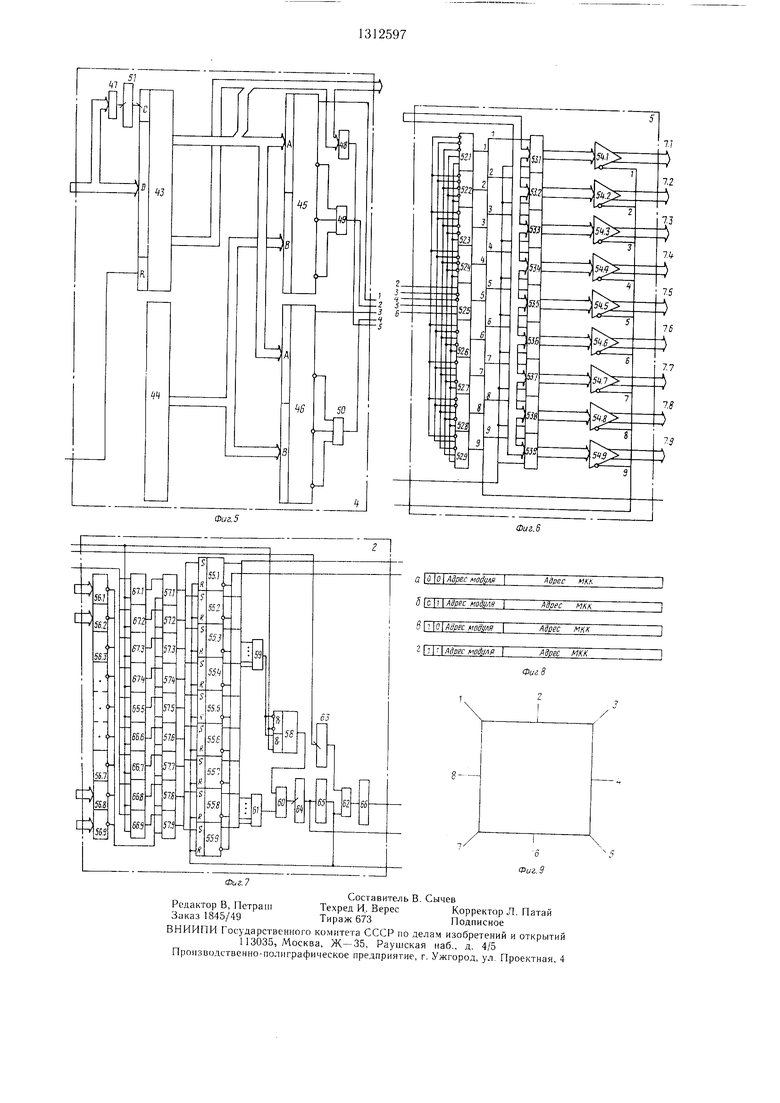

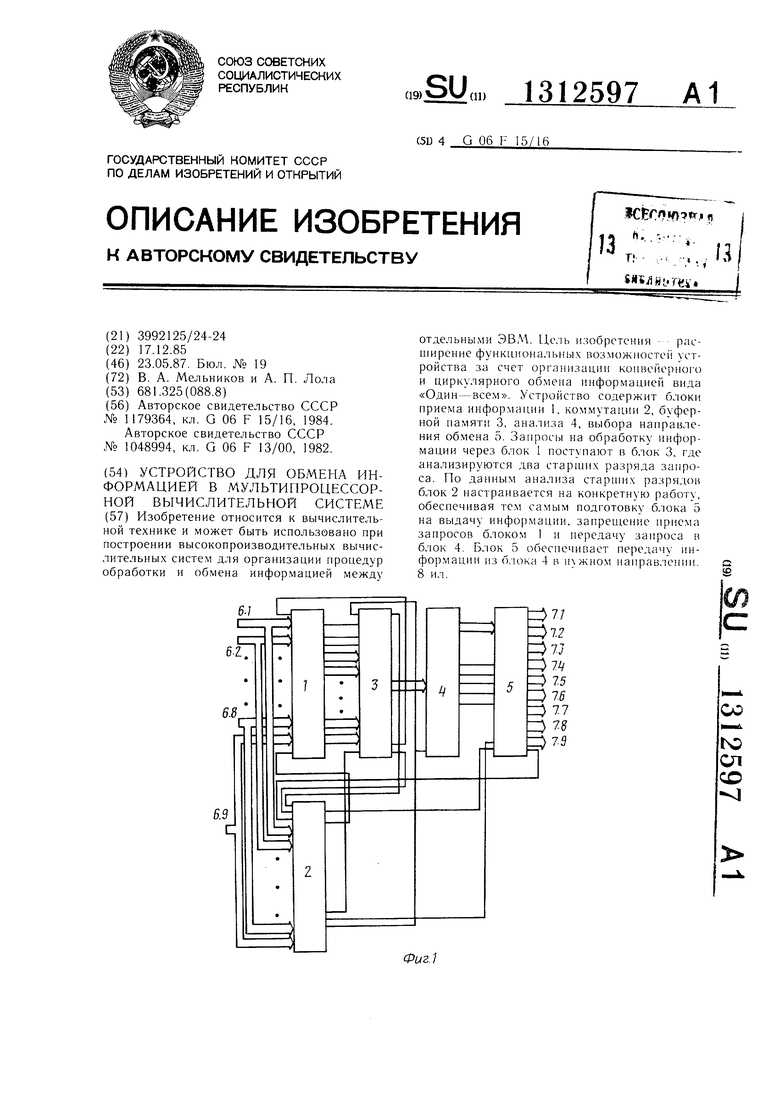

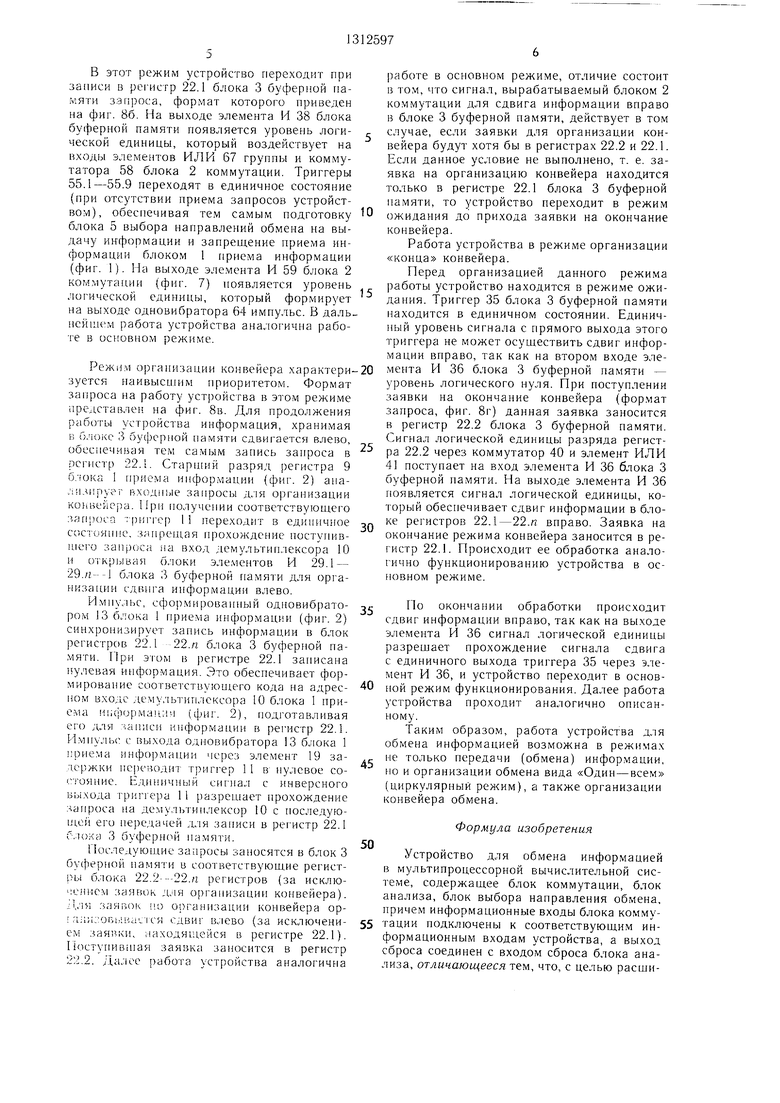

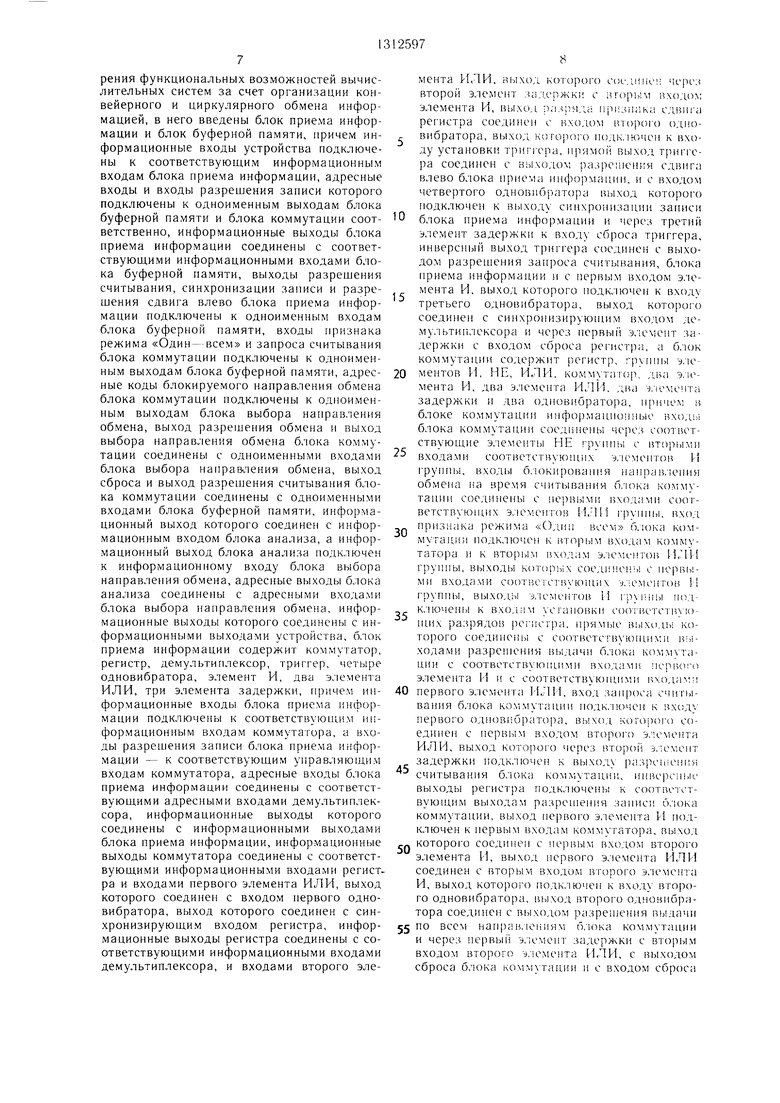

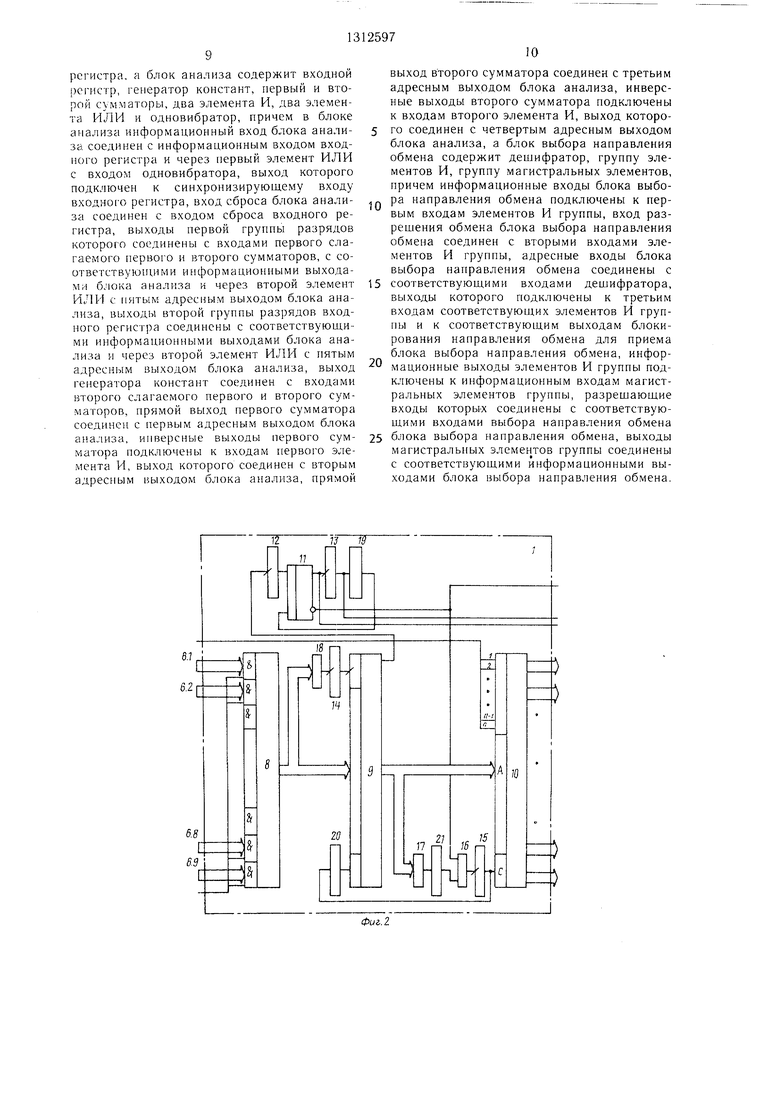

На фиг. 1 нредставлена структурная схема устройства для обмена информацией в мультипроцессорной вычислительной сис- те.ме; на фиг. 2 - функциональная схема блока приема информации; на фиг. 3 - функци(М1альная схема блока буферной памяти; на фиг. 5 - функциональная схема блока анализа; на фиг. 6 - - функциональная схема блока выбора направления об.мена; на ()иг. 7 -- функциональная схема блока коммутации; на фиг. 8 - форматы слов обмена информации; на фиг. 9 - пример организации взаимодействия устройства с аналогичными устройствами в мультипроцессорной вычислительной системе.

Устройство для обмена информацией в мультипроцессорной вычислительной системе (фиг. 1) содержит блок приема информации, блок 2 коммутации, блок 3 буферной намятн, блок 4 анализа, блок 5 выбора направления обмена, информационные входы 6.1-6.9 устройства, инс|)ормационные выходы 7.1 7.9 устройства.

Блок 1 приема информации (фиг. 2) со- .аержит коммутатор 8, регистр 9, демульти- п,;1ексор И), триггер 11, второй 12, четвертый 13, первый 14 и третий 15 одновибраторы, элемент И 16, второй элемент ИЛИ 17, первый элемент ИЛИ 18, третий 19, первый 20 и второй 21 элементы задержки.

Блок 3 буферной памяти (фиг. 3 и 4) содержит блок регистров 21.1-22.л, первый блок элементов И 23.1--23.п, первый блок элементов ИЛИ 24.1-24.п, блок одновиб- раторов 25.1-25.п, второй блок элементов ИЛИ 26.1-26./, группу блоков элементов ИЛИ 27.1-27.п, первую группу блоков элементов И 28.1 --28.п, вторую группу блоков элементов И 29.1 -29./г- 1, второй блок элементов И 30, блок коммутаторор. 31.1 - 31./i-1, первый блок элементов 32.1 - 32.--1 задержки, второй блок элементов 33.1-33.п-2 задержки, элемент 34 задержки, григгер 35, первый 36, второй 37, третий 38 и четвертый 39 элементы И, коммутатор 40 нервый 41 и второй 42 элементы ИЛИ.

Блок 4 анализа (фиг. 5) содержит входной регистр 43, генератор 44 констант, первый 45 и второй 46 сумматоры, первый 47 и второй 48 элементы ИЛИ, первый 49 и второй 50 элементы И, одновибратор 51.

Блок 5 выбора направления обмена (. 6) содержит девять элементов И 52.1 - о2.9, группу из девяти блоков элементов

5

И 53.1-53.9, группу из девяти блоков магистральных элементов 54.1-54.9.

Б. юк 2 коммутации (фиг. 7) содержит регистр, состоянхий из девяти триггеров

55.1-55.9, блок из девяти элементов НЕ 56.1-56.9, блок из девяти элементов И 57.1-57.9, коммутатор 58, первый 59 и второй 60 элементы И, первый 61 и второй 62 элементы ИЛИ, первый 63 и второй 64 одно- вибраторы, первый 65 и второй 66 элементы

задержки, блок из девяти элементов ИЛИ 67.1-67.9.

Блок 1 приема информации предназначен для приема информации с любого из i (i 1, 9) направлений, хранения принятой

информации и выдачи ее в блок 3 буферной намяти. Блок 2 коммутации обеспечивает управление работой всего устройства обмена информацией. Е)лок 3 буферной памяти предназначен для нриема поступающей информации, распределения ее в зависимости от

0 приоритета, хранения и выдачи на обработку. Блок 4 анализа предназначен для приема информации из буферной намяти, обработки ее и выдачи на блок выбора направления обмена. Блок 5 выбора направления обмена осуществляет определение направления передачи информации в зависимости от кода, поступившего с блока анализа, и выдачу информации потребителям.

Блок 1 приема информации содержит коммутатор 8, обеспечивающий принятие

Q информации из i (, 9) направлений, регистр 9, используемый для временного хранения принятой информации, демультиплек- сор 10, служащий для определения направления передачи информации в буферную память в зависимости от кода на его входах,

5 триггер 11 с одновибраторами 12 и 13 и элементом 19 задержки, используемые для выработки сиг}1алов управления сдвига информации влево, хранящейся в буферной памяти.

Блок 2 коммутации содержит регистр, состоящий из девяти триггеров 55.1-55.9. обеспечивающий разре1пение выдачи информации по каналу связи, запрет на принятие информации и выполнение циркулярного режима организации обмена вида «Один-

г всем, набор одновибраторов 63 и 64, элементов 65 и 66 задержки, элементов И 60. ИЛИ 62, управляющих работой всего устройства.

Блок 3 буферной памяти содержит блок регистров 22.1-22.л, используе.мых для

0 хранения информации, набор элементов 33.1-33.л-2, 32.1.32.л-1 задержки, коммутаторов 31.1-31.П-1, используемых для организации сдвига информации влево или вправо.

Блок 4 анализа содержит входной ре5 гистр 43, обеспечивающий прием и хранение информации, генератор 44 констант, формирующий адрес устройства обмена, и сумматоры 45 и 46, используемые для выполнения

0

операций с адресами, поступающими из генератора 44 констант и регистра 43.

Блок 5 выбора направления обмена содержит дешифратор, состоящий из девяти элементов И 52.1-52.9, обеспечивающих определение направления обмена, девяти блоков элементов И 53.1-53.9, разрешающих выдачу информации, и группу из девяти магистральных элементов 54.1-54.9, имеющих три состояния по выходу и обеспечивающих передачу информации в каналы связи.

Устройство работает следующим образом.

Рассмотрим работу устройства для обмена информацией в мультипроцессорной вычислительной системе. Работа устройства возможна в основном режиме функционирования, циркулярном режиме - режиме организации обмена «Один - всем, режиме организации конвейера и режиме организации «конца конвейера.

При работе устройства в основном режиме в исходном состоянии регистр 55 (фиг. 7), состоящий из набора / 5-триггеров находится в нулевом состоянии, что обеспечивает прием информации с любого из / (, 9) направлений (фиг. 9). Инверсные выходы регистра 55 разрешают прохождение информации через коммутатор 8 блока 1 приема информации (фиг. 2). Блок 3 буферной памяти находится в нулевом состоянии. В блоке 4 анализа регистр 43 находится в нулевом состоянии, генератор 44 констант формирует адрес устройства в дополнительном коде и представляет устройство памяти, например регистр с записанным в него заранее кодом устройства. Этот код определяет местоположение устройства для обмена в общей мулртипроцессорной системе (в общем случае этот код определяет «имя устройства). Магистральные элементы 54 блока 5 выбора направления обмена (фиг. 6) находятся в высокоимпедансном состоянии.

Запрос (формат слова которого представлен на фиг. 8а), поступивший с одного из девяти направлений, записывается в регистр 9 блока 1 приема информации (фиг. 2). Через определенный промежуток времени, обусловленный скоростью распространения сигнала в элементе 21 задержки, запрос поступает на вход демультиплексора 10.

Кодовая комбинация, поступающая на адресный вход демультиплексора 10 (фиг. 2) обеспечивает запись первого запроса в регистр 22.1 блока регистров 22.1-22.л блока 3 буферной памяти. При этом на выходе элемента И 23.1 появляется уровень логического нуля. Этот сигнал изменяет кодовую комбинацию, поступающую на адресный вход демультиплексора 10, и обеспечивает тем самым запись очередного запроса в следующий регистр 22.2 блока 3 буферной памяти. Одновременно с этим уровень логического нуля с выхода элемента И 23.1 поступает на вход одновибратора 63 блока 2

0

коммутации (ф)1г. 7). На вы. (хановпб- ратора 63 формируется импульс, поступающий на вход элемента И 30 блока буферной памяти, чем обеспечивается прохождение поступившего запроса с выхода регистра 22.1 на информационный вход регистра 43 блока 4 анализа (фиг. 5). В сумматорах 45 и 46 происходит сложение дополнительного кода адреса устройства, формируемого генератором 44 констант, с адресной частью поступившего запроса.

В результате сложения на выходах группы элементов И 52.1-52.9 блока 5 выбора направлений обмена (фиг. 6) появляется кодовая комбинация, позволяющая открыть

5 один из элементов И группы. На выходе соответствующего элемента И группы элементов И 52.1 - 52.9 появляется сигнал логической единицы, этот сигнал подготавливает открытие одного из элементов И группы элементов И 53 и переводит один из разрядов

0 (триггеров) регистра 55 блока 2 коммутации в единичное состояние (при отсутствии приема информации по этому направлению). Сигнал логического нуля с инверсного выхода триггера, воздействуя на один из

5 входов коммутатора 8 блока 1 приема информации, запрещает прием запросов по этому направлению на время В1 1дачи информации.

Сигнал логической единит с прямого выхода соответствующего триггера регист0 ра 55 открывает один из магистральных элементов 54 блока 5 выбора направления обмена, подготавливая тем самым устройство к выдаче информации. Этот же сигна.м через элемент ИЛИ 61 блока 2 коммутации воздействует на вход одновибратора 64. На

5 выходе одновибратора 64 (фиг. 7) формируется импульс разрешения выдачи по всем направлениям. Один из элементов И 53 группы (фиг. 6) блока 5 выбора направления обмена открывается, и запрос из регистра 43 блока 4 поступает на соответствующую шину.

После выдачи информации происходит обнуление соответствующего триггера регистра 55 блока 2 коммутации, что обеспечивает перевод устройства из режима выдас чи информации на прием информации по данному направлению. Регистр 43 блока анализа 4 обнуляется, и происходит сдви информации содержимого блока регистров 22.1 --22./7 блока 3 буферной памяти впрано. Если имеются необслуженные запросы, то

0 устройство обеспечивает их обработку. Запрос через группу элементов И 30 блока 3 буферной памяти заносится в регистр 43 блока 4 анализа, и в дальнейшем процесс обработки информации повторяется аналогично описанному. В противном случае уст5 ройство переходит в режим ожидания и приема запросов.

Работа устройства при организации обмена вида «Один-всем.

0

В этот режим устройство переходит при записи в регистр 22.1 блока 3 буферной памяти запроса, формат которого приведен па фиг. 86. На выходе элемента И 38 блока буферной памяти появляется уровень логической единицы, который воздействует на входы элементов ИЛИ 67 группы и коммутатора 58 блока 2 коммутации. Триггеры 55.1-55.9 переходят в единичное состояние (при отсутствии приема запросов устройством), обеспечивая те.м самым подготовку блока 5 выбора направлений обмена на выдачу информации и запрещение приема информации блоком 1 приема информации (фиг. 1). На выходе элемента И 59 блока 2 коммутации (фиг. 7) появляется уровень логической единицы, который формирует на выходе одновибратора 64 импульс. В даль, пейшем работа устройства аналогична работе в основном режиме.

Г еж11;М организации конвейера характеризуется наивысшим приоритетом. Формат запроса на работу устройства в этом режи.ме представлен на фиг. 8в. Для продолжения работы устройства информация, хранимая в б.чокс 3 бус)српой памяти сдвигается влево, обеспечивая тем самым запись занроса в регистр 22.1. Старший разряд регистра 9 б.юка 1 приема информации (фиг. 2) апа- лизируег входные запросы д.чя организации конвейера. При получении соответствующего : ,япросз : |И ггер I i переходит в единичное состояние, запрещая ирохождепие поступившего зап)оса на вход демультиплексора 10 и откр1 1вая блоки элементов И 29.1 - 29./г-- блока 3 буферной памяти для организации сдвига информации влево.

Импульс, сформированпый одно вибратором 13 блока 1 приема )ормации (фиг. 2) синхронизирует занись информации в блок регистров 22.1 22.я блока 3 буферной памяти. При этом в регистре 22.1 записапа нулевая информация. Это обеспечивает формирование соответствующего кода на адресном входе демультиплексора 10 б,лока 1 приема ипформацли (фиг. 2), подготавливая его ;1ля чаписп информации в pei HCTp 22.1. Импульс- с выхода одновибратора 13 блока 1 приема информации через эле.мент 19 за- п,ержки нс) триггер 1 1 в нулевое состояние. Единичный сиг на; с инверсного выхода триггера 11 разрешает нрохождение запроса на демул1 тинлексор 10 с носледую- пи;й его передачей для записи в рег истр 22.1 г.юка 3 буферн(1Й на.мяти.

Последующие запросы заносятся в блок 3 бу()1ерной намяти в соответствующие регист- Р Ы блока 22.2--22./I регистров (за исключением заявок для орг апизации конвейера). il. iVi заявок 1о органнзацип конвейера ор- i а;;;и:ог,;;1иа 1 ся сдвиг в;1ево (за исключением заявки, находящейся в регистре 22.1). заявка заносится в регистр . Далее работа устройства аналогична

работе в основном режиме, отличие состоит в том, что сигнал, вырабать ваемый блоком 2 коммутации для сдвига информации вправо в блоке 3 буферной памяти, действует в том случае, если заявки для организации конвейера будут хотя бы в регистрах 22.2 и 22.1. Если данное условие не выполнено, т. е. заявка на организацию конвейера находится только в регистре 22.1 блока 3 буферной памяти, то устройство переходит в режим

О ожидания до прихода заявки на окончание конвейера.

Работа устройства в режиме организации «конца конвейера.

Иеред организацией данного режима работы устройство находится в режиме ожидания. Триггер 35 блока 3 буферной памяти находится в единичном состоянии. Единич- Щз1Й уровень сигнала с прямого выхода этого триггера не может осуществить сдвиг информации внраво, так как на втором входе эле0 мента И 36 блока 3 буферной памяти - уровень логического нуля. При поступлении заявки на окончание конвейера (формат занроса, фиг. 8г) данная заявка заносится в регистр 22.2 блока 3 буферной памяти. Сигнал логической единицы разряда регист5 ра 22.2 через коммутатор 40 и элемент ИЛИ 41 поступает на вход элемента И 36 блока 3 буферной намяти. На выходе элемента И 36 появляется сигнал логической единицы, который обеспечивает сдвиг информации в блоке регистров 22.1-22.« вправо. Заявка на окончание режима конвейера заносится в регистр 22.1. Происходит ее обработка аналогично функционированию устройства в основном режиме.

о,- По окончании обработки происходит сдвиг информации вправо, так как на выходе элемента И 36 сигнал логической единиць разрешает прохождение сигнала сдвига с единичного выхода триггера 35 через элемент И 36, и устройство переходит в основ40 ной режим функционирования. Далее работа устройства проходит аналогично описанному.

Таким образом, работа устройства для обмена информацией возможна в режимах не только передачи (обмена) инфор.мации, но и организации обмена вида «Один - всем (циркулярный режим), а также организации конвейера обмена.

45

Формула изобретения

Устройство для обмена информацией в мультипроцессорной вычислительной системе, содержащее блок коммутации, блок анализа, блок выбора направления обмена, причем информационные входы блока комму- тации нодключены к соответствующим информационным входам устройства, а выход сброса соединен с входом сброса блока анализа, отличающееся тем, что, с целью расщирения функциональных возможностей вычислительных систем за счет организации конвейерного и циркулярного обмена информацией, в него введены блок приема информации и блок буферной памяти, причем информационные входы устройства подключены к соответствующим информационным входам блока приема информации, адресные входы и входы разрешения записи которого подключены к одноименным выходам блока буферной памяти и блока коммутации соответственно, информационные выходы блока приема информации соединены с соответствующими информационными входами блока буферной памяти, выходы разрешения считывания, синхронизации записи и разрешения сдвига влево блока приема информации подключены к одноименным входам блока буферной памяти, входы признака режима «Один - всем и запроса считывания блока коммутации подключены к одноименным выходам блока буферной памяти, адресные коды блокируемого направления обмена блока коммутации подключены к одноименным выходам блока выбора направления обмена, выход разрешения обмена и выход выбора направления обмена блока коммутации соединены с одноименными входами блока выбора нанрав-ления обмена, выход сброса и выход разрешения считывания блока коммутации соединены с одноименными входами блока буферной памяти, информационный выход которого соединен с информационным входом блока анализа, а информационный выход блока анализа подключен к информационному входу блока выбора нанравления обмена, адресные выходы блока анализа соединены с адресными входами блока выбора направления обмена, информационные выходы которого соединены с информационными выходами устройства, блок приема информации содержит коммутатор, регистр, демультиплексор, триггер, четыре одновибратора, элемент И, два элемента ИЛИ, три элемента задержки, причем информационные входы блока приема информации подключены к соответствующим информационным входам коммутатора, а входы разрешения записи блока приема информации - к соответствующим управляюп им входам коммутатора, адресные входы блока приема информации соединены с соответст- вующ,ими адресными входами демультиплек- сора, информационные выходы которого соединены с информационными выходами блока приема информации, информационные выходы коммутатора соединены с соответствующими информационными входами регистра и входами первого элемента ИЛИ, выход которого соединен с входом нервого одно- вибратора, выход которого соединен с синхронизирующим входом регистра, информационные выходы регистра соединены с соответствующими информационными входами демультиплексора, и входами второго эле

0

5

0

5

0

5

50

55

мента ИЛИ, выход KOTopoi-o cotMHiioi-: через второй элемент Зол.ержки с входом элемента И, выход г чл-ря/и: признг.ка сд15М|-а регистра соединен с входом inopoix) одно- вибратора, выхо;; кого|10 -о нодк,1ючен к входу установки трип сра, н(1ямо11 триггера соединен с выxoдo l разрешения сдвига влево блока приема информации, и с входом четвертого одновиб)атора выход которого подключен к В1 1ходу синхронизации записи блока приема информации и через третий элемент задержки к входу сброса триггера, инверсный выход триггера соединен с выходом разрешения запроса считывания, блока приема информации и с первым входом э.че- мента И, выход которого подключен к входу третьего одновибратора, выход которого соединен с синхронизирующим входом демультиплексора и через нервьн э, задержки с входом сброса регистра, а блок коммутации содержит регистр, групшя э.ю- ментов И, НЕ, ИЛИ, комм тагор. jiia э.и - мента И, два элемента ИЛИ. два чломсчта задержки и два одновибратора, причел; и блоке коммутации инфо|)мацпо 1ныо входы блока коммутации соединепы через соответствующие элемент) ИЕ с )

входами соответстную и х э. И

ГруНП 1, входы бЛОК 1рОВа Н Я .

обмена )а время считыва 1ия б, соед 1нень с ход;п и соот- ветствук)н.нх элеме ггов I-IJIII , вход признака режима «();iiiii всем б.кжа ком- мута и1 -| подключе к (тор)1М вxoдa к() татора к втор)1м ходам э, ИЛИ

, ВЫХОД) KOTOpliiX СОеД НОНЫ О пер 5Ыми входами cooTi5eTCTii iHiiix ;..емьмпч)в

, В) элементов И -p l;ilb НОД- К. ИОЧе)) к входим COOTiH TCT fyiO цих разрядо нл исгри, В1 1холь которого соединены с соответсг уюп п ;и )ы- ходам 1 разрешен 1Я В)1дачи б/кж;; к( с cooTBeTCTByiO uiiM i входами iicpiuird элеме 1та 1-i с соответствук) i xexuiN;;: первого элемента ИЛИ, вход блока коммута 1И11 :одкл очеп к вх( нервого од 1ов1 братора, выход когорО Ч) ссь с ,М входом второго элехкчп я ИЛИ, которого через BTopoii элемент задержки подключен к выходу iKKVpcnieMiisi

СЧИТЫВаН 1Я блока КОМЛ5ута иП, HI epCiil,k

выход регистра подключен к соотве 1Ч т- выходам разре1 ен я ол.ока коммута 1.ии, выход нервого элеме1 та И 1од- ключен к входам ком% утатора, В з1ход которого с пер)м входом вторО Ч) элемента И, выход ервого элеме1 та ИЛИ соединен с втор)м входом второго элемента И, выход KOTOpOi O подключен к входу второго одновибратора, В)1ход второго одновибра- тора соеди ен с вь ходом разре ения в)дачи по веем )ав.ениям блока коммутгщии и через нервьн задержки с входом второго ИЛИ, с выходом сброса блока коммутации i с входом сброса

регистра, а блок анализа содержит входной |)егистр, генератор констант, первый и второй сумматоры, два элемента И, два элемента ИЛИ и одновибратор, причем в блоке анализа информационный вход блока анализа соединен с информационным входом входного регистра и через первый элемент ИЛИ с входом одновибратора, выход которого подключен к синхронизирующему входу входного регистра, вход сброса блока анализа соединен с входом сброса входного регистра, выходы первой группы разрядов которого соединены с входами первого слагаемого первого и второго сумматоров, с соответствующими информационными выходами блока анализа и через второй элемент ИЛИ с пятым адресным выходом блока анализа, выходы второй группы разрядов входного регистра соединены с соответствующими информационными выходами блока анализа и через второй элемент ИЛИ с пятым адресным выходом блока анализа, выход генератора констант соединен с входами второго слагаемого первого и второго сумматоров, прямой выход первого сумматора соединен с тервым адресным выходом блока анализа, инверсные выходы первого сумматора подключены к входам первого элемента И, выход которого соединен с вторым адресным выходом блока анализа, прямой

выход второго сумматора соединен с третьим адресным выходом блока анализа, инверсные выходы второго сумматора подключены к входам второго элемента И, выход которого соединен с четвертым адресным выходом блока анализа, а блок выбора направления обмена содержит дешифратор, группу элементов И, группу магистральных элементов, причем информационные входы блока выбоQ ра направления обмена подключены к первым входам элементов И группы, вход разрешения обмена блока выбора направления обмена соединен с вторыми входами элементов И группы, адресные входы блока выбора направления обмена соединены с

5 соответствующими входами дешифратора, выходы которого подключены к третьим входам соответствуюидих элементов И группы и к соответствующим выходам блокирования направления обмена для приема блока выбора направления обмена, инфор мационные выходы элементов И группы подключены к информационным входам магистральных элементов группы, разрешающие входы которы-х соединены с соответствующими входами выбора направления обмена

5 блока выбора направления обмена, выходы магистральных элементов группы соединены с соответствующими информационными выходами блока выбора направления обмена.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для организации процедур обработки и обмена инфор.мацией между отдельными ЭВМ. Ц,ель изобретения - расширение функциональны.х возможностей устройства за счет организации конвейерного и циркулярного обмена информацией вида «Один-всем. Устройство содержит блоки приема иифор.мации 1, коммутации 2, буферной памяти 3, анализа 4, выбора направления обмена 5. Запросы на обработку информации через блок 1 поступают в блок 3, где анализируются два CTapHjnx разряда запроса. Но данным анализа старнн1х разрядов блок 2 настраивается на конкретную работу, обеспечивая тем самым подготовку блока 5 на выдачу информации, запрещение приема запросов блоком 1 и передачу запроса в блок 4. Блок 5 обеспечивает передачу информации из б. юка 4 в нанрав.мении. 8 ил. о S СО «i N5 СП СО -vl

В

to

Ф(уг.5

Фиг. 8

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электрохромное устройство | 1978 |

|

SU1048994A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1985-12-17—Подача