Изобретение относится к вычислительной технике и может использоваться в системах обмена информацией, результатами счета между несколькими ЭВМ и внешними устройствами.

Известно устройство для обмена информацией, содержащее блок синхронизации, выходы которого соединены с первыми входами блоков подключения последовательных каналов, блока приоритета, блок буферной памяти, блока узлов регистров каналов, блока поиска свободных зон, блока отсчета времени и блока управления, соединенного группой входов-выходов соответственно с входами-выходами буферной памяти, блока узлов регистров каналов, блока поиска свободных зон, блока отсчета времени, блока подключения последовательных каналов, и блоки подключения параллельных каналов и выходом блока приоритета, входы запросов которого подсоединены к выходу блока отсчета времени, выходам подключения последовательных и параллельных каналов, соединенных информационными входами-выходами с входами-выходами блока узлов регистрации каналов, который соединен двусторонними связями с блоком поиска свободных зон и блоком буферной памяти [1].

Недостатком этого устройства является ограниченная область применения из-за того, что устройство не обеспечивает оперативной передачи ЭВМ, подключенной к одному из параллельных каналов устройства обмена, информации в соответствии с ее приоритетом и информации, состоящей из нескольких сообщений. Кроме того, время занятия зоны жестко фиксировано, и это приводит к необходимости часто повторять ввод сообщений в ЭВМ.

Наиболее близким по технической сущности к предлагаемому устройству является многоканальный коммутатор, содержащий линии связи, каждая из которых соединена с первым входом соответствующего блока приемопередатчика, демультиплексор, первый мультиплексор, счетчик, генератор, блок сравнения, пространственный коммутатор, М дополнительных мультиплексоров, М блоков обмена информации, блок анализа, адресный коммутатор, М регистров, блок управления регистрации ключей, М блоков индикации [2].

Недостатком этого коммутатора является низкая скорость обмена информацией и малое быстродействие коммутатора из-за синхронного режима работы блоков устройства.

Цель изобретения - повышение скорости обмена информации.

Это достигается благодаря использованию асинхронного режима работы коммутатора и возможности независимого обмена между несколькими устройствами.

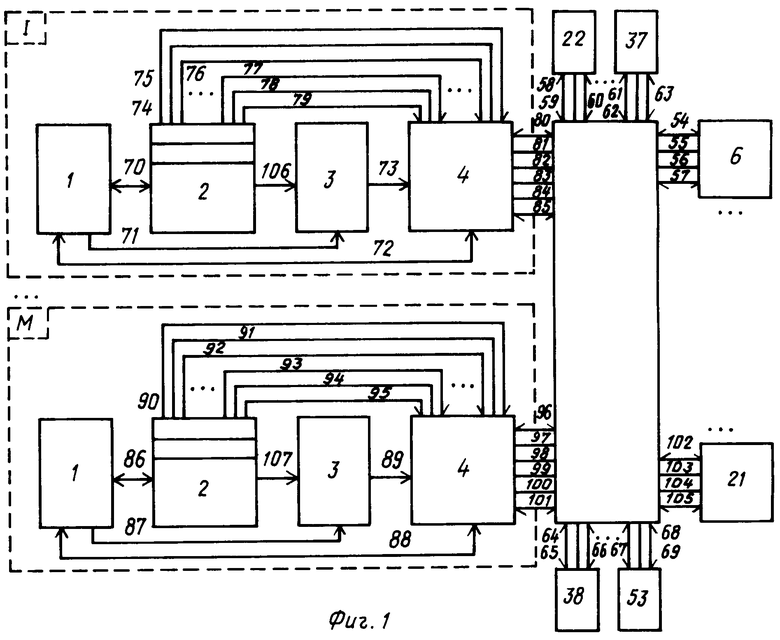

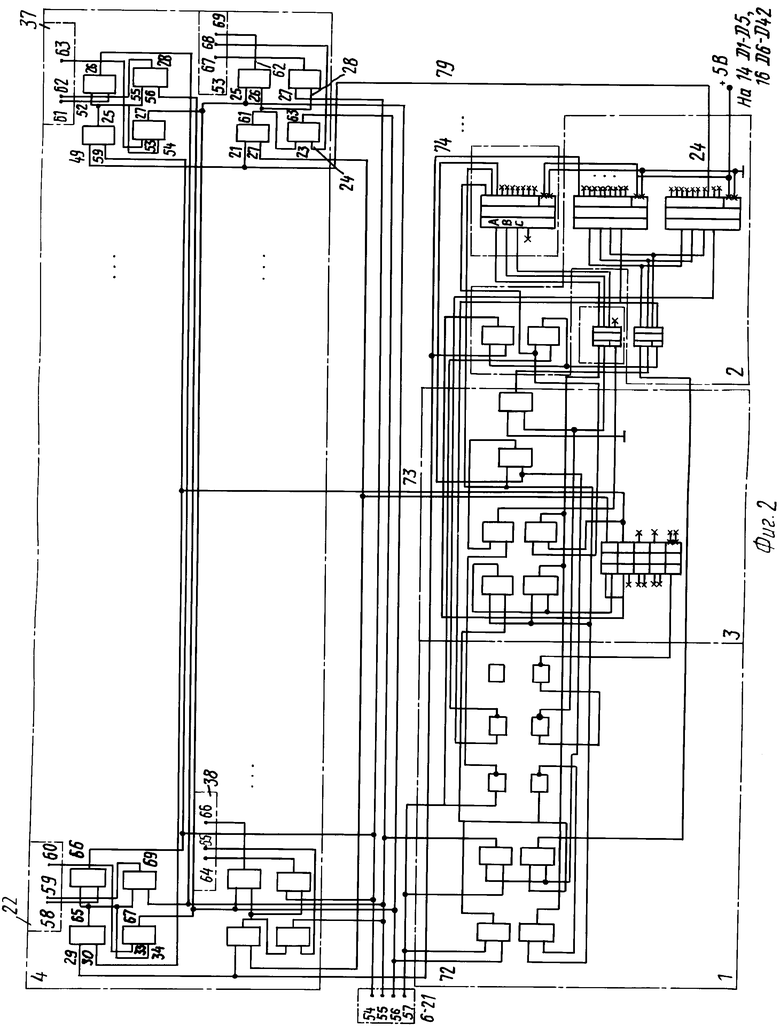

На фиг. 1 приведена функциональная схема предлагаемого коммутатора; на фиг. 2 - принципиальная схема асинхронного канала коммутации.

Коммутатор содержит М асинхронных каналов (1...М), соединенных объемной коммутационной платой (см. фиг. 1). Каждый асинхронный канал содержит командный коммутатор 1, адресный коммутатор 2, коммутатор 3 режимов "запись-считывание", ключевой блок 4 (на элементах И), общую объемную коммутационную плату 5, внешние входные-выходные шины 6-21, внешние шины 22-37 считывания, внешние шины 38-53 записи, линии 54-57 связи шины 6 первого канала с платой 5, линии 58-60 связи шины 22 первого канала с платой 5, линии 61-63 связи шины 37 М-го канала с платой 5, линии 64-66 связи шины 38 первого канала с платой 5, линии 67-69 связи шины 58 М-го канала с платой 5, двунаправленную линию 70 связи командного коммутатора 1 первого канала с адресным коммутатором 2 первого канала, линию 71 связи от командного коммутатора 1 первого канала к коммутатору 3 первого канала, двунаправленную линию 72 связи коммутатора 1 первого канала с ключевым блоком на элементах И первого канала, линию 73 связи от коммутатора 3 первого канала к ключевому блоку 4 первого канала, линии 74-79 связи от коммутатора 2 первого канала к ключевому блоку 4 первого канала, двунаправленные линии 80-85 связи ключевого блока 4 первого канала с платой 5, двунаправленную линию 86 связи коммутатора 1 М-го канала с коммутатором 2 М-го канала, линию 87 связи от коммутатора 1 М-го канала к коммутатору 3 М-го канала к коммутатору 3 М-го канала, двунаправленную линию 88 связи коммутатора 1 М-го канала с ключевым блоком 4 М-го канала, линию 89 связи от коммутатора 3 М-го канала к ключевому блоку 4 М-го канала, линии 90-95 связи от коммутатора 2 М-го канала к ключевому блоку 4 М-го канала, двунаправленные линии 96-101 связи ключевого блока 4 М-го канала с платой 5, линии 102-105 связи шины 21 М-го канала с платой 5, линии 106 и 107 связи коммутаторов 2 и 3.

К внешним входным-выходным шинам 6-21 могут быть подключены внешние устройства, например ЭВМ, к внешним шинам 22-37 считывания - внешние считывающие устройства, а к внешним шинам 38-53 записи - внешние записывающие устройства. Связь внешних устройств между собой, с внешними считывающими устройствами и с внешними записывающими устройствами осуществляется с помощью коммутатора.

Конструктивное выполнение предлагаемого коммутатора в зависимости от элементной базы может быть различным. Пример выполнения схемы одного канала коммутатора для связи 16-ти внешних устройств, 16-ти внешних считывающих и 16-ти внешних записывающих устройств показан на фиг. 2.

Коммутатор работает следующим образом.

Начальное состояние каждого канала коммутатора следующее (см. фиг. 1): в линиях 54-57, 102-105, 58-69 связи - "лог. 0". Коммутатор настроен на прием внешнего сигнала.

По первой линии 54 или 102 связи входной-выходной шины (6-21) приходит запрос о передаче или принимается посылка запроса; по второй линии 55 или 103 связи входной-выходной шины (6-21) принимается сигнал готовности к обмену и посылается сигнал готовности; по третьей линии 56 или 105 связи входной-выходной шины (6-21) передается информационный сигнал; по четвертой линии 57 или 105 связи входной-выходной шины (6-21) осуществляется обмен входной-выходной шины через плату 5 с ключевым блоком 4 и коммутаторами 1, 3 и 2.

Входные-выходные шины 6-21, шины 22-37 считывания и шины 38-53 записи каждого канала соединены через плату 5 с ключевым блоком 4 и коммутаторами 1, 3 и 2 соответствующего канала.

По 57-й или 105-й линии связи шины 6 или 21 приходит запрос на разрешение обмена в виде "лог. 1" и одновременно по 56-й или 104-й линии связи шины 6 или 21 приходит запрос на запись в другую входную-выходную шину 7-21 или в шину 38-53 записи в виде "лог. 1". Если по 56-й или 104-й линии связи не приходит "лог. 1", то устанавливается запрос на считывание из шины 7-21 или из шины 22-37. В 55-й или 103-й линии связи остается "лог. 0". Канал коммутатора настроен на считывание.

На втором выходе адресного коммутатора 2 соответствующего канала появляется "лог. 1" и поступает на седьмой вход адресного коммутатора 2, на одиннадцатом выходе командного коммутатора появляется "лог. 1" и поступает на восьмой вход коммутатора 1, на пятнадцатом выходе коммутатора 1 появляется "лог. 1", затем на первом выходе коммутатора 3 появляется "лог. 1", переводящая коммутатор режимов в режим записи: на седьмом выходе коммутатора 3 устанавливается "лог. 1", на восьмом выходе - "лог. 0".

С третьего выхода коммутатора 3 поступает "лог. 1" на пятнадцатый вход коммутатора 1, на двенадцатом выходе коммутатора 1 получается "лог. 1", поступающая на двенадцатый вход коммутатора 1. В результате на шестнадцатом выходе коммутатора 1 формируется "лог. 1", на втором выходе коммутатора 1 получается "лог. 1", идущая в 55-ю или 103-ю линию связи шины 6 (7-21), являющаяся сигналом готовности канала коммутатора к приему посылки адреса канала, с которым требуется установить связь.

По 56-й или 104-й линии связи шины 6 (7-21) приходит серия импульсов, по числу соответствующих номеру канала, через шины которого устанавливается связь. Импульсы проходят на второй вход коммутатора 1, с первого выхода командного коммутатора, поступают на седьмой вход коммутатора 1, с четвертого выхода командного коммутатора импульсы поступают на пятый вход адресного коммутатора, на третьем, четвертом, пятом, шестом выходах которого формируется соответствующее номеру соединяемого канала состояние, которое дешифруется адресным коммутатором 2. В результате появляется "лог. 1" на соответствующем выходе адресного коммутатора (седьмом, ..., (М+7)-ом), открываются соответствующие номеру соединяемого канала ключи блока 4, и канал готов к связи шин 6-21 между собой попарно или с шинами 38-53 на запись.

Аналогично происходит связь шин 6-21 между собой попарно или с шинами 22-37 на считывание.

Таким образом, предлагаемый многоканальный коммутатор обеспечивает повышение скорости обмена информации за счет возможности независимого обычного между несколькими каналами одновременно.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| СИСТЕМА ВНУТРИКОРАБЕЛЬНОЙ ГРОМКОГОВОРЯЩЕЙ СВЯЗИ И ТРАНСЛЯЦИИ | 1996 |

|

RU2131168C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕМЕЩЕНИЙ ОБЪЕКТОВ | 1984 |

|

RU2140721C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 1995 |

|

RU2109334C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| АВТОНОМНЫЙ НАВИГАЦИОННЫЙ ПРИБОР | 1994 |

|

RU2098767C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЙ | 1991 |

|

RU2022366C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией, результатами счета между несколькими электронно-вычислительными машинами (ЭВМ) и внешними устройствами. Цель изобретения - повышение скорости обмена информации. Многоканальный коммутатор содержит M асинхронных каналов, каждый из которых содержит коммутатор запись-считывание, адресный коммутатор, командный коммутатор. Многоканальный коммутатор осуществляет связь между несколькими ЭВМ по четырем линиям связи и между ЭВМ и внешними считывающими и записывающими устройствами по трем линиям связи. Количество коммутируемых ЭВМ равно количеству асинхронных каналов коммутатора. 3 з.п.ф-лы, 2 ил.

Авторы

Даты

1994-06-15—Публикация

1991-07-02—Подача