Изобретение относится к вычислительной технике и системам управления, может быть применено для построения адаптивных нечетких регуляторов для решения задач управления объектами, математическая модель которых априорно не определена, а цель функционирования выражена в нечетких понятиях.

Известен вероятностный автомат (а. с. СССР N 1045232, кл. G 06 F 15/36, 1983), содержащий блок генерации случайного кода, блок выбора состояний, генератор тактовых импульсов, элемент И, коммутатор, блок памяти, блок задания времени ожидания, элемент ИЛИ, генератор случайного напряжения, причем группа выходов блока генерации случайного кода соединена со входами группы информационных входов блока выбора состояний, группа выходов которого соединена с группой информационных входов коммутатора, группа выходов которого соединена с группой входов блока памяти, группа выходов которого соединена со группой управляющих входов блока выбора состояний и с группой входов блока задания времени ожидания, группа выходы которого соединена с группой выходов автомата и со входами элемента ИЛИ, выход которого соединен с инверсным входом элемента И и с первым тактовым входом блока генерации случайного кода, выход генератора тактовых импульсов соединен с первым тактовым входом блока задания времени ожидания и с прямым входом элемента И, выход которого соединен с тактовым входом коммутатора, со вторым тактовым входом блока генерации случайного кода и со вторым тактовым входом блока задания времени ожидания, выход генератора случайного напряжения соединен со входом управления блока задания времени ожидания.

Признаки, совпадающими с признаками заявляемого технического решения, является блок генерации случайного кода, блок выбора состояний, генератор тактовых импульсов, коммутатор, блок памяти.

Недостаток данного устройства состоит в ограниченных функциональных возможностях, так как в данном устройстве нет возможности осуществить сопоставление состояниям автомата качественные характеристики последних.

Причины, препятствующие достижению требуемого технического решения, состоят в особенности реализации известного устройства, при которой возможно осуществить генерацию состояний и выходных сигналов только лишь в четких понятиях.

Известен вероятностный автомат (а.с. СССР N 1108455, кл. G 06 F 15/20, 1984), содержащий первый блок памяти, блок выбора состояний, блок генерации случайного кода, генератор тактовых импульсов, коммутатор, второй блок памяти, причем входы групп управляющих и установочных входов первого блока памяти соединены соответственно с выходами групп управляющих входов и групп установочных входов, а группа входов соединена с первой группой информационных входов блока выбора состояний, группа выходов которого соединена с первой группой информационных входов блока выбора состояний, вторая группа информационных входов которого соединена с группой выходов блока генерации случайного кода, группа выходов которого соединена с группой входов коммутатора, группа выходов которого соединена с группой входов второго блока памяти, группа выходов которого соединена с выходами устройства и с группой управляющих входов блока выбора состояний, выход генератора тактовых импульсов соединен с тактовыми входами блока генерации случайного кода и коммутатора.

Признаками, совпадающими с признаками заявляемого технического решения, являются блок генерации случайного кода, блок выбора состояний, первый блок памяти, генератор тактовых импульсов, коммутатор, второй блок памяти.

Недостатком данного устройства является ограниченные функциональные возможности, связанные с тем, что при нечетком определении выходных состояний устройство не позволяет задать на четком множестве (выходных сигналов) нечеткие множества качественных характеристик этих сигналов.

Причины, препятствующие достижению требуемого технического решения, состоят в особенности реализации вероятностного автомата, при которой осуществляется генерация состояний и выходных сигналов, принадлежащих четко заданным множествам.

Из известных устройств наиболее близким к заявляемому нечеткому вероятностному автомату по совокупности конструктивных и функциональных признаков является вероятностный автомат (а. с. СССР N 1200297, кл. G 06 F 15/20, 1985), содержащий первый блок памяти, блок выбора состояний, блок генерации случайного кода, коммутатор, второй блок памяти, блок выбора выходного сигнала, третий блок памяти, генератор тактовых импульсов, причем входы групп управляющих и установочных входов первого блока памяти соединены соответственно с входами групп управляющих входов и групп установочных входов, а группа выходов соединена с первой группой информационных входов блока выбора состояний, группа выходов которого соединена с первой группой входов коммутатора, группа выходов которого соединена с группой установочных входов второго блока памяти, группа выходов которого соединена с группой управляющих входов блока выбора состояний и с первой группой управляющих входов блока выбора выходного сигнала, группа выходов которого соединена с группой входов третьего блока памяти, группа выходов которого соединена с группой выходов устройства, выход генератора тактовых импульсов соединен с тактовых входами коммутатора, блока выбора выходного сигнала и блока генерации случайного кода, группа выходов которого соединена со второй группой информационных входов блока выбора состояний.

Признаками, совпадающими с признаками заявляемого технического решения, являются блок генерации случайного кода, блок выбора состояний, первый блок памяти, генератор тактовых импульсов, коммутатор, второй блок памяти, блок выбора выходного сигнала, третий блок памяти.

Недостаток известного устройства состоит в ограниченных функциональных возможностях, вызванных тем, что известное устройство невозможно применить для решения задач моделирования и управления объектами, обладающими априорной неопределенностью и нечетким (качественным) описанием параметров и цели моделирования. Это связано в первую очередь с тем, что известное устройство не выполняет функцию установления соответствия четких понятий (множества выходов и входов) и нечетких понятий (качественные характеристики входов и выходов), заданных в виде нечетких переменных.

Причины, препятствующие достижению требуемого технического решения, состоят в особенности реализации вероятностного автомата, при которой генерируются состояния и выходные сигналы, принадлежащие четко заданным множествам, в соответствии с заданными функциями переходов и выходов для задач моделирования стохастических объектов.

Задача, на решение которой направлено изобретение, заключается в возможности генерации состояний и выходных сигналов в соответствии с заданными функциями переходов и выходов, а также генерации нечетких переменных, заданных на множествах состояний и выходных сигналов в соответствии с экспертными оценками для дальнейшего использования в задачах моделирования и управлениями сложными объектами в условиях отсутствия априорных сведений о математической модели.

Для достижения технического результата, заключающегося в расширении функциональных возможностей за счет осуществления генерации нечетких переменны, заданных на множествах состояний и выходных сигналов с использованием экспертной информации, предлагается в нечеткий вероятностный автомат, содержащий генератор тактовых импульсов, первый блок генерации случайного кода, блок выбора состояний, блок выбора выходного сигнала, первый, второй и третий блоки и коммутатор, причем M выходов группы управляющих входов устройства соединена с M входами первых групп управляющих входов первого блока памяти, входы (NxNxM) групп первых установочных входов устройства соединены соответственно со входами (NxNxM) групп установочных входов первого блока памяти, N входов групп второго управляющих входов которого соединены с N выходами группы выходов третьего блока памяти, выход первого генератора тактовых импульсов соединен с тактовых входов первого блока генерации случайного кода, K выходов группы выходов которого соединены с K входами второй группы информационных входов блока выбора состояний, дополнительно ввести второй блока генерации случайного кода, четвертый и пятый блоки памяти, второй коммутатор, первый и второй блоки определения максимального кода, причем входы (NxPxM) групп установочных входов второго блока памяти соединены со входами (NxPxM) групп вторых установочных входов устройства, M входов группы первых управляющих входов соединены с M входами группы управляющих входов устройства и с M входами группы первых управляющих входов первого блока памяти, N входов группы вторых управляющих входов соединены с N входами группы вторых управляющих входов первого блока памяти, N выходами группы выходов третьего блока памяти и N входами группы управляющих входов первого коммутатора, выходы P групп информационных выходов соединены с соответствующими входами P групп информационных входов блока выбора выходного сигнала, а тактовый вход соединен с выходом генератора тактовых импульсов и с тактовыми входами первого блока памяти, первого и второго блоков генерации случайного кода, N выходов группы информационных выходов блока выбора состояний соединены с соответствующими N входами группы первых информационных входов третьего блока памяти, K выходов группы выходов второго блока генерации случайного кода соединены с K входам группы вторых информационных входов блока выбора выходного сигнала, выход (NxL) групп информационных входов первого коммутатора соединены с выходами (NxL) групп информационных выходов четвертого блока памяти, (NxL) групп информационных входов которого соединены со входами (NxL) третьих групп установочных входов устройства, выходы L групп информационных выходов первого коммутатора соединены со входами L групп информационных входов первого блока определения максимального кода, выхода группы информационных выходов которого соединены с выходами третьей группы выходов устройства, P выходов группы выходов блока выбора выходных сигналов соединены с P входами группы управляющих входов второго коммутатора, входы (PxF) групп информационных входов которого соединены с выходами (PxF) групп информационных выходов пятого блока памяти, входы (PxF) групп информационных входов которого соединены со входами (PxF) четвертых групп установочных входов устройства, выходы P групп информационных выходов второго коммутатора соединены со входами F групп информационных входов второго блока определения максимального кода, группы информационных выходов которого соединены с выходами четвертой группы выходов устройства.

Наличие причинно-следственной связи между техническими результатами и признаками заявляемого изобретения доказывается следующими логическими посылками.

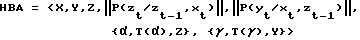

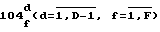

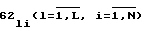

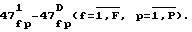

А основу работы вероятностного автомата положено предположение, состоящее в том, что формальное задание нечеткого вероятностного автомата (НВА) может быть представлено в виде

где

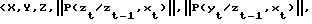

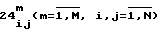

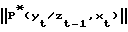

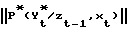

X, Y, Z - соответственно множество входных, выходных сигналов и сигналов состояний,  - множество условных вероятностей, определяющих пребывание НВА в такте времени t в состоянии zt при условии подачи в этом такте на вход сигнала xt и пребывания НВА в предшествующем (t-1) такте в состоянии

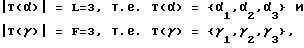

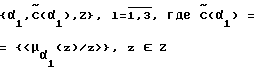

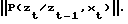

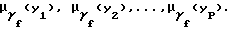

- множество условных вероятностей, определяющих пребывание НВА в такте времени t в состоянии zt при условии подачи в этом такте на вход сигнала xt и пребывания НВА в предшествующем (t-1) такте в состоянии  - множество условных вероятностей, определяющих наличие на выходе автомата сигнала yt при условии наличия в этом такте на выходе сигнала xt и пребывания НВА в предшествующем (t-1) такте в состоянии xt-1; лингвистическая переменная (ЛП) "выбор состояния", заданная набором {α,T(α),Z} , где α - наименование ЛП, T (α) -терм-множество ЛП α, , Z - базовое множество; ЛП "выбор выходного параметра", заданная набором {γ,T(γ),Y}, , где γ - наименование ЛП, T (γ) - терм-множество ЛП γ, , Y - базовое множество.

- множество условных вероятностей, определяющих наличие на выходе автомата сигнала yt при условии наличия в этом такте на выходе сигнала xt и пребывания НВА в предшествующем (t-1) такте в состоянии xt-1; лингвистическая переменная (ЛП) "выбор состояния", заданная набором {α,T(α),Z} , где α - наименование ЛП, T (α) -терм-множество ЛП α, , Z - базовое множество; ЛП "выбор выходного параметра", заданная набором {γ,T(γ),Y}, , где γ - наименование ЛП, T (γ) - терм-множество ЛП γ, , Y - базовое множество.

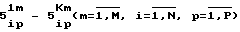

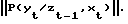

Если α и γ - лингвистические переменные, а T(α) = {α1,...,αL} и T(γ) = {γ1,...,γF} - терм-множество, где  - наименования НП, то с помощью экспертного опроса можно задать

- наименования НП, то с помощью экспертного опроса можно задать  и

и  - функции принадлежности нечетких переменных.

- функции принадлежности нечетких переменных.

Нечеткий вероятностный автомат генерирует состояния, выходные сигналы, а также лингвистические переменные, заданные на множествах состояний и выходных сигналов.

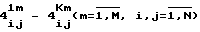

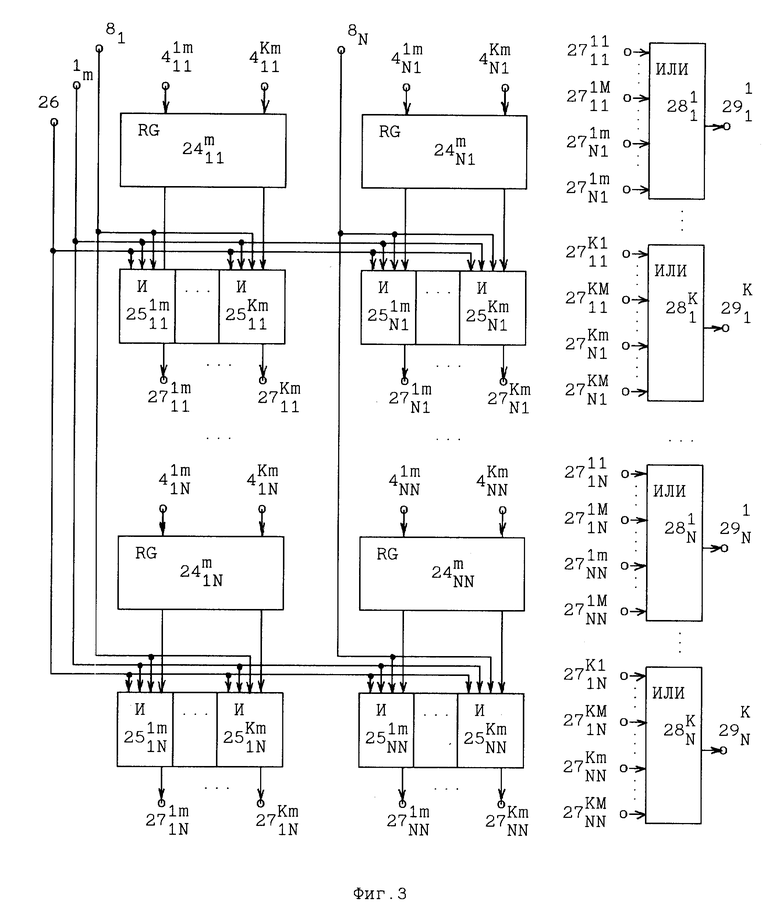

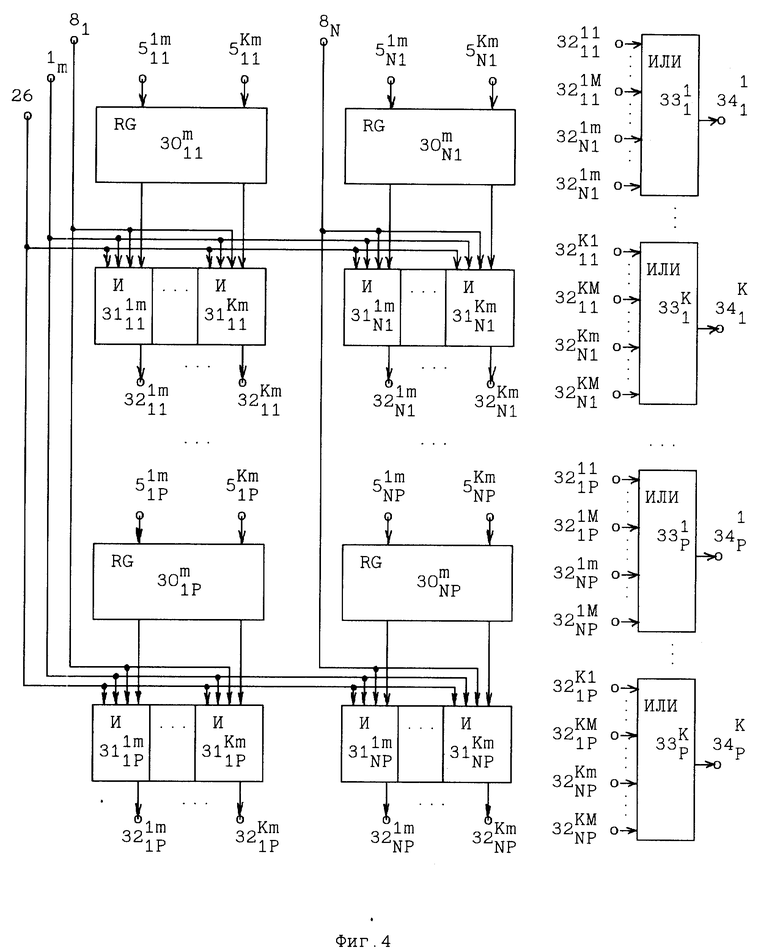

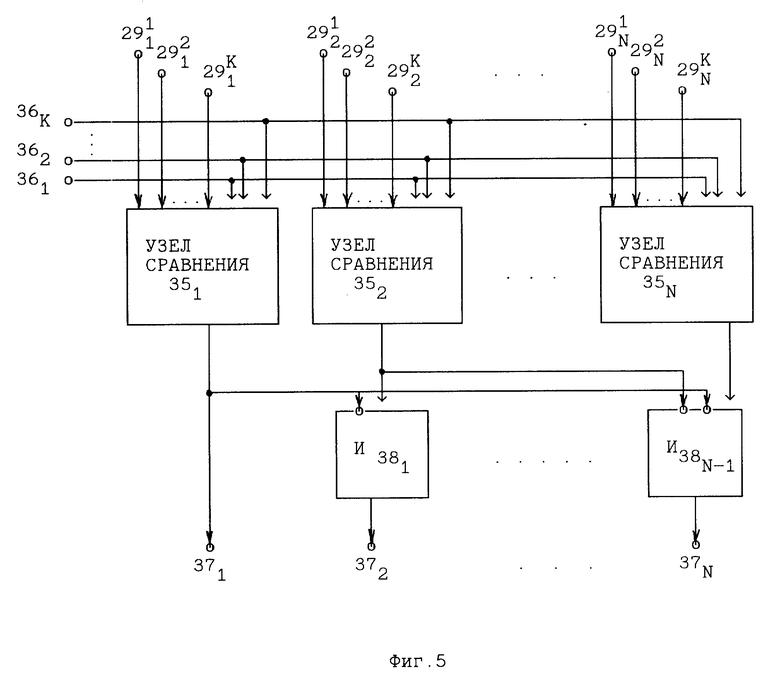

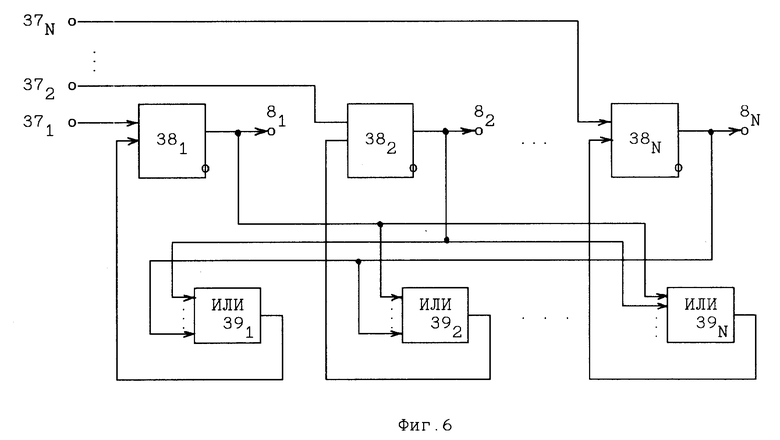

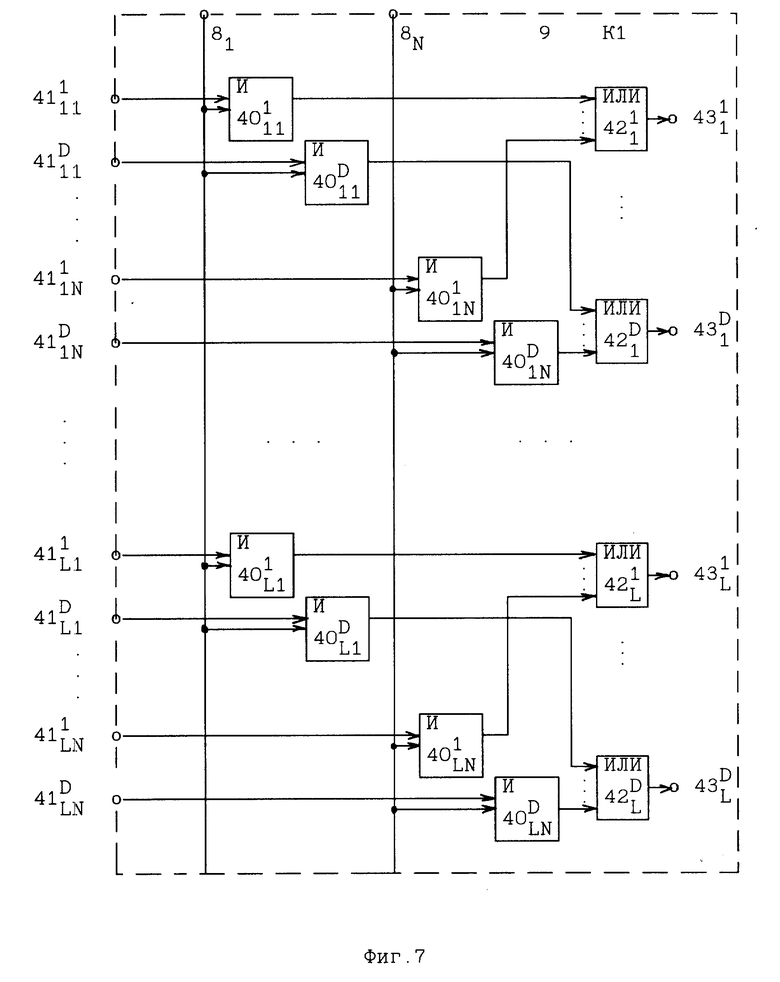

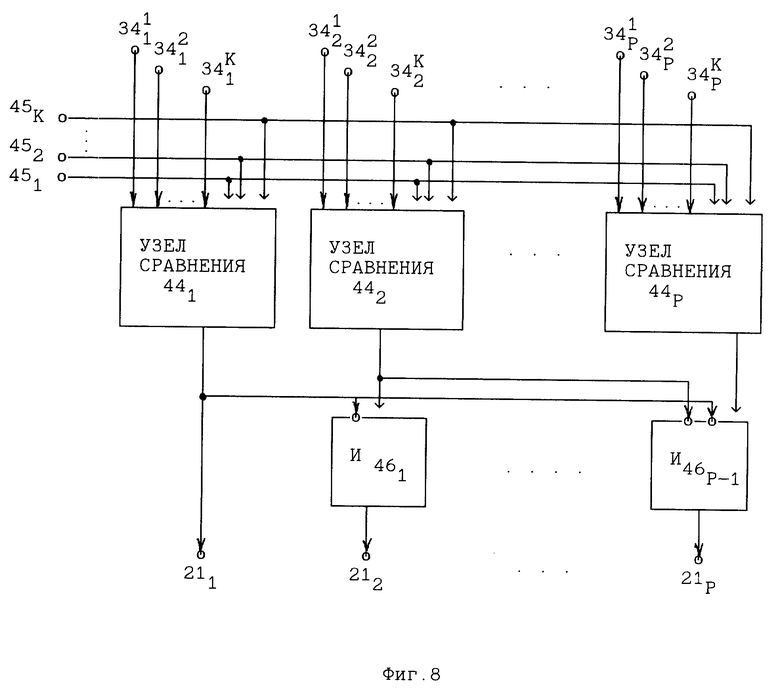

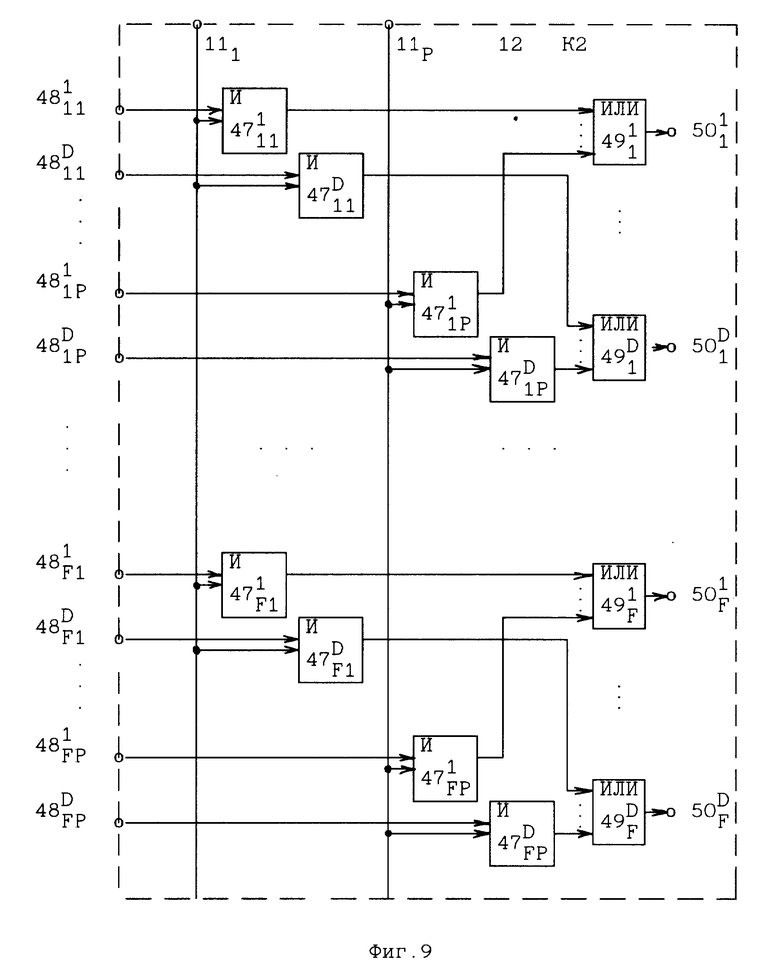

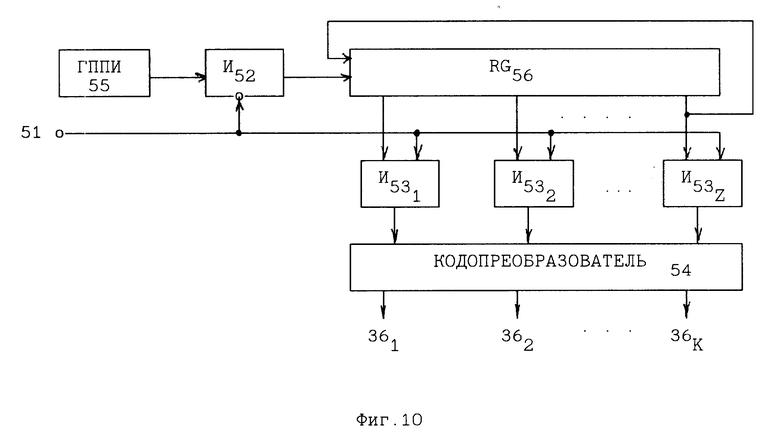

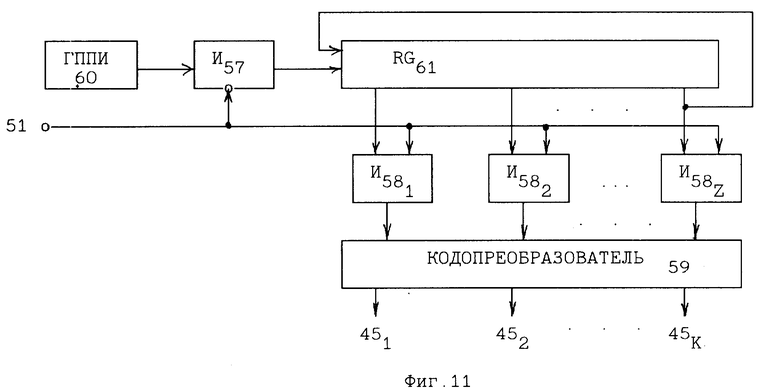

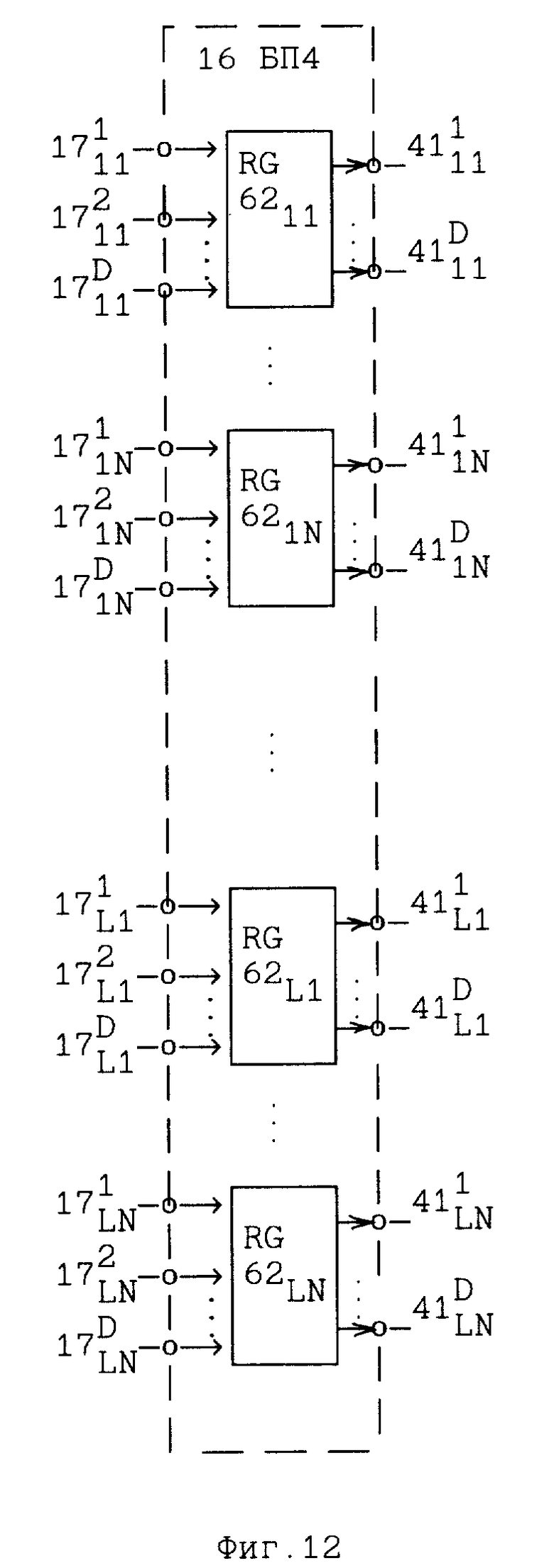

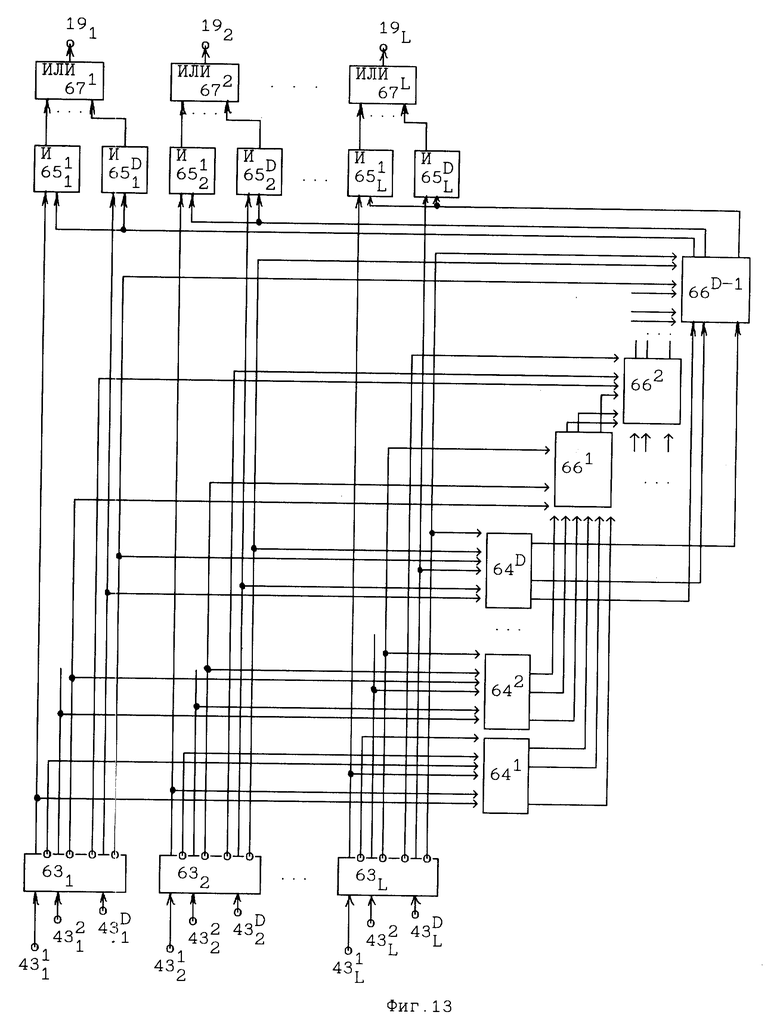

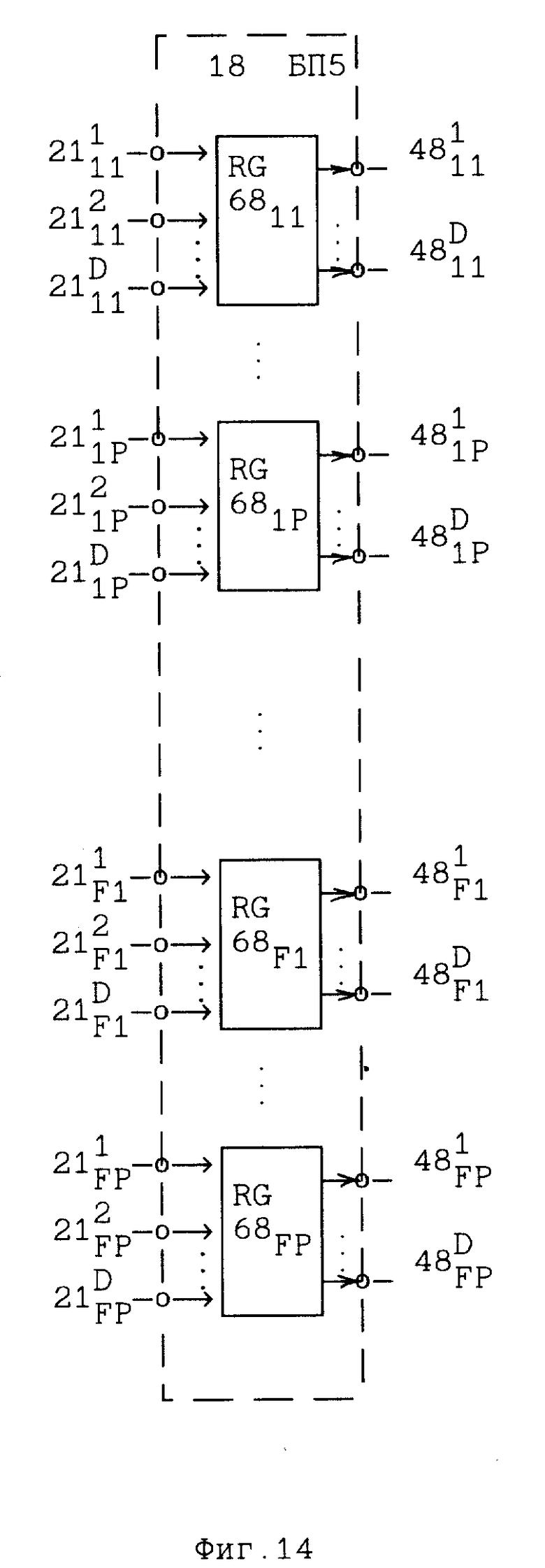

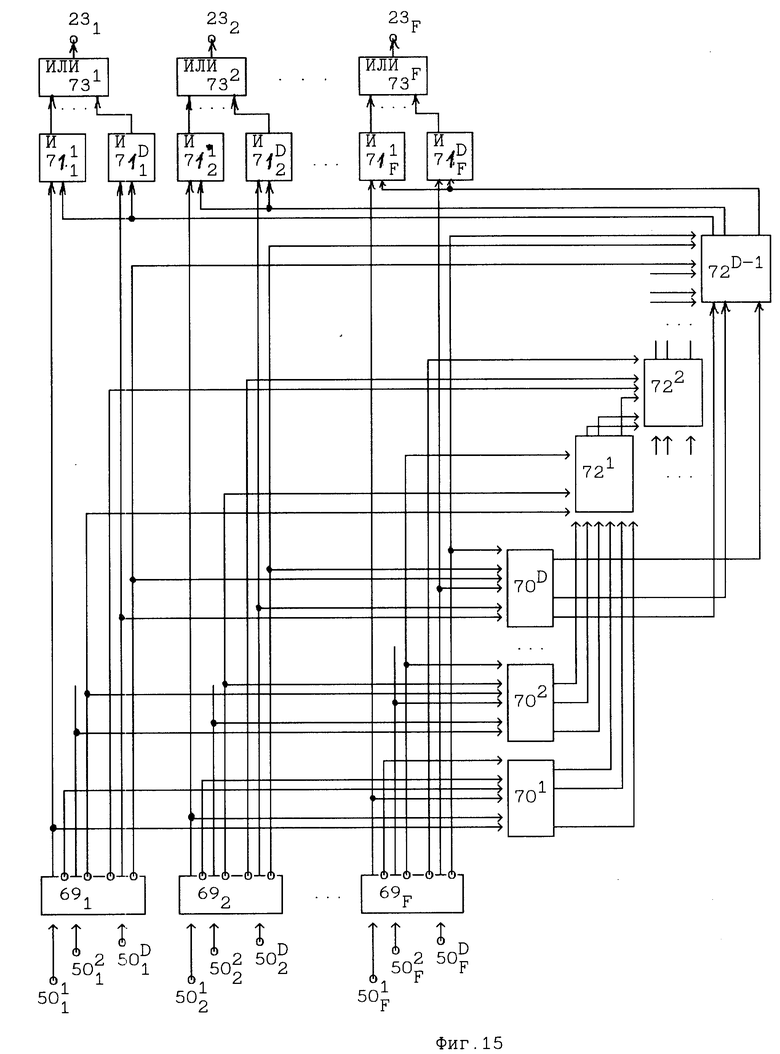

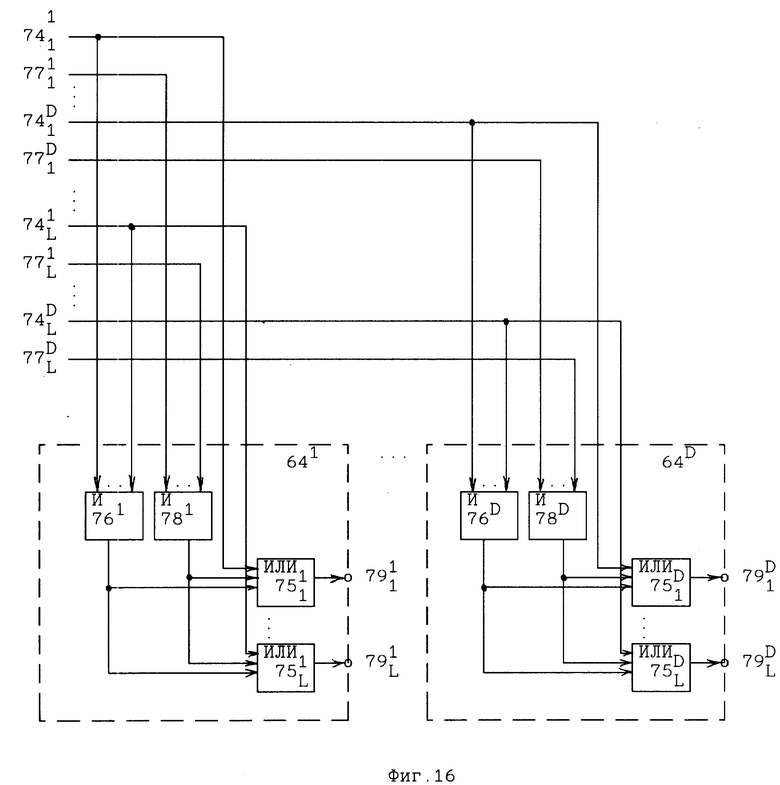

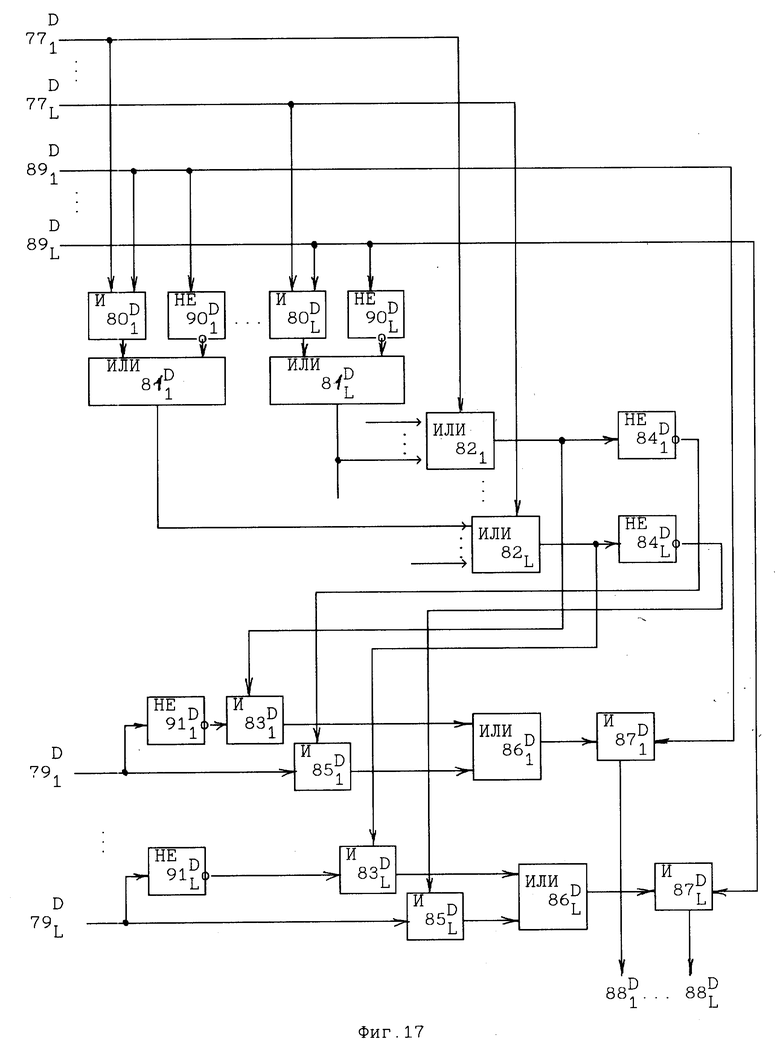

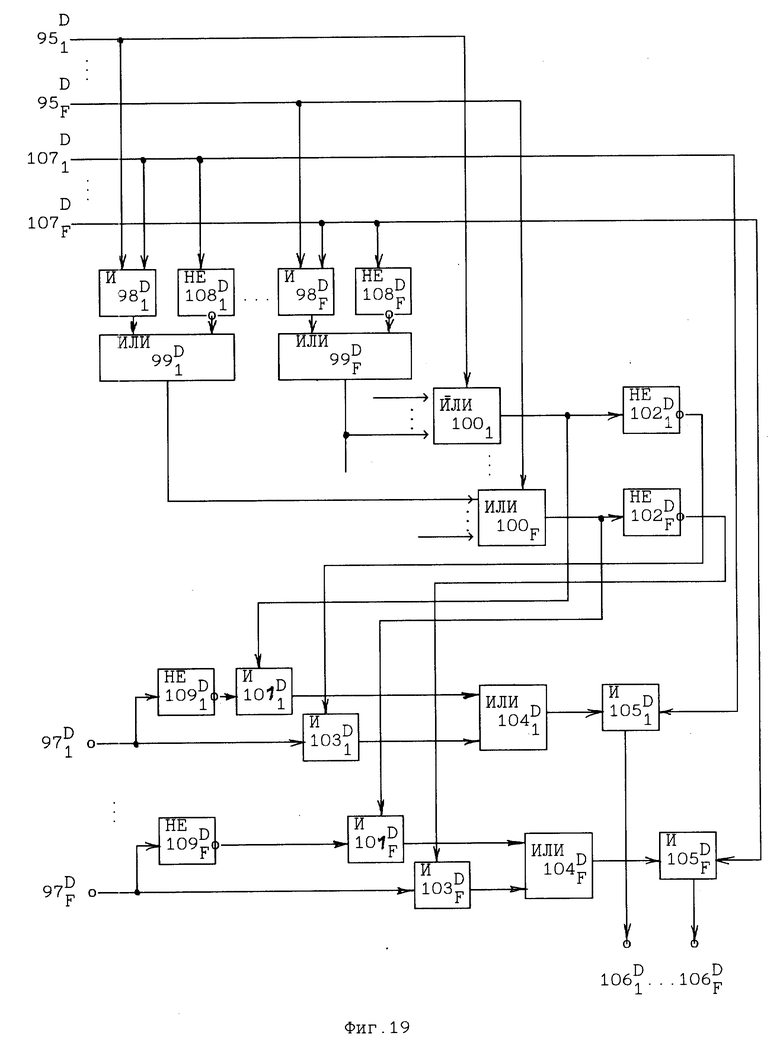

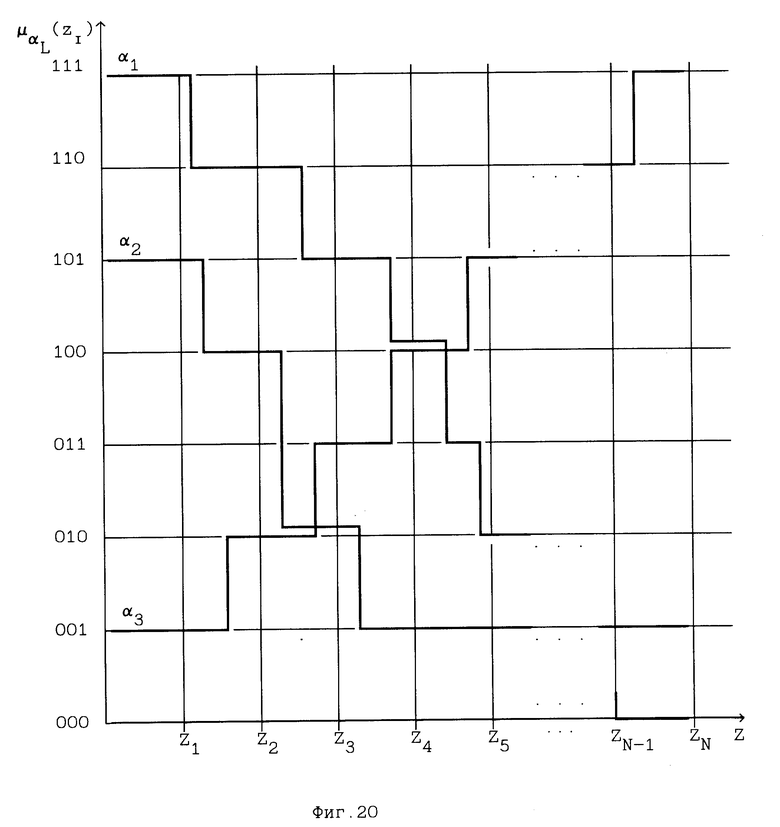

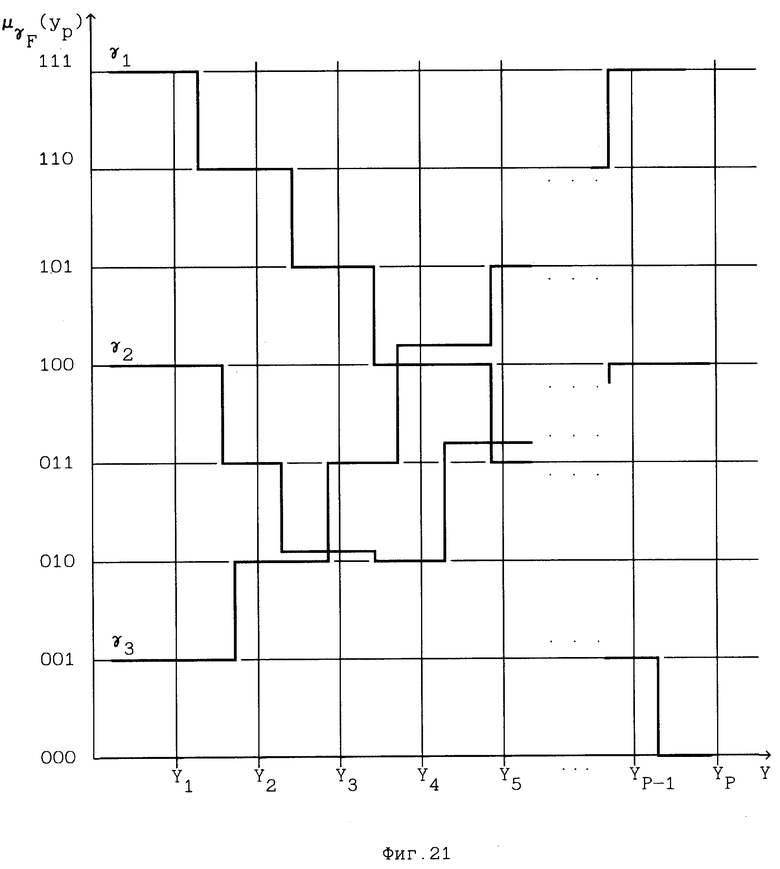

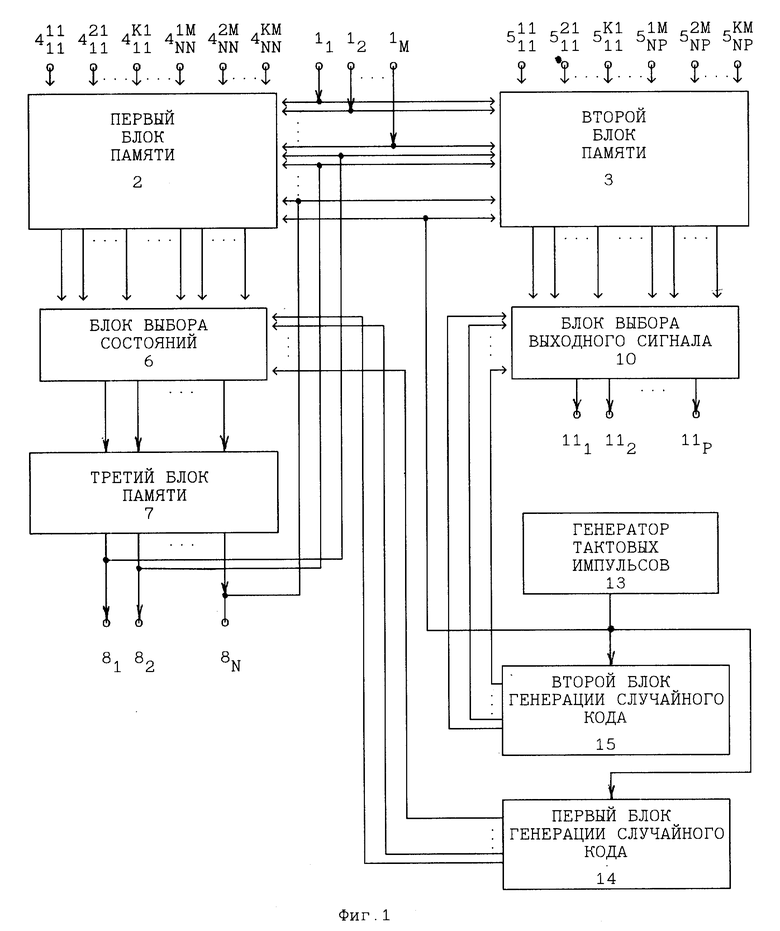

На фиг. 1 и фиг. 2 приведена схема заявляемого объекта; на фиг. 3 - функциональная схема первого блока памяти 2; на фиг. 4 - функциональная схема второго блока памяти 3; на фиг. 5 - структурная схема блока выбора состояния 6; на фиг. 6 - функциональная схема третьего блока памяти 7; на фиг. 7 - функциональная схема первого коммутатора 9; на фиг. 8 - функциональная схема блока выбора выходного сигнала 10; на фиг. 9 - функциональная схема второго коммутатора 12; на фиг. 10 - функциональная схема первого блока генерации случайного кода 14; на фиг. 11 - функциональная схема второго блока генерации случайного кода 15; на фиг. 12 - структурная схема четвертого блока памяти 16; на фиг. 13 - функциональная схема первого блока определения максимального кода 18; на фиг. 14 - структурная схема пятого блока памяти 20; на фиг. 15 - функциональная схема второго блока определения максимального кода 22; на фиг. 16 - функциональная схема дешифратора первого блока определения максимального кода; на фиг. 17 - функциональная схема каждого из блоков сравнения первого блока определения максимального кода, на фиг. 18 - функциональная схема дешифратора второго блока определения максимального кода; на фиг. 19 - функциональная схема каждого из блоков сравнения второго блока определения максимального кода; на фиг. 20 - графики функций принадлежности нечетких переменных α1,α2,...,αL ; на фиг. 21 - графики функций принадлежности нечетких переменных γ1,γ2,...,γF .

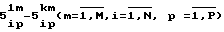

Структурная схема нечеткого вероятностного автомата (фиг. 1 и 2) содержат: 11-1M - группу управляющих входов; 2 - первый блок памяти; 3 - второй блок памяти;  - (NxNxM) групп первых установочных входов;

- (NxNxM) групп первых установочных входов;  (NxPxM) - групп вторых установочных входов; 6 - блок выбора состояний; 7 - третий блок памяти; 81-8N -группу выходов третьего блока памяти 7 и управляющих входов первого коммутатора 9; 10 - блок выбора выходного сигнала; 111-11P - группу вторых выходов устройства и управляющих входов второго коммутатора 12; 13 - генератор тактовых импульсов; 14 - первый блок генерации случайного кода; 15 - второй блок генерации случайного кода; 16 - четвертый блок памяти;

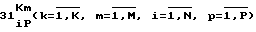

(NxPxM) - групп вторых установочных входов; 6 - блок выбора состояний; 7 - третий блок памяти; 81-8N -группу выходов третьего блока памяти 7 и управляющих входов первого коммутатора 9; 10 - блок выбора выходного сигнала; 111-11P - группу вторых выходов устройства и управляющих входов второго коммутатора 12; 13 - генератор тактовых импульсов; 14 - первый блок генерации случайного кода; 15 - второй блок генерации случайного кода; 16 - четвертый блок памяти;  , (NxL) групп третьих групп установочных входов устройства; 18 - первый блок определения максимального кода; 191 - 19L - выходы третьей группы выходов устройства; 20 - пятый блока памяти;

, (NxL) групп третьих групп установочных входов устройства; 18 - первый блок определения максимального кода; 191 - 19L - выходы третьей группы выходов устройства; 20 - пятый блока памяти;  - (PxF) групп четвертых установочных входов устройства; 22 - второй блок определения максимального кода; 231-23F - выходы четвертой группы выходов устройства.

- (PxF) групп четвертых установочных входов устройства; 22 - второй блок определения максимального кода; 231-23F - выходы четвертой группы выходов устройства.

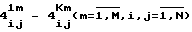

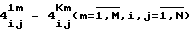

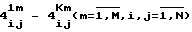

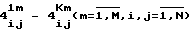

Функциональная схема первого блока памяти 2 (фиг. 3) содержит:  - M входов первой группы управляющих входов;

- M входов первой группы управляющих входов;  - (MxNxN) групп установочных входов;

- (MxNxN) групп установочных входов;  - N входов второй группы управляющих входов;

- N входов второй группы управляющих входов;  - регистры; (25

- регистры; (25 - (MxN) групп выходов элементов И 25 и (MxN) групп входов (MxN) групп элементов ИЛИ

- (MxN) групп выходов элементов И 25 и (MxN) групп входов (MxN) групп элементов ИЛИ  выходы N групп выходов блока памяти 2.

выходы N групп выходов блока памяти 2.

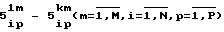

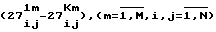

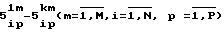

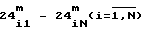

Функциональная схема второго блока памяти 3 (фиг. 4) содержит:  - M - групп входов первой группы управляющих входов;

- M - групп входов первой группы управляющих входов;  - N входов второй группы управляющих входов;

- N входов второй группы управляющих входов;  - (MxNxP) групп первых установочных входов; 26 - тактовый вход;

- (MxNxP) групп первых установочных входов; 26 - тактовый вход;  - регистры; (31

- регистры; (31 - выходы P групп выходов блока памяти 3.

- выходы P групп выходов блока памяти 3.

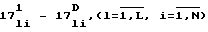

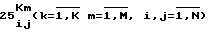

Структурная схема блока выбора состояния 6 (фиг. 5) содержит:  - N группа входов первой группы информационных входов;

- N группа входов первой группы информационных входов;  - N узлов сравнения; 361 - 36K - входы второй группы информационных входов;

- N узлов сравнения; 361 - 36K - входы второй группы информационных входов;  - N выходов блока выбора состояния 6; 381 - 38N-1 - элементы И.

- N выходов блока выбора состояния 6; 381 - 38N-1 - элементы И.

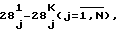

Структурная схема третьего блока памяти 7 (фиг. 6) содержит: 81 - 8N - выходы; 371 - 37N - группу входов; 381 - 38N - триггеры; 391 - 39N - элементы ИЛИ.

Функциональная схема первого коммутатора 9 (фиг. 7) содержит:  - N групп управляющих входов;

- N групп управляющих входов;  - (LxN) групп элементов И, по D элементов в каждой;

- (LxN) групп элементов И, по D элементов в каждой;  - (LxN) групп D-разрядных информационных входов;

- (LxN) групп D-разрядных информационных входов;  - L группа элементов ИЛИ, по D элементов в каждой;

- L группа элементов ИЛИ, по D элементов в каждой;  - L групп D - разрядных выходов первого коммутатора 9.

- L групп D - разрядных выходов первого коммутатора 9.

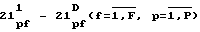

Функциональная схема блока выбора выходного сигнала 10 (фиг. 8) содержит:  - выходы;

- выходы;  входы первой группы информационных входов;

входы первой группы информационных входов;  - узлы сравнения; 451 - 45K - входы второй группы информационных входов; 461 - 46p-1 - элементы P.

- узлы сравнения; 451 - 45K - входы второй группы информационных входов; 461 - 46p-1 - элементы P.

Функциональная схема второго коммутатора 12 (фиг. 9) содержит:  - P групп входов группы управляющих входов;

- P групп входов группы управляющих входов;  (FxP) групп элементов И, по D элементов в каждой;

(FxP) групп элементов И, по D элементов в каждой;  (FxP) групп D - разрядных входов группы информационных входов;

(FxP) групп D - разрядных входов группы информационных входов;  - F групп элементов ИЛИ, по D элементов в каждой; 50

- F групп элементов ИЛИ, по D элементов в каждой; 50

Функциональная схема первого блока генерации случайного кода 14 (фиг. 10) содержит: 361 - 36K - выходы; 51 - тактовый вход; 52 - первый элемент И; 531 - 53Z вторые элементы И; 54 - кодопреобразователь; 55 - генератор пуассоновского потока импульсов; 56 - циклически замкнутый регистр сдвига.

Функциональная схема второго блока генерации случайного кода 15 (фиг. 11) содержит: 451 - 45K - выходы; 51 - тактовый вход; 57 - первый элемент И; 581 - 58Z - вторые элементы И; 59 - кодопреобразователь; 60 - генератор пуассоновского потока импульсов; 61 - циклически замкнутый регистр сдвига.

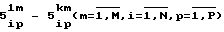

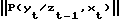

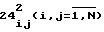

Структурная схема четвертого блока памяти 16 (фиг. 12) содержит:  - (LxN) групп D - разрядных информационных входов; 621i - (LxN) групп регистров; 41

- (LxN) групп D - разрядных информационных входов; 621i - (LxN) групп регистров; 41

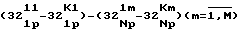

Функциональная схема первого блока определения максимального кода 18 (фиг. 13) содержит: 191 - 29L - группу выходов;  - L групп D - разрядных входов;

- L групп D - разрядных входов;  - группу регистров; 651 - 64D группу дешифраторов состояний; 65

- группу регистров; 651 - 64D группу дешифраторов состояний; 65

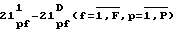

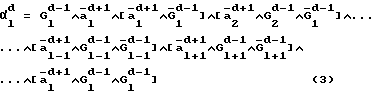

Структурная схема пятого блока памяти 20 (фиг. 14) содержит:  (FxP) групп D - разрядных информационных входов; 68fp - 68fp

(FxP) групп D - разрядных информационных входов; 68fp - 68fp - F групп регистров, по P в каждой группе;

- F групп регистров, по P в каждой группе;  - (FxP) групп D - разрядных выходов.

- (FxP) групп D - разрядных выходов.

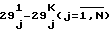

Функциональная схема второго блока определения максимального кода 22 (фиг. 15) содержит: 231 - 23F - группу выходов;  - F групп D - разрядных входов; 691 - 69F - группу регистров; 701 - 70D - группу дешифраторов состояний;

- F групп D - разрядных входов; 691 - 69F - группу регистров; 701 - 70D - группу дешифраторов состояний;  - F групп элементов И, по D элементов в каждой; 721 - 72D - узлы анализа; 731 - 73F - группу элементов ИЛИ.

- F групп элементов И, по D элементов в каждой; 721 - 72D - узлы анализа; 731 - 73F - группу элементов ИЛИ.

Функциональная схема дешифратора первого блока определения максимального кода (фиг. 16) содержит  - первые группы входов;

- первые группы входов;  - группы элементов ИЛИ, по L - элементов в каждой; 761 - 76D - первые элементы И;

- группы элементов ИЛИ, по L - элементов в каждой; 761 - 76D - первые элементы И;  - вторые группы входов; 781 - 78D - вторые элементы И;

- вторые группы входов; 781 - 78D - вторые элементы И;  - группы выходов дешифраторов 64.

- группы выходов дешифраторов 64.

Функциональная схема каждого из d,  узлов анализа 66 первого блока определения максимального кода 18 (фиг. 17) содержит

узлов анализа 66 первого блока определения максимального кода 18 (фиг. 17) содержит  - D-1 групп первых L - разрядных входов;

- D-1 групп первых L - разрядных входов;  - D-1 групп вторых L - разрядных входов;

- D-1 групп вторых L - разрядных входов;  - D-1 первых групп элементов И, по L элементов И в каждой;

- D-1 первых групп элементов И, по L элементов И в каждой;  - D-1 первых групп элементов ИЛИ, по L элементов ИЛИ в каждой;

- D-1 первых групп элементов ИЛИ, по L элементов ИЛИ в каждой;  - D-1 групп вторых элементов ИЛИ, по L элементов ИЛИ в каждой

- D-1 групп вторых элементов ИЛИ, по L элементов ИЛИ в каждой  - D-1 вторых групп элементов И, по L элементов в каждой;

- D-1 вторых групп элементов И, по L элементов в каждой;  - D-1 вторых групп элементов НЕ, по L элементов в каждой группе;

- D-1 вторых групп элементов НЕ, по L элементов в каждой группе;  - D-1 третьих групп элементов И, по L элементов в каждой;

- D-1 третьих групп элементов И, по L элементов в каждой;  - D-1 третьих групп элементов ИЛИ, по L элементов в каждой группе;

- D-1 третьих групп элементов ИЛИ, по L элементов в каждой группе;  - D-1 четвертых групп элементов И, по L элементов в каждой;

- D-1 четвертых групп элементов И, по L элементов в каждой;  - D-1 групп L - разрядных выходов;

- D-1 групп L - разрядных выходов;  - D-1 групп третьих L - разрядных входов;

- D-1 групп третьих L - разрядных входов;  - D-1 вторых групп элементов НЕ, по L в каждой группе;

- D-1 вторых групп элементов НЕ, по L в каждой группе;  - D-1 третьих групп элементов НЕ, по L в каждой группе.

- D-1 третьих групп элементов НЕ, по L в каждой группе.

Функциональные схемы дешифраторов 70 второго блока определения максимального кода 22 (фиг. 18) содержит:  - первые группы входов;

- первые группы входов;  - группы элементов ИЛИ, по F элементов в каждой; 941 - 94D - первые элементы И;

- группы элементов ИЛИ, по F элементов в каждой; 941 - 94D - первые элементы И;  - вторые группы входов; 961 - 96D - вторые элементы И;

- вторые группы входов; 961 - 96D - вторые элементы И;  - D групп выходов дешифраторов.

- D групп выходов дешифраторов.

Функциональная схема каждого из d,  узлов анализа 72 второго блока определения максимального кода 22 (фиг. 19) содержит:

узлов анализа 72 второго блока определения максимального кода 22 (фиг. 19) содержит:  - D-1 групп первых F - разрядных входов;

- D-1 групп первых F - разрядных входов;  - D-1 групп вторых F - разрядных входов;

- D-1 групп вторых F - разрядных входов;  - D-1 первых групп элементов И, по F элементов И в каждой;

- D-1 первых групп элементов И, по F элементов И в каждой;  - D-1 первых групп элементов ИЛИ, по F элементов ИЛИ в каждой;

- D-1 первых групп элементов ИЛИ, по F элементов ИЛИ в каждой;  - D-1 групп вторых элементов ИЛИ, по F элементов ИЛИ в каждой;

- D-1 групп вторых элементов ИЛИ, по F элементов ИЛИ в каждой;  - D-1 вторых групп элементов И, по F элементов в каждой;

- D-1 вторых групп элементов И, по F элементов в каждой;  - D-1 вторых групп элементов НЕ, по F элементов в каждой группе;

- D-1 вторых групп элементов НЕ, по F элементов в каждой группе;  - D-1 третьих групп элементов И, по F элементов в каждой;

- D-1 третьих групп элементов И, по F элементов в каждой;  - D-1 третьих групп элементов ИЛИ, по F элементов в каждой группе;

- D-1 третьих групп элементов ИЛИ, по F элементов в каждой группе;  - D-1 четвертых групп элементов И, по F элементов в каждой;

- D-1 четвертых групп элементов И, по F элементов в каждой;  - D-1 групп F - разрядных выходов;

- D-1 групп F - разрядных выходов;  - D-1 групп третьих F - разрядных входов;

- D-1 групп третьих F - разрядных входов;  - D-1 вторых групп элементов НЕ, по F в каждой группе;

- D-1 вторых групп элементов НЕ, по F в каждой группе;  - D-1 третьих групп элементов НЕ, по F в каждой группе.

- D-1 третьих групп элементов НЕ, по F в каждой группе.

Элементы нечеткого автомата взаимосвязаны следующим образом.

Входы группы управляющих входов 11 - 1M устройства соединены со входами первых групп управляющих входов первого блока памяти 2 и второго блока памяти 3, входы  (NxNxM) - групп первых установочных входов устройства соединены соответственно со входами групп установочных входов первого блока памяти 2, входы

(NxNxM) - групп первых установочных входов устройства соединены соответственно со входами групп установочных входов первого блока памяти 2, входы  (NxPxM) - групп вторых установочных входов устройства соединены со входами групп установочных входов второго блока памяти 3, выходы N групп информационных выходов первого блока памяти 2 соединены с соответствующими входами N групп первой группы информационных входов блока выбора состояний 6, выходы группы информационных выходов блока выбора состояний 6 соединены с соответствующими входами группы информационных входов третьего блока памяти 7, выходы 81 - 8N группы выходов третьего блока памяти 7 соединены с соответствующими входами 81 - 8N группы управляющих входов первого коммутатора 9, со входами групп вторых управляющих входов первого 2 и второго 3 блоков памяти, и с выходами 81 - 8N первой группы выходов устройства, выходы P групп информационных выходов второго блока памяти 3 соединены с соответствующими входам P групп информационных входов блока выбора выходного сигнала 10, выходы 111 - 11P группы управляющих выходов которого соединены с соответствующими входами 111 - 11P группы управляющих входов второго коммутатора 12, с выходами 111 - 11P второй группы выходов устройства, выход генератора тактовых импульсов 13 соединен с тактовыми входами первого 2 и второго 3 блоков памяти, первого 14 и второго 15 блоков генерации случайного кода, выходы группы K информационных выходов первого блока генерации случайного кода 14 соединены с соответствующими входами второй группы информационных входов блока выбора состояний 6, выходы группы выходов второго блока генерации случайного кода 15 соединены с соответствующими входами второй группы информационных входов блока выбора выходного сигнала 10, входы (NxL) групп вторых информационных входов первого коммутатора 9 соединены с выходами (NxL) групп информационных выходов четвертого блока памяти 16, (NxL) групп информационных входов которого соединены со входами (NxL) третьих групп установочных входов

(NxPxM) - групп вторых установочных входов устройства соединены со входами групп установочных входов второго блока памяти 3, выходы N групп информационных выходов первого блока памяти 2 соединены с соответствующими входами N групп первой группы информационных входов блока выбора состояний 6, выходы группы информационных выходов блока выбора состояний 6 соединены с соответствующими входами группы информационных входов третьего блока памяти 7, выходы 81 - 8N группы выходов третьего блока памяти 7 соединены с соответствующими входами 81 - 8N группы управляющих входов первого коммутатора 9, со входами групп вторых управляющих входов первого 2 и второго 3 блоков памяти, и с выходами 81 - 8N первой группы выходов устройства, выходы P групп информационных выходов второго блока памяти 3 соединены с соответствующими входам P групп информационных входов блока выбора выходного сигнала 10, выходы 111 - 11P группы управляющих выходов которого соединены с соответствующими входами 111 - 11P группы управляющих входов второго коммутатора 12, с выходами 111 - 11P второй группы выходов устройства, выход генератора тактовых импульсов 13 соединен с тактовыми входами первого 2 и второго 3 блоков памяти, первого 14 и второго 15 блоков генерации случайного кода, выходы группы K информационных выходов первого блока генерации случайного кода 14 соединены с соответствующими входами второй группы информационных входов блока выбора состояний 6, выходы группы выходов второго блока генерации случайного кода 15 соединены с соответствующими входами второй группы информационных входов блока выбора выходного сигнала 10, входы (NxL) групп вторых информационных входов первого коммутатора 9 соединены с выходами (NxL) групп информационных выходов четвертого блока памяти 16, (NxL) групп информационных входов которого соединены со входами (NxL) третьих групп установочных входов  устройства, выходы L групп информационных выходов первого коммутатора 9 соединены со входами L групп информационных входов первого блока определения максимального кода 18, выходы группы информационных выходов которого соединены с выходами 191 - 19L третьей группы выходов устройства, входы (PxF) групп вторых информационных входов второго коммутатора 12 соединены с выходами (PxF) групп информационных выходов пятого блока памяти 20, входы (PxF) групп информационных входов которого соединены со входами (PxF) четвертых групп установочных входов

устройства, выходы L групп информационных выходов первого коммутатора 9 соединены со входами L групп информационных входов первого блока определения максимального кода 18, выходы группы информационных выходов которого соединены с выходами 191 - 19L третьей группы выходов устройства, входы (PxF) групп вторых информационных входов второго коммутатора 12 соединены с выходами (PxF) групп информационных выходов пятого блока памяти 20, входы (PxF) групп информационных входов которого соединены со входами (PxF) четвертых групп установочных входов  устройства, выходы F групп информационных выходов второго коммутатора 12 соединены со входами F групп информационных входов второго блока определения максимального кода 22, группы информационных выходов которого соединены с выходами 231 - 23F четвертой группой выходов устройства.

устройства, выходы F групп информационных выходов второго коммутатора 12 соединены со входами F групп информационных входов второго блока определения максимального кода 22, группы информационных выходов которого соединены с выходами 231 - 23F четвертой группой выходов устройства.

В первом блоке памяти 2 каждые из K входов  (i, j, m)-й группы установочных входов соединены с входами записи соответствующих регистров 24

(i, j, m)-й группы установочных входов соединены с входами записи соответствующих регистров 24 соединены с первыми входами соответствующих элементов И (25

соединены с первыми входами соответствующих элементов И (25 объединены и соединены с тактовым входом 26 блока памяти 2, третьи входы элементов И 25

объединены и соединены с тактовым входом 26 блока памяти 2, третьи входы элементов И 25 элементом И 25 соединены с соответствующими входами (N x M) групп элементов ИЛИ

элементом И 25 соединены с соответствующими входами (N x M) групп элементов ИЛИ  , выходы которых соединены соответственно с выходами N групп выходов 29

, выходы которых соединены соответственно с выходами N групп выходов 29

Во втором блоке памяти 3 каждые из K входов  (i, p, m)-й группы установочных входов соединены со входами записи соответствующих регистров 30

(i, p, m)-й группы установочных входов соединены со входами записи соответствующих регистров 30 объединены и соединены с тактовым входом 26 блока памяти 2, третьи входы элементов И 31

объединены и соединены с тактовым входом 26 блока памяти 2, третьи входы элементов И 31 элементов И 31 соединены с соответствующими входами (N x M) групп элементов ИЛИ

элементов И 31 соединены с соответствующими входами (N x M) групп элементов ИЛИ  , выходы которых соединены соответственно с выходами P групп выходов 34

, выходы которых соединены соответственно с выходами P групп выходов 34

В блоке выбора состояний 6 входы  первых групп информационных входов соединены с входами первых групп входов j-х узлов сравнения 35j, одноименные входы вторых групп входов которых объединены и соединены с соответствующими входами 361-36K второй группы информационных входов блока выбора состояний 6, выход узла сравнения 351 соединен с выходом 371 блока 6 и с первыми инверсными входами элементов И 381-38N-1, выходы узлов сравнения 35i

первых групп информационных входов соединены с входами первых групп входов j-х узлов сравнения 35j, одноименные входы вторых групп входов которых объединены и соединены с соответствующими входами 361-36K второй группы информационных входов блока выбора состояний 6, выход узла сравнения 351 соединен с выходом 371 блока 6 и с первыми инверсными входами элементов И 381-38N-1, выходы узлов сравнения 35i соединены с прямыми входами соответствующих элементов И 38i-1 и с i-и инверсными входами элементов И 38i, выходы которых соединены с выходами 37i+1 блока 6.

соединены с прямыми входами соответствующих элементов И 38i-1 и с i-и инверсными входами элементов И 38i, выходы которых соединены с выходами 37i+1 блока 6.

В третьем блоке памяти 7 входы 371 - 37N соединены с единичными входами соответствующих триггеров 381 - 38N, нулевые входы которых соединены с выходами соответствующих элементов ИЛИ 391 - 39N, а единичные выходы соединены с выходами 81 - 8N блока 7 и соответствующими входами соответствующих элементов ИЛИ 391 - 39N, причем единичный выход триггера 38i соединен с выходом 8i блока 7 и с соответствующими входами элементов ИЛИ 391 - 39i-1, 39i+1 - 39N.

В первом коммутаторе 9 i-е  входы 8i группы управляющих входов соединены с первыми входами элементов И

входы 8i группы управляющих входов соединены с первыми входами элементов И  группы, вторые входы которых соединены со входами

группы, вторые входы которых соединены со входами  групп информационных входов, выходы элементов И

групп информационных входов, выходы элементов И  соединены с соответствующими входами элементов ИЛИ

соединены с соответствующими входами элементов ИЛИ  , выходы которых соединены с выходами

, выходы которых соединены с выходами  первого коммутатора 9.

первого коммутатора 9.

В блоке выбора выходного сигнала 10 входы  первой группы информационных входов соединены с входами первых групп входов p-х узлов сравнения 44P, одноименные входы вторых групп входов которых объединены и соединены с соответствующими входами 451 - 45K второй группы информационных входов блока выбора выходного сигнала 10, выход узла сравнения 441 соединен с выходом 11 блока и с первыми инверсными входами элементов И 461 - 46p-1, выходы узлов сравнения 44p

первой группы информационных входов соединены с входами первых групп входов p-х узлов сравнения 44P, одноименные входы вторых групп входов которых объединены и соединены с соответствующими входами 451 - 45K второй группы информационных входов блока выбора выходного сигнала 10, выход узла сравнения 441 соединен с выходом 11 блока и с первыми инверсными входами элементов И 461 - 46p-1, выходы узлов сравнения 44p  соединены с прямыми входами соответствующих элементов И 46p-1 и с p-и инверсными входами элементов И 46p, выходы которых соединены с выходами 11p+1 блока 10.

соединены с прямыми входами соответствующих элементов И 46p-1 и с p-и инверсными входами элементов И 46p, выходы которых соединены с выходами 11p+1 блока 10.

Во втором коммутаторе 12 p-е  входы 11p группы управляющих входов соединены с первыми входами элементов B

входы 11p группы управляющих входов соединены с первыми входами элементов B  группы, вторые входы которых соединены со входами

группы, вторые входы которых соединены со входами  группы информационных входов, выходы элементов И

группы информационных входов, выходы элементов И  соединены с соответствующими входами элементов ИЛИ

соединены с соответствующими входами элементов ИЛИ  , выходы которых соединены с выходами

, выходы которых соединены с выходами  второго коммутатора 12.

второго коммутатора 12.

В первом блоке генерации случайного кода 14 тактовый вход 52 соединен с инверсным входом первого элемента И 52 и с первыми входами вторых элементов И 531 - 53Z, выхода которых соединены с соответствующими входами кодопреобразователя 54, выхода которого соединены с выходами 361 - 36K блока, выход генератора пуассоновского потока импульсов 55 соединен с прямым входом первого элемента И 52, выход которого соединен с тактовым входом циклически замкнутого регистра сдвига 56, разрядные выходы которого соединены со вторыми входами соответствующих элементов И 531 - 53Z.

Во втором блоке генерации случайного кода 15 тактовый вход 51 соединен с инверсным входом первого элемента И 57 и с первыми входами вторых элементов И 581 - 58Z, выходы которых соединены с соответствующими входами кодопреобразователя 59, выходы которого соединены с выходами 451 - 45K блока, выход генератора пуассоновского потока импульсов 60 соединен с прямым входом первого элемента И 57, вхыод которого соединен с тактовым входом циклически замкнутого регистра сдвига 61, разрядные выходы которого соединены со вторыми входами соответствующих элементов И 581 - 58Z.

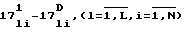

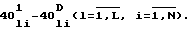

В четвертом блоке памяти 16 входы 17 соединены с соответствующими входами (li)-х регистров 62li

соединены с соответствующими входами (li)-х регистров 62li , выходы которых соединены соответственно с выходами

, выходы которых соединены соответственно с выходами  (l, i)-й группы выходов блока 16.

(l, i)-й группы выходов блока 16.

В первом блоке 18 определения максимального кода входы l групп  соединены со входами записи регистров 63l

соединены со входами записи регистров 63l , прямые d-е

, прямые d-е  выходы которых соединены с первой группой входов дешифраторов 64d и с первыми входами элементом И

выходы которых соединены с первой группой входов дешифраторов 64d и с первыми входами элементом И  , первые инверсные выходы регистров 63l

, первые инверсные выходы регистров 63l соединены с первыми входами второй группы входов дешифратора 641, остальные инверсные выходы регистров 63l соединены со входами второй группы входов дешифраторов 64d

соединены с первыми входами второй группы входов дешифратора 641, остальные инверсные выходы регистров 63l соединены со входами второй группы входов дешифраторов 64d и с первыми группами входов (D-1)-х узлов анализа 66d

и с первыми группами входов (D-1)-х узлов анализа 66d , группы выходов первого дешифратора 641 соединена со второй группой входов узла анализа 661б группы выходов остальных дешифраторов 64d

, группы выходов первого дешифратора 641 соединена со второй группой входов узла анализа 661б группы выходов остальных дешифраторов 64d соединены с третьими группами входов узлов анализа 66d

соединены с третьими группами входов узлов анализа 66d , выходы d-х узлов анализа 66d

, выходы d-х узлов анализа 66d соединены со второй группой входов (d+1)-х узлов анализа 66j+1, L выходов (D-1)-го узла анализа 66D-1 соединены со вторыми входами элементов И

соединены со второй группой входов (d+1)-х узлов анализа 66j+1, L выходов (D-1)-го узла анализа 66D-1 соединены со вторыми входами элементов И  выходы элементов И 65

выходы элементов И 65 выходы которых соединены с выходами 19l блока выдачи максимального кода 18.

выходы которых соединены с выходами 19l блока выдачи максимального кода 18.

В пятом блоке памяти 20 входы  (f, p)-х групп информационных входов соединены с соответствующими входами (fp) - регистров 68fp

(f, p)-х групп информационных входов соединены с соответствующими входами (fp) - регистров 68fp группы, выходы которых соединены соответственно с выходами

группы, выходы которых соединены соответственно с выходами  (f, p)-й группы выходов блока 20.

(f, p)-й группы выходов блока 20.

Во втором блоке 22 определения максимального кода входы f групп информационных входов  соединены со входами записи регистров

соединены со входами записи регистров  , прямые d-е

, прямые d-е  выходы которых соединены с первой группой входов дешифраторов 70d

выходы которых соединены с первой группой входов дешифраторов 70d и с первыми входами элементов И

и с первыми входами элементов И  , первые инверсные выходы регистров 69f

, первые инверсные выходы регистров 69f соединены с первыми входами второй группы входов дешифратора 701, остальные инверсные выходы регистров 69f

соединены с первыми входами второй группы входов дешифратора 701, остальные инверсные выходы регистров 69f соединены со входами второй группы входов дешифраторов 70d

соединены со входами второй группы входов дешифраторов 70d и с первыми группами входов (D-1)-х узлов анализа 72d

и с первыми группами входов (D-1)-х узлов анализа 72d , группа выходов первого дешифратора 701 соединена со второй группой входов узла анализа 721, группы выходов остальных дешифраторов 70d

, группа выходов первого дешифратора 701 соединена со второй группой входов узла анализа 721, группы выходов остальных дешифраторов 70d соединены с третьими группами входов узлов анализа 72d,

соединены с третьими группами входов узлов анализа 72d,  выходы d-х узлов анализа 72d

выходы d-х узлов анализа 72d  соединены со второй группой входов (d+1)-х узлов анализа 72d+1 Выходы (D-1)-го узла анализа

соединены со второй группой входов (d+1)-х узлов анализа 72d+1 Выходы (D-1)-го узла анализа  соединены со вторыми входами элементов И

соединены со вторыми входами элементов И  , выходы элементов И 71

, выходы элементов И 71 выходы которых соединены с выходами 23f второго блока выдачи максимального кода 22.

выходы которых соединены с выходами 23f второго блока выдачи максимального кода 22.

В дешифраторах 64d  первого блока определения максимального кода 18 входы

первого блока определения максимального кода 18 входы  первой группы входов соединены с первыми входами соответствующих элементов ИЛИ

первой группы входов соединены с первыми входами соответствующих элементов ИЛИ  и со входами первых элементов И

и со входами первых элементов И  , выходы которых соединены со вторыми входами соответствующих элементов ИЛИ

, выходы которых соединены со вторыми входами соответствующих элементов ИЛИ  , входы

, входы  второй группы входов соединены со входами вторых элементов И

второй группы входов соединены со входами вторых элементов И  , выходы которых соединены с третьими входами соответствующих элементов ИЛИ

, выходы которых соединены с третьими входами соответствующих элементов ИЛИ  , выходы которых соединены с выходами

, выходы которых соединены с выходами  дешифраторов 64d,

дешифраторов 64d,  .

.

В узлах анализа 66d,  первого блока определения максимального кода 18 входы

первого блока определения максимального кода 18 входы  первой группы входов соединены с первыми входами соответствующих элементов И

первой группы входов соединены с первыми входами соответствующих элементов И  первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ

первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ  первой группы, выходы которых соединены с соответствующими q-и

первой группы, выходы которых соединены с соответствующими q-и  входами элементов ИЛИ 81l

входами элементов ИЛИ 81l второй группы, выходы которых соединены с первыми входами соответствующих элементов И

второй группы, выходы которых соединены с первыми входами соответствующих элементов И  второй группы и со входами соответствующих элементов НЕ 84

второй группы и со входами соответствующих элементов НЕ 84 третьей группы соответственно, выходы которых соединены первыми входами элементов ИЛИ

третьей группы соответственно, выходы которых соединены первыми входами элементов ИЛИ  третьей группы, выходы которых соединены с первыми входами элементов И

третьей группы, выходы которых соединены с первыми входами элементов И  четвертой группы, выходы которых соединены с выходами

четвертой группы, выходы которых соединены с выходами  d-го узла анализа 66d,

d-го узла анализа 66d,  входы второй группы входов

входы второй группы входов  соединены со вторыми входами элементов И

соединены со вторыми входами элементов И  первой группы, со вторыми входами элементов И

первой группы, со вторыми входами элементов И  четвертой группы и со входами элементов НЕ

четвертой группы и со входами элементов НЕ  второй группы, выходы которых соединены со вторыми входами элементов ИЛИ

второй группы, выходы которых соединены со вторыми входами элементов ИЛИ  первой группы, входы

первой группы, входы  третьей группы входов узлов анализа

третьей группы входов узлов анализа  соединены со вторыми входами элементов И

соединены со вторыми входами элементов И  третьей группы и со входами элементов НЕ

третьей группы и со входами элементов НЕ  третьей группы, выходы которых соединены со вторыми входами элементов И

третьей группы, выходы которых соединены со вторыми входами элементов И  второй группы, выходы которых соединены со вторыми входами элементов ИЛИ

второй группы, выходы которых соединены со вторыми входами элементов ИЛИ  третьей группы.

третьей группы.

В дешифраторах 70d второго устройства определения максимального кода 22 входы

второго устройства определения максимального кода 22 входы  первой группы входов соединены с первыми входами соответствующих элементов ИЛИ

первой группы входов соединены с первыми входами соответствующих элементов ИЛИ  и со входами первых элементов И 94d

и со входами первых элементов И 94d выходы которых соединены со вторыми входами соответствующих элементов ИЛИ

выходы которых соединены со вторыми входами соответствующих элементов ИЛИ  входы

входы  второй группы входов соединены со входами вторых элементов И

второй группы входов соединены со входами вторых элементов И  , выходы которых соединены с третьими входами соответствующих элементов ИЛИ

, выходы которых соединены с третьими входами соответствующих элементов ИЛИ  , выходы которых соединены с выходами

, выходы которых соединены с выходами  дешифраторов 70d

дешифраторов 70d .

.

В узлах анализа 72d второго устройства определения максимального кода 22 входы

второго устройства определения максимального кода 22 входы  первой группы входов соединены с первыми входами соответствующих элементов И

первой группы входов соединены с первыми входами соответствующих элементов И  первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ

первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ  первой группы, выходы которых соединены с соответствующими q-и

первой группы, выходы которых соединены с соответствующими q-и  входами элементов ИЛИ 100f

входами элементов ИЛИ 100f второй группы, выходы которых соединены с первыми входами соответствующих элементов И

второй группы, выходы которых соединены с первыми входами соответствующих элементов И  второй группы и со входами соответствующих элементов НЕ

второй группы и со входами соответствующих элементов НЕ  первой группы, выходы которых соединены с первыми входами элементов И

первой группы, выходы которых соединены с первыми входами элементов И  третьей группы соответственно, выходы которых соединены с первыми входами элементов ИЛИ

третьей группы соответственно, выходы которых соединены с первыми входами элементов ИЛИ  третьей группы, выходы которых соединены с первыми входами элементов И

третьей группы, выходы которых соединены с первыми входами элементов И  четвертой группы, выходы которых соединены с выходами

четвертой группы, выходы которых соединены с выходами  d-го узла анализа 72d

d-го узла анализа 72d , входы второй группы входов

, входы второй группы входов  соединены со вторыми входами элементов И

соединены со вторыми входами элементов И  первой группы, со вторыми входами элементов И

первой группы, со вторыми входами элементов И  четвертой группы и со входами элементов НЕ

четвертой группы и со входами элементов НЕ  второй группы, выходы которых соединены со вторыми входами элементов ИЛИ

второй группы, выходы которых соединены со вторыми входами элементов ИЛИ  первой группы, входы

первой группы, входы  третьей группы входов узлов анализа

третьей группы входов узлов анализа  соединены со вторыми входами элементов И

соединены со вторыми входами элементов И  третьей группы и со входами элементов НЕ

третьей группы и со входами элементов НЕ  третьей группы, выходы которых соединены со вторыми входами элементов И

третьей группы, выходы которых соединены со вторыми входами элементов И  второй группы, выходы которых соединены со вторыми входами элементов ИЛИ

второй группы, выходы которых соединены со вторыми входами элементов ИЛИ  третьей группы.

третьей группы.

Назначение нечеткого вероятностного автомата состоит в генерации сигналов состояний и выходных сигналов, а также генерации нечетких переменных, заданных на множествах состояний и выходов.

Формальная математическая модель нечеткого вероятностного автомата имеет вид: ,

,

{α,T(α),Z},{γ,T(γ),Y} ,

где

X, Y, Z - множества входных, выходных параметров и параметров состояний;  - множество условных вероятностей, определяющих пребывание вероятностного автомата в такте времени t в состоянии zt при условии подачи в этом такте на вход параметра xt и пребывания вероятностного автомата в предшествующем такте времени t-1 в состоянии zt-1;

- множество условных вероятностей, определяющих пребывание вероятностного автомата в такте времени t в состоянии zt при условии подачи в этом такте на вход параметра xt и пребывания вероятностного автомата в предшествующем такте времени t-1 в состоянии zt-1;  - множество условных вероятностей, определяющих наличие на выходе вероятностного автомата в такте времени t параметра yt при условии подачи на этом такте на вход параметра xt и нахождении нечеткого вероятностного автомата в предшествующем такте в состоянии zt; {α,T(α),Z} - задание лингвистической переменной α, , где α - наименование нечеткой переменной "выбор состояния", T (α) - терм-множество лингвистической переменной, Z - базовое множество; {α,T(α),Y} - задание лингвистической переменной γ, , где γ - наименование лингвистической переменной "выбор выходного сигнала", T (γ) - терм-множество лингвистической переменной, Y - базовое множество. Например, пусть

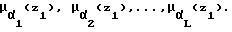

- множество условных вероятностей, определяющих наличие на выходе вероятностного автомата в такте времени t параметра yt при условии подачи на этом такте на вход параметра xt и нахождении нечеткого вероятностного автомата в предшествующем такте в состоянии zt; {α,T(α),Z} - задание лингвистической переменной α, , где α - наименование нечеткой переменной "выбор состояния", T (α) - терм-множество лингвистической переменной, Z - базовое множество; {α,T(α),Y} - задание лингвистической переменной γ, , где γ - наименование лингвистической переменной "выбор выходного сигнала", T (γ) - терм-множество лингвистической переменной, Y - базовое множество. Например, пусть  , где переменные: α1 - "выбор наилучших состояний", α2 - "выбор хороших состояний", α3 - "выбор плохих состояний", задаются тройками

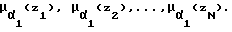

, где переменные: α1 - "выбор наилучших состояний", α2 - "выбор хороших состояний", α3 - "выбор плохих состояний", задаются тройками  - нечеткие подмножества на базовом множестве Z; γ1 - "выбор наилучшего выходного сигнала", γ2 -"выбор хорошего выходного сигнала", γ3 - "выбор плохого выходного сигнала" задаются набором

- нечеткие подмножества на базовом множестве Z; γ1 - "выбор наилучшего выходного сигнала", γ2 -"выбор хорошего выходного сигнала", γ3 - "выбор плохого выходного сигнала" задаются набором  - нечеткие множества, заданные на базовом множестве Y. Функции принадлежности

- нечеткие множества, заданные на базовом множестве Y. Функции принадлежности  задаются исходя из опроса экспертов.

задаются исходя из опроса экспертов.

При подготовке к работе нечеткого вероятностного автомата следует выполнить следующие операции.

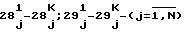

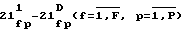

По установочным входам  записываются в регистры

записываются в регистры  (фиг. 1 и 3) первого блока памяти 2 коды приведенных матриц переходных вероятностей

(фиг. 1 и 3) первого блока памяти 2 коды приведенных матриц переходных вероятностей  . По установочным входам

. По установочным входам  записываются в регистры 30

записываются в регистры 30 . По установочным входам 17

. По установочным входам 17 (фиг. 1 и 12) значения

(фиг. 1 и 12) значения  степеней принадлежности нечетких переменных α1. . По установочным входам

степеней принадлежности нечетких переменных α1. . По установочным входам  записываются в регистры 68fp пятого блока памяти 20 значения

записываются в регистры 68fp пятого блока памяти 20 значения  степеней принадлежности нечетких переменных γf. . Матрицы

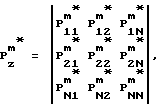

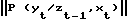

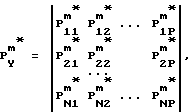

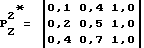

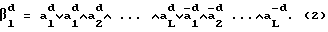

степеней принадлежности нечетких переменных γf. . Матрицы  имеют вид:

имеют вид:

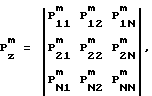

где

P

Приведенные матрицы  имеют вид:

имеют вид: ,

,

где

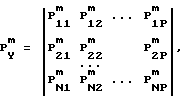

Матрицы вероятностей  задаются в следующем виде:

задаются в следующем виде: ,

,

где

P при условии, что в момент t-1 он находился в состоянии zi

при условии, что в момент t-1 он находился в состоянии zi .

.

Приведенные матрицы  задаются в следующем виде:

задаются в следующем виде: ,

,

где

При записи кодов в регистры 24, вероятность  матрицы P

матрицы P матрицы P

матрицы P

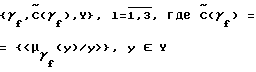

Информация о функции принадлежности  вводится по следующему правилу. Мощность множества

вводится по следующему правилу. Мощность множества  , а диапазон (0,1) значений функций принадлежности квантуется (на фиг. 20 квантование показано в семи уровнях).

, а диапазон (0,1) значений функций принадлежности квантуется (на фиг. 20 квантование показано в семи уровнях).

Для каждого состояния zi имеется L значений функций принадлежности

имеется L значений функций принадлежности .

.

Для рассматриваемого примера L = 3.

В регистры 62l1 - 62lN четвертого блока памяти 26 будут записаны коды  .

.

Аналогичные рассуждения справедливы и для записи квантованных значений функций принадлежности  .

.

В регистры 68f1 - 68fp пятого блока памяти 20  будут занесены коды

будут занесены коды  .

.

Функционирует нечеткий вероятностный автомат по следующему алгоритму. Синхронизация работы нечеткого вероятностного автомата осуществляется генератором 13 тактовых импульсов. По входам 11 - 1M подаются входные сигналы xt, управляющие работой нечеткого вероятностного автомата.

В третьем блоке памяти хранится состояние автомата.

При поступлении на вход 1m в момент времени t управляющего воздействия xm в зависимости от того, в каком состоянии zi был автомат в момент t-1, т. е. в зависимости от сигнала на выходе 8i, поступающего с третьего блока памяти 7 на вход 8i блока памяти 2 и вход 8i блока памяти 3, на выходы блока памяти 2 подаются коды i-q строки матрицы  , и ан выходы второго блока памяти 3 подаются коды i-й строки матрицы

, и ан выходы второго блока памяти 3 подаются коды i-й строки матрицы  . Происходит это следующим образом. Так как в блоке 2 имеется потенциал на входах 8i, 2m, а также на входе 26, то открыты будут элементы И (25

. Происходит это следующим образом. Так как в блоке 2 имеется потенциал на входах 8i, 2m, а также на входе 26, то открыты будут элементы И (25

Таким же образом и во втором блоке памяти 3 коды вероятностей регистров 30i1 - 30ip через открытые элементы И (31

Первым 14 и вторым 15 блоками генерации случайного кода вырабатываются коды чисел, равномерно распределенные на интервале (0,1).

Блок 6 выбора состояния в соответствии с правилом испытания в схеме случайных событий вырабатывает текущее состояние zt. Также и в блоке 10 выбора выходного сигнала в соответствии с правилом испытания в схеме случайных событий вырабатывается выходной сигнал yt. Определенные для времени t сигналы zt и yt подаются на входы 8 коммутатора 9 и входы 11 коммутатора 12 соответственно.

В зависимости от поступившего сигнала zi в момент времени t, с выходов первого коммутатора 9 поступают на блок определения максимального кода соответствующие сигналу zi значения степеней принадлежности нечетких переменных. Блок 18 определения максимального кода анализирует значения поступивших на его вход кодовых комбинаций, и на выход 19l поступает сигнал, индекс l которого соответствует наибольшему значению степени принадлежности переменной α1. .

поступает сигнал, индекс l которого соответствует наибольшему значению степени принадлежности переменной α1. .

При поступлении в момент времени t на вход 11p второго коммутатора 12 выходного сигнала yP на выходы коммутатора 12 поступают значения степеней принадлежности нечетких переменных

второго коммутатора 12 выходного сигнала yP на выходы коммутатора 12 поступают значения степеней принадлежности нечетких переменных  для элемента yp базового множества Y. Далее блок определения максимального кода анализирует поступившие кодовые комбинации, и на один из f выходов поступает единичный сигнал, соответствующий наибольшей по величине кодовой комбинации.

для элемента yp базового множества Y. Далее блок определения максимального кода анализирует поступившие кодовые комбинации, и на один из f выходов поступает единичный сигнал, соответствующий наибольшей по величине кодовой комбинации.

Рассмотрим работу нечеткого вероятностного автомата более подробно.

Пусть, например, известно, что множество состояний имеет три элемента Z = { z1, z2, z3}, множество выходных сигналов также имеет три элемента Y = { y1, y2, y3}, и пусть в момент времени t на вход 12 подан управляющий сигнал x2. Матрица  переходных вероятностей пусть имеет вид:

переходных вероятностей пусть имеет вид:

Регистры  предназначены для хранения K = 8-разрядных значений величин вероятностей. Пусть в момент времени (t-1) автомат находился в состоянии z1, поэтому со входа 81 поступил единичный сигнал, что позволило считать содержимое первой строки матрицы

предназначены для хранения K = 8-разрядных значений величин вероятностей. Пусть в момент времени (t-1) автомат находился в состоянии z1, поэтому со входа 81 поступил единичный сигнал, что позволило считать содержимое первой строки матрицы  при поступлении синхронизирующего сигнала от генератора 13 тактовых импульсов по входу 26 с регистров 24

при поступлении синхронизирующего сигнала от генератора 13 тактовых импульсов по входу 26 с регистров 24

Т. е. на выходах 29

Схемная реализация второго блкоа памяти 3 идентична схемной реализации первого блока памяти 2. Работа блока 3 будет протекать таким же образом, как и работа блока 2.

Первый блок генерации случайного кода 14 работает следующим образом. Случайные импульсы от генератора 55 пуассоновского потока импульсов поступают через открытый (в интервалы времени, соответствующие нахождению автомата в i-х  состояниях) первый элемент И 52 на синхронизирующий вход циклически замкнутого регистра 56 сдвига, в одном из разрядов которого записана единица, а в остальных нули. Интенсивность случайных импульсов генератора 55 значительно превышает частоту опроса по входу 51. Тогда записанная единица многократно "обегает" регистр 56 сдвига между моментами опроса его состояний по входу 51 импульсами генератора 13 тактовых импульсов. При таком условии единица будет находиться в момент опроса на любом из выходов регистра 56 сдвига с вероятностью, равной единице, деленной на число выходов регистра 56. Кодопреобразователь преобразует код на одно сочетание в двоичный код числа, равновероятно распределенного на интервале (0,1).

состояниях) первый элемент И 52 на синхронизирующий вход циклически замкнутого регистра 56 сдвига, в одном из разрядов которого записана единица, а в остальных нули. Интенсивность случайных импульсов генератора 55 значительно превышает частоту опроса по входу 51. Тогда записанная единица многократно "обегает" регистр 56 сдвига между моментами опроса его состояний по входу 51 импульсами генератора 13 тактовых импульсов. При таком условии единица будет находиться в момент опроса на любом из выходов регистра 56 сдвига с вероятностью, равной единице, деленной на число выходов регистра 56. Кодопреобразователь преобразует код на одно сочетание в двоичный код числа, равновероятно распределенного на интервале (0,1).

Аналогичным образом работает и второй блок генерации случайного кода 15.

В блоке 6 выбора состояний (фиг. 5) каждый i-й  узел сравнения 35i анализирует кодовую комбинацию, поступившую со входов 29

узел сравнения 35i анализирует кодовую комбинацию, поступившую со входов 29

Если значение кодовой комбинации, поступающей по входам 361 - 36K оказывается меньше либо равно, чем значение, поступающее по i-й группе входов 29 поступает нулевой сигнал, закрывающий эти элементы. Таким образом, блок выбора состояний 6 определяет состояние zi, в которое переходит нечеткий вероятностный автомат в момент времени t. Допустим, что в нашем случае единичный сигнал поступил на выход 373 , и это означает, что автомат перешел в момент времени t в состояние z3.

поступает нулевой сигнал, закрывающий эти элементы. Таким образом, блок выбора состояний 6 определяет состояние zi, в которое переходит нечеткий вероятностный автомат в момент времени t. Допустим, что в нашем случае единичный сигнал поступил на выход 373 , и это означает, что автомат перешел в момент времени t в состояние z3.

Третий блок памяти (см. фиг.6) задерживает единичный сигнал zi, поступивший по входу 37i от блока выбора состояний 6, на один такт времени генератора 13, и выдает затем его на выход 8i. Это происходит следующим образом. Единичный сигнал, поданный на вход 373, перебрасывает триггер 383 в единичное состояние. Потенциал с единичного выхода триггера 383 сбрасывает триггеры 381, 382 в нулевое состояние через элементы ИЛИ 391, 392 и подается на выход 83 нечеткого вероятностного автомата и вход 83 коммутатора 9.

Аналогично блоку выбора состояний 6 функционирует блок выбора выходного сигнала 10. Определенный блоком 10 выходной сигнал Yp подается на выход 11p нечеткого автомата и вход 11p второго коммутатора 12.

При поступлении сигнала zi,  , в момент времени t c выхода 8i третьего блока памяти 7 происходит считывание L D-арзрядных значений функций принадлежности из регистров первого блока памяти 6. Потенциал на выходе 8i откроет элементы И

, в момент времени t c выхода 8i третьего блока памяти 7 происходит считывание L D-арзрядных значений функций принадлежности из регистров первого блока памяти 6. Потенциал на выходе 8i откроет элементы И  . Происходит считывание значений содержимых регистров 62li, которое с выходов коммутатора 9 поступает на входы первого блока 18 определения максимального кода в виде L групп D-разрядных кодов значений функции принадлежности

. Происходит считывание значений содержимых регистров 62li, которое с выходов коммутатора 9 поступает на входы первого блока 18 определения максимального кода в виде L групп D-разрядных кодов значений функции принадлежности  нечетких переменных α1 в точке zi.

нечетких переменных α1 в точке zi.

При поступлении сигнала Yp,  от блока выбора выходного сигнала 10 в момент времени t происходит считывание F D-разрядных значений функций принадлежности

от блока выбора выходного сигнала 10 в момент времени t происходит считывание F D-разрядных значений функций принадлежности  из регистров второго блока памяти 20. Потенциал на выходе 11p откроет элементы И

из регистров второго блока памяти 20. Потенциал на выходе 11p откроет элементы И  . Содержимое регистров 68fr, через коммутатор 12 поступает на входы второго блока 22 определения максимального кода в виде F групп D-разрядных кодов значений функции принадлежности

. Содержимое регистров 68fr, через коммутатор 12 поступает на входы второго блока 22 определения максимального кода в виде F групп D-разрядных кодов значений функции принадлежности  нечетких переменных γf в точке Yp.

нечетких переменных γf в точке Yp.

Блок 18 определения максимального кода анализирует поступающие с коммутатора 9 L D-разрядных кодовых комбинаций, являющихся соответственно степенями принадлежности нечетких переменных  , т.е. устанавливает, какая из нечетких переменных имеет большее значение функции принадлежности для текущего состояния, и подает на выход сигнал о номере наибольшей по величине кодовой комбинации.

, т.е. устанавливает, какая из нечетких переменных имеет большее значение функции принадлежности для текущего состояния, и подает на выход сигнал о номере наибольшей по величине кодовой комбинации.

На входные шины 431 - 43L (фиг.13) подается L кодовых комбинаций, из которых устройство определения максимального кода должно выбрать максимальную по величине кодовую комбинацию, причем, если в поступающих по входам 431 - 43L кодах имеется k одинаковых по величине и максимальных среди L кодовых комбинаций, то такой случай также должен быть распознан. Каждая 1-я  кодовая комбинация подается по входным шинам 43

кодовая комбинация подается по входным шинам 43

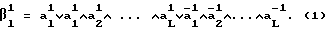

Алгоритм работы блока определения максимального кода состоит в последовательном анализе параллельных (одноименных) разрядов кодовых комбинаций записанных в регистры 631 - 63L с последовательным выявлением больших по величине кодов в параллельных (одноименных) разрядах, начиная со старшего разряда вплоть до младшего. Причем анализ параллельных разрядов кодовых комбинаций регистров 63 производится как дешифраторами состояний 64, так и узлами анализа 66. Выявление кодовых комбинаций, больших по величине, чем наименьшее, производится первым дешифратором состояний 641 и узлами анализа 661 - 66D-1 , причем последний узел анализа 66D-1 выявляет максимальные (одну или несколько) кодовые комбинации из N, записанные в регистры 63.

Сущность алгоритма работы блока определения максимального кода состоит в следующем. Вначале рассмотрим параллельные старшие разряды a выходе 79

выходе 79 .

.

Для определения сигнала на l-м выходе  d-го дешифратора 64d

d-го дешифратора 64d , исходя из метода математической индукции, можно записать следующую логическую функцию

, исходя из метода математической индукции, можно записать следующую логическую функцию .

.

Равенство  является достаточным условием, но не обходимым для определения, что в регистре 63l может быть максимальное число, т.е. дешифраторами 64d

является достаточным условием, но не обходимым для определения, что в регистре 63l может быть максимальное число, т.е. дешифраторами 64d выделяются регистры 63l

выделяются регистры 63l , в которых символы al равны единице. Первым определяющим состояние l-го выхода 88

, в которых символы al равны единице. Первым определяющим состояние l-го выхода 88

Причем  всегда равна нулю, если G

всегда равна нулю, если G , либо одна из (L-1) дезъюнкций, входящих в конъюктивную нормальную форму (2), равны нулю.

, либо одна из (L-1) дезъюнкций, входящих в конъюктивную нормальную форму (2), равны нулю.

Функцию  определяющую состояние l-го выхода d-го узла анализа 66d (единицу или ноль на выходе 88

определяющую состояние l-го выхода d-го узла анализа 66d (единицу или ноль на выходе 88

Из уравнений (1), (2) и (3) следует, что  всегда равно нулю, если либо β

всегда равно нулю, если либо β

С выходов  узла анализа 66D-1 поступает кодовая комбинация G

узла анализа 66D-1 поступает кодовая комбинация G

Второй блок определения максимального кода 22 работает так же, как и первый блок определения максимального кода 18, поэтому подробное описание его работы не проводится.

Итак, на выходах 19l первого блока определения максимального кода 18 будет зафиксирован потенциал, определяющий индекс l нечеткой переменной α1, , наиболее предпочтительной для текущего состояния. На выходах 23f второго блока определения максимального кода 22 будет потенциал, определяющий индекс f нечеткой переменной γf, , наиболее предпочтительной для текущего состояния.

Технико-экономическую эффективность предлагаемого устройства по отношению к известному (а.с.СССР N 1200297, кл. G 06 F 15/20, 1985), возможно определить из расширения функциональных возможностей, а именно, предлагаемое устройство осуществляет генерацию не только состояний, выходных сигналов, но и лингвистических переменных, заданных на базовых множествах состояний и выходных сигналов. Функции принадлежности нечетких переменных задаются методом экспертного опроса. Функции переходов и выходов автомата задаются в виде рандоминизированных правил.

Если оценить затраты на разработку и изготовление предлагаемого устройства через величину C1 , затраты на проведение исследований - через величину C2, то суммарные затраты на решение задачи определим

CI = C1 + C2.

При применении известного устройства для решения задач управления необходимы затраты на изготовление специальных дополнительных приборов и проведение натурных экспериментов. Эти затраты определим величиной CN. Отметим, что затраты CN существенно будут превышать величину CI, так как проведение натурных испытаний уже требует значительных экономических расходов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО ПРИНЯТИЯ НЕЧЕТКИХ РЕШЕНИЙ | 1993 |

|

RU2054708C1 |

| Вероятностный автомат | 1984 |

|

SU1200297A1 |

| Устройство для моделирования канала связи | 1983 |

|

SU1132294A1 |

| Устройство для моделирования канала передачи дискретной информации | 1985 |

|

SU1273943A1 |

| Вероятностный автомат | 1988 |

|

SU1608684A1 |

| Вероятностный автомат | 1982 |

|

SU1045232A1 |

| Вероятностный автомат | 1982 |

|

SU1108455A1 |

| Вероятностный автомат | 1983 |

|

SU1200296A2 |

Изобретение относится к вычислительной технике и системам управления, может быть применено для построения адаптивных нечетких регуляторов для решения задач управления объектами, математическая модель которых априорно не определена, а цель функционирования выражена в нечетких понятиях. Целью изобретения является расширение функциональных возможностей. Вероятностный автомат содержит: первый блок памяти 2, второй блок памяти 3, блок выбора состояний 6, третий блок памяти 7, первый коммутатор 9, блок выбора выходного сигнала 10, второй коммутатор 12, генератор тактовых импульсов 13, первый блок генерации случайного кода 14, второй блок генерации случайного кода 15, четвертый блок памяти 16, первый блок определения максимального кода 18, пятый блок памяти 20, второй блок определения максимального кода 22. 6 з.п. ф-лы, 21 ил.

групп установочных входов соединены с входами записи соответствующих (i, j, m)-х регистров, выходы которых соединены с первыми входами соответствующих элементов (i, j, m)-х групп элементов И, вторые входы элементов И объединены и соединены с тактовым входом блока памяти, третьи входы элементов И каждых из m групп объединены и соединены с m-ми входами группы первых управляющих входов блока, четвертые входы элементов И (im)-й группы объединены и соединены с i-и входом второй группы управляющих входов блока, выходы элементов И - с соответствующими входами N x M групп элементов ИЛИ, выходы которых соединены соответственно с выходами N групп выходов блока.

групп установочных входов соединены с входами записи соответствующих (i, j, m)-х регистров, выходы которых соединены с первыми входами соответствующих элементов (i, j, m)-х групп элементов И, вторые входы элементов И объединены и соединены с тактовым входом блока памяти, третьи входы элементов И каждых из m групп объединены и соединены с m-ми входами группы первых управляющих входов блока, четвертые входы элементов И (im)-й группы объединены и соединены с i-и входом второй группы управляющих входов блока, выходы элементов И - с соответствующими входами N x M групп элементов ИЛИ, выходы которых соединены соответственно с выходами N групп выходов блока. первой группы информационных входов соединения с входами первых групп входов j-х узлов сравнения, одноименные входы вторых групп входов которых объединены и соединены с соответствующими k входами второй группы информационных входов блока, выход первого узла сравнения соединен с первым выходом блока и с первыми инверсными входами элементов И, выходы i-х узлов сравнения

первой группы информационных входов соединения с входами первых групп входов j-х узлов сравнения, одноименные входы вторых групп входов которых объединены и соединены с соответствующими k входами второй группы информационных входов блока, выход первого узла сравнения соединен с первым выходом блока и с первыми инверсными входами элементов И, выходы i-х узлов сравнения  соединены с прямыми входами соответствующих (i - 1)-х элементов И и с i-ми инверсными входами i-х элементов И, выходы которых соединены с (i + 1)-ми выходами блока.

соединены с прямыми входами соответствующих (i - 1)-х элементов И и с i-ми инверсными входами i-х элементов И, выходы которых соединены с (i + 1)-ми выходами блока. первых групп информационных входов соединены с входами первых групп входов p-х узлов сравнения, одноименные входы вторых групп входов которых объединены и соединены с соответствующими k входами второй группы информационных входов блока, выход первого узла сравнения соединен с первым выходом блока и с первыми инверсными входами элементов И, выходы p-х узлов сравнения

первых групп информационных входов соединены с входами первых групп входов p-х узлов сравнения, одноименные входы вторых групп входов которых объединены и соединены с соответствующими k входами второй группы информационных входов блока, выход первого узла сравнения соединен с первым выходом блока и с первыми инверсными входами элементов И, выходы p-х узлов сравнения  соединены с прямыми входами соответствующих (p - 1)-х элементов И и с p-ми инверсными входами p-х элементов И, выходы которых соединены с (p + 1)-ми выходами блока.

соединены с прямыми входами соответствующих (p - 1)-х элементов И и с p-ми инверсными входами p-х элементов И, выходы которых соединены с (p + 1)-ми выходами блока. соединены с входами записи l-х регистров, прямые d-е выходы которых соединены с первой группой входов d-х дешифраторов и с первыми входами d-х элементов И l-й группы, первые инверсные выходы l-х регистров соединены с первыми входами второй группы входов l-х дешифраторов, остальные инверсные выходы l-х регистров соединены с входами второй группы входов d-х дешифраторов

соединены с входами записи l-х регистров, прямые d-е выходы которых соединены с первой группой входов d-х дешифраторов и с первыми входами d-х элементов И l-й группы, первые инверсные выходы l-х регистров соединены с первыми входами второй группы входов l-х дешифраторов, остальные инверсные выходы l-х регистров соединены с входами второй группы входов d-х дешифраторов  и с первыми группами входов (d - 1)-х узлов анализа, группа выходов первого дешифратора соединена с второй группой входов первого узла анализа, группы выходов остальных d-х дешифраторов

и с первыми группами входов (d - 1)-х узлов анализа, группа выходов первого дешифратора соединена с второй группой входов первого узла анализа, группы выходов остальных d-х дешифраторов  соединены с третьими группами входов d-х узлов анализа

соединены с третьими группами входов d-х узлов анализа  выходы d-х узлов анализа

выходы d-х узлов анализа  соединены с второй группой входов (d + 1)-х узлов анализа, L выходов (d - 1)-го узла анализа соединены с вторыми входами d-х элементов И l-й группы, выходы элементов И l-й группы соединены с входами l-х элементов ИЛИ, выходы которых соединены с l-ми выходами блока определения максимального кода.

соединены с второй группой входов (d + 1)-х узлов анализа, L выходов (d - 1)-го узла анализа соединены с вторыми входами d-х элементов И l-й группы, выходы элементов И l-й группы соединены с входами l-х элементов ИЛИ, выходы которых соединены с l-ми выходами блока определения максимального кода.

| SU, авторское свидетельство, 1045232, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1200297, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-04-27—Публикация

1995-03-31—Подача