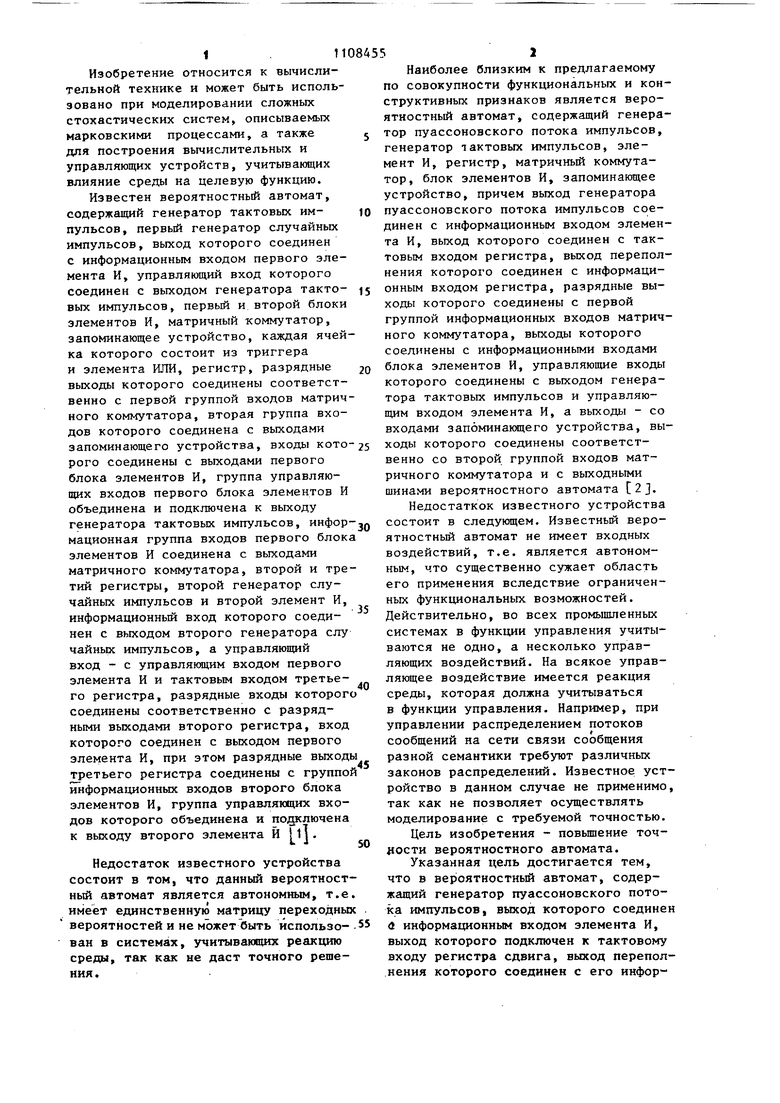

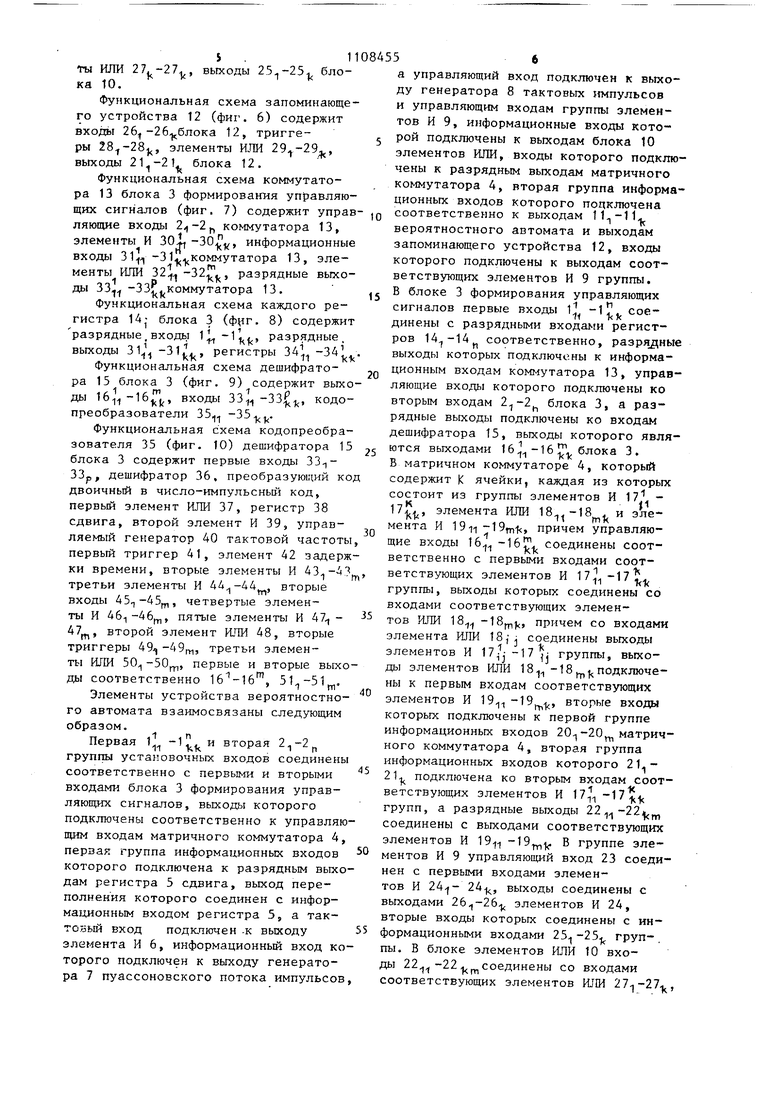

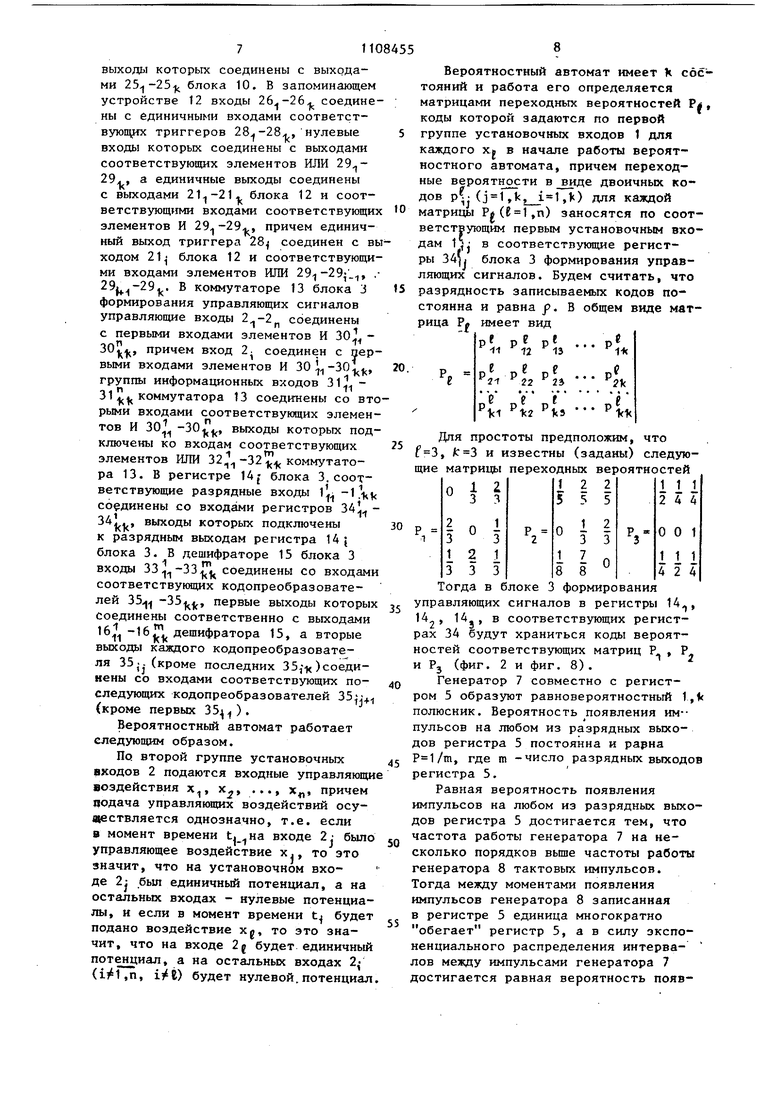

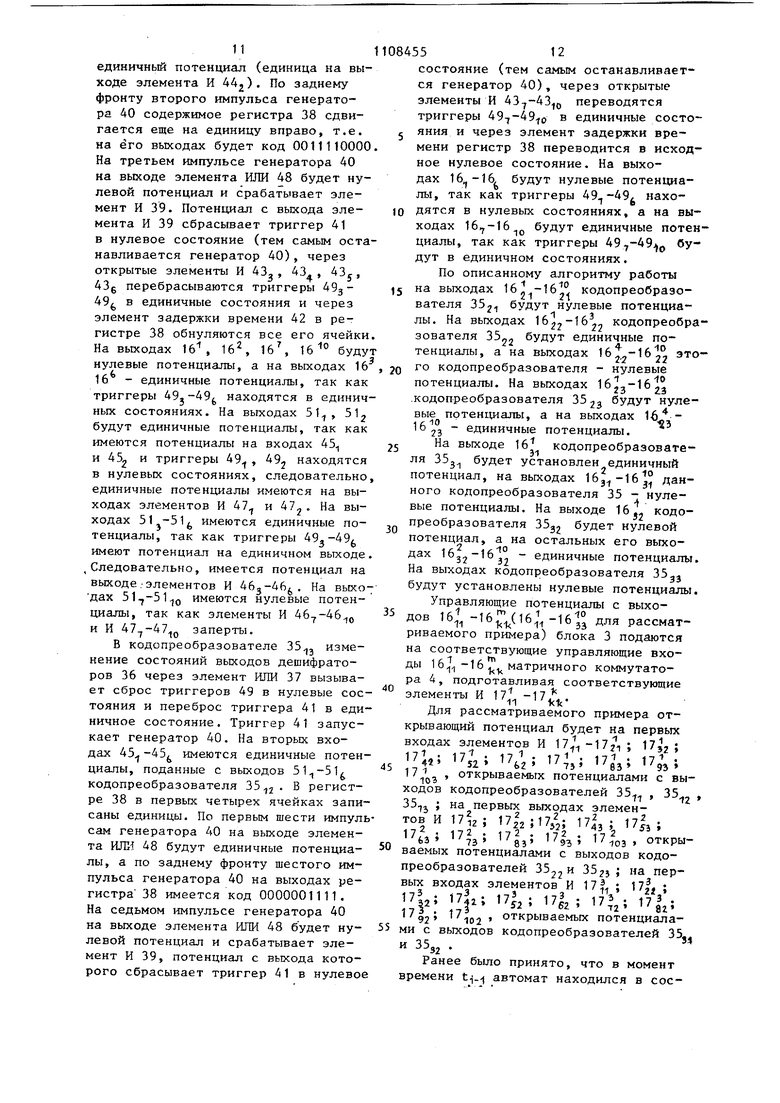

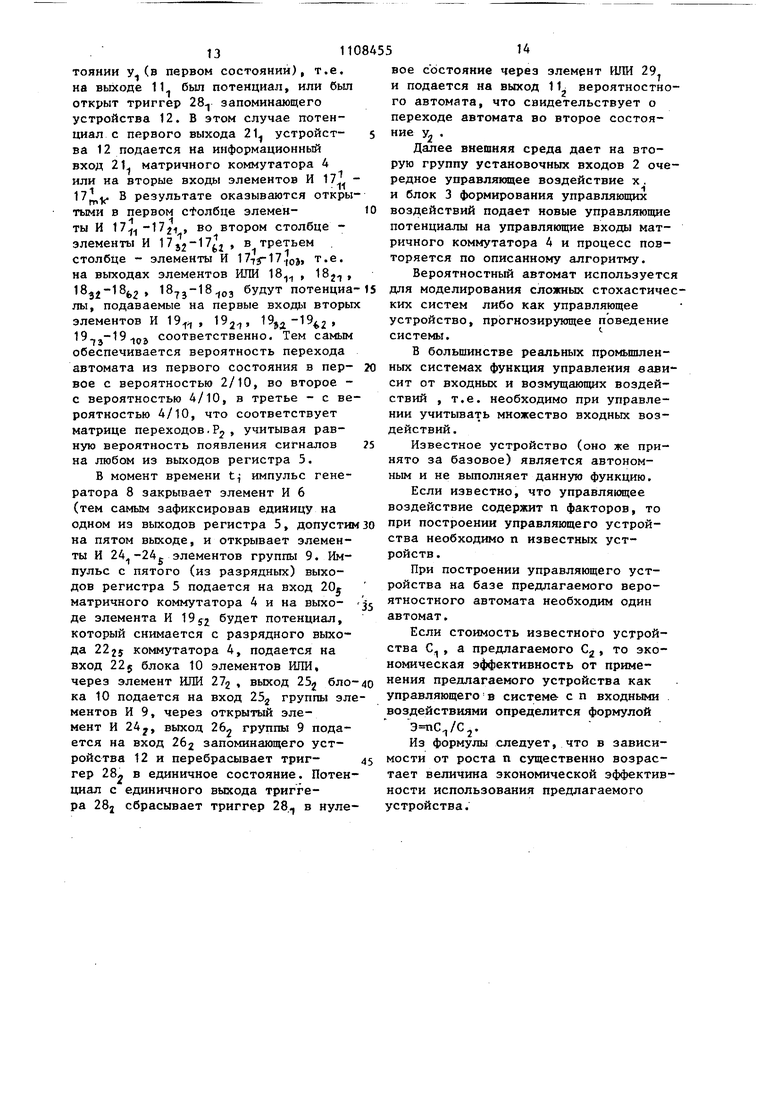

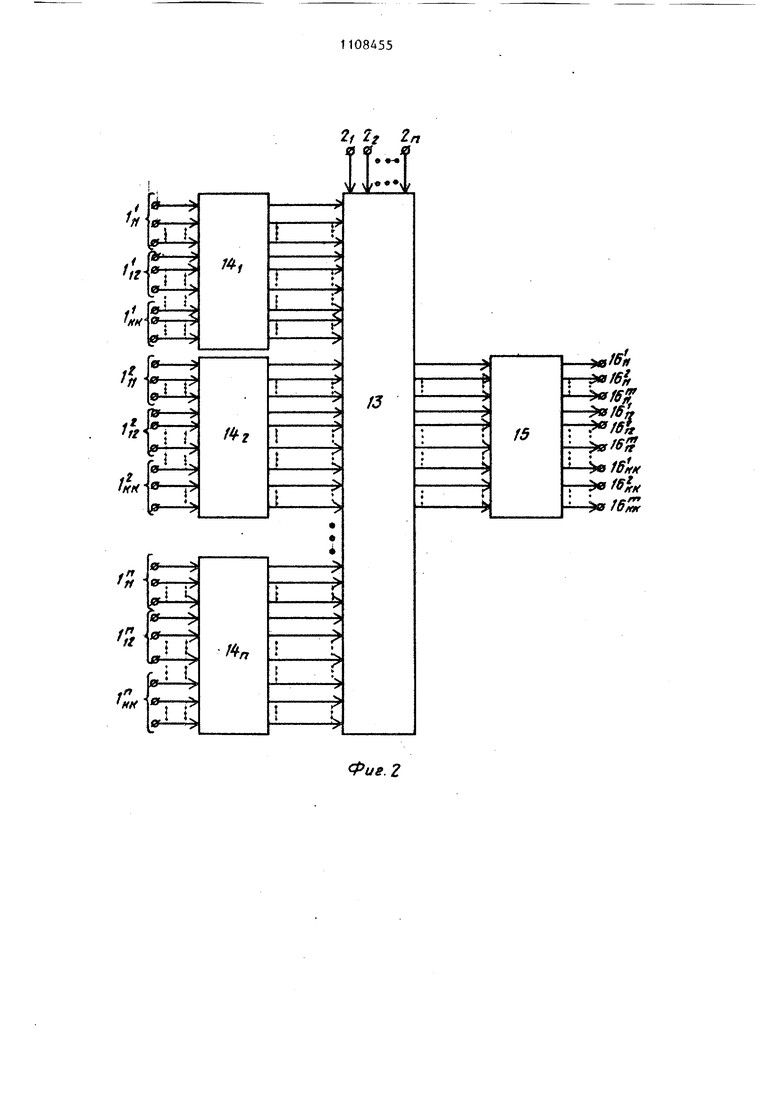

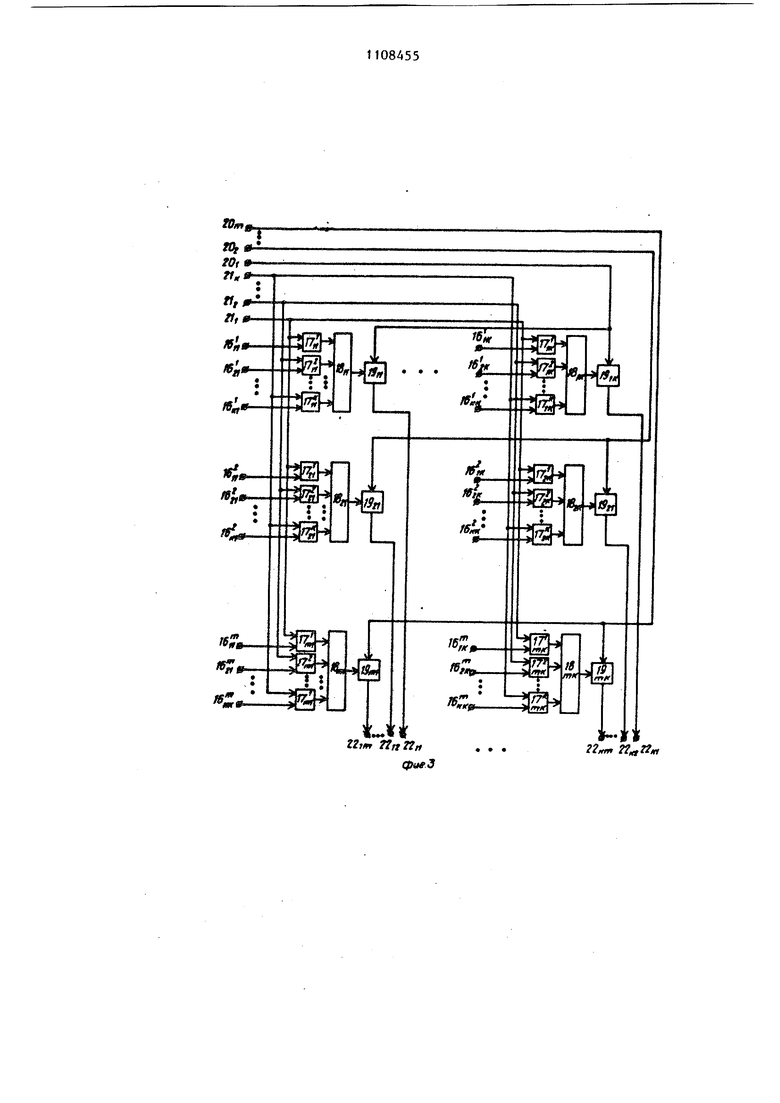

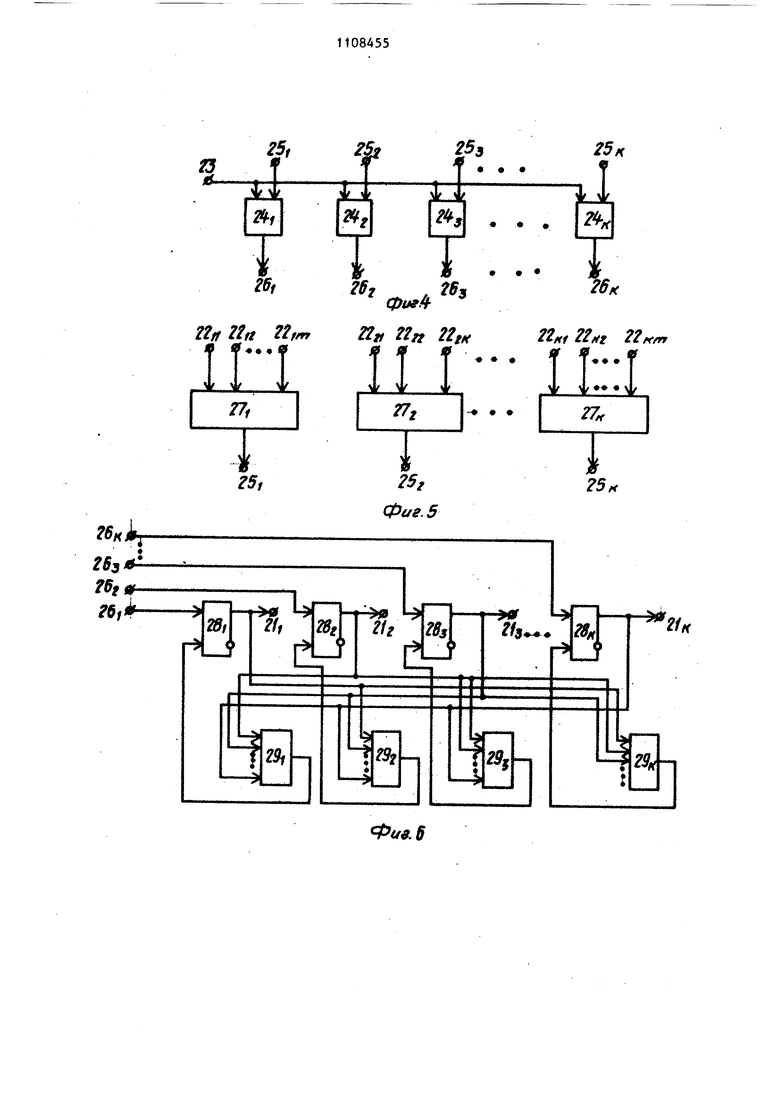

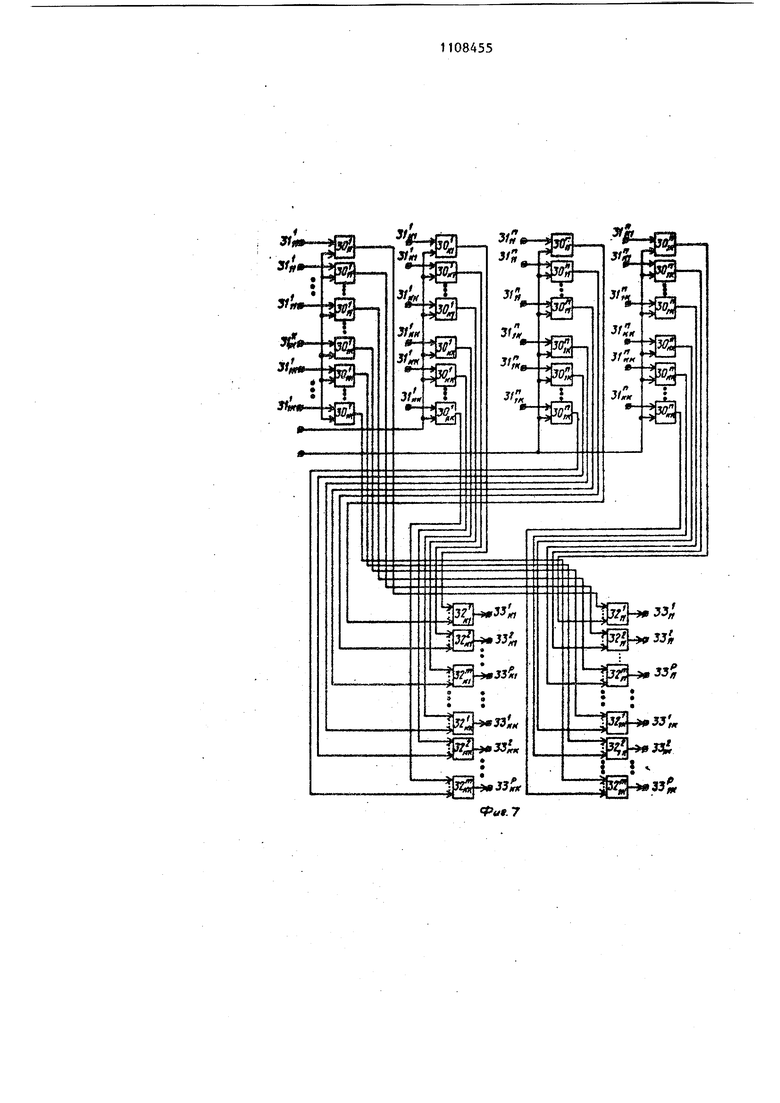

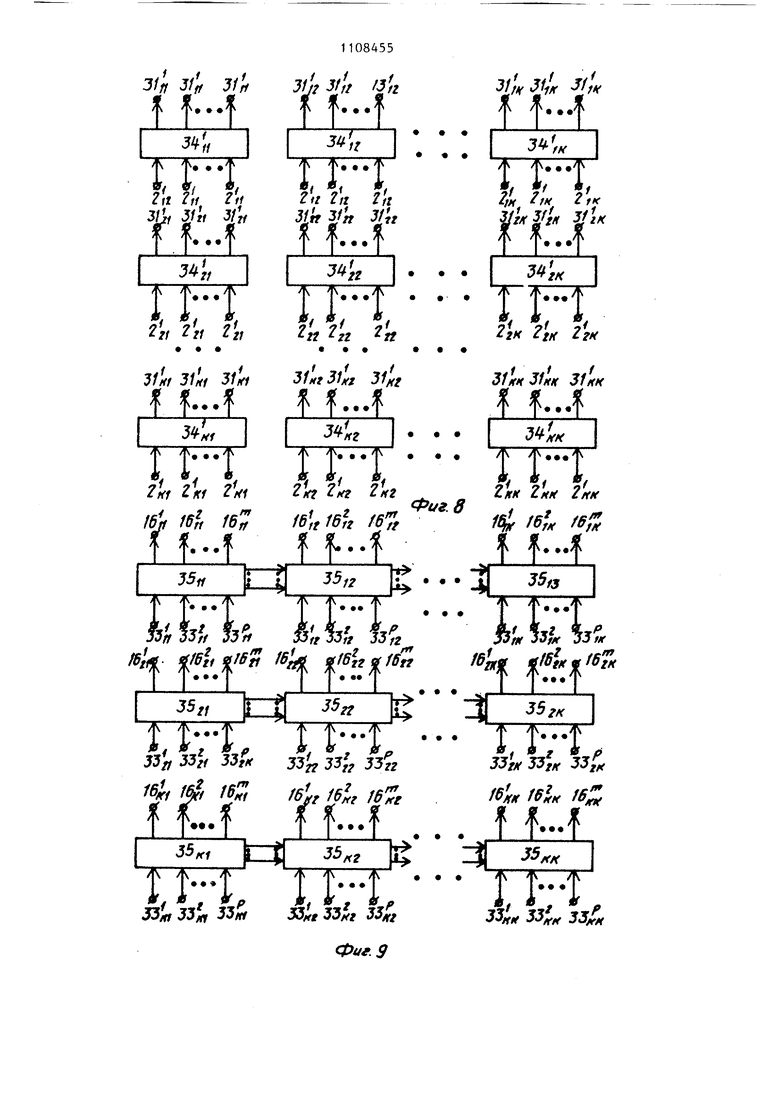

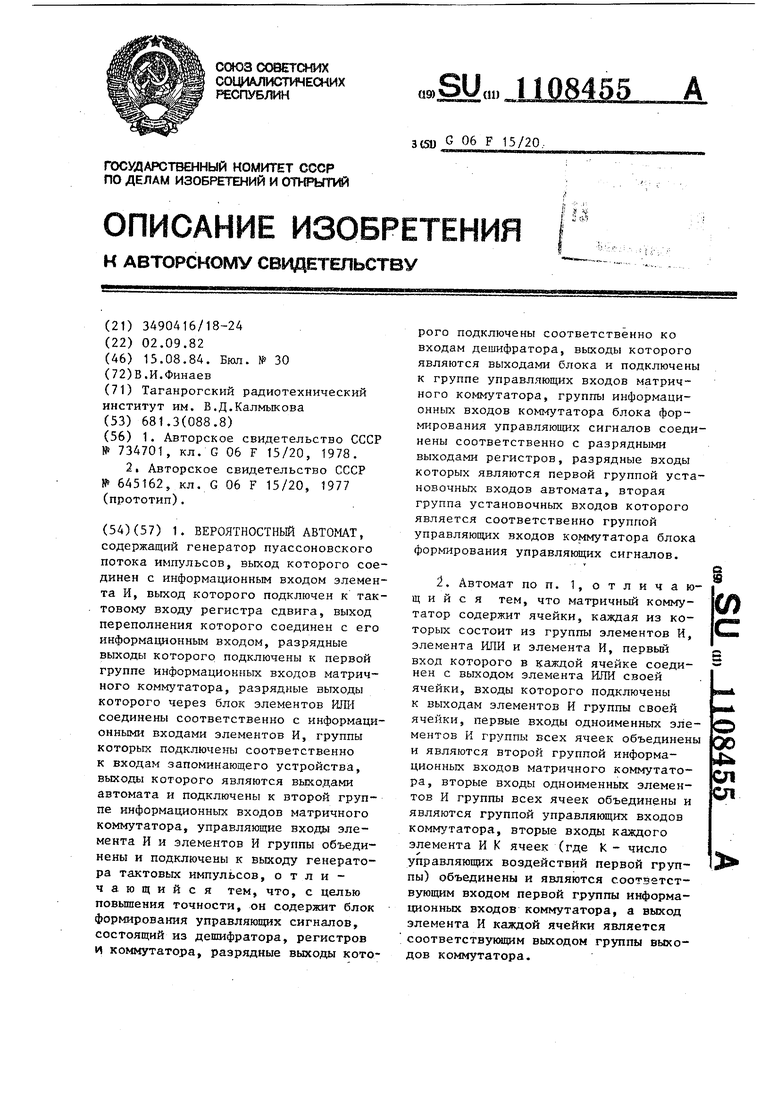

Изобретение относится к вычислительной технике и может быть использовано при моделировании сложных стохастических систем, описываемых марковскими процессами, а также для построения вычислительных и управляющих устройств, учитывающих влияние среды на целевую функцию. Известен вероятностный автомат, содержащий генератор тактовых импульсов, первый генератор случайных импульсов, выход которого соединен с информационным входом первого элемента И, управляющий вход которого соединен с выходом генератора тактовых импульсов, первый и второй блоки элементов И, матричный коммутатор, запоминающее устройство, каждая ячей ка которого состоит из триггера и элемента ИЛИ, регистр, разрядные выходы которого соединены соответственно с первой группой входов матрич ного коммутатора, вторая группа входов которого соединена с выходами запоминающего устройства, входы кото рого соединены с выходами первого блока элементов И, группа управляющих входов первого блока элементов И объединена и подключена к выходу генератора тактовых импульсов, инфор мационная группа входов первого блок элементов И соединена с выходами матричного коммутатора, второй и тре тий регистры, второй генератор случайных импульсов и второй элемент И, информационный вход которого соединен с выходом второго генератора слу чайньрс импульсов, а управляющий вход - с управлякнцим входом первого элемента И и тактовым входом третьего регистра, разрядные входы которог соединены соответственно с разрядными выходами второго регистра, вход которого соединен с выходом первого элемента И, при этом разрядные выход третьего регистра соединены с группо информационных входов второго блока элементов И, группа управляющих входов которого объединена и подключена к выходу второго элемента И ill. Недостаток известного устройства состоит в том, что данный вероятност ный автомат является автономным, т.е имеет единственную матрицу переходны вероятностей и не может быть йспользован в системах, учитывающих реакцию среды, так как не даст точного решения . Наиболее близким к предлагаемому по совокупности функциональных и конструктивных признаков является вероятностный автомат, содержащий генератор пуассоновского потока импульсов, генератор тактовых импульсов, элемент И, регистр, матричный коммутатор, блок элементов И, запоминающее устройство, причем выход генератора пуассоновского потока импульсов соединен с информационным входом элемента И, выход которого соединен с тактовым входом регистра, выход переполнения которого соединен с информационным входом регистра, разрядные выходы которого соединены с первой группой информационных входов матричного коммутатора, выходы которого соединены с информационными входами блока элементов И, управляющие входы которого соединены с выходом генератора тактовых импульсов и управляющим входом элемента И, а выходы - со входами запоминающего устройства, выходы которого соединены соответственно со второй группой входов матричного коммутатора и с выходными шинами вероятностного автомата 2J. Недостаткок известного устройства состоит в следующем. Известный вероятностный автомат не имеет входных воздействий, т.е. является автономным, что существенно сужает область его применения вследствие ограниченных функциональных возможностей. Действительно, во всех промыщленных системах в функции управления учитываются не одно, а несколько управляющих воздействий. На всякое управляющее воздействие имеется реакция среды, которая должна учитываться в функции управления. Например, при управлении распределением потоков сообщений на сети связи сообщения разной семантики требуют различных законов распределений. Известное; устройство в данном случае не применимо, так как не позволяет осуществлять моделирование с требуемой точностью. Цель изобретения - повьппение точлости вероятностного автомата. Указанная цель достигается тем, что в вероятностный автомат, содержащий генератор пуассоновского потока импульсов, выход которого соединен в информационным входом элемента И, выход которого подключен к тактовому входу регистра сдвига, выход переполнения которого соединен с его информационным входом, разрядные выходы которого подключены к первой группе информационньк входов матричного ком мутатора, разрядные выходы которого через блок элементов ИЛИ соединены соотйетственно с информационными вхо дами элементов И, группы которых под ключены соответственно к входам запо минающего устройства, выходы которого являются выходами автомата и подключены к второй группе информационных входов матричного коммутатора, управляющие входы элемента И и элементов И группы объединены и подключены к выходу генератора тактовых им пульсов, дополнительно введен блок формирования управляющих сигналов, состоящий из дешифратора, регистров и коммутатора, разрядные выходы кото рого подключены соответственно ко входам дешифратора, выходы которого являются вьгходами блока и подключены к группе управляющих входов матричного коммутатора, группы информационных входов коммутатора блока форми рования управляющих сигналов соедине ны соответственно с разрядными выходами регистров, разрядные входы которых являются первой группой установочных входов автомата, вторая гру па установочных входов которого является соответственно группой управлякнцих входов коммутатора блока формирования управляющих сигналов. Кроме того, матричный коммутатор содержит ячейки, каждая из которых состоит из группы элементов И, элемента ИЛИ и элемента И, первый вход которого в каждой ячейке соединен с выходом элемента ИЛИ своей ячейки, входы которого подключены к выходам элементов И группы своей ячейки, пер вые входы одноименных элементов И группы всех ячеек объединены и являются второй группой информационных входов матричного коммутатора, вторы входы одноименных элементов И группы всех ячеек объединены и являются группой управляющих входов коммутато ра, вторые входы каждого элемента И К ячеек (где К - число управляю щих воздействий первой группы) объединены -и являются соответствующим входом первой группы информационных входов коммутатора, а выход элемента И каждой ячейки является соответствующим выходом группы выходов коммутатора. На фиг. 1 приведена блок-схема предлагаемоего устройства; на фиг.2 функциональная схема блока формирования управляющих сигналов j на фиг. 3 - функциональная схема матричного коммутатора; на фиг. 4 функциональная схема группы элементов И; на фиг. 5 - функциональная схема блока элементов ИЛИ; на фиг.6 функциональная схема запоминающего устройства; на фиг. 7 - функциональная схема коммутатора блока формирования управляющих сигналов; на фиг. 8 - функциональная схема регистров блока формирования управляющих сигналов; на фиг. 9 - функциональная схема дешифратора блока формирования управляющих сигналов; на фиг.10 функциональная схема кодопреобразователя дешифратора блока формирования управляющих сигналов. Блок-схема вероятностного автомата (фиг. 1) содержит первую группу установочных входов lL -kv вторую группу установочных входов , блок 3 формирования управляющих сигналов, матричный коммутатор 4, регистр 5 сдвига, элемент И 6,. генератор 7 пуассоновского потока импульсов, генератор 8 тактовых импульсов, группу элементов И 9, блок 10 элементов ИЛИ, выходные шины 1Ц-11, запоминающее устройство 12. Функциональная схема блока 3 формирования управляющих сигналов (фиг. 2) содержит первые входы 1 J 11 , вторые входы ,, коммутатор 13, регистры ,, дешифратор 15, выходы 16 -1б1|. Функциональная схема матричного коммутатора 4 (фиг. 3) содержит управляющие входы , rpynnbi элементов И элементы ИЛИ , элементы И , первую группу информационных входов блока 4, вторую группу информационных входов 2 1 j, 21 блока 4, группу выходов 22 22 блока 4. Функциональная схема группы элементов И 9 (фиг. 4) содержит управяющий вход 23, элементы И , информационные входы группы, выходы . группы элементов И 9. Функциональная схема блока 10 элеентов ИЛИ (фиг. 5) содержит вхоы -22 -22 блока 10, элеменТЫ или , выходы блока 10, Функциональная схема запоминающего устройства 12 (фиг. 6) содержит входа 26.,-26 блока 12, триггеры 28.,-28|, элементы ИЛИ , выходы 21.-2Ь блока 12. Функциональная схема коммутатора 13 блока 3 формирования управляющих сигналов (фиг, 7) содержит управ ляющие входы коммутатора 13, элементы И 301 -30.j, информационные входы 31.,. -ЗЦ коммутатора 13, элементы ИЛИ 32 -32, разрядные выходы 33:. -33.коммутатора 13. Функциональная схема каждого регистра 14- блока 3 (. В) содержит разрядные, входь разрядные, выходы 31 31, регистры 34., Функциональная схема дешифратора 15 блока 3 (фиг. 9) содержит выхо ды ,, входы 33., , кодопреобразователи 35,, -35. Функциональная схема кодопреобразователя 35 (фиг. 10) дешифратора 15 блока 3 содержит первые входы , дешифратор 36, преобразуюищй ко двоичный в число-импульсный код, первый элемент ИЛИ 37, регистр 38 сдвига, второй элемент И 39, управляемый генератор 40 тактовой частоты первый триггер 41, элемент 42 задерж ки времени, вторые элементы И . третьи элементы И , вторые входы , четвертые элементы И , пятые элементы И 47-, 47j, второй элемент ИЛИ 48, вторые триггеры 49:,-49fy,, третьи элементы ИЛИ 50 50f, первые и вторые выхо ды соответственно , . Элементы устройства вероятностного автомата взаимосвязаны следующим образом. Первая 1 вторая группы установочных входов соединены соответственно с первыми и вторыми входами блока 3 формирования управляющих сигналов, выходы которого подключены соответственно к управляю щим входам матричного коммутатора 4, первая группа информационных входов которого подключена к разрядным выхо дам регистра 5 сдвига, выход переполнения которого соединен с информационным входом регистра 5, а тактовый вход подк-пючен -к выходу элеь{ента И 6, информационный вход ко торого подключен к выходу генератора 7 пуассоновского потока импульсов а управляющий вход подключен к выходу генератора 8 тактовьп импульсов и управляющим входам группы элементов И 9, информационные входы которой подключены к выходам блока 10 элементов ИЛИ, входы которого подключены к разрядным выходам матричного коммутатора 4, вторая группа информационных входов которого подключена соответственно к выходам вероятностного автомата и выходам запоминающего устройства 12, входы которого подключены к выходам соответствующих элементов И 9 группы. В блоке 3 формирования управляющих 11 -I сигналов первые входы динены с разрядными входами регистров соответственно, разрядные выходы которых подключены к информационным входам коммутатора 13, управляющие входы которого подключены ко вторым входам блока 3, а разрядные выходы подключены ко входам дешифратора 15, выходы которого являются выходами Г. блока 3. В матричном коммутаторе 4, который содержит К ячейки, каждая из которых состоит из группы элементов И 17 17J, элемента ИЛИ и элемента И 19-11-19tTii, причем управляющие входы 16 соединены соответственнос первыми входами соот1 -17 ветствующих элементов И 17. 11 группы, выходы которых соединены со входами соответствующих элементов ИЛИ 18.,., , причем со входами элемента ИЛИ 18;j соединены выходы элементов И 17 ;-17|j группы, выходы элементов ИЛИ 18.,.,-18 подключены к первым входам соответствующих элементов И 19.,-19.|, вторые входы которых подключены к первой группе информационных входов 20.-20 матричного коммутатора 4, вторая группа информационных входов которого 21.,21 подключена ко вторым входам соответствующих элементов И 17 групп, а разрядные выходы 22,-22 соединены с выходами соответствующих элементов И 19.,., -19. В группе элементов И 9 управляющий вход 23 соединен с первыми входами элементов И 24-f- 24, выходы соединены с выходами 26.,-26.j элементов И 24, вторые входы которых соединены с информационными входами 25.,-25.j груп-. пы. В блоке элементов ИЛИ 10 входы .ц соединены со входами соответствующих элементов ИЛИ , 7110 выходы которых соединены с выходами 25,,-25|, блока 10. В запоминающем устройстве 12 входы соединены с единичными входами соответствующих триггеров , нулевые входы которых соединены с выходами соответствующих элементов ИЛИ ., а единичные выходы соединены с выходами . блока 12 и соответствующими входами соответствующих элементов И , причем единичный выход триггера 28 соединен с вы ходом 21 блока 12 и соответствующими входами элементов ИЛИ , . . В коммутаторе 13 блока J формирования управляющих сигналов управляющие входы соединены с первыми входами элементов И , причем вход 2. соединен с первыми входами элементов И 30 -30, группы информационных входов коммутатора 13 соединены со вто рыми входами соответствующих элементов И 30 -30, выходы которых подключены ко входам соответствующих элементов ИЛИ коммутатора 13. В регистре 14{ блока 3.соответствующие разрядные входы lL -1.Vi соединены со входами регистров 341 34., выходы которых подключены к разрядным выходам регистра 14{ блока 3. В дешифраторе 15 блока 3 входы 33 -331 соединены со входами соответствующих кодопреобразователей 35xj -35, первые выходы которых соединены соответственно с выходами дещифратора 15, а вторые выходы каждого кодопреобразователя 35j. (кроме последних 35)соер,ккены со входами соответствующих последующих кодопреобразователей 35{j+i (кроме первых 35). Вероятностный автомат работает следующим образом. По второй группе установочных входов 2 подаются входные управляющи воздействия х, х, ..., х, причем цодача управляющих воздействий осуществляется однозначно, т.е. если в момент времени t.Ha входе 2- было управляющее воздействие х., то это значит, что на установочном входе 2j был единичный потенциал, а на остальных входах - нулевые потенциалы, и если в момент времени t будет подано воздействие xg, то это значит, что на входе 2j будет единичный потенциал, а на остальных входах 2,(,n, iM) будет нулевой.потенциал Вероятностный автомат имеет X состояний и работа его определяется матрицами переходных вероятностей Р, коды которой задаются по первой группе установочных входов 1 для каждого х в начале работы вероятностного автомата, причем переходные вероятности в виде двоичных кодов (j 1 ,.1,1() для каждой матрицы Р(,п) заносятся по соответствующим первым установочным входам в соответствующие регистры 34ъ блока 3 формирования управляющих сигналов. Будем считать, что разрядность записываемых кодов постоянна и равна р. В общем виде матрица Р« имеет вид Для простоты предположим, что , и известны (заданы) следующие матрицы переходных вероятностей Тогда в блоке 3 формирования управляющих сигналов в регистры 14,, 14 , 14., в соответствующих регистрах 34 будут храниться коды вероятностей соответствующих матриц Р , Р и РЗ (фиг. 2 и фиг. 8). Генератор 7 совместно с регистром 5 образуют равновероятностный 1,k полюсник. Вероятность появления им-пульсов на любом из разрядных выходов регистра 5 постоянна и рарна , где m -число разрядных выходов регистра 5. Равная вероятность появления импульсов на любом из разрядных выходов регистра 5 достигается тем, что частота работы генератора 7 на несколько порядков вьщ1е частоты работы генератора 8 тактовых импульсов. Тогда между моментами появления импульсов генератора 8 записанная в регистре 5 единица многократно обегает регистр 5, а в силу экспоненциального распределения интервалов между импульсами генератора 7 достигается равная вероятность появ911ления импульсов на разрядных выходах регистра 5 в момент обращения генератора 8. Предположим, что в рассматриваемый момент времени t подано управляющее воздействие х, т.е. потенци 1Л имеется на втором входе 2 , а в предыдущем t., моменте времени автомат находился в первом у состоянии. Отметим, что моменты времени t, задаются генератором 8 тактовой частоты. Потенциал-со второго входа 22 подается на управляющий вход 2 ком мутатора 13 блока 3 и тем самьпч открывает соответствующие элементы И 30Д -30 и коды регистров 341л-3- ii регистра подаются через элементы И , элементы ИЛИ , выходы 33 коммутатора 13 на входы дешифратора 15. На вьосодах дешифратора 15 формируются управляющие потенциалы для матричного коммутатора 4. Это происходит следующим образом Число выходов 16 от каждого кодо преобразователя 35 равно десяти. В этом случае точность установки управляющих потенциалов равна 1/10. На входы 33, -ЗЗ ещифратора 15 по даются коды матрицы переходных вероя ностей Р2. В кодопреобразователях 35, , 3521 35 на вторых входах (на фиг. 9 не показано) постоянно присутствуют нулевые поте циалы. На первые входы дешифраторов 36 кодопреобразователей 35 , 35i3 подаются коды чисел 0,2; 0,4; 0,4 соответственно. Сумма чисе каждой строки всегда равна единице. Тогда дешифраторы 36 преобразуют дв ичные кода чисел 0,2; 0,4; 0,4 соответственно в число-импульсные коды 1100000000, 1111000000, 11110000 т.е. на первых двух выходах дешифра тора 36 кодопреобразователя 35 и на первых четырех вьпсодах дешифра торов 36 кодопреобразователей 35 и будут потенциалы. На первые входы дешифраторов 36 кодопреобразователей 352-) , 3522 3523 подаются коды чисел 0; 0,33; 0,66 соответственно. Дешифраторы 36 преобразуют двоичные коды этих чисел в число-импульсгые коды 0000000000; 1110000000; 11111110 соответственно, т.е. на всех выхода дешифратора 36 кодопреабразователя 35 будут нулевые потенциалы, на первых трех выходах дешифратора 36 кодопреобразователя на первых семи выходах дешифратора 36 кодопреобразователя будут единичные потенциалы. На первые входы 33 дешифраторов 36 кодопреобразователей 35з , 35зэ подаются коды чисел Ор125; 0,875; О соответственно. Дешифраторы 36 преобразуют двоичные коды чисел в число-импульсные коды 1000000000; 1111111110; 0000000000 соответственно. В кодопреобразователе 35 изменение состояний выходов дешифратора 36 вызывает через элемент ИЛИ 37 сброс : триггеров 49 в нулевое состояние и переброс триггера 41 в единичное состояние. Генератор 40 запускается и подает тактовые импульсы на тактовый вход регистра 38, в первых двух ячейках которого записаны единицы. На первом такте работы генератора 40 на выходе элемента И 44 бу- . дет нулевой потенциал и срабатывает элемент И 39. Потенциал с выхода элемента И 39 сбрасывает триггер 41 в исходное нулевое состояние, через элементы И 43 и 43, перебрасывает триггеры 49 и 49- в единичные состояния и через элемент задержки времени 42 сбрасывает регистр 38 в исходное состояние, Обнулив все его ячейки. На первых выходах 16 , 16 и вторых выходах 51 и Slj будут единичные потенциалы, а на остальных его выходах 1б-1б и 51,-51- нулевые потенциалы. В кодопреобразователе 35 измене-. ние состояний выходов дешифратора 36 через элемент ИЛИ 37 вызывает сброс триггеров 49 в нулевое состояние и переброс триггера 41 в единичное состояние. Триггер 41 запускает генератор 40. На вторьгх входах 45 и 45, имеются единичные потенциалы, поданные с выходов 51 и 51 кодопреобразователя 35-, . В регистре 38 в первых четырех ячейках записаны единицы. По первому шпульсу генератора 40 на выходе элемента ИЛИ 48 будет единичный потенциал. По заднему фронту первого импульса генератора 40 содержимое регистра 38 сдвигается вправо, т.е. на его выходах будет код 0111100000. На втором импульсе генератора 40 на выходе элемента ИЛИ 48 будет также 11 единичный потенциал (единица на выходе элемента И AAj). По заднему фронту второго импульса генератора 40 содержимое регистра 38 сдвигается еще на единицу вправо, т.е. на его выходах будет код 0011110000 На третьем импульсе генератора 40 на выходе элемента ИЛИ 48 будет нулевой потенциал и срабатывает элемент И 39. Потенциал с выхода элемента И 39 сбрасывает триггер 41 в нулевое состояние (тем самым оста навливается генератор 40), через открытые элементы И 43,, 43,, 43j, 43g перебрасываются триггеры в единичные состояния и через элемент задержки времени 42 в регистре 38 обнуляются все его ячейки На выходах 16, 16, 16% 16° буду нулевые потенциалы, а на выходах 16 16 - единичные потенциалы, так как триггеры 49,-49 находятся в единич ных состояниях. На выходах 51, 512 будут единичные потенциалы, так как имеются потенциалы на входах 45 и 452 триггеры 49 , 49 находятся в нулевых состояниях, следовательно единичные потенциалы имеются на выходах элементов И 47 и 47. На выходах 51 -51 имеются единичные потенциалы, так как триггеры 49.-49 имеют потенциал на единичном выходе Следовательно, имеется потенциал на выходе .-элементов И . На выхо дах 5Ц-51 о имеются нулевые потенциалы, так как элементы И и И заперты. В кодопреобразователе 35 изменение состояний выходов дешифраторов 36 через элемент ИЛИ 37 вызывает сброс триггеров 49 в нулевые сос тояния и переброс триггера 41 в еди ничное состояние. Триггер 41 запускает генератор 40. На вторых входах 45 имеются единичные потен циалы, поданные с выходов кодопреобразователя регистре 38 в первых четырех ячейках запи саны единицы. По первым шести импул сам генератора 40 на выходе элемента ШП 48 будут единичные потенциалы, а по заднему фронту шестого импульса генератора 40 на выходах регистра 38 имеется код 0000001111. На седьмом импульсе генератора 40 на выходе элемента ИЛИ 48 будет нулевой потенциал и срабатывает элемент И 39, потенциал с выхода которого сбрасывает триггер 41 в нулево 5512 состояние (тем самым останавливается генератор 40), через открытые элементы И 43-j-43 Q переводятся триггеры 49-j-49 o в единичные состояния и через элемент задержки времени регистр 38 переводится в исходное нулевое состояние. На выходах 16-16, будут нулевые потенциалы, так как триггеры , находятся в нулевых состояниях, а на выходах будут единичные потенциалы, так как триггеры будут в единичном состояниях. По описанному алгоритму работы на выходах 16, -16 кодопреобразователя 35,- будут нулевые потенция 1 Ч лы. На выходах 162-, кодопреобразователя 35-2 будут единичные потенциалы, а на выходах . это1 ° кодопреобразователя - нулевые потенциалы. На выходах .кодопреобразователя будут нулевые потенциалы, а на вьпсодах единичные потенциалы. На выходе 16 кодопреобразователя 35 будет установлен единичный потенциал, на выходах 16j., данного кодопреобразователя 35 - нулевые потенциалы. На выходе 16jj кодопреобразователя будет нулевой потенциал, а на остальных его выходах - единичные потенциалы. На выходах кодопреобразователя 35 будут установлены нулевые потенциалы. Управляющие потенциалы с выходов 1 11-16 3 яля рассматриваемого примера) блока 3 подаются на соответствующие управляющие входы матричного коммутатора 4, подготавливая соответствующие -17. элементы И 17 11 Для рассматриваемого примера открывающий потенциал будет на первых входах элементов И 17 -172i ; 17 17 17 . 171 52 Ч TJ 52 Ь2 7} 83 открываемых потенциалами с выходов кодопреобразователей 35 ; на первых выходах элементов И 17i2 ; 722 ll, 5 %; 17fo3. ОТКРЫаемых потенциалами с выходов кодореобразователей 3522 и перых входах элементов И 17f ; 17|j ; 17|2; 17|i; 17|,; 7|,; 17|,; ,73 . 17 2 92 102 о1крываемых потенциала и с выходов кодопреобразователей 35j., 35,2 . Ранее было принято, что в момент ремени t. автомат находился в соетоянии у,(в первом состоянии), т.е. на выходе 11 был потенциал, или был открыт триггер 28 запоминающего устройства 12. В этом случае потенциал с первого выхода 21 устройства 12 подается на информационный вход 21 матричного коммутатора 4 или на вторые входы элементов И 17 17 У В результате оказываются откры тыми в первом столбце элемен ты И 17 ,, во втором столбце элементы И 17j2-17jj , в третьем . столбце - элементы И ..о, т.е. на выходах элементов ИЛИ 18 18з2-18ь2 будут потенциа лы, подаваемые на первые входы вторы . элементов ll-Л.Г-1,-- г |1лл . -L М С- ЗМЫМ обеспечивается вероятность перехода автомата из первого состояния в первое с вероятностью 2/10, во второе с вероятностью 4/10, в третье - с ве роятностью 4/10, что соответствует матрице переходов.Р, учитывая равную вероятность появления сигналов на любом из выходов регистра 5. В момент времени t импульс генератора 8 закрывает элемент И 6 (тем самым зафиксировав единицу на одном из выходов регистра 5, допусти на пятом выходе, и открывает элементы И элементов группы 9. Импульс с пятого (из разрядных) выходов регистра 5 подается на вход 20j матричного коммутатора 4 и на выходе элемента И 19jj будет потенциал, который снимается с разрядного выхода 2225 коммутатора 4, подается на вход 225 блока 10 элементов ИЛИ, через элемент ИЛИ 272 выход 25j бло ка 10 подается на вход 25 группы эл ментов И 9, через открытый элемент И 24у, выход 262 группы 9 подается на вход запоминающего устройства 12 и перебрасывает триггер 28- в единичное состояние. Потен циал с единичного выхода триггера 282 сбрасывает триггер 28., в нуле вое состояние через элемент tLFUi 29 и подается на выход 11. вероятностного автомата, что свидетельствует о переходе автомата во второе состоя ие у Далее внешняя среда дает на вторую группу установочных входов 2 очередное управлякяцее воздействие х . и блок 3 формирования управляющих воздействий подает новые управляющие потенциалы на управляющие входы матричного коммутатора 4 и процесс повторяется по описанному алгоритму. Вероятностный автомат используется для моделирования сложных стохастических систем либо как управляющее устройство, прогнозирующее поведение системы. В большинстве реальных промьшленных системах функция управления зависит от входных и возмущающих воздействий , т.е. необходимо при управлении учитывать множество входных воздействий. Известное устройство (оно же принято за базовое) является автономным и не выполняет данную функцию. Если известно, что управлякнцее воздействие содержит п факторов, то при построении управляющего устройства необходимо п известных устройств . При построении управляющего устройства на базе предлагаемого вероятностного автомата необходим один автомат. Если стоимость известного устройства С,, а предлагаемого Су , то экономическая эффективность от примене ия предлагаемого устройства как управляющегов системе- с п входными воздействиями определится формулой . Из формулы следует, что в зависимости от роста п существенно возрастает величина экономической эффективности использования предлагаемого устройства.

/// /// /fff

фае.1

2f2i

-n

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЧЕТКИЙ ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1995 |

|

RU2110090C1 |

| Вероятностный автомат | 1983 |

|

SU1200296A2 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для моделирования вероятностного графа | 1982 |

|

SU1119023A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Вероятностный автомат | 1982 |

|

SU1045232A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1479938A1 |

1. ВЕРОЯТНОСТНЫЙ АВТОМАТ, содержащий генератор пуассоновского потока импульсов, выход которого соединен с информационным входом элемента И, выход которого подключен к тактовому входу регистра сдвига, выход переполнения которого соединен с его информационным входом, разрядные выходы которого подключены к первой группе информационных входов матричного коммутатора, разрядные выходы которого через блок элементов ИЛИ соединены соответственно с информационными входами элементов И, группы которых подключены соответственно к входам запоминающего устройства, выходы которого являются выходами автомата и подключены к второй группе информационных входов матричного коммутатора, управляющие входы элемента И и элементов И группы объединены и подключены к выходу генератора тактовых импульсов, отличающийся тем, что, с целью повышения точности, он содержит блок формирования управляющих сигналов, состоящий из дешифратора, регистров И коммутатора, разрядные выходы которого подключены соответственно ко входам дешифратора, вькоды которого являются выходами блока и подключены к группе управляющих входов матричного коммутатора, группы информационных входов коммутатора блока формирования управляющих сигналов соединены соответственно с разрядными выходами регистров, разрядные входы которых являются первой группой установочных входов автомата, вторая группа установочных входов которого является соответственно группой управляющих входов коммутатора блока формирования управлякяцих сигналов. 2. Автомат по п. 1,отличаюСО щ и и с я тем, что матричный коммутатор содержит ячейки, каждая из которых состоит из группы элементов И, элемента ИЛИ и элемента И, первый вход которого в каждой ячейке соединен с выходом элемента ИЛИ своей ячейки, входы которого подключены к выходам элементов И группы своей ячейки, первые входы одноименных элео ментов И группы всех ячеек объединены 00 4;: и являются второй группой информационных входов матричного коммутато01 ра, вторые входы одноименных элеменСП тов И группы всех ячеек объединены и являются группой управляющих входов коммутатора, вторые входы каждого элемента И К ячеек (где К - число управляющих воздействий первой группы) объединены и являются соотэетствующим входом первой группы информационных входов коммутатора, а выход элемента И каждой ячейки является соответствукицим выходом группы выходов коммутатора.

Фие.2

Т

15з

25к

Фи9.Ь

1108455 / ../

//У 31 tf J/i 31j J/// Ф..1 Ф

,

3

ITТП

Zfz ; fJr - -

/ « f/r

rj/ |/« j/;/

j/;f3/;r j/;/ t f-T T.T-T urT ;/ J, f J; 7 7 7 f-n 21 n J/ 31ffi f l р; -j. , 1 Пп / f / / / 2HI IKI A7 A ZHZ 2ff1 2fff Af 1 Z т / , /5; f6ft 16 fZ fSff ty IQfi JtJfflOiflOlZ 10 |, «.t..i 55 j J5// 1 T T T T T T Jjjyfo/ fe /fe f fff.f i:fff| 2 J5,/ 22 tit |i iriyTTUrC 33ff 33| 33fff 55 55/;, 53 J5« 33| J3f 55 55/, 53. /r/ /p . /5 T f-f t f-f. . pzfl УЛ К 1;тгСи7Г J3i, 33j, 33jJ 53;, 33 J% 33i, J3l, 33j 53;, 33 J% . 9

1/f t.. .f

J4

/AC

UrT

4л /A- r

гл- л

J ;Y|/A xJ t I V. V «j/ /л ;A Ъ1кк 31мк 31 кн I / .в Н f Z/rff Zftff 2мк f I 1f /6fff f6fif «e , /J T lijrfelrJjfii «f::| 5,к i,M. 33f 33fl /4-r fSl fS /G J6 h f f-f j L.fL итг, JJ 5J VAT

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автономный вероятностный автомат | 1978 |

|

SU734701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-09-02—Подача