Изобретение относится к области техники связи и может быть применено в системах передачи информации при построении дискретного канала как кодирующее и декодирующее устройство кодов различной корректирующей способности с обнаружением ошибок.

Известно декодирующее устройство (см. авт.свид. СССР N 853809, H 04 L 3/02, H 03 K 13/32, опубликованное в офиц. бюлл. ОИПОТЗ N 29 за 1981 г.), содержащее первый, второй, третий и четвертый регистры памяти, первый, второй счетчики, элемент ЗАПРЕТ, элемент И, сумматор по модулю два, блок сравнения, генератор кодовых слов, первый и второй ключи, причем первый вход устройства соединен с входом первого регистра памяти, второй вход устройства соединен с входом второго регистра и входом первого счетчика, выход которого соединен с первым входом первого генератора кодовых слов, второй вход которого соединен с выходом первого ключа, а выход соединен с первым входом второго ключа и с первым входом сумматора по модулю два, второй вход которого соединен с первым выходом первого регистра памяти, а выход - с прямым входом элемента ЗАПРЕТ, инверсный вход которого соединен с выходом второго регистра памяти, а выход соединен с первым входом блока сравнения, входом второго счетчика и с первым входом первого ключа, второй вход которого соединен со вторым выходом первого регистра памяти, выход второго счетчика соединен с первым входом элемента И, выход которого соединен с входом третьего регистра, выход которого соединен со вторым входом блока сравнения, выход которого соединен со вторым входом элемента И и вторым входом второго ключа, выход которого соединен с входом четвертого регистра памяти, выход которого соединен с выходом устройства.

Недостатком данного устройства является то, что оно не обеспечивает адаптацию кода как к изменяющимся характеристикам канала связи, так и к различным требованиям к верности передачи сообщений от различных источников; кроме того, известное устройство не выполняет функций кодирования.

Признаками аналога, совпадающими с признаками заявляемого технического решения, являются регистры памяти, ключи, счетчики, элемент И, сумматор по модулю два.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известного устройства, не позволяющих изменить корректирующую способность и длину кода в зависимости от состояния канала либо от важности передаваемого сообщения, а также обеспечить кодирование помехоустойчивых кодов.

Известно устройство декодирования циклических кодов (см. авт. свид. СССР N 1496009, М. кл. H 03 M 13/10, опубликованное в офиц. бюлл. БИ N 27 за 1989 г. ), содержащее кодер полинома, перестраиваемый счетчик, коммутатор, вычислитель синдрома, перестраиваемый регистр памяти, генератор тактовых импульсов, элемент ИЛИ-НЕ, элемент И, при этом информационный вход устройства соединен с информационным входом коммутатора, группа управляющих входов устройства соединена с группами управляющих входов кодера полинома, перестраиваемого счетчика и коммутатора, группа управляющих выходов кодера полинома соединена с группой управляющих входов вычислителя синдрома, первый управляющий выход перестраиваемого счетчика соединен с первым входом элемента И, второй управляющий выход перестраиваемого счетчика соединен со вторым управляющим входом перестраиваемого регистра памяти и с управляющим входом вычислителя синдрома, выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого соединен со вторым входом элемента И, выход которого соединен с первым управляющим входом перестраиваемого регистра памяти, группа информационных выходов которого соединена с группой информационных выходов устройства, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого счетчика, вычислителя синдрома и перестраиваемого регистра памяти.

Однако данное устройство не позволяет учесть при выборе кодов изменения помеховой обстановки в канале связи; кроме того, известное устройство не выполняет функций кодирования циклических кодов переменной длины.

Признаками аналога, совпадающими с признаками заявляемого технического решения, являются перестраиваемый счетчик, кодер полинома, вычислитель синдрома, элементы ИЛИ-НЕ, И, генератор тактовых импульсов, коммутатор, перестраиваемый регистр памяти.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известного устройства, не позволяющих изменить корректирующую способность и длину кода в зависимости от состояния канала связи, а также обеспечить кодирование циклических кодов переменной длины.

Наиболее близким к предлагаемому по совокупности функциональных и конструктивных признаков является устройство декодирования циклических кодов (см. авт. свид. СССР N 1735996, М. кл. H 03 M 13/00, опубликованное в офиц. бюлл. БИ N 19 за 1992 г. ), содержащее кодер полинома, перестраиваемый счетчик, коммутатор, канальный коммутатор, ключ управления, сумматор по модулю два, вычислитель синдрома, перестраиваемый регистр памяти, генератор тактовых импульсов, элементы И, ИЛИ-НЕ, при этом информационный вход устройства соединен с первым входом сумматора по модулю два и вторым информационным входом канального коммутатора, вход-выход которого соединен с канальным входом-выходом устройства, группа управляющих входов устройства соединена с группами управляющих входов кодера полинома, перестраиваемого счетчика и коммутатора, вход управления декодированием устройства соединен с первым управляющим входом канального коммутатора, вход управления кодированием устройства соединен со вторым управляющим входом канального коммутатора и первым управляющим входом ключа управления, группа управляющих выходов кодера полинома соединена с группой управляющих входов вычислителя синдрома, третий и первый управляющие выходы перестраиваемого счетчика соединены соответственно со вторым входом элемента И и вторым управляющим входом ключа управления, второй управляющий выход перестраиваемого счетчика соединен с управляющим входом вычислителя синдрома, третьим управляющим входом ключа управления и первым управляющим входом перестраиваемого регистра памяти, группа информационных выходов коммутатора соединена с группами информационных входов вычислителя синдрома и перестраиваемого регистра памяти, информационный выход канального коммутатора соединен с информационным входом коммутатора, второй и первый информационные выходы ключа управления соединены соответственно с информационным входом вычислителя синдрома и первым информационным входом канального коммутатора, выход сумматора по модулю два соединен с информационным входом ключа управления, группа информационных выходов вычислителя синдрома соединена с входами схемы ИЛИ-НЕ, а последний из этой группы выход соединен со вторым входом сумматора по модулю два, группа информационных выходов перестраиваемого регистра памяти соединена с группой информационных выходов устройства, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого счетчика, вычислителя синдрома и перестраиваемого регистра памяти, выход элемента ИЛИ-НЕ соединен с первым входом элемента И, выход которого соединен со вторым управляющим входом перестраиваемого регистра памяти.

Данное устройство обеспечивает как декодирование, так и кодирование циклических кодов переменной длины; оно позволяет учесть при выборе кодов различные требования к верности передачи сообщений от различных источников.

Однако известное устройство не обеспечивает адаптацию кода к изменяющимся характеристикам канала связи.

Признаками аналога, совпадающими с признаками заявляемого технического решения, являются перестраиваемый счетчик, кодер полинома, ключ управления, вычислитель синдрома, элементы ИЛИ-НЕ, И, сумматор по модулю два, коммутатор, генератор тактовых импульсов, канальный коммутатор, перестраиваемый регистр памяти.

Причины, препятствующие достижению требуемого технического результата, состоят в особенностях реализации известного устройства, не позволяющих изменять корректирующую способность и длину кода в зависимости от уровня помех в канале связи.

Задача, на решение которой направлено предлагаемое изобретение, заключается в повышении эффективности использования канала связи за счет адаптации кода к уровню помех в канале.

Технический результат от применения предлагаемого изобретения заключается в уменьшении времени использования канала связи за счет уменьшения корректирующей способности и длины кода при улучшении помеховой обстановки в канале (уменьшение уровня помех в канале). Это позволяет увеличить количество пользователей, передающих информацию по выделенному каналу.

Для достижения технического результата в устройство адаптивного кодирования и декодирования, содержащее кодер полинома, перестраиваемый счетчик, коммутатор, канальный коммутатор, ключ управления, сумматор по модулю два, вычислитель синдрома, перестраиваемый регистр памяти, генератор тактовых импульсов, элементы И, ИЛИ-НЕ, при этом информационный вход устройства соединен с первым входом сумматора по модулю два и вторым информационным входом канального коммутатора, вход-выход которого соединен с канальным входом-выходом устройства, вход управления декодированием устройства соединен с первым управляющим входом канального коммутатора, вход управления кодированием устройства соединен со вторым управляющим входом канального коммутатора и первым управляющим входом ключа управления, группа управляющих выходов кодера полинома соединена с группой управляющих входов вычислителя синдрома, третий и первый управляющие выходы перестраиваемого счетчика соединены соответственно со вторым входом элемента И и вторым управляющим входом ключа управления, второй управляющий выход перестраиваемого счетчика соединен с управляющим входом вычислителя синдрома, третьим управляющим входом ключа управления и первым управляющим входом перестраиваемого регистра памяти, группа информационных выходов коммутатора соединена с группами информационных входов вычислителя синдрома и перестраиваемого регистра памяти, информационный выход канального коммутатора соединен с информационным входом коммутатора, второй и первый информационные выходы ключа управления соединены соответственно с информационным входом вычислителя синдрома и первым информационным входом канального коммутатора, выход сумматора по модулю два соединен с информационным входом ключа управления, группа информационных выходов вычислителя синдрома соединена с входами схемы ИЛИ-НЕ, а последний из этой группы выход соединен со вторым входом сумматора по модулю два, группа информационных выходов перестраиваемого регистра памяти соединена с группой информационных выходов устройства, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого счетчика, вычислителя синдрома и перестраиваемого регистра памяти, выход элемента ИЛИ-НЕ соединен с первым входом элемента И, выход которого соединен со вторым управляющим входом перестраиваемого регистра памяти, дополнительно введены блок оценки состояния канала, блок выбора кода, группа элементов ИЛИ, при этом вход управления кодированием устройства соединен с управляющим входом блока выбора кода, входы второй группы управляющих входов устройства соединены с первыми входами группы элементов ИЛИ, первая группа управляющих входов устройства соединена с первой группой управляющих входов блока оценки состояния канала, группа выходов которого соединена с группой входов блока выбора кода, выходы группы управляющих выходов которого соединены с входами второй группы управляющих входов блока оценки состояния канала и со вторыми входами группы элементов ИЛИ, управляющий выход блока выбора кода соединен с управляющим входом блока оценки состояния канала, выходы группы схем ИЛИ соединены с входами групп управляющих входов кодера полинома, перестраиваемого счетчика и коммутатора.

Наличие причинно-следственной связи между техническим результатом и признаками заявляемого изобретения доказывается следующими логическими посылками.

Наиболее дорогой частью системы передачи информации является канал связи, поэтому эффективность системы определяется в первую очередь эффективностью использования канала. Если устройство не обеспечивает адаптацию кода к изменению уровня помех в канале, то для передачи сообщения необходимо использовать код с максимальной корректирующей способностью и максимальной длиной. Изменение корректирующей способности и длины кода в соответствии с изменением помеховой обстановки в канале позволяет повысить эффективность использования канала. Для этого в устройство необходимо ввести блок оценки состояния канала, определяющий соответствие используемого для передачи кода уровню помех в канале, и блок выбора кода, обеспечивающий в случае несоответствия переход к коду с большей (при увеличении уровня помех) или меньшей (при уменьшении уровня помех) корректирующей способностью и длиной.

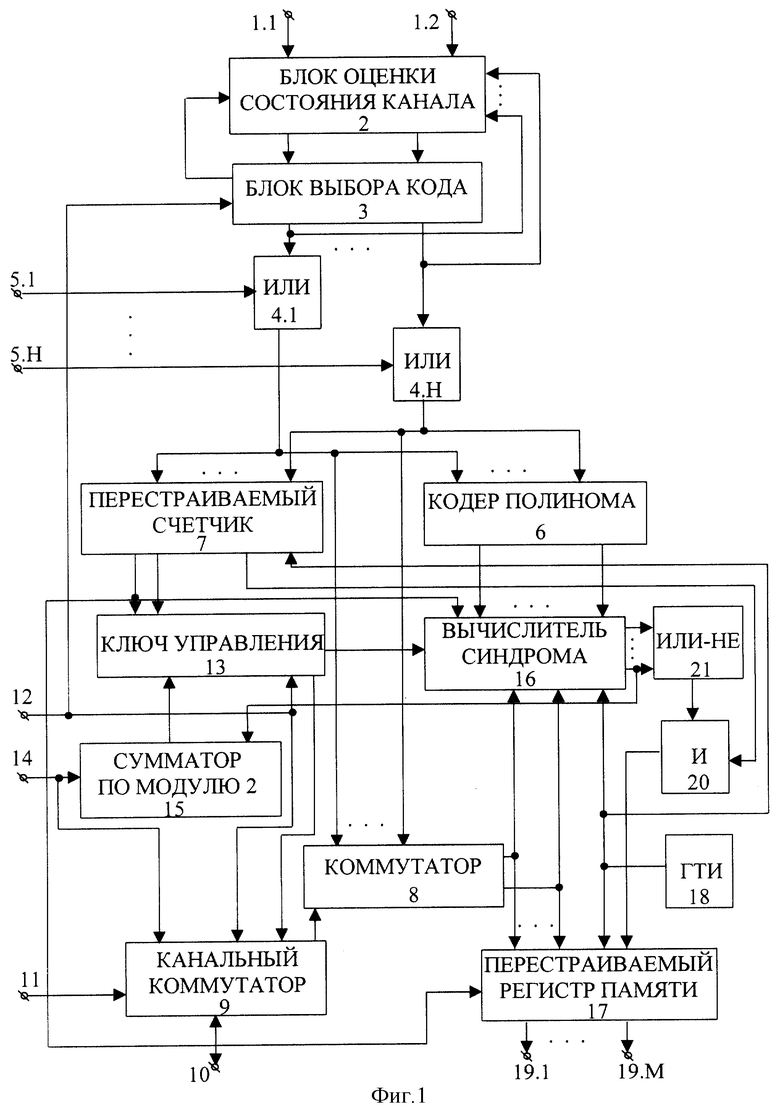

Сущность предлагаемого варианта реализации изобретения поясняется чертежами.

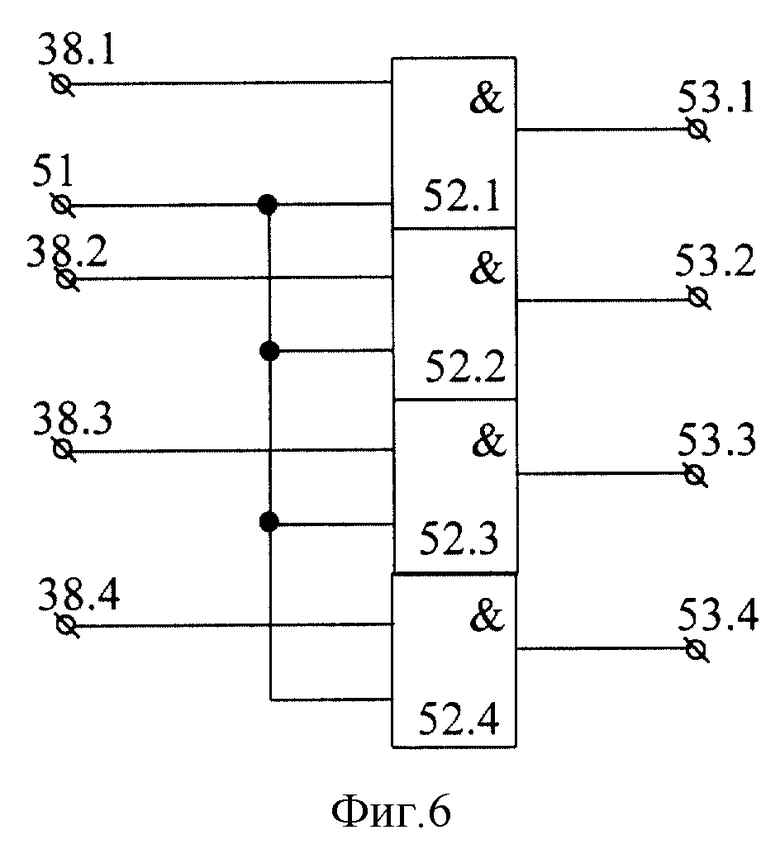

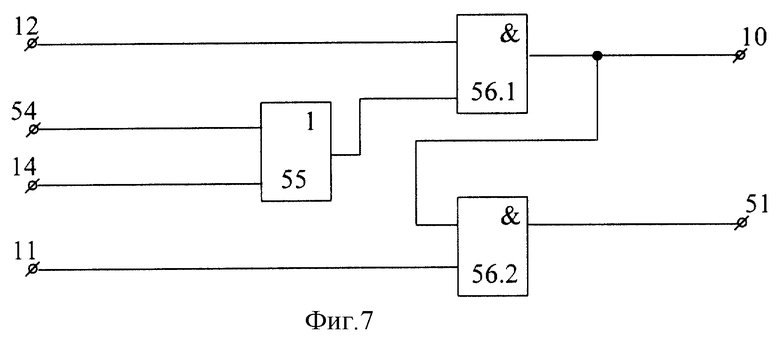

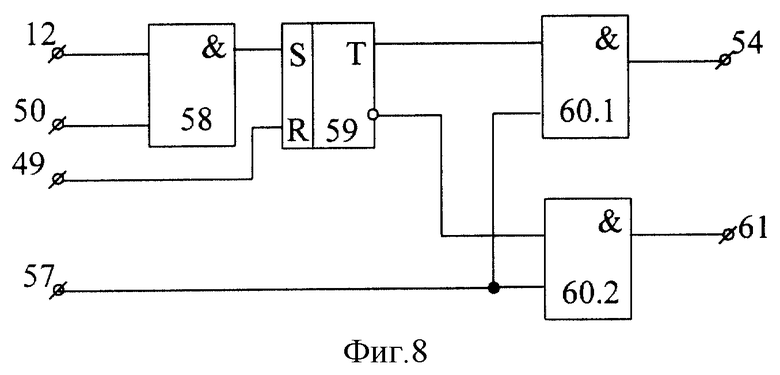

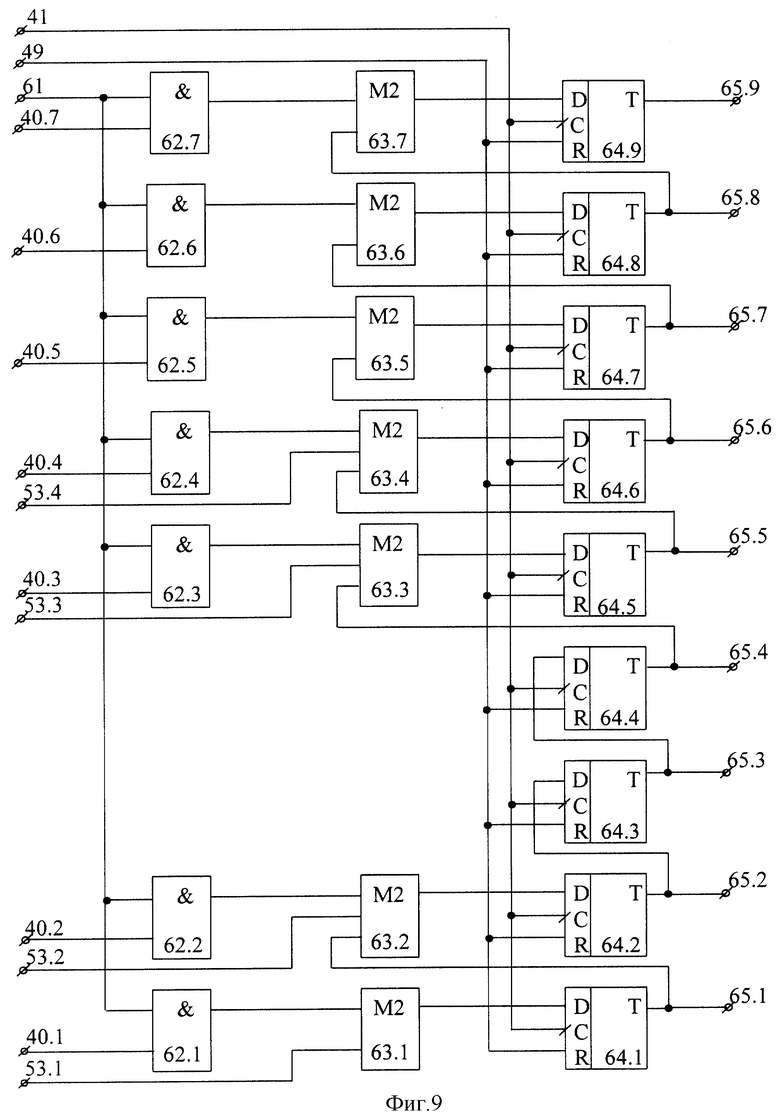

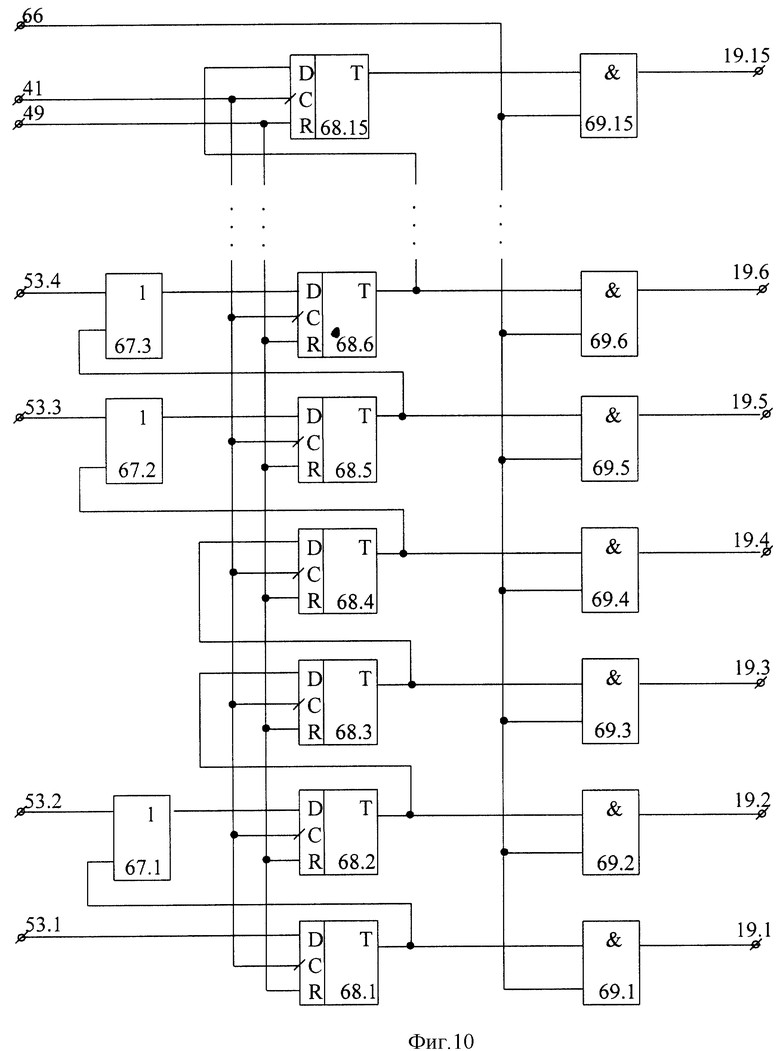

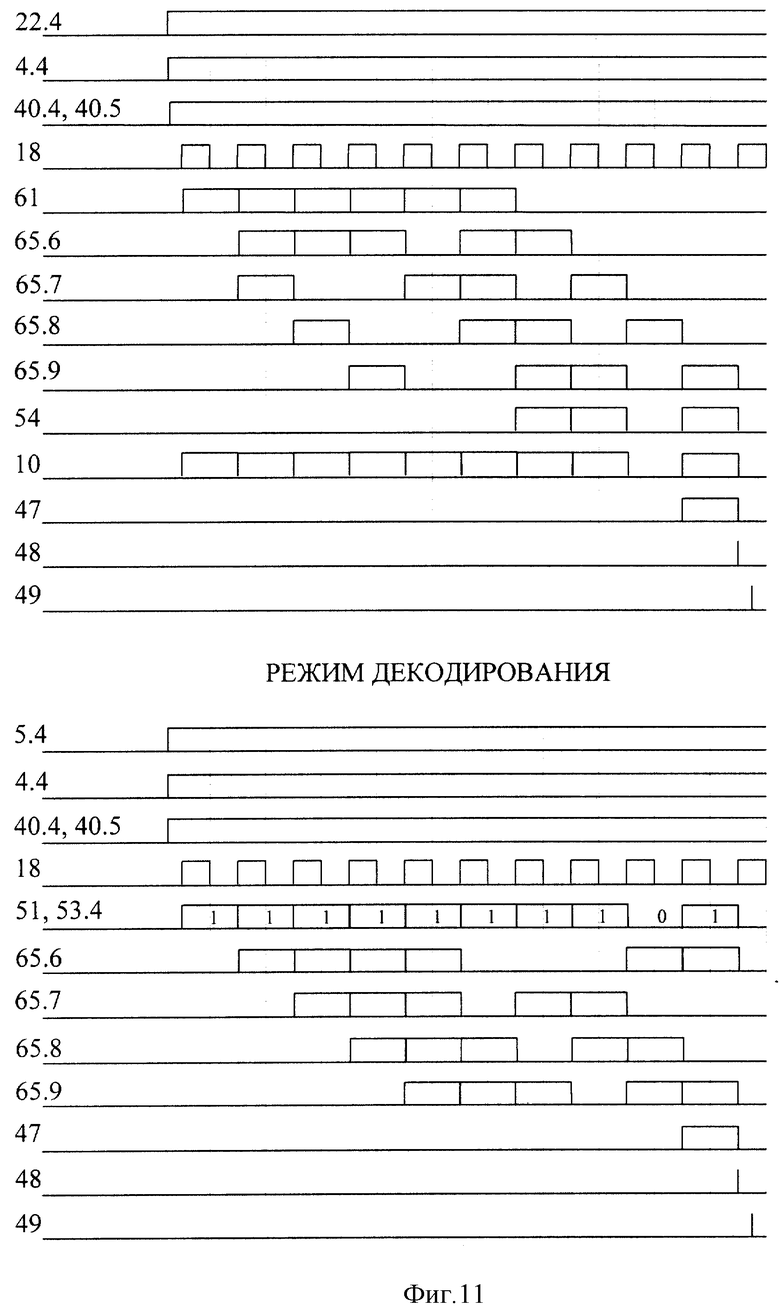

На фиг. 1 приведена структурная схема заявляемого устройства, на фиг. 2 - функциональная схема блока оценки состояния канала, на фиг. 3 - функциональная схема блока выбора кода, на фиг. 4 - функциональная схема кодера полинома, на фиг. 5 - функциональная схема перестраиваемого счетчика, на фиг. 6 - функциональная схема коммутатора, на фиг. 7 - функциональная схема канального коммутатора, на фиг. 8 - функциональная схема ключа управления, на фиг. 9 - функциональная схема вычислителя синдрома, на фиг. 10 - функциональная схема перестраиваемого регистра памяти, на фиг. 11 - временные диаграммы, поясняющие работу устройства.

Структурная схема заявляемого устройства (см. фиг. 1) содержит: 11-12 - первую группу управляющих входов; 2 - блок оценки состояния канала; 3 - блок выбора кода; 41-4H - группу элементов ИЛИ; 51-5H - вторую группу управляющих входов; 6 - кодер полинома; 7 - перестраиваемый счетчик; 8 - коммутатор; 9 - канальный коммутатор; 10 - канальный вход-выход устройства; 11 - вход управления декодированием устройства; 12 - вход управления кодированием устройства; 13 - ключ управления; 14 - информационный вход устройства; 15 - сумматор по модулю два; 16 - вычислитель синдрома; 17 - перестраиваемый регистр памяти; 18 - генератор тактовых импульсов; 191-19N - группу информационных выходов устройства; 20 - элемент И; 21 - элемент ИЛИ-НЕ.

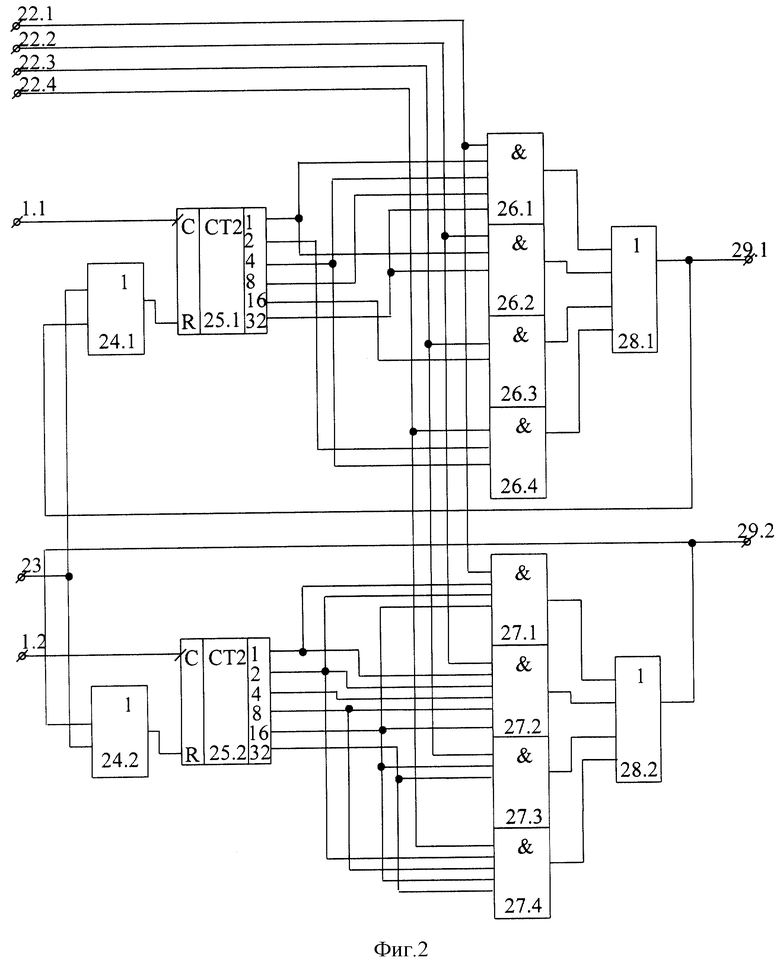

Функциональная схема блока 2 оценки состояния канала (см. фиг. 2) содержит: 11, 12 - первую группу управляющих входов; 221-224 - вторую группу управляющих входов; 23 - управляющий вход; 241, 242 - соответственно первый и второй элементы ИЛИ; 251, 252 - соответственно первый и второй двоичные счетчики; 261-264, 271-274 - соответственно первую и вторую группы элементов И; 281, 282 - соответственно третий и четвертый элементы ИЛИ; 291, 292 - группу управляющих выходов.

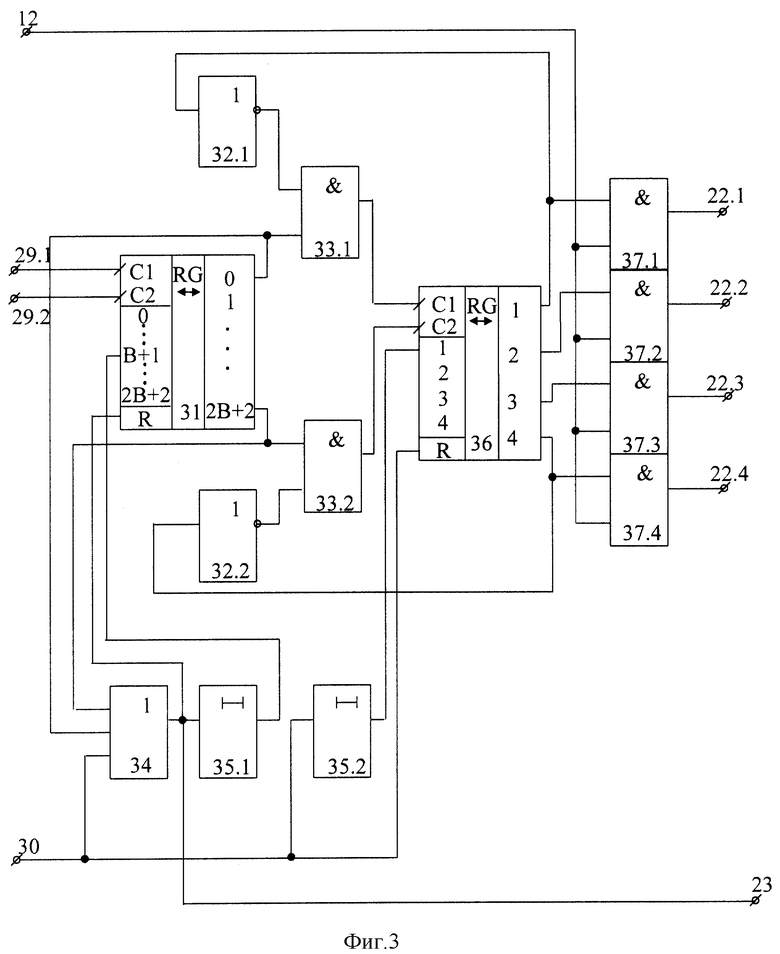

Функциональная схема блока 3 выбора кода (см. фиг. 3) содержит: 12 - управляющий вход; 221-224 - группу управляющих выходов; 291, 292 - группу управляющих входов; 30 - вход начальной установки; 31 - первый регистр сдвига; 321, 322 - соответственно первый и второй инверторы; 331, 332 - соответственно первый и второй элементы И; 34 - элемент ИЛИ; 351, 352 - соответственно первый и второй элементы задержки; 36 - второй регистр сдвига; 371-374 - группу элементов И.

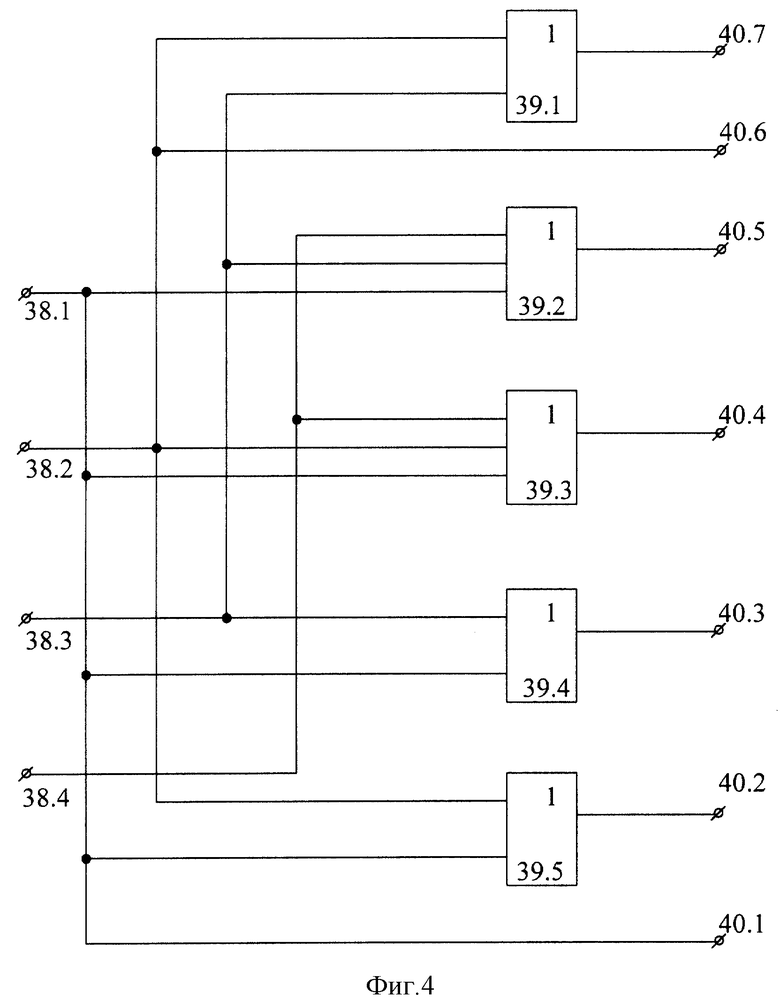

Функциональная схема кодера 6 полинома (см. фиг. 4) содержит: 381-384 - группу управляющих входов; 391-395 - группу элементов ИЛИ; 401-407 - группу управляющих выходов.

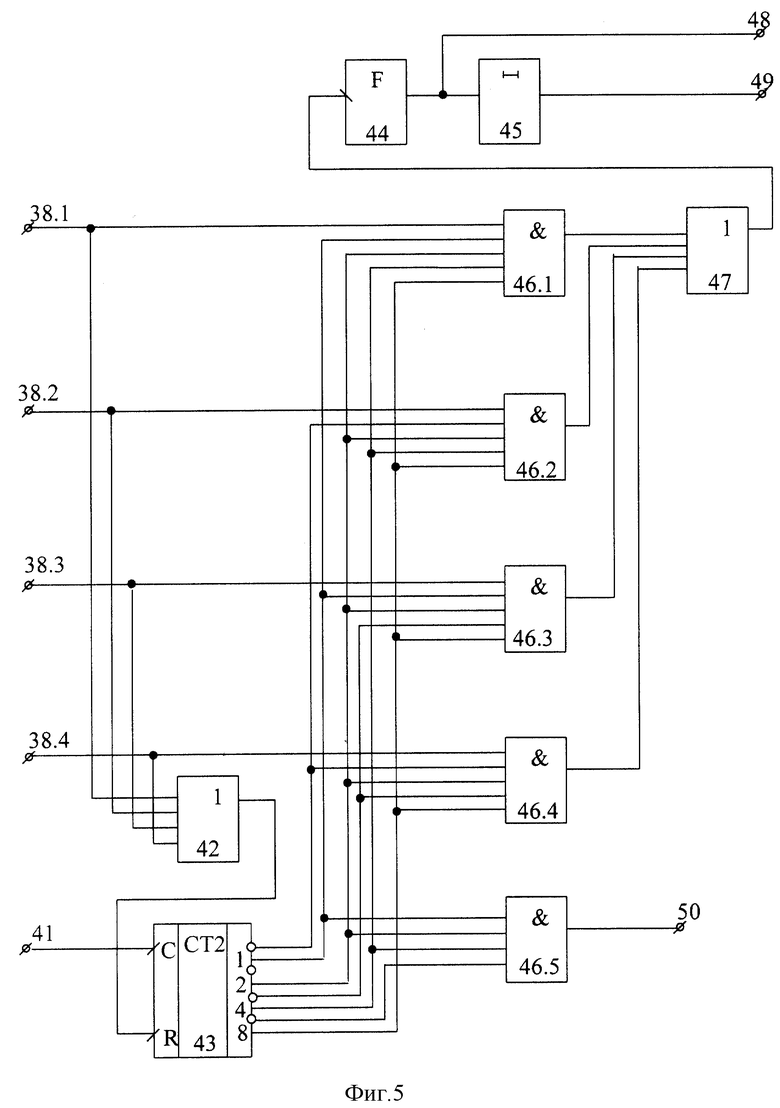

Функциональная схема перестраиваемого счетчика 7 (см. фиг. 5) содержит: 381-384 - группу управляющих входов; 41 - тактовый вход; 42 - первый элемент ИЛИ; 43 - двоичный счетчик; 44 - формирователь сигнала заднего фронта импульса; 45 - элемент задержки; 461-465 - группу элементов И; 47 - второй элемент ИЛИ; 48, 49, 50 - соответственно третий, второй и первый управляющие выходы.

Функциональная схема коммутатора 8 (см. фиг. 6) содержит: 381-384 - группу управляющих входов; 51 - информационный вход; 521-524 - группу элементов И; 531-534 - группу информационных выходов.

Функциональная схема канального коммутатора 9 (см. фиг. 7) содержит: 10 - канальный вход-выход; 11 и 12 - соответственно первый и второй управляющие входы; 14 - второй информационный вход; 51 -информационный выход; 54 - первый информационный вход; 55 - элемент ИЛИ; 561, 562 - соответственно первый и второй элементы И.

Функциональная схема ключа 13 управления (см. фиг. 8) содержит: 12, 48 и 50 - соответственно первый, третий и второй управляющие входы; 54 - первый информационный выход; 57 - информационный вход; 58 - первый элемент И; 59 - RS-триггер; 601 и 602 - соответственно второй и третий элементы И; 61 - второй информационный выход.

Функциональная схема вычислителя 16 синдрома (см. фиг. 9) содержит: 401-407 - группу управляющих входов; 41 - тактовый вход; 49 - управляющий вход; 531-534 - группу информационных входов; 61 - информационный вход; 621-627 - группу элементов И; 631-637 - группу сумматоров по модулю два; 641-649 - группу D-триггеров; 651-659 - группу информационных выходов.

Функциональная схема перестраиваемого регистра 17 памяти (см. фиг. 10) содержит: 191-1915 - группу информационных выходов; 41 - тактовый вход; 49 - первый управляющий вход; 531-534 - группу информационных входов; 66 - второй управляющий вход; 671-673 - группу элементов ИЛИ; 681-6815 - группу D-триггеров; 691-6915 - группу элементов И.

Функциональные схемы блока 2 оценки состояния канала, блока 3 выбора кода, кодера 6 полинома, перестраиваемого счетчика 7, коммутатора 8, вычислителя 16 синдрома и перестраиваемого регистра 17 памяти приведены для примера реализации устройства адаптивного кодирования и декодирования в случае, когда используются H=4 циклических кода с параметрами (15,6), (14,6), (11,6) и (10,6), где первое число в скобках обозначает длину N1,  кода, а второе число - количество M информационных символов в кодовой комбинации.

кода, а второе число - количество M информационных символов в кодовой комбинации.

Элементы устройства адаптивного кодирования и декодирования взаимосвязаны следующим образом.

Первая группа управляющих входов 11, 12 устройства соединена с первой группой управляющих входов блока 2 оценки состояния канала, входы 51-5H второй группы управляющих входов устройства соединены с первыми входами группы элементов ИЛИ 41-4H; канальный вход-выход 10 устройства соединен с входом-выходом канального коммутатора 9; вход 11 управления декодированием соединен с первым управляющим входом канального коммутатора 9, вход 12 управления кодированием соединен с управляющим входом блока 3 выбора кода, первым управляющим входом ключа 13 управления и вторым управляющим входом канального коммутатора 9; информационный вход 14 устройства соединен с первым входом сумматора 15 по модулю два и вторым информационным входом канального коммутатора 9; группа выходов блока 2 оценки состояния канала соединена с группой входов блока 3 выбора кода; выходы группы управляющих выходов блока 3 выбора кода соединены с входами второй группы управляющих входов блока 2 оценки состояния канала и вторыми входами группы элементов ИЛИ 41-4H, управляющий выход блока 3 выбора кода соединен с управляющим входом блока 2 оценки состояния канала; выходы группы схем ИЛИ 41-4H соединены с входами групп управляющих входов кодера 6 полинома, перестраиваемого счетчика 7 и коммутатора 8; группа управляющих выходов кодера 6 полинома соединена с группой управляющих входов вычислителя 16 синдрома; первый управляющий выход перестраиваемого счетчика 7 соединен со вторым управляющим входом ключа 13 управления, второй управляющий выход перестраиваемого счетчика 7 соединен с управляющим входом вычислителя 16 синдрома, первым управляющим входом перестраиваемого регистра 17 памяти и третьим управляющим входом ключа 13 управления, третий управляющий выход перестраиваемого счетчика 7 соединен со вторым входом элемента И 20; группа информационных выходов коммутатора 8 соединена с группами информационных входов вычислителя 16 синдрома и перестраиваемого регистра 17 памяти; первый и второй информационные выходы ключа 13 управления соединены соответственно с первым информационным входом канального коммутатора 9 и информационным входом вычислителя 16 синдрома; выход сумматора 15 по модулю два соединен с информационным входом ключа 13 управления; группа информационных выходов вычислителя 16 синдрома соединена с группой входов элемента ИЛИ-НЕ 21, а последний из этой группы выход соединен со вторым входом сумматора 15 по модулю два; группа информационных выходов перестраиваемого регистра 17 памяти соединена с группой информационных выходов 191-19N устройства; выход элемента И 20 соединен со вторым управляющим входом перестраиваемого регистра 17 памяти; выход элемента ИЛИ-НЕ 21 соединен с первым входом элемента И 20.

В блоке 2 оценки состояния канала (см. фиг. 2) для примера реализации входы 11 и 12 первой группы управляющих входов соединены с тактовыми входами соответствующих счетчиков 251 и 252; вход 221 второй группы управляющих входов соединен с первыми входами элементов И 261, 271; вход 222 - с первыми входами элементов И 262, 272; вход 223 - с первыми входами элементов И 263, 273; вход 224 - с первыми входами элементов И 264, 274; управляющий вход 23 соединен с первым входом первого элемента ИЛИ 241 и вторым входом второго элемента ИЛИ 242; выходы первого элемента ИЛИ 241 и второго элемента ИЛИ 242 соединены соответственно с входами сброса первого счетчика 251 и второго счетчика 252; первый выход первого счетчика 251 соединен со вторыми входами элементов И 261, 262; второй выход - со вторым входом элемента И 264, третий выход - с третьими входами элементов И 261, 264; четвертый выход - с четвертым входом элемента И 261; пятый выход - со вторым входом элемента И 263; шестой выход - с пятым выходом элемента И 261 и третьим выходом элемента И 262; первый выход второго счетчика 252 соединен со вторыми входами элементов И 271, 272; второй выход - с третьими входами элементов И 271, 272 и вторым входом элемента И 274; третий выход - с четвертым входом элемента И 272; четвертый выход - с пятым входом элемента И 272 и третьим входом элемента И 274; пятый выход - с четвертым входом элемента И 271, шестым входом элемента И 272, вторым входом элемента И 273 и четвертым входом элемента И 274; шестой выход - с третьим входом элемента И 273 и пятым входом элемента И 274; выходы элементов И 261-264 соединены с входами третьего элемента ИЛИ 281; выходы элементов И 271-274 соединены с входами четвертого элемента ИЛИ 282; выход третьего элемента ИЛИ 281 соединен со вторым входом первого элемента ИЛИ 241 и с выходом 291 группы управляющих выходов блока 2 оценки состояния канала; выход четвертого элемента ИЛИ 282 соединен с первым входом второго элемента ИЛИ 242 и с выходом 292 группы управляющих выходов блока 2 оценки состояния канала.

В блоке 3 выбора кода (см. фиг. 3) для примера реализации управляющий вход 12 соединен со вторыми входами элементов ИЛИ 371-374; входы 291 и 292 группы управляющих входов соединены соответственно с входами сдвига вверх и вниз первого регистра 31 сдвига; вход 30 начальной установки соединен с третьим входом элемента ИЛИ 34, входом второго элемента 352 задержки и входом сброса второго регистра 36 сдвига; первый выход первого регистра 31 сдвига соединен со вторыми входами элемента ИЛИ 34 и первого элемента И 331, последний [(2B+1)-й] выход первого регистра 31 сдвига - с первыми входами элемента ИЛИ 34 и второго элемента И 332; выход первого инвертора 321 соединен с первым входом первого элемента И 331; выход второго инвертора 322 соединен со вторым входом второго элемента И 332; выходы первого элемента И 331 и второго элемента И 332 соединены соответственно с входами сдвига вверх и вниз второго регистра 36 сдвига; выход элемента ИЛИ 34 соединен с входом сброса первого регистра 31 сдвига, входом первого элемента 351 задержки и управляющим выходом 23 блока 3 выбора кода; выход первого элемента 351 задержки соединен с входом установки в состояние "1" (B+1)-го разряда первого регистра 31 сдвига; выход второго элемента 352 задержки соединен с входом установки в состояние "1" первого разряда второго регистра 36 сдвига; первый выход второго регистра 36 сдвига соединен с входом первого инвертора 321 и первым входом элемента И 371, второй выход - с первым входом элемента И 372, третий выход - с первым входом элемента И 373, четвертый выход - с входом второго инвертора 322 и первым входом элемента И 374; выходы элементов И 371-374 соединены соответственно с выходами 221-224 группы управляющих выходов блока 3 выбора кода.

В кодере 6 полинома (см. фиг. 4) для примера реализации вход 381 группы управляющих входов соединен с третьими входами элементов ИЛИ 392, 393, вторыми входами элементов ИЛИ 394, 395 и выходом 401 группы управляющих выходов кодера; вход 382 группы управляющих входов соединен с первым входом элемента ИЛИ 391, выходом 406 группы управляющих выходов кодера, вторым входом элемента ИЛИ 393 и первым входом элемента ИЛИ 395; вход 383 группы управляющих входов соединен со вторыми входами элементов ИЛИ 391, 392 и первым входом элемента ИЛИ 394; вход 384 группы управляющих входов соединен с первыми входами элементов ИЛИ 392 и 393; выходы элементов ИЛИ 391-395 соединены соответственно с выходами 407, 405, 404, 403 и 402 группы управляющих выходов кодера 6 полинома.

В перестраиваемом счетчике 7 (см. фиг. 5) для примера реализации входы 381-384 группы управляющих входов соединены с входами первого элемента ИЛИ 42 и первыми входами соответствующих элементов И 461-464; тактовый вход 41 соединен с тактовым входом счетчика 43; выход первого элемента ИЛИ 42 соединен с входом сброса счетчика 43; первый инверсный выход счетчика 43 соединен со вторыми входами элементов И 462, 464, первый прямой выход - со вторыми входами элементов И 461, 463 и первым входом элемента И 465, второй прямой выход - с третьими входами элементов И 461-464 и вторым входом элемента И 465, третий инверсный выход - с четвертыми входами элементов И 463, 464, третий прямой выход - с четвертыми входами элементов И 461, 462 и третьим входом элемента И 465, четвертый инверсный выход - с четвертым входом элемента И 465, четвертый прямой выход - с пятыми входами элементов И 461-464; выход формирователя 44 сигнала заднего фронта импульса соединен с входом элемента 45 задержки и третьим управляющим выходом 48 перестраиваемого счетчика 7; выход элемента 45 задержки соединен со вторым управляющим выходом 49 перестраиваемого счетчика 7; выходы элементов И 461-464 соединены с соответствующими входами второго элемента ИЛИ 47; выход элемента И 465 соединен с первым управляющим выходом 50 перестраиваемого счетчика 7; выход второго элемента ИЛИ 47 соединен с входом формирователя 44 сигнала заднего фронта импульса.

В коммутаторе 8 (см. фиг. 6) для примера реализации входы 381-384 группы управляющих входов соединены соответственно с первыми входами элементов И 521-524; информационный вход 51 соединен со вторыми входами элементов И 521-524; выходы элементов И 521-524 соединены соответственно с выходами 531-534 группы информационных выходов коммутатора 8.

В канальном коммутаторе 9 (см. фиг. 7) первый управляющий вход 11 соединен со вторым входом второго элемента И 562; второй управляющий вход 12 соединен с первым входом первого элемента И 561; первый информационный вход 54 и второй информационный вход 14 соединены с входами элемента ИЛИ 55; выход элемента ИЛИ 55 соединен со вторым входом первого элемента И 561; выход первого элемента И 561 соединен с первым входом второго элемента И 562 и канальным входом-выходом 10; выход второго элемента И 562 соединен с информационным выходом 51 канального коммутатора 9.

В ключе 13 управления (см. фиг. 8) первый управляющий вход 12 и второй управляющий вход 50 соединены с входами первого элемента И 58; третий управляющий вход 48 соединен с входом сброса RS-триггера 59; информационный вход 57 соединен со вторыми входами второго элемента И 601 и третьего элемента И 602; выход первого элемента И 58 соединен с входом установки в состояние "1" RS-триггера 59; прямой и инверсный выходы RS-триггера 59 соединены соответственно с первыми входами второго элемента И 601 и третьего элемента И 602; выход второго элемента И 601 и выход третьего элемента И 602 соединены соответственно с первым информационным выходом 54 и вторым информационным выходом 61 ключа 13 управления.

В вычислителе 16 синдрома (см. фиг. 9) для примера реализации входы 401-407 группы управляющих входов соединены соответственно со вторыми входами элементов И 621-627; тактовый вход 41 соединен с тактовыми входами D-триггеров 641-649; управляющий вход 49 соединен соответственно с входами сброса D-триггеров 641-649; входы 531-534 группы информационных входов соединены соответственно со вторыми входами сумматоров 631-634 по модулю два; информационный вход 61 соединен с первыми входами элементов И 621-627; выходы элементов И 621-627 соединены соответственно с первыми входами сумматоров 631-637 по модулю два; выходы сумматоров 631, 632, 633-637 по модулю два соединены соответственно с информационными входами D-триггеров 641, 642, 645-649; выход D-триггера 641 соединен с третьим входом сумматора 632 по модулю два и выходом 651 вычислителя 16 синдрома; выход D-триггера 642 соединен с выходом 652 вычислителя 16 синдрома и информационным входом D-триггера 643, выход которого соединен с выходом 653 вычислителя 16 синдрома и информационным входом D-триггера 644; выходы D-триггеров 644-648 соединены соответственно с третьими входами сумматоров 633-637 по модулю два и выходами 654-658 вычислителя 16 синдрома.

В перестраиваемом регистре 17 памяти (см. фиг. 10) для примера реализации тактовый вход 41 соединен с тактовыми входами D-триггеров 681-6815; первый управляющий вход 49 соединен с входами сброса D-триггеров 681-6815; вход 531 группы информационных входов соединен с информационным входом D-триггера 681, входы 532-534 группы информационных входов соединены соответственно с первыми входами элементов ИЛИ 671-673; второй управляющий вход 66 соединен со вторыми входами элементов И 691-6915; выходы элементов ИЛИ 671-673 соединены соответственно с информационными входами D-триггеров 682, 685, 686; выход D-триггера 681 соединен с первым входом элемента И 691 и вторым входом элемента ИЛИ 671; выходы D-триггеров 682, 683 соединены соответственно с первыми входами элементов И 692, 693 и информационными входами D-триггеров 683, 684; выходы D-триггеров 684, 685 соединены соответственно с первыми входами элементов И 694, 695 и вторыми входами элементов ИЛИ 672, 673; выходы D-триггеров 686-6814 соединены соответственно с первыми входами элементов И 696-6914 и информационными входами D-триггеров 687-6815; выход D-триггера 6815 соединен с первым входом элемента И 6915; выходы элементов И 691-6915 соединены соответственно с выходами 191-1915 группы информационных выходов перестраиваемого регистра 17 памяти.

Устройство адаптивного кодирования и декодирования работает следующим образом.

Устройство может быть использовано в режимах кодирования и декодирования сообщений в системах передачи информации с обратным каналом связи. Выбор режима зависит от наличия сигналов на управляющих входах 11 (декодирование) и 12 (кодирование). Пусть обратная связь построена по принципу решающей обратной связи. Тогда на передающей стороне данное устройство применяется как кодирующее, а на приемной стороне - как декодирующее.

Используемый для передачи сообщений код выбирается на передающей стороне (в режиме кодирования). Выбор кода, соответствующего при заданных требованиях к верности передачи уровню помех в канале, происходит с помощью блока 2 оценки состояния канала и блока 3 выбора кода. В режиме кодирования сигнал, несущий информацию о номере кода, поступает на I-й,  выход группы управляющих выходов блока 3 выбора кода. В режиме декодирования блок 2 оценки состояния канала и блок 3 выбора кода в работе не участвуют. Сигнал, несущий информацию о номере кода, поступает на вход 51,

выход группы управляющих выходов блока 3 выбора кода. В режиме декодирования блок 2 оценки состояния канала и блок 3 выбора кода в работе не участвуют. Сигнал, несущий информацию о номере кода, поступает на вход 51,  второй группы управляющих входов устройства.

второй группы управляющих входов устройства.

Рассмотрим работу устройства по выбору корректирующего кода в режиме кодирования.

Пусть в устройстве используется H кодов, причем с увеличением номера I,  кода уменьшается его корректирующая способность (его кодовое расстояние D).

кода уменьшается его корректирующая способность (его кодовое расстояние D).

Таким образом, при M = const, выполняется:

D1 > D2 > ... > DH,

N1 > N2 > ... > NH.

При фиксированных требованиях к верности передачи в случае уменьшения уровня помех устройство должно выбирать код с меньшей корректирующей способностью, а в случае увеличения уровня помех - код с большей корректирующей способностью. При таком подходе обеспечивается эффективное использование канала связи за счет изменения длины кода.

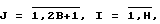

Для решения задачи выбора кода предлагается использовать вероятностный автомат с множеством состояний S = {SJI},

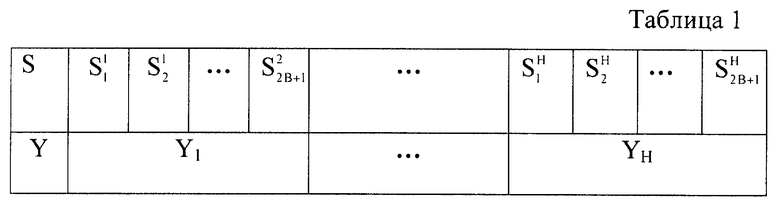

При этом S1I - S2B+1I - подмножество состояний, находясь в которых автомат выбирает для передачи I-й код. Обозначим через YI выходной сигнал автомата, определяющий выбор I-го кода. Соответствие состояний SJI автомата и выходных сигналов YI приведено в табл. 1.

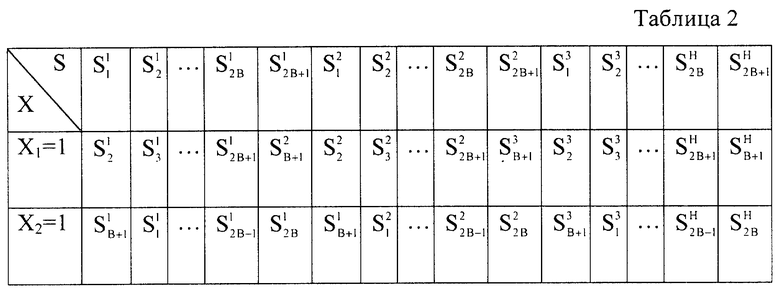

При переходе автомата на I-й код он устанавливается в состояние SB+1I. Если при передаче кодовой комбинации корректирующая способность кода больше необходимой, в автомат поступает сигнал "поощрение" X1, если корректирующая способность меньше необходимой - сигнал "наказание" X2. Изменение состояний автомата в зависимости от входных сигналов X1 и X2 приведено в табл. 2.

Таким образом, если автомат находится в состоянии SB+1I, I < H, и число "поощрений" превысит число "наказаний" на величину B, то автомат перейдет в состояние SB+1I+1, т.е. автомат перейдет с I-го кода на (I+1)-й код, имеющий меньшую корректирующую способность. Если же автомат находится в состоянии SB+1I, I > 1, и число "наказаний" превысит число "поощрений" на величину B, то автомат перейдет в состояние SB+1I-1, т.е. автомат перейдет с I-го на (I-1)-й код, имеющий большую корректирующую способность.

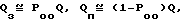

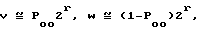

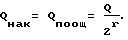

Поскольку рассматривается система с решающей обратной связью, то для формирования сигналов "поощрение" целесообразно использовать сигналы "подтверждение", сигналов "наказание" - сигналы "запрос". Сигналы "запрос" и "подтверждение" передает приемник по обратному каналу в случае соответственно обнаружения ошибок (вероятность Pоо) и отсутствия или необнаружения ошибок (вероятность 1-Pоо) в принятой кодовой комбинации. Таким образом, если происходит Q передач, то можно считать, что

где Qз и Qп - соответственно число сигналов "запрос" и "подтверждение".

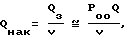

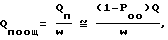

Для определения соответствия корректирующей способности кода помеховой обстановке в канале применен следующий подход. При соответствии используемого для передачи кода уровню помех в канале число QНАК сигналов "наказание" должно быть равно числу QПООЩ сигналов "поощрение". Обеспечение указанного равенства достигается за счет определения QНАК и QПООЩ из соотношений

где v, w - постоянные коэффициенты, v > 1, w > 1.

Выберем

где r - разрядность счетчика, используемого в качестве делителя при определении QНАК и QПООЩ.

Тогда

Если уровень помех увеличится, то для используемого кода увеличится Pоо. Следовательно, разность числа сигналов "наказание" и "поощрение" станет положительной и будет расти с ростом Q. Когда эта разность превысит величину B, осуществляется переход на код с большей корректирующей способностью, соответствующий новому уровню помех. При этом коэффициент деления v увеличивается, а коэффициент деления w уменьшается, что обеспечивает в новых условиях равенство числа сигналов "наказание" и "поощрение".

Аналогично при уменьшении уровня помех происходит переход на код с меньшей корректирующей способностью.

Схемной реализацией преобразователей сигналов "запрос" и "подтверждение" соответственно в сигналы "наказание" и "поощрение" является реализация блока 2 оценки состояния канала. Преобразование сигналов "запрос" в сигналы "наказание" выполняется перестраиваемой схемой деления на v, реализованной на первом двоичном счетчике 251, группе элементов И 26 и элементе ИЛИ 281. Преобразование сигналов "подтверждение" в сигналы "поощрение" выполняется перестраиваемой схемой деления на w, реализованной на втором двоичном счетчике 252, группе элементов И 27 и элементе ИЛИ 282.

Схемной реализацией вероятностного автомата является реализация блока 3 выбора кода. Состояния SJI моделируются с помощью регистров 31 и 36, при этом параметру J соответствует единица в J-м разряде регистра 31, а параметру I - единица в I-м разряде регистра 36.

Начальные состояния блока 2 оценки состояния канала и блока 3 выбора кода определяются при включении питания. Сигнал начальной установки, поступающий на вход 30 блока 3 выбора кода, устанавливает через элемент ИЛИ 34 в нулевое состояние регистры 31 и 36. Затем через время, определяемое элементом 351 задержки, в (B+1)-й разряд регистра 31 записывается единица, а через время, определяемое элементом 352 задержки, в 1-й разряд регистра 36 также записывается единица. Вследствие этого вероятностный автомат устанавливается в состояние SB+1I. Это определяет выбор для передачи кода с номером 1 с наибольшей корректирующей способностью и максимальной длиной. Сигнал с первого выхода регистра 36 через элемент И 371 подается на выход 221, а затем на второй вход элемента ИЛИ 41 и на вход 221 блока 2 оценки состояния канала, в котором подготавливаются элементы И 261, 271.

Также сигнал начальной установки, поступающий с выхода 23 блока 3 выбора кода на соответствующий вход блока 2 оценки состояния канала, устанавливает в нулевое состояние первый двоичный счетчик 251 (через элемент ИЛИ 241) и второй двоичный счетчик 252 (через элемент ИЛИ 242). Сигналы "запрос", поступающие на вход 11, подсчитываются первым двоичным счетчиком 251, который совместно с элементом И 261 осуществляет деление на v1. В результате на выходе 291 блока 2 оценки состояния канала формируются сигналы "наказание". Аналогично, сигналы "подтверждение", поступающие на вход 12, преобразуются вторым двоичным счетчиком 252 совместно с элементом И 271 в сигналы "поощрение", поступающие на выход 292.

В блоке 3 выбора кода сигналы "наказание" и "поощрение" поступают соответственно на входы сдвига вверх и вниз регистра 31. Если в результате превышения числа сигналов "наказание" над числом сигналов "поощрение" записанная в регистре 31 единица сдвигается в 0-й разряд, то сигнал с 0-го выхода регистра 31 при открытом элементе И 331 поступает на вход сдвига вверх регистра 36. При этом записанная в I-м, I > 1, разряде регистра 36 единица сдвигается в (I-1)-й разряд, в результате чего снимается сигнал с выхода 22I и появляется сигнал на выходе 22I-1 блока 3 выбора кода. Так происходит переход на код с большей корректирующей способностью.

Если в результате превышения числа сигналов "поощрение" над числом сигналов "наказание" записанная в регистре 31 единица сдвигается в (2B+2)-й разряд, то сигнал с (2B+2)-го выхода регистра 31 при открытом элементе И 332 поступает на вход сдвига вниз регистра 36. При этом записанная в I-м, I < H, разряде регистра 36 единица сдвигается в (I+1)-й разряд, в результате чего снимается сигнал с выхода 22I и появляется сигнал на выходе 22I+1 блока 3 выбора кода. Так происходит переход на код с меньшей корректирующей способностью.

При появлении сигнала на 0-м или (2B+2)-м выходе регистра 31 происходит установка через элемент ИЛИ 34 регистра 31 в нулевое состояние и последующая запись через элемент 351 задержки единицы в (B+1)-й разряд регистра 31.

Если единица записана в 1-м разряде регистра 36 (для передачи используется код с номером 1, имеющий максимальную корректирующую способность), то элемент И 331 закрыт и сигнал с 0-го выхода регистра 31 (при его появлении) не будет поступать на вход сдвига вверх регистра 36. Аналогично, если единица записана в последнем (H-м) разряде регистра 36 (для передачи используется код с номером H, имеющий минимальную корректирующую способность), то элемент И 332 закрыт и сигнал с (2B+2)-го выхода регистра 31 (при его появлении) не будет поступать на вход сдвига вниз регистра 36.

Рассмотрим обобщенный алгоритм работы устройства.

В режиме кодирования на вход 12 управления кодированием подается сигнал, на вход 11 управления декодированием сигнал не подается, на входы 51-5H второй группы управляющих входов сигналы также не подаются.

Сигнал управления кодированием поступает на второй управляющий вход 12 канального коммутатора 9, в котором осуществляется подключение первого 54 и второго 14 информационных входов к канальному входу-выходу 10 устройства. Так обеспечивается вывод формируемой устройством кодовой комбинации в канал связи. Кроме того, сигнал управления кодированием поступает на первый управляющий вход ключа 13 управления, разрешая прием управляющих сигналов, поступающих на второй управляющий вход ключа 13 управления с первого управляющего выхода перестраиваемого счетчика 7. Сигнал управления кодированием поступает также на управляющий вход блока 3 выбора кода, разрешая выдачу сигнала, несущего информацию о номере I,  используемого в данный момент для передачи сообщений кода на I-й выход группы управляющих выходов блока 3 выбора кода. Сигнал, определяющий номер I кода, поступает через элемент ИЛИ 41 на I-е входы групп управляющих входов кодера 6 полинома, перестраиваемого счетчика 7 и коммутатора 8 (в режиме кодирования коммутатор 8 в работе не участвует).

используемого в данный момент для передачи сообщений кода на I-й выход группы управляющих выходов блока 3 выбора кода. Сигнал, определяющий номер I кода, поступает через элемент ИЛИ 41 на I-е входы групп управляющих входов кодера 6 полинома, перестраиваемого счетчика 7 и коммутатора 8 (в режиме кодирования коммутатор 8 в работе не участвует).

В соответствии с указанным сигналом кодер 6 полинома выдает на группу управляющих входов вычислителя 16 синдрома сигналы, которые несут информацию об образующем полиноме выбранного кода. Кроме того, по переднему фронта указанного сигнала перестраиваемый счетчик 7 обнуляется, а затем отсчитывает такты, поступающие от генератора 18 тактовых импульсов. Также сигнал с выхода элемента ИЛИ 41 задает в перестраиваемом счетчике 7 число тактов, необходимых для передачи кодовой комбинации длины NI.

Процедура кодирования реализуется в соответствии с соотношением

a(x) = c(x)xK + r(x),

где a(x) - кодовый полином циклического кода,

c(x) - полином информационных символов,

K - степень образующего полинома g(x), равная числу контрольных символов кода;

r(x) - полином контрольных символов кода, равный остатку от деления полинома c(x)xK на полином g(x).

В течение первых M тактов происходит выдача информационных символов, поступающих с информационного входа 14 в устройство, через канальный коммутатор 9 (элементы ИЛИ 55 и И 561 на фиг. 7) на шину (канальный вход-выход) 10 подключения к каналу связи. Одновременно происходит процесс вычисления с помощью сумматора 15 по модулю два и вычислителя 16 синдрома полинома r(x), коэффициентами которого являются контрольные символы кода. При этом ключ 13 управления подключает выход сумматора 15 к информационному входу 61 вычислителя 16 синдрома.

На (M+1)-м такте перестраиваемый счетчик 7 с первого управляющего выхода 50 выдает сигнал, под действием которого ключ 13 управления подключает выход сумматора 15 по модулю два к первому информационному входу 54 канального коммутатора 9. В течение KI последующих тактов (с (M+1)-го такта по NI такт) контрольные символы из вычислителя 16 синдрома через сумматор 15 по модулю два, ключ 13 управления, канальный коммутатор 9 выдаются на шину 10 подключения устройства к каналу связи.

На NI-м такте по заднему фронту сигнала с небольшой задержкой во времени со второго управляющего выхода перестраиваемого счетчика 7 (выход 49 на фиг. 5) подается импульс на третий управляющий вход ключа 13 управления и управляющий вход вычислителя 16 синдрома, в которых элементы памяти устанавливаются в исходное состояние. Устройство вновь готово к кодированию очередной кодовой комбинации.

В режиме декодирования на вход 11 управления декодированием подается сигнал, на вход 12 управления кодированием сигнал не подается, на вход 5I,  второй группы управляющих входов подается сигнал, который указывает, что для кодирования сообщений передатчиком применяется корректирующий код с номером I.

второй группы управляющих входов подается сигнал, который указывает, что для кодирования сообщений передатчиком применяется корректирующий код с номером I.

Сигнал управления декодированием поступает на первый управляющий вход канального коммутатора 9, в котором осуществляется подключение шины (канального входа-выхода) 10 к информационному выходу канального коммутатора 9 (выход 51 на фиг. 7). Так обеспечивается ввод принимаемой из канала связи кодовой комбинации в устройство.

Сигнал, определяющий номер I кода, поступает через элемент ИЛИ 4I на I-е входы групп управляющих входов кодера 6 полинома, перестраиваемого счетчика 7 и коммутатора 8.

Под воздействием указанного сигнала в кодере 6 полинома и перестраиваемом счетчике 7 выполняются действия, аналогичные описанным выше в режиме кодирования.

Кроме того, под действием указанного сигнала в коммутаторе 8 осуществляется подключение (через элемент И 521 на фиг. 6) информационного выхода канального коммутатора 9 к I-м входам групп информационных входов вычислителя 16 синдрома и перестраиваемого регистра 17 памяти. Таким образом, принимаемая из канала кодовая комбинация поступает через канальный коммутатор 9, коммутатор 8, вычислитель 16 синдрома и перестраиваемый регистр 17 памяти.

В течение NI тактов происходит декодирование кодовой комбинации (вычисление остатка от деления принятого кодового полинома на образующий полином, называемого синдромом) в вычислителе 16 синдрома и одновременная запись ее в регистр 17 памяти. На NI-м такте перестраиваемый счетчик 7 с третьего управляющего выхода (выход 48 на фиг. 5) по заднему фронту импульса выдает сигнал опроса, который поступает на второй вход элемента И 20, на первый вход которого поступает логическая единица с выхода элемента ИЛИ-НЕ 21, если синдром равен нулю, или логический ноль, если синдром не равен нулю. Таким образом, если принятая кодовая комбинация не содержит обнаруживаемых кодом ошибок (синдром равен нулю), то на выходе элемента И 20 будет сигнал, который поступает на второй управляющий вход регистра 17 памяти (вход 66 на фиг. 10) и разрешает выдачу комбинации на информационные выходы 191-19N устройства. Если же в принятой кодовой комбинации обнаружены ошибки (синдром не равен нулю), то на второй управляющий вход регистра 17 памяти сигнал не поступает и комбинация не выдается получателю.

На NI-м такте по заднему фронту сигнала с небольшой задержкой во времени со второго управляющего выхода перестраиваемого счетчика 7 подается импульс на управляющий вход вычислителя 16 синдрома и первый управляющий вход перестраиваемого регистра 17 памяти, в которых элементы памяти устанавливаются в исходное состояние. Устройство вновь готово к декодированию очередной кодовой комбинации.

В качестве примера подтверждения работоспособности устройства рассмотрим реализацию блоков 2, 6, 7, 16 и 17 и функционирование устройства в случае, когда используются H= 4 циклических или укороченных циклических кода с образующими полиномами g1(x) = x9 + x6 + x5 + x4 + x + 1; g2(x) = x8 + x7 + x6 + x4 + 1; g3(x) = x5 + x4 + x2 + 1; g4(x) = x4 + x + 1.

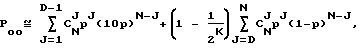

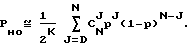

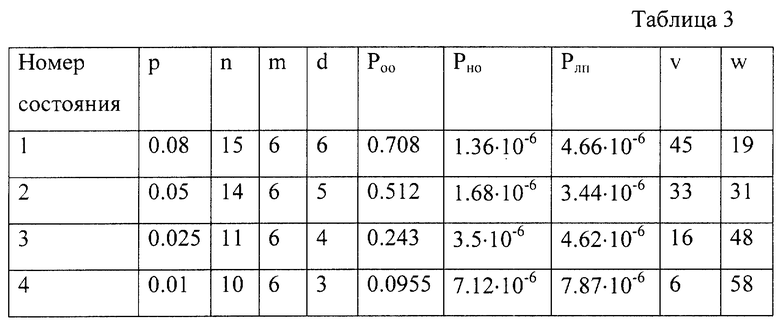

Рассмотрим вычисление коэффициентов деления v и w для кусочно-стационарного двоичного симметричного канала без памяти с вероятностью p ошибочного приема символа (элементарного сигнала). Канал может находиться в одном из H состояний. При увеличении номера I состояния уменьшается уровень помех в канале и, соответственно, вероятность p. Таким образом,

p1 > p2 > ... > pH.

Для систем с решающей обратной связью вероятность Pлп ложного приема сообщения определяется следующим образом:

где Pно - вероятность необнаружения ошибок в принятой кодовой комбинации.

Для двоичного симметричного канала без памяти вероятности Pоо и Pно при использовании кода длины N с минимальным кодовым расстоянием D определяются из соотношений

В табл. 3 приведены параметры кодов, обеспечивающих для различных p Pлп ≅ 10-5 и соответствующие (при r = 6) коэффициенты деления v и w.

Таким образом, в блоке 2 оценки состояния канала (фиг. 2) при сигнале на входе 221 первый двоичный счетчик 251 совместно с элементом И 261 осуществляет деление числа сигналов "запрос" на v1 = 45, так как элемент И 261 сработает при наборе 101101 (коэффициенты a5a4a3a2a1a0 в двоичной записи числа 45) в счетчике 251; при этом второй двоичный счетчик 252 совместно с элементом И 271 осуществляет деление числа сигналов "подтверждение" на w1 = 19, так как элемент И 271 сработает при наборе 010011 в счетчике 252. При сигнале на входе 222 первый двоичный счетчик 251 совместно с элементом И 262 осуществляет деление числа сигналов "запрос" на v2 = 33, так как элемент И 262 сработает при наборе 100001 в счетчике 251; второй двоичный счетчик 252 совместно с элементом И 272 осуществляет деление числа сигналов "подтверждение" на w2 = 31, так как элемент И 272 сработает при наборе 011111 в счетчике 252. При сигнале на входе 223 первый двоичный счетчик 251 совместно с элементом И 263 осуществляет деление числа сигналов "запрос" на v3 = 16, так как элемент И 263 сработает при наборе 010000 в счетчике 251; второй двоичный счетчик 252 совместно с элементом И 273 осуществляет деление числа сигналов "подтверждение" на w3 = 48, так как элемент И 273 сработает при наборе 110000 в счетчике 252. При сигнале на входе 224 первый двоичный счетчик 251 совместно с элементом И 264 осуществляет деление числа сигналов "запрос" на v4 = 6, так как элемент И 264 сработает при наборе 000110 в счетчике 251; второй двоичный счетчик 252 совместно с элементом И 274 осуществляет деление числа сигналов "подтверждение" на w4 = 58, так как элемент И 274 сработает при наборе 111010 в счетчике 252.

Представим образующие полиномы gI(x),  в нормализованной форме, при этом старший член полинома имеет степень K1 = 9, а K1-KI = 9-KI младших членов равны нулю: g1(x) = x9 + x6 + x5 + x4 + x + 1; g2(x)x = x9 + x8 + x7 + x5 + x; g3(x)x4 = x9 + x8 + x6 + x4; g4(x)x5 = x9 + x6 + x5.

в нормализованной форме, при этом старший член полинома имеет степень K1 = 9, а K1-KI = 9-KI младших членов равны нулю: g1(x) = x9 + x6 + x5 + x4 + x + 1; g2(x)x = x9 + x8 + x7 + x5 + x; g3(x)x4 = x9 + x8 + x6 + x4; g4(x)x5 = x9 + x6 + x5.

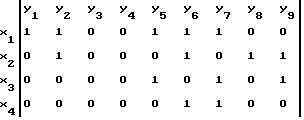

На основании значений коэффициентов полиномов в нормализованной форме составим матрицу для синтеза кодера 6 полинома, в которой строки соответствуют входным сигналам xI,  а столбцы - выходным сигналам yJ,

а столбцы - выходным сигналам yJ,  кодера:

кодера:

Из матрицы следует, что выходные сигналы yJ кодера 6 полинома определяются через его входные сигналы xI следующим образом:

y1 = x1, y2 = x1 ∨ x2, y3 = y4 = 0, y5 = x1 ∨ x3, y6 = x1 ∨ x2 ∨ x4, y7 = x1 ∨ x3 ∨ x4, y8 = x2, y9 = x2∨ x3.

В кодере 6 полинома (фиг. 4) логика соединений входов 38 с входами элементов ИЛИ 39 и выходами 40 соответствует логическим функциям y1, y2, y5-y9.

Поскольку длины кодов N1 = 15, N2 = 14, N3 = 11, N4 = 10, то в перестраиваемом счетчике 7 (фиг. 5) при сигнале на входе 381 сигнал на выходе 48 появится на 15-м такте генератора 18 тактовых импульсов, так как элемент И 461 сработает при наборе 1111 (коэффициенты a3a2a1a0 в двоичной записи числа 15) в счетчике 43. При сигнале на входе 382 сигнал на выходе 48 появится на 14-м такте генератора 18 тактовых импульсов, так как элемент И 462 сработает при наборе 1110 в счетчике 43. При сигнале на входе 383 сигнал на выходе 48 появится на 11-м такте генератора 18 тактовых импульсов, так как элемент И 463 сработает при наборе 1011 в счетчике 43. При сигнале на входе 384 сигнал на выходе 48 появится на 10-м такте генератора 18 тактовых импульсов, так как элемент И 464 сработает при наборе 1010 в счетчике 43. В соответствии с описанным выше алгоритмом работы устройства сигнал на третьем управляющем выходе 48 появляется по окончании сигнала на выходе элемента ИЛИ 47, так как сигнал на выходе 48 формируется формирователем 44 сигнала заднего фронта импульса, а на втором управляющем выходе 49 сигнал появляется с небольшой задержкой во времени. Поскольку на первом управляющем выходе 50 сигнал появляется на (M+1)-м такте, то для всех четырех кодов (M = 6) элемент И 465 сработает при наборе 0111 в счетчике 43.

В соответствии с видом полиномов g1(x)-g4(x) реализованы связи в вычислителе 16 синдрома (фиг. 9), который представляет собой схему деления на образующий полином. На элементах вычислителя 16 синдрома совместно с сумматором 15 по модулю два осуществляется и получение контрольных символов в режиме кодирования. Выходы 53 коммутатора 8 подключены к входам соответствующих сумматоров 63 по модулю два, а входы 40 группы управляющих входов через элементы И 62 реализуют схему деления на образующий полином кода, номер которого соответствует индексу входа 38 из группы управляющих входов, на котором появляется сигнал.

Поскольку длины кодов N1 = 15, N2 = 14, N3 = 11, N4 = 10, то в перестраиваемом регистре 17 памяти (фиг. 10) принятая кодовая комбинация с входа 531 подается на информационный вход D-триггера 681, с входа 532 - на информационный вход D-триггера 682 через элемент ИЛИ 671, с входа 533 - на информационный вход D-триггера 685 через элемент ИЛИ 672, с входа 534 - на информационный вход D-триггера 686, через элемент ИЛИ 673. В режиме кодирования сигнал задания режима работы подается на вход 12 устройства. Пусть на выходы 22 блока 3 выбора кода подан сигнал 0001, что означает, что для передачи сообщения применяется код длины N4 = 10 с образующим полиномом g4(x) = x4 + x + 1. При этом на выходах 404 и 405 кодера 6 полинома имеются сигналы, в перестраиваемом счетчике 7 подготовлен элемент И 464. Пусть с информационного входа 14 последовательно поступает комбинация информационных символов 111111. Эти информационные символы поступают через канальный коммутатор 9 на шину 10 подключения устройства к каналу связи и через сумматор 15 по модулю два и ключ 13 управления на информационный вход 61 вычислителя 16 синдрома, в котором в течение 6 тактов определяются контрольные символы. Затем на 7-м такте в ключе 13 управления открывается элемент И

58, RS-триггер 59 устанавливается в единичное состояние и открывается элемент И 601. Таким образом, в течение первых 6 тактов информационные символы 111111 с информационного входа 14 устройства поступают на второй информационный вход канального коммутатора 9 и через элементы ИЛИ 55 и И 561 на шину 10 подключения к каналу связи. Затем в течение следующих 4-х тактов сформированные в вычислителе 16 синдрома контрольные символы 1101 с информационного выхода 659 через сумматор 15 по модулю два, ключ 13 управления поступают на первый информационный вход 54 канального коммутатора 9 и через элементы ИЛИ 55 и И 561 на шину 10 подключения к каналу связи. Таким образом сформированная кодовая комбинация поступает в канал связи.

В режиме декодирования сигнал задания режима работы подается на вход 11 устройства. Пусть на входы 5 второй группы управляющих входов подан сигнал 0001, что означает, что для передачи сообщения применяется код длины N4 = 10 с образующим полиномом g4(x) = x4 + x = 1. При этом на выходах 404 и 405 кодера 6 полинома имеются сигналы, в коммутаторе 8 открыт элемент И 524, в перестраиваемом счетчике 7 подготовлен элемент И 464. Пусть на шину 10 подключения к каналу связи последовательно поступает кодовая комбинация 1111111101. Эта комбинация проходит через элемент И 562 канального коммутатора 9 на информационный вход коммутатора 8 и через элемент И 524 поступает на входы 534 вычислителя 16 синдрома и перестраиваемого регистра 17 памяти. За десять тактов генератора 18 эта комбинация записывается в D-триггеры 686-6815 регистра 17, а в вычислителе 16 синдрома осуществляется деление полинома кодовой комбинации на образующий полином. На 10-м такте по заднему фронту сигнала на выходе элемента ИЛИ 47 перестраиваемого счетчика 7 формируется импульс опроса, который появляется на выходе 48. Так как на выходах 656-659 вычислителя 16 синдрома в этот момент появляются нули, то элемент И 20 открывается. Следовательно, на вход 66 регистра 17 памяти поступает сигнал и комбинация выдается получателю. Затем с задержкой, необходимой для считывания информации, с выхода 49 подается сигнал, который по соответствующим управляющим входам 49 устанавливает в нулевое состояние D-триггеры 64 вычислителя 16 синдрома и D-триггеры 68 перестраиваемого регистра 17 памяти.

Пусть на шину 10 подключения к каналу связи поступает комбинация с ошибкой 1111110101. В вычислителе 16 синдрома полином этой комбинации делится на образующий полином. Так как на выходах 656-659 вычислителя 16 синдрома к моменту опроса не появляются нули, то элемент И 20 не открывается. Следовательно, элементы И 69 регистра 17 не открываются и комбинация с выходов 19 не выдается получателю.

Временная диаграмма работы устройства для рассматриваемого примера приведена на фиг. 11.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство декодирования циклических кодов | 1987 |

|

SU1496009A1 |

| СПОСОБ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ N ОБЪЕКТОВ | 2000 |

|

RU2198418C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АДАПТИВНЫМ МОБИЛЬНЫМ РОБОТОМ | 1998 |

|

RU2143334C1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 1998 |

|

RU2130641C1 |

| УСТРОЙСТВО ДЛЯ СЕЙСМИЧЕСКОГО ЗОНДИРОВАНИЯ ДНА ВОДОЕМОВ | 2002 |

|

RU2212692C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АДАПТИВНЫМ МОБИЛЬНЫМ РОБОТОМ | 2000 |

|

RU2187832C2 |

| УСТРОЙСТВО ПРИНЯТИЯ НЕЧЕТКИХ РЕШЕНИЙ | 1993 |

|

RU2054708C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ РИТМИЧНОСТИ ПРОЦЕССА | 1998 |

|

RU2133979C1 |

Изобретение относится к области техники связи и может быть использовано в системах передачи информации при построении дискретного канала как кодирующее и декодирующее устройство кодов различной корректирующей способности с обнаружением ошибок. Технический результат - уменьшение времени использования канала связи за счет уменьшения корректирующей способности и длины кода при улучшении помеховой обстановки в канале. Для достижения технического результата в устройство, содержащее кодер полинома, перестраиваемый счетчик, коммутатор, канальный коммутатор, ключ управления, сумматор по модулю два, вычислитель синдрома, перестраиваемый регистр памяти, генератор тактовых импульсов, элемент И, элемент ИЛИ-НЕ, дополнительно введены блок оценки состояния канала, блок выбора кода, элементы ИЛИ. Устройство обеспечивает адаптацию кода к изменяющимся характеристикам канала связи, в частности к уровню помех в канале связи. Устройство позволяет увеличить количество источников и получателей сообщений, передающих информацию по выделенному каналу. 11 ил., 3 табл.

Устройство адаптивного кодирования и декодирования, содержащее кодер полинома, перестраиваемый счетчик, коммутатор, канальный коммутатор, ключ управления, сумматор по модулю два, вычислитель синдрома, перестраиваемый регистр памяти, генератор тактовых импульсов, элементы И, ИЛИ-НЕ, при этом информационный вход устройства соединен с первым входом сумматора по модулю два и вторым информационным входом канального коммутатора, вход-выход которого соединен с канальным входом-выходом устройства, вход управления декодированием устройства соединен с первым управляющим входом канального коммутатора, вход управления кодированием устройства соединен со вторым управляющим входом канального коммутатора и первым управляющим входом ключа управления, группа управляющих выходов кодера полинома соединена с группой управляющих входов вычислителя синдрома, третий и первый управляющие выходы перестраиваемого счетчика соединены соответственно со вторым входом элемента И и вторым управляющим входом ключа управления, второй управляющий выход перестраиваемого счетчика соединен с управляющим входом вычислителя синдрома, третьим управляющим входом ключа управления и первым управляющим входом перестраиваемого регистра памяти, группа информационных выходов коммутатора соединена с группами информационных входов вычислителя синдрома и перестраиваемого регистра памяти, информационный выход канального коммутатора соединен с информационным входом коммутатора, второй и первый информационные выходы ключа управления соединены соответственно с информационным входом вычислителя синдрома и первым информационным входом канального коммутатора, выход сумматора по модулю два соединен с информационным входом ключа управления, группа информационных выходов вычислителя синдрома соединена с входами схемы ИЛИ-НЕ, а последний из этой группы выход соединен со вторым входом сумматора по модулю два, группа информационных выходов перестраиваемого регистра памяти соединена с группой информационных выходов устройства, выход генератора тактовых импульсов соединен с тактовыми входами перестраиваемого счетчика, вычислителя синдрома и перестраиваемого регистра памяти, выход элемента ИЛИ-НЕ соединен с первым входом элемента И, выход которого соединен со вторым управляющим входом перестраиваемого регистра памяти, отличающееся тем, что в него дополнительно введены блок оценки состояния канала, блок выбора кода, группа элементов ИЛИ, при этом вход управления кодированием устройства соединен с управляющим входом блока выбора кода, входы второй группы управляющих входов устройства соединены с первыми входами группы элементов ИЛИ, первая группа управляющих входов устройства соединена с первой группой управляющих входов блока оценки состояния канала, группа выходов которого соединена с группой входов блока выбора кода, выходы группы управляющих выходов которого соединены с входами второй группы управляющих входов блока оценки состояния канала и со вторыми входами группы элементов ИЛИ, управляющий выход блока выбора кода соединен с управляющим входом блока оценки состояния канала, выходы группы схем ИЛИ соединены с входами групп управляющих входов кодера полинома, перестраиваемого счетчика и коммутатора.

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Устройство декодирования циклических кодов | 1987 |

|

SU1496009A1 |

| US 5063576 A, 05.11.1991 | |||

| US 5392037 A1, 21.02.1995 | |||

| DE 4136090 A1, 25.02.1993 | |||

| DE 1950728 A1, 28.09.1995 | |||

| СПОСОБ КОЛИЧЕСТВЕННОГО ОПРЕДЕЛЕНИЯ МИКРООРГАНИЗМОВ В ВЕЩЕСТВАХ | 0 |

|

SU200124A1 |

Авторы

Даты

2001-06-20—Публикация

2000-05-15—Подача