Изобретение относится к вычислительной технике и может быть использовано для организации межмашинного обмена в распределительных вычислительных комплексах и сетях ЭВМ.

Известно устройство [1] для коммутации сообщений, содержащее блок входного накопителя, блок дешифрации заголовков, блок центрального накопителя, блок микропрограммного управления, арифметико-логический блок, блок приема сообщений, два блока коммутации и блок выдачи сообщений, причем выход блока микропрограммного управления соединен с управляющими входами арифметико-логического блока, блока центрального накопителя и блока входного накопителя, выход которого соединен с первым информационным входом арифметико-логического блока и входом блока дешифрации заголовков, выход которого соединен с входом заголовков блока микропрограммного управления.

Однако это устройство обладает низкой производительностью, которая обусловлена тем, что в любой момент времени оно обрабатывает (коммутирует) не более одного сообщения.

Наиболее близким по технической сущности и достигаемому положительному эффекту является устройство [2] для коммутации сообщений, содержащее блоки сопряжения с каналами, имеющие шины приема-передачи и управления, являющиеся входами-выходами устройства, блок микропрограммного управления, первый выход которого соединен с объединенными первыми входами блоков сопряжения, блок оперативной памяти, информационную и адресную шины, приоритетный блок, блок выбора маршрута и блок ведения очередей, первые и второй входы-выходы которого соединены соответственно с адресной и информационной шинами устройства, а третий вход-выход с первым входом-выходом блока оперативной памяти, другой вход которого подсоединен к четвертому выходу блока ведения очередей, пятый выход и четвертый вход которого соединены со вторым входом и выходом блока микропрограммного управления, третий и четвертый выходы которого подсоединены соответственно к адресной шине и первому входу приоритетного блока, выход которого соединен с первым входом блока микропрограммного управления, а второй вход соединен с первым объединенным выходом блоков сопряжения с каналами, вторые и третьи входы-выходы которых соединены соответственно с адресной и информационной шинами устройства, которые соединены также со вторым входом и с входом-выходом блока выбора маршрута, первый выход которого соединен с объединенным первым входом блоков сопряжения с каналами, а третий вход соединен с пятым выходом блока микропрограммного управления.

Однако данное устройство, принятое за прототип, также обладает низкой производительностью, потому что оно не позволяет одновременно коммутировать более одного сообщения. Это вызвано тем, что в устройстве имеется только один блок выбора маршрута, и поэтому нельзя достигнуть производительности устройства большей, чем производительность блока выбора маршрута. Указанный недостаток приводит к тому, что известное устройство не находит достаточно широкого применения.

Цель изобретения - повышение производительности устройства за счет обработки входного потока сообщений группой каналов обработки.

Цель достигается тем, что в устройстве для коммутации сообщений, содержащее в каждом из K (K - число дуплексных каналов связи) приемном блоке регистр приема, причем K-й информационный вход устройства соединен с информационным входом приемного регистра K-го приемного блока, и в блоке выбора маршрута постоянное запоминающее устройство, регистр и групповой элемент И, причем группа выходов постоянного запоминающего устройства соединена соответственно с группой информационных входов регистра, группа информационных выходов которого соединена соответственно с группой информационных входов группового элемента И, группа выходов которого соединена соответственно с группой выходов блока выбора маршрута, дополнительно введены генератор тактовых импульсов, первый и второй счетчики, дешифратор, блок согласования, группа из K передающих блоков, группа из M-1 блоков выбора маршрута (M - общее число блоков выбора маршрута), матрица загрузки, ответная матрица, адресная матрица, блок фильтрации, информационная матрица, матрица управления и матрица сопряжения, причем выход генератора тактовых импульсов соединен с первыми входами приемных, передающих блоков и со счетным входом первого счетчика, выход которого соединен со счетным входом второго счетчика, группа информационных выходов которого соединена соответственно с группой входов дешифратора, A-й  выход которого соединен с первым входом A-го блока выбора маршрута, второй вход которого соединен с A-м выходом первой группы выходов блока фильтрации, A-я группа входов первой группы входов которого соединена соответственно с группой выходов A-го блока выбора маршрута, группа входов которого соединена соответственно с A-й группой выходов адресной матрицы, B-я

выход которого соединен с первым входом A-го блока выбора маршрута, второй вход которого соединен с A-м выходом первой группы выходов блока фильтрации, A-я группа входов первой группы входов которого соединена соответственно с группой выходов A-го блока выбора маршрута, группа входов которого соединена соответственно с A-й группой выходов адресной матрицы, B-я  группа входов первой группы входов которой соединена соответственно с группой выходов B-го приемного блока, A-й выход первой группы выходов блока фильтрации соединен также с A-м входом первой группы входов ответной матрицы и матрицы загрузки, группа выходов которой соединена соответственно со вторыми группами входов ответной матрицы, адресной матрицы, блока фильтрации и блока согласования, группа выходов которого соединена соответственно со второй группой входов матрицы загрузки, выход которой соединен с входом блока согласования, B-й выход второй группы выходов которого соединен соответственно с четвертым входом B-го приемного блока, второй выход которого соединен с B-м входом первой группы входов блока согласования, третья группа входов которого соединена соответственно с группой выходов ответной матрицы, B-й информационный и сигнальный входы устройства соединены соответственно со вторым и третьим входами B-го приемного блока, первый выход которого соединен с B-м сигнальным выходом устройства, B-й информационный и запросный выходы которого соединены соответственно с первым и вторым выходами B-го передающего блока, второй вход которого соединен с B-м запросным входом устройства, третий выход B-го передающего блока соединен с B-м входом первой группы входов матрицы сопряжения, B-й выход которой соединен с пятым входом B-го приемного блока, третий выход которого соединен с B-м входом первой группы входов информационной матрицы, B-й выход которой соединен с третьим входом B-го передающего блока, четвертый выход которого соединен с B-м входом третьей группы входов матрицы управления, B-й выход третьей группы выходов которой соединен с четвертым входом B-го передающего блока, вторые группы входов информационной матрицы и матрицы сопряжения соединены соответственно со второй группой выходов матрицы управления, первая группа выходов которой соединена соответственно с третьей группой входов блока фильтрации, вторая и третья группы выходов которого соединены соответственно с первой и второй группой входов матрицы управления, причем блок согласования содержит группу из K элементов И, группу из K элементов ИЛИ, две из K триггеров и группу из K формирующих элементов, причем B-й вход первой группы входов соединен с первым входом B-го элемента И, выход которого соединен с единичным входом B-го триггера первой группы, нулевой динамический вход которого соединен с выходом B-го элемента ИЛИ, входов которого соединены соответственно с M входами B-й группы второй группы входов блока согласования, вход которого соединен со вторым входом B-го элемента И, третий вход которого соединен с инверсным выходом B-го триггера второй группы, прямой выход которого соединен с входом B-го формирующего элемента, выход которого соединен с B-м выходом первой и второй группы выходов блока согласования, B-й вход третьей группы входов которого соединены соответственно с M входами B-й группы второй группы входов блока согласования, вход которого соединен со вторым входом B-го элемента И, третий вход которого соединен с инверсным выходом B-го триггера второй группы, прямой выход которого соединен с входом B-го формирующего элемента, выход которого соединен с B-м выходом первой и второй группы выходов блока согласования, B-й вход третьей группы входов которого соединен с нулевым входом B-го триггера второй группы, единичный динамический вход которого соединен с прямым выходом B-го триггера первой группы, инверсный выход которого соединен с входами всех элементов И кроме B-х, причем в каждый из K приемных блоков введены два счетчика, шесть элементов И, два элемента ИЛИ, пять триггеров и элемент НЕ, причем первый вход приемного блока соединен с первым входом второго элемента И, вторыми входами четвертого и пятого элементов И и со счетным входом первого счетчика, выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым выходом приемного блока, второй вход которого соединен с информационным входом приемного регистра, группа выходов которого, соответствующая прямым выходам триггеров, содержащих адрес ЭВМ назначения, соединена соответственно с группой выходов приемного блока, третий вход которого соединен с первым входом шестого элемента И, выход которого соединен с первым выходом приемного блока, четвертый вход которого соединен с нулевым входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, пятый вход приемного блока соединен с единичным динамическим входом первого триггера и с нулевым динамическим входом третьего триггера, прямой выход которого соединен с управляющим входом приемного регистра, информационный выход которого соединен с третьим выходом приемного блока, прямой выход первого триггера приемного блока соединен со вторым входом второго элемента И и со вторым входом второго элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, выход которого соединен с тактовым входом приемного регистра, информационный выход триггера последнего разряда которого соединен с единичным динамическим входом пятого триггера, прямой выход которого соединен с первым входом четвертого элемента И выход которого соединен с суммирующим входом второго счетчика, вычитающий вход которого соединен с выходом второго элемента И, информационная группа выходов второго счетчика соединена соответственно с группой входов первого элемента ИЛИ, выход которого соединен с нулевыми динамическими входами первого и четвертого триггера, инверсный выход которого соединен с первым входом второго элемента ИЛИ, прямые выходы триггеров разрядов второго счетчика приемного блока, соответствующие числу битов в пакете информации, соединены соответственно с входами третьего элемента И, выход которого с единичными динамическими входами второго, третьего и четвертого триггеров и с нулевым динамическим входом пятого триггера, выход первого элемента ИЛИ приемного блока соединен с входом элемента НЕ, выход которого соединен со вторым входом шестого элемента И, причем каждый из K передающих блоков содержит два триггера, три элемента И, два счетчика и элемент задержки, причем первый вход передающего блока соединен со счетным входом второго счетчика и со вторым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход которого соединен с инверсным входом первого триггера и с четвертым выходом передающего блока, второй вход которого соединен с нулевым входом второго триггера, инверсный выход которого соединен с первым входом третьего элемента И, выход которого соединен с третьим выходом передающего блока, третий вход которого соединен с прямым входом первого триггера и с первым выходом передающего блока, четвертый вход которого соединен с входом элемента задержки и с единичным динамическим входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, выход которого соединен со вторым выходом передающего блока, выход второго счетчика передающего блока соединен с первым входом второго элемента И, выход элемента задержки передающего блока соединен со вторым входом третьего элемента И, прямой выход первого триггера передающего блока соединен с первым входом первого элемента И, причем группа входов блока выбора маршрута соединена соответственно с группой входов постоянного запоминающего устройства блока выбора маршрута, первый и второй входы которого соединены соответственно с управляющим входом группового элемента И, и с входом установки в "O" регистра, причем матрица загрузки содержит группу из M элементов ИЛИ/НЕ, группу из M элементов задержки, группу из M элементов задержки, матрицу K•M триггеров, матрицу K•M элементов И, элемент ИЛИ и группу из K-1 элементов И-НЕ, причем A-й вход первой группы входов матрицы загрузки соединен с входом A-го элемента задержки, выход которого соединен с нулевыми входами триггеров A-й строки матрицы загрузки, B-й вход второй группы входов которой соединен с первыми входами элементов И B-го столбца матрицы загрузки, инверсный выход A, B-го триггера матрицы загрузки соединен со вторым входом A, B-го элемента И, выход которого соединен с единичным входом A, B-го триггера, прямой выход которого соединен с A, B-м выходом матрицы загрузки и с B-м входом A-го элемента ИЛИ-НЕ, выход которого соединен с A-м входом элемента ИЛИ, выход которого соединен выходом матрицы загрузки, выход первого элемента ИЛИ-НЕ матрицы загрузки соединен с третьими входами элементов И первой строки, первым и вторым входом элемента И-НЕ и со вторым входом второго элемента И-НЕ, выходы третьего и второго элементов ИЛИ-НЕ матрицы загрузки соединены соответственно с третьими входами третьей и второй строк элементов и матрицы загрузки, выход второго элемента ИЛИ-НЕ матрицы загрузки соединен с первым входом второго элемента И-НЕ, выход A-го элемента И-НЕ матрицы загрузки соединен с четвертыми входами A+1-й строки элементов И матрицы загрузки, причем ответная матрицы содержит матрицу M•K элементов И и группу из K элементов ИЛИ, причем A, B-й вход второй группы входов ответной матрицы соединен со вторым входом A, B-й вход второй группы входов ответной матрицы соединен со вторым входом A, B-го элемента И выход которого соединен с A-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом ответной матрицы, A-й вход первой группы которой соединен с первыми входами элементов И A-го столбца ответной матрицы, причем адресная матрица содержит матрицу M•K групповых элементов И и группу из M групповых элементов ИЛИ, причем A, B-й вход второй группы входов адресной матрицы соединен с управляющим входом A, B-го группового элемента И, группа выходов которого соединена соответственно с B-й группой входов A-го группового элемента ИЛИ, группа выходов которого соединена соответственно с A-й группой выходов адресной матрицы, B-я группа входов первой группы входов которой соединена соответственно с группой информационных входов B-го столбца групповых элементов И адресной матрицы, причем групповой элемент ИЛИ содержит S (S - число связей в каждой из R коммутируемых групп) элементов ИЛИ, причем S-й вход группового элемента ИЛИ R-й группы соединен с R-м входом S-го элемента ИЛИ, выход которого соединен с S-м выходом группового элемента ИЛИ, причем блок фильтрации содержит группу из M групповых элементов И, первую группу из M элементов ИЛИ, матрицу из M•K элементов И, вторую и третью группу из K элементов ИЛИ, причем B-й вход A-й группы второй группы входов блока фильтрации соединен с B-м входом A-го группового элемента И, B-й выход которого соединен с A-м входом B-го элемента ИЛИ второй группы, выход которого соединен с B-м выходом второй группы выходов блока фильтрации, B-й вход третьей группы входов которого соединен с вторым входами B-й строки матрицы элементов И блока фильтрации, выход A, B-го элемента И блока фильтрации соединен с A-м входом B-го элемента ИЛИ третьей группы, выход которого соединен с B-м выходом третьей группы выходов блока фильтрации, A, B-й вход первой группы входов которого соединен с первым входом A, B-го элемента И, выход которого соединен с B-м входом A-го элемента ИЛИ выход которого соединен с управляющим входом A-го группового элемента И и с A-м выходом первой группы выходом блока фильтрации, причем информационная матрица содержит матрицу K•K элементов И и группу из K элементов ИЛИ, причем B, B-й вход второй группы входов информационной матрицы соединен со вторым входом B, B-го элемента И, выход которого соединен с B-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом информационной матрицы, B-й вход первой группы которой соединен с первыми входами элементов И B-го столбца информационной матрицы, причем матрица сопряжения содержит матрицу K•K элементов И и группу из K элементов ИЛИ, причем B, B-й вход второй группы входов матрицы сопряжения соединен со вторым входом B, B-го элемента И, выход которого соединен с B-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом матрицы сопряжения, B-й вход первой группы которой соединен с первыми входами элементов И B-го столбца матрицы сопряжения, причем матрица управления содержит матрицу K•K триггеров, матрицу K•K элементов И, группу из K элементов ИЛИ, группу из K элементов НЕ, причем B-1 вход первой группы входов матрицы управления соединен с первыми входами элементов И B-го столбца матрицы управления, B-й вход второй группы которой соединен со вторыми входами элементов И B-й строки матрицы управления, выход B, B-го элемента И матрицы управления соединен с единичным входом B, B-го триггера инверсный выход которого соединен с третьим входом B, B-го элемента И, прямой выход B, B-го триггера матрицы управления соединен с B, B-м выходом второй группы выходов матрицы управления и с B-входом B-го элемента ИЛИ, выход которого соединен с B-м выходом третьей группы матрицы управления и с выходом B-го элемента НЕ, выход которого соединен с B-м выходом первой группы выходов матрицы управления, B-й вход третьей группы входов которой соединен с нулевыми входами триггеров B-й строки матрицы управления.

группа входов первой группы входов которой соединена соответственно с группой выходов B-го приемного блока, A-й выход первой группы выходов блока фильтрации соединен также с A-м входом первой группы входов ответной матрицы и матрицы загрузки, группа выходов которой соединена соответственно со вторыми группами входов ответной матрицы, адресной матрицы, блока фильтрации и блока согласования, группа выходов которого соединена соответственно со второй группой входов матрицы загрузки, выход которой соединен с входом блока согласования, B-й выход второй группы выходов которого соединен соответственно с четвертым входом B-го приемного блока, второй выход которого соединен с B-м входом первой группы входов блока согласования, третья группа входов которого соединена соответственно с группой выходов ответной матрицы, B-й информационный и сигнальный входы устройства соединены соответственно со вторым и третьим входами B-го приемного блока, первый выход которого соединен с B-м сигнальным выходом устройства, B-й информационный и запросный выходы которого соединены соответственно с первым и вторым выходами B-го передающего блока, второй вход которого соединен с B-м запросным входом устройства, третий выход B-го передающего блока соединен с B-м входом первой группы входов матрицы сопряжения, B-й выход которой соединен с пятым входом B-го приемного блока, третий выход которого соединен с B-м входом первой группы входов информационной матрицы, B-й выход которой соединен с третьим входом B-го передающего блока, четвертый выход которого соединен с B-м входом третьей группы входов матрицы управления, B-й выход третьей группы выходов которой соединен с четвертым входом B-го передающего блока, вторые группы входов информационной матрицы и матрицы сопряжения соединены соответственно со второй группой выходов матрицы управления, первая группа выходов которой соединена соответственно с третьей группой входов блока фильтрации, вторая и третья группы выходов которого соединены соответственно с первой и второй группой входов матрицы управления, причем блок согласования содержит группу из K элементов И, группу из K элементов ИЛИ, две из K триггеров и группу из K формирующих элементов, причем B-й вход первой группы входов соединен с первым входом B-го элемента И, выход которого соединен с единичным входом B-го триггера первой группы, нулевой динамический вход которого соединен с выходом B-го элемента ИЛИ, входов которого соединены соответственно с M входами B-й группы второй группы входов блока согласования, вход которого соединен со вторым входом B-го элемента И, третий вход которого соединен с инверсным выходом B-го триггера второй группы, прямой выход которого соединен с входом B-го формирующего элемента, выход которого соединен с B-м выходом первой и второй группы выходов блока согласования, B-й вход третьей группы входов которого соединены соответственно с M входами B-й группы второй группы входов блока согласования, вход которого соединен со вторым входом B-го элемента И, третий вход которого соединен с инверсным выходом B-го триггера второй группы, прямой выход которого соединен с входом B-го формирующего элемента, выход которого соединен с B-м выходом первой и второй группы выходов блока согласования, B-й вход третьей группы входов которого соединен с нулевым входом B-го триггера второй группы, единичный динамический вход которого соединен с прямым выходом B-го триггера первой группы, инверсный выход которого соединен с входами всех элементов И кроме B-х, причем в каждый из K приемных блоков введены два счетчика, шесть элементов И, два элемента ИЛИ, пять триггеров и элемент НЕ, причем первый вход приемного блока соединен с первым входом второго элемента И, вторыми входами четвертого и пятого элементов И и со счетным входом первого счетчика, выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым выходом приемного блока, второй вход которого соединен с информационным входом приемного регистра, группа выходов которого, соответствующая прямым выходам триггеров, содержащих адрес ЭВМ назначения, соединена соответственно с группой выходов приемного блока, третий вход которого соединен с первым входом шестого элемента И, выход которого соединен с первым выходом приемного блока, четвертый вход которого соединен с нулевым входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, пятый вход приемного блока соединен с единичным динамическим входом первого триггера и с нулевым динамическим входом третьего триггера, прямой выход которого соединен с управляющим входом приемного регистра, информационный выход которого соединен с третьим выходом приемного блока, прямой выход первого триггера приемного блока соединен со вторым входом второго элемента И и со вторым входом второго элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, выход которого соединен с тактовым входом приемного регистра, информационный выход триггера последнего разряда которого соединен с единичным динамическим входом пятого триггера, прямой выход которого соединен с первым входом четвертого элемента И выход которого соединен с суммирующим входом второго счетчика, вычитающий вход которого соединен с выходом второго элемента И, информационная группа выходов второго счетчика соединена соответственно с группой входов первого элемента ИЛИ, выход которого соединен с нулевыми динамическими входами первого и четвертого триггера, инверсный выход которого соединен с первым входом второго элемента ИЛИ, прямые выходы триггеров разрядов второго счетчика приемного блока, соответствующие числу битов в пакете информации, соединены соответственно с входами третьего элемента И, выход которого с единичными динамическими входами второго, третьего и четвертого триггеров и с нулевым динамическим входом пятого триггера, выход первого элемента ИЛИ приемного блока соединен с входом элемента НЕ, выход которого соединен со вторым входом шестого элемента И, причем каждый из K передающих блоков содержит два триггера, три элемента И, два счетчика и элемент задержки, причем первый вход передающего блока соединен со счетным входом второго счетчика и со вторым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход которого соединен с инверсным входом первого триггера и с четвертым выходом передающего блока, второй вход которого соединен с нулевым входом второго триггера, инверсный выход которого соединен с первым входом третьего элемента И, выход которого соединен с третьим выходом передающего блока, третий вход которого соединен с прямым входом первого триггера и с первым выходом передающего блока, четвертый вход которого соединен с входом элемента задержки и с единичным динамическим входом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, выход которого соединен со вторым выходом передающего блока, выход второго счетчика передающего блока соединен с первым входом второго элемента И, выход элемента задержки передающего блока соединен со вторым входом третьего элемента И, прямой выход первого триггера передающего блока соединен с первым входом первого элемента И, причем группа входов блока выбора маршрута соединена соответственно с группой входов постоянного запоминающего устройства блока выбора маршрута, первый и второй входы которого соединены соответственно с управляющим входом группового элемента И, и с входом установки в "O" регистра, причем матрица загрузки содержит группу из M элементов ИЛИ/НЕ, группу из M элементов задержки, группу из M элементов задержки, матрицу K•M триггеров, матрицу K•M элементов И, элемент ИЛИ и группу из K-1 элементов И-НЕ, причем A-й вход первой группы входов матрицы загрузки соединен с входом A-го элемента задержки, выход которого соединен с нулевыми входами триггеров A-й строки матрицы загрузки, B-й вход второй группы входов которой соединен с первыми входами элементов И B-го столбца матрицы загрузки, инверсный выход A, B-го триггера матрицы загрузки соединен со вторым входом A, B-го элемента И, выход которого соединен с единичным входом A, B-го триггера, прямой выход которого соединен с A, B-м выходом матрицы загрузки и с B-м входом A-го элемента ИЛИ-НЕ, выход которого соединен с A-м входом элемента ИЛИ, выход которого соединен выходом матрицы загрузки, выход первого элемента ИЛИ-НЕ матрицы загрузки соединен с третьими входами элементов И первой строки, первым и вторым входом элемента И-НЕ и со вторым входом второго элемента И-НЕ, выходы третьего и второго элементов ИЛИ-НЕ матрицы загрузки соединены соответственно с третьими входами третьей и второй строк элементов и матрицы загрузки, выход второго элемента ИЛИ-НЕ матрицы загрузки соединен с первым входом второго элемента И-НЕ, выход A-го элемента И-НЕ матрицы загрузки соединен с четвертыми входами A+1-й строки элементов И матрицы загрузки, причем ответная матрицы содержит матрицу M•K элементов И и группу из K элементов ИЛИ, причем A, B-й вход второй группы входов ответной матрицы соединен со вторым входом A, B-й вход второй группы входов ответной матрицы соединен со вторым входом A, B-го элемента И выход которого соединен с A-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом ответной матрицы, A-й вход первой группы которой соединен с первыми входами элементов И A-го столбца ответной матрицы, причем адресная матрица содержит матрицу M•K групповых элементов И и группу из M групповых элементов ИЛИ, причем A, B-й вход второй группы входов адресной матрицы соединен с управляющим входом A, B-го группового элемента И, группа выходов которого соединена соответственно с B-й группой входов A-го группового элемента ИЛИ, группа выходов которого соединена соответственно с A-й группой выходов адресной матрицы, B-я группа входов первой группы входов которой соединена соответственно с группой информационных входов B-го столбца групповых элементов И адресной матрицы, причем групповой элемент ИЛИ содержит S (S - число связей в каждой из R коммутируемых групп) элементов ИЛИ, причем S-й вход группового элемента ИЛИ R-й группы соединен с R-м входом S-го элемента ИЛИ, выход которого соединен с S-м выходом группового элемента ИЛИ, причем блок фильтрации содержит группу из M групповых элементов И, первую группу из M элементов ИЛИ, матрицу из M•K элементов И, вторую и третью группу из K элементов ИЛИ, причем B-й вход A-й группы второй группы входов блока фильтрации соединен с B-м входом A-го группового элемента И, B-й выход которого соединен с A-м входом B-го элемента ИЛИ второй группы, выход которого соединен с B-м выходом второй группы выходов блока фильтрации, B-й вход третьей группы входов которого соединен с вторым входами B-й строки матрицы элементов И блока фильтрации, выход A, B-го элемента И блока фильтрации соединен с A-м входом B-го элемента ИЛИ третьей группы, выход которого соединен с B-м выходом третьей группы выходов блока фильтрации, A, B-й вход первой группы входов которого соединен с первым входом A, B-го элемента И, выход которого соединен с B-м входом A-го элемента ИЛИ выход которого соединен с управляющим входом A-го группового элемента И и с A-м выходом первой группы выходом блока фильтрации, причем информационная матрица содержит матрицу K•K элементов И и группу из K элементов ИЛИ, причем B, B-й вход второй группы входов информационной матрицы соединен со вторым входом B, B-го элемента И, выход которого соединен с B-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом информационной матрицы, B-й вход первой группы которой соединен с первыми входами элементов И B-го столбца информационной матрицы, причем матрица сопряжения содержит матрицу K•K элементов И и группу из K элементов ИЛИ, причем B, B-й вход второй группы входов матрицы сопряжения соединен со вторым входом B, B-го элемента И, выход которого соединен с B-м входом B-го элемента ИЛИ, выход которого соединен с B-м выходом матрицы сопряжения, B-й вход первой группы которой соединен с первыми входами элементов И B-го столбца матрицы сопряжения, причем матрица управления содержит матрицу K•K триггеров, матрицу K•K элементов И, группу из K элементов ИЛИ, группу из K элементов НЕ, причем B-1 вход первой группы входов матрицы управления соединен с первыми входами элементов И B-го столбца матрицы управления, B-й вход второй группы которой соединен со вторыми входами элементов И B-й строки матрицы управления, выход B, B-го элемента И матрицы управления соединен с единичным входом B, B-го триггера инверсный выход которого соединен с третьим входом B, B-го элемента И, прямой выход B, B-го триггера матрицы управления соединен с B, B-м выходом второй группы выходов матрицы управления и с B-входом B-го элемента ИЛИ, выход которого соединен с B-м выходом третьей группы матрицы управления и с выходом B-го элемента НЕ, выход которого соединен с B-м выходом первой группы выходов матрицы управления, B-й вход третьей группы входов которой соединен с нулевыми входами триггеров B-й строки матрицы управления.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием новых элементов: генератора тактовых импульсов, двух счетчиков, дешифратора, блока согласования, группы передающих блоков, группы блоков выбора маршрута, матрицы загрузки, ответной матрицы, адресной матрицы, блока фильтрации, информационной матрицы, матрицы управления и матрицы сопряжения, и соответствующими связями с другими элементами схемы, что соответствует критерию новизны технического решения.

В научно-технической литературе не найдено устройство с описанной совокупностью новых признаков. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

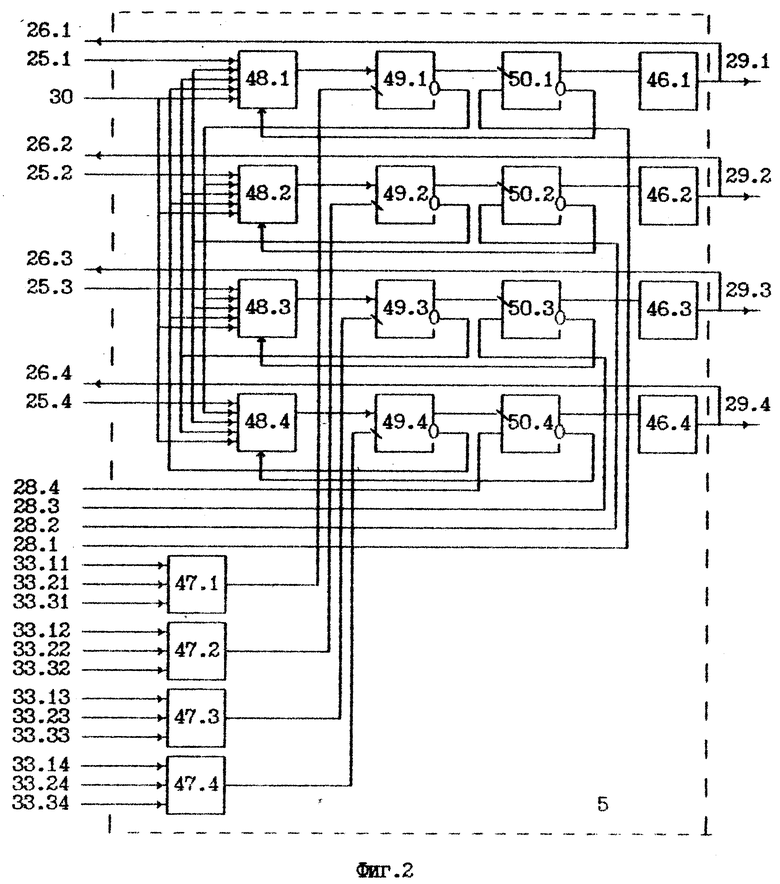

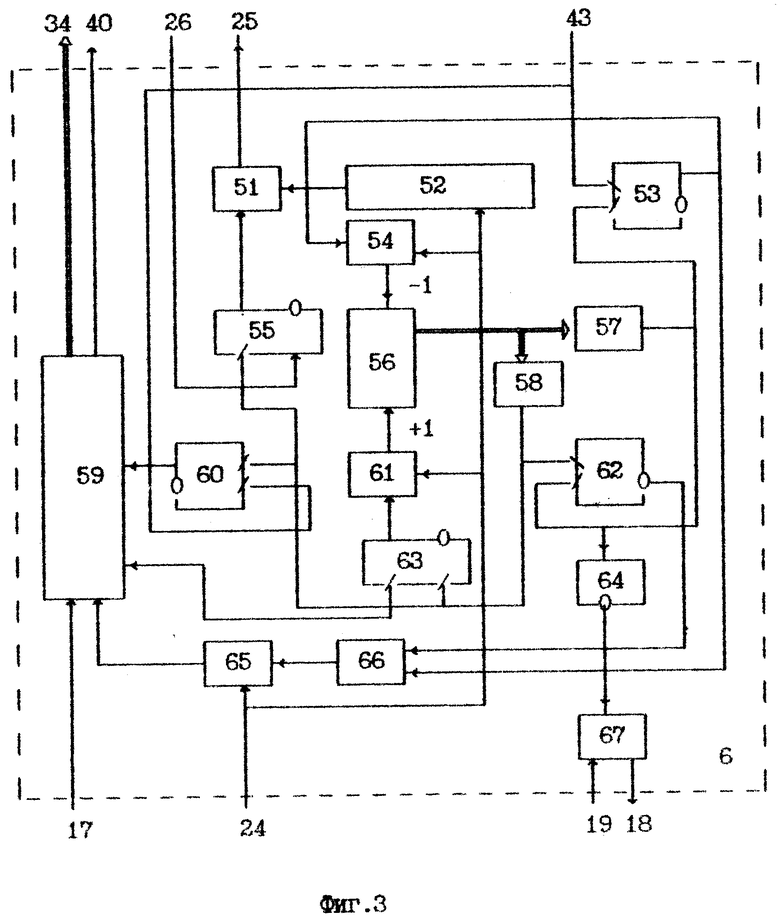

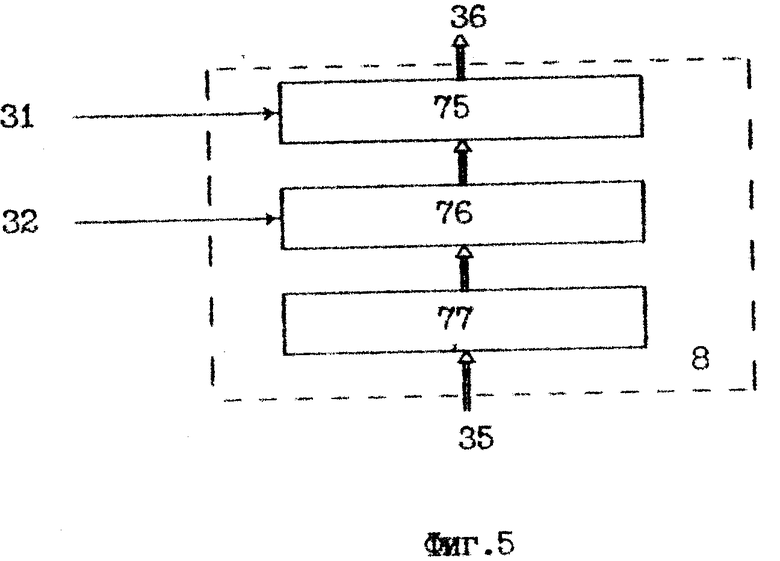

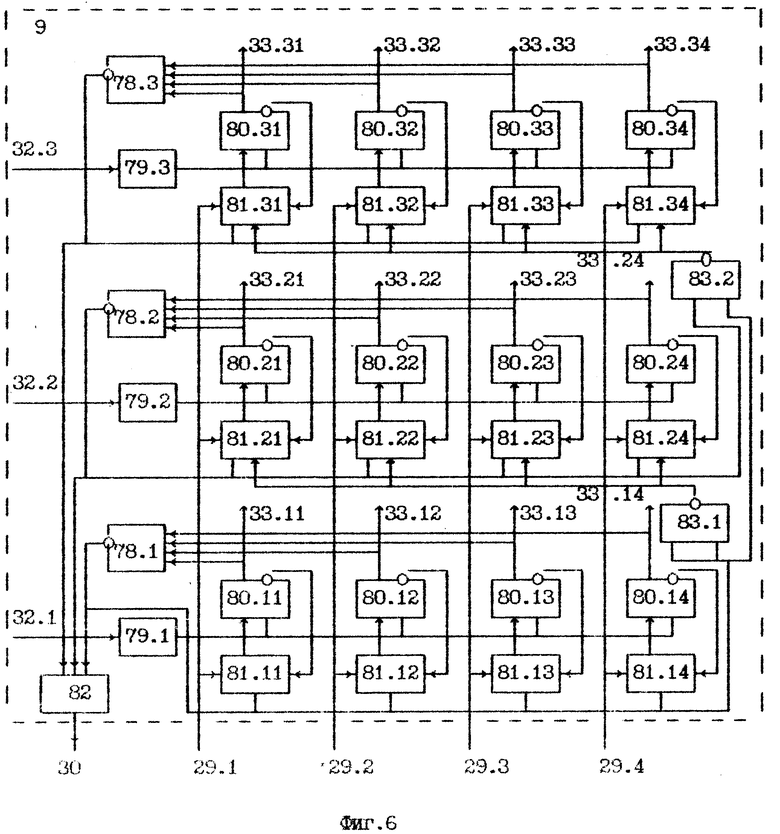

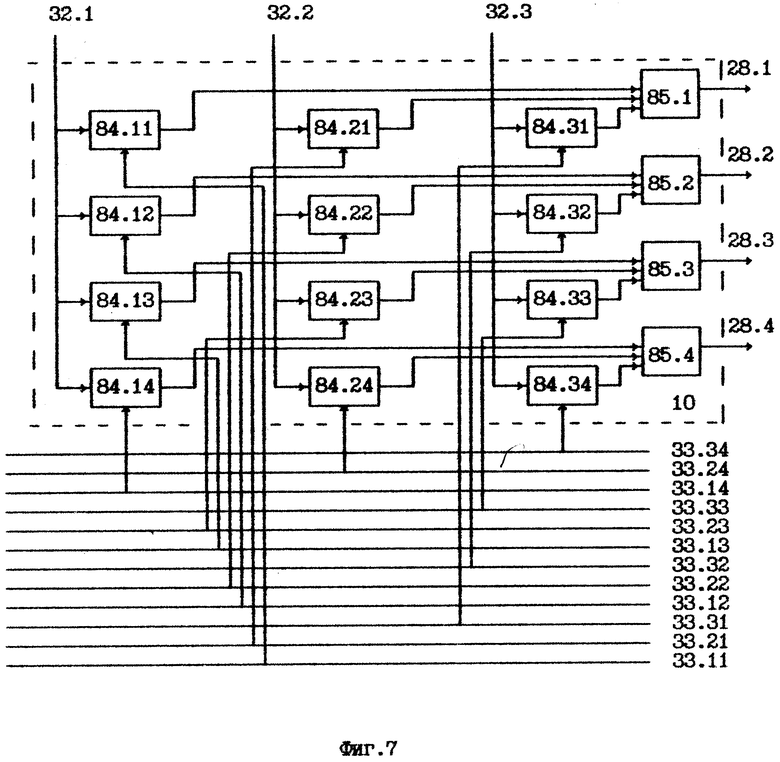

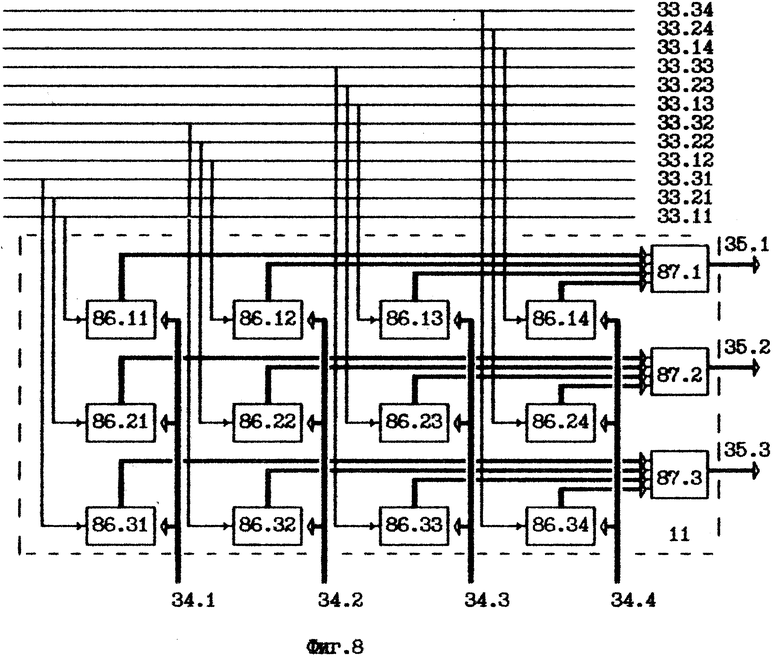

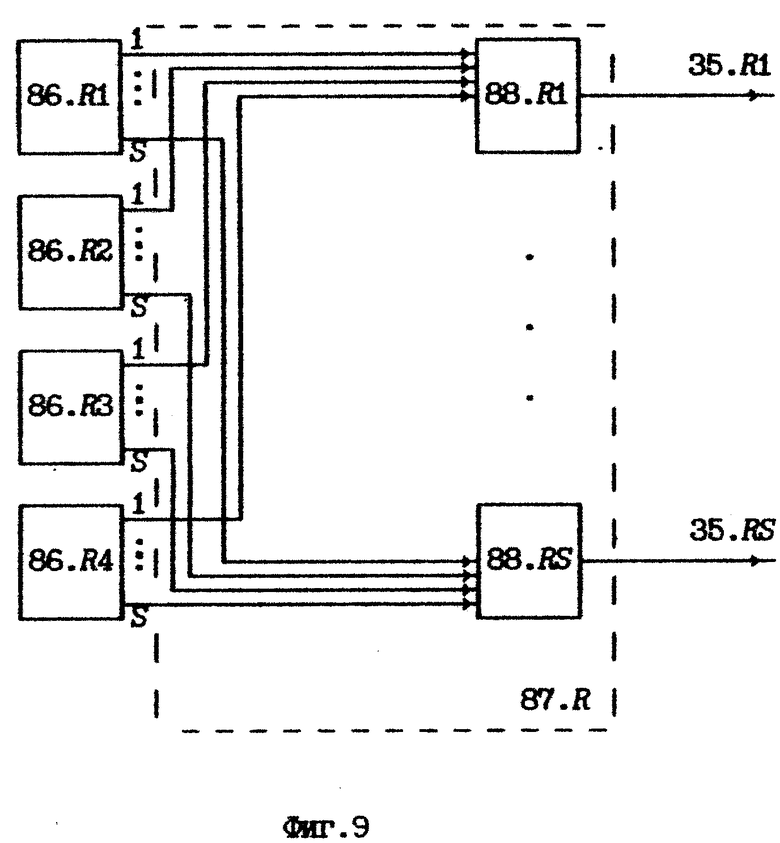

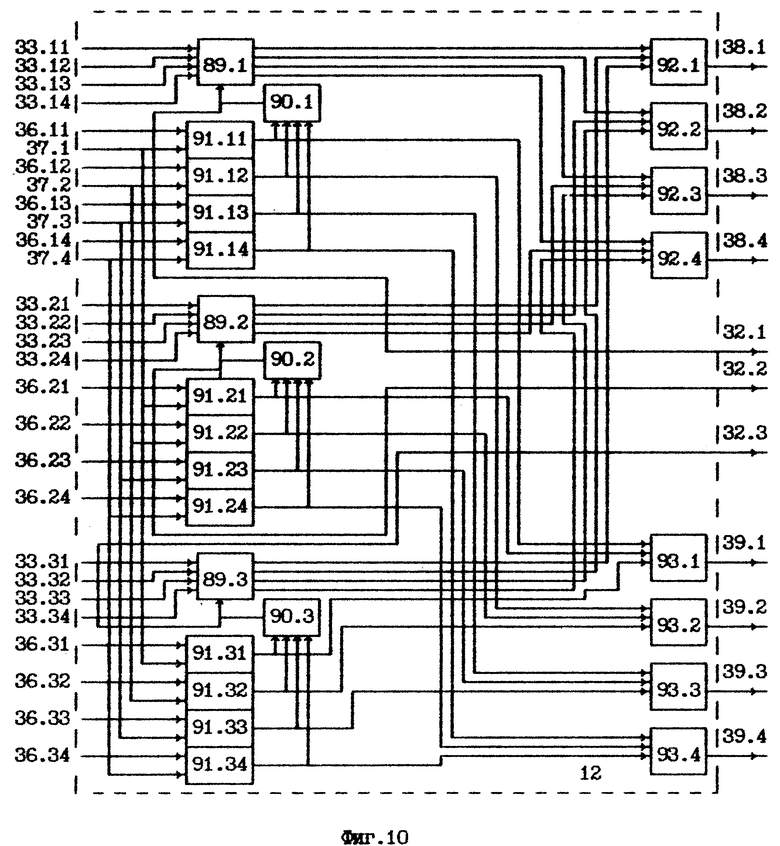

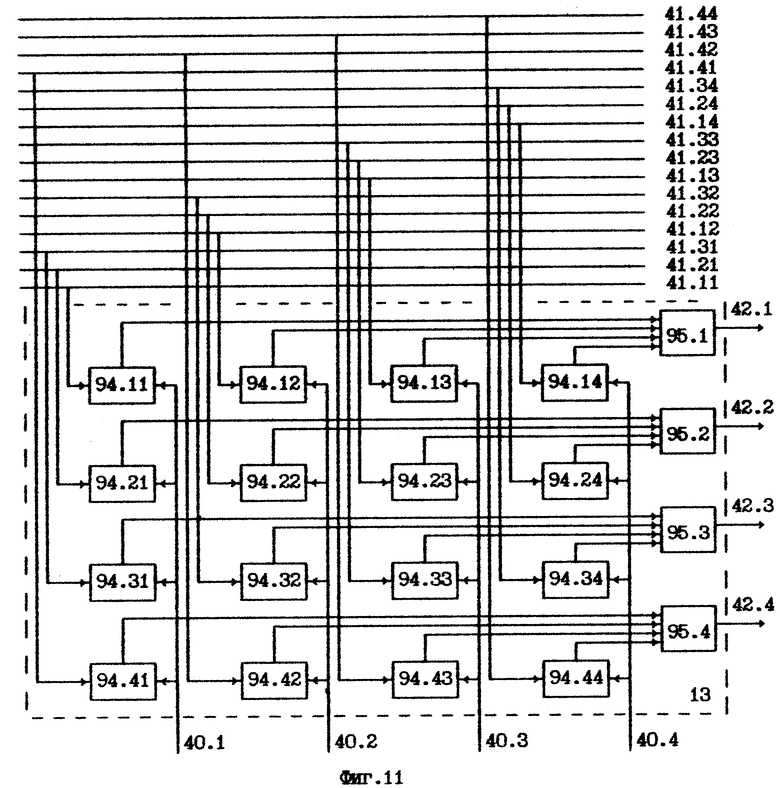

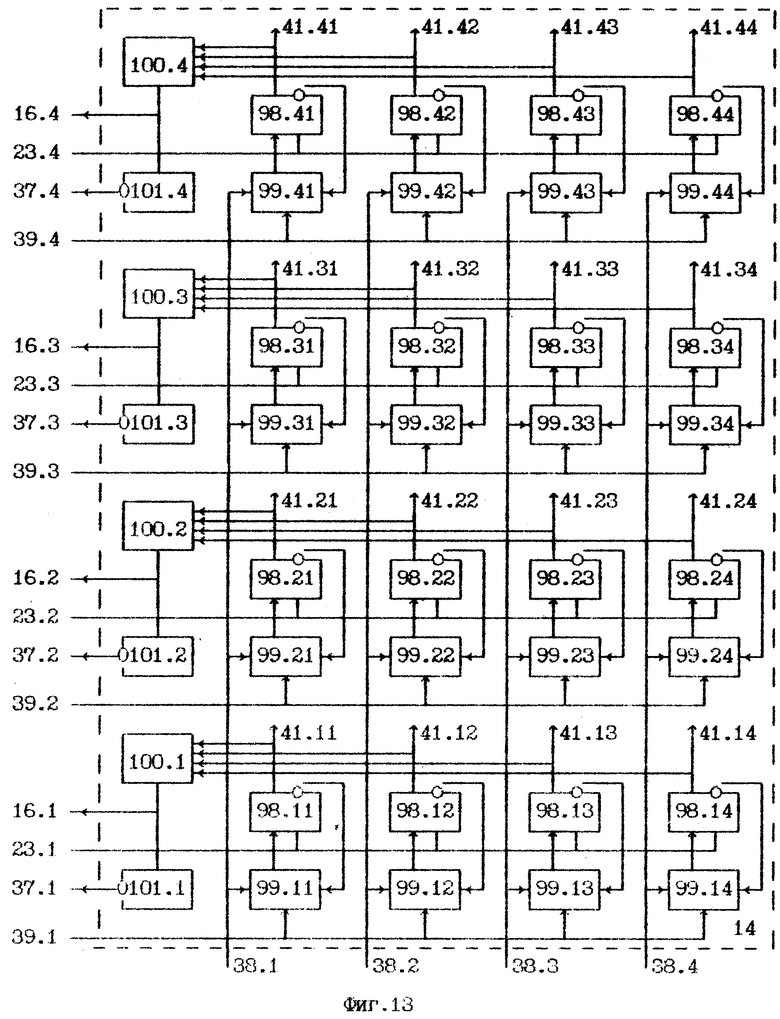

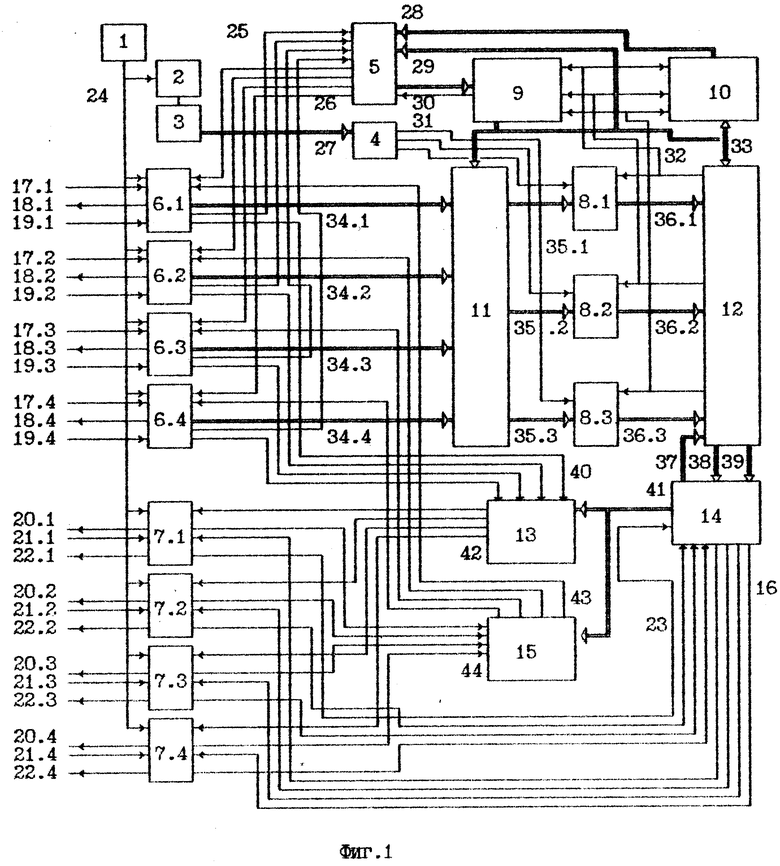

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока согласования; на фиг. 3 - структурная схема приемного блока; на фиг. 4 - структурная схема передающего блока; на фиг. 5 - структурная схема блока выбора маршрута; на фиг. 6 - структурная схема матрицы загрузки; на фиг. 7 - структурная схема ответной матрицы; на фиг. 8 - структурная схема адресной матрицы; на фиг. 9 - структурная схема группового элемента ИЛИ; на фиг. 10 - структурная схема блока фильтрации; на фиг. 11 - структурная схема информационной матрицы; на фиг. 12 - cтруктурная схема матрицы сопряжения; на фиг. 13 - структурная схема матрицы управления.

Устройство для коммутации сообщений (фиг. 1) содержит генератор 1 тактовых импульсов, первый счетчик 2, второй счетчик 3, дешифратор 4, блок 5 согласования, группу приемных блоков 6.1 - 6.4, группу передающих блоков 7.1 - 7.4, группу блоков выбора маршрута 8.1 - 8.3, матрицу загрузки 9, ответную матрицу 10, адресную матрицу 11, блок фильтрации 12, информационную матрицу 13, матрицу управления 14, матрицу сопряжения 15, группу информационных входов 17.1 - 17.4, группу сигнальных выходов 18.1 - 18.2, группу сигнальных входов 19.1 - 19.4, группу информационных выходов 20.1 - 20.4, группу запросных входов 21.1 - 21.4, группу запросных выходов 22.1 - 22.2, внутренние связи 16, 23-44.

Блок 5 согласования (фиг. 2) содержит группу формирующих элементов 46.1 - 46.4, группу элементов ИЛИ 47.1 - 47.2, группу элементов И 48.1 - 48.4, первую группу триггеров 49.1 - 49.4, вторую группу триггеров 50.1 - 50.4.

Приемный блок 6 (фиг. 3) содержит первый элемент И 51, первый счетчик 52, первый триггер 53, второй элемент И 54, второй триггер 55, второй счетчик 56, первый элемент ИЛИ 57, третий элемент И 58, приемный регистр 59, третий триггер 60, четвертый элемент И 61, четвертый триггер 62, пятый триггер 63, элемент НЕ 64, пятый элемент И 65, второй элемент ИЛИ 66, шестой элемент И 67.

Передающий блок 7 (фиг. 4) содержит элемент задержки 45, первый триггер 68, первый элемент И 69, первый счетчик 70, второй счетчик 71, второй элемент И 72, второй триггер 73, третий элемент И 74.

Блок выбора маршрута 8 (фиг. 5) содержит групповой элемент И 75, регистр 76, постоянное запоминающее устройство (ПЗУ) 77.

Матрица загрузки 9 (фиг. 6) содержит группу элементов ИЛИ-НЕ 78.1 - 78.3, группу элементов задержки 79.1 - 79.3, матрицу триггеров 80.11 - 80.34, матрицу элементов И 81.11 - 81.34, элемент ИЛИ 82, группу элементов И-НЕ 83.1 - 83.2.

Ответная матрица 10 (фиг. 7) содержит матрицу элементов И 84.11 - 84.34, группу элементов ИЛИ 85.1 - 85.4.

Адресная матрица 11 (фиг. 8) содержит матрицу групповых элементов И 86.11 - 86.34, группу групповых элементов ИЛИ 87.1 - 87.3.

Групповой элемент ИЛИ 87 (фиг. 9) содержит группу элементов ИЛИ 88.1 - 88.S.

Блок фильтрации 12 (фиг. 10) содержит группу групповых элементов И 89.1 - 89.3, первую группу элементов ИЛИ 90.1 - 90.3, матрицу элементов И 91.11 - 91.34, вторую группу элементов ИЛИ 92.1 - 92.4, третью группу элементов ИЛИ 93.1 - 93.4.

Информационная матрица 13 (фиг. 11) содержит матрицу элементов И 94.11 - 94.44, группу элементов ИЛИ 95.1 - 95.4.

Матрица сопряжения 15 (фиг. 12) содержит матрицу элементов И 96.11 - 96.44, группу элементов ИЛИ 97.1 - 97.4.

Матрица управления 14 (фиг. 13) содержит матрицу триггеров 98.11 - 98.44, матрицу элементов И 99.11 - 99.44, группу элементов ИЛИ 100.1 - 100.4, группу элементов НЕ 101.1 - 101.4.

В устройстве для коммутации сообщений K-й информационный вход 17 устройства соединен с информационный входом приемного регистра 59 K-го приемного блока 6, в блоке выбора маршрута 8 группа выходов постоянного запоминающего устройства 77 соединена соответственно с группой информационных входов регистра 76, группа информационных выходов которого соединена соответственно с группой информационных входов группового элемента И 75, группа выходов которого соединена соответственно с группой выходов блока выбора маршрута 8, причем выход 24 генератора 1 тактовых импульсов соединен с первыми входами приемных 6, передающих 7 блоков и со счетным входом первого счетчика 2, выход которого соединен со счетным входом второго счетчика 3, группа информационных выходов которого соединена соответственно с группой входов дешифратора 4, A-й  выход 31 которого соединен с первым входом A-го блока выбора маршрута 8, второй вход которого соединен с A-м выходом первой группы выходов 32 блока фильтрации 12, A-я группа входов первой группы входов 36 которого соединена соответственно с группой выходов A-го блока выбора маршрута 8, группа входов которого соединена соответственно с A-й группой адресной матрицы 11, B-я

выход 31 которого соединен с первым входом A-го блока выбора маршрута 8, второй вход которого соединен с A-м выходом первой группы выходов 32 блока фильтрации 12, A-я группа входов первой группы входов 36 которого соединена соответственно с группой выходов A-го блока выбора маршрута 8, группа входов которого соединена соответственно с A-й группой адресной матрицы 11, B-я  группа входов первой группы входов 34 которой соединена соответственно с группой выходов B-го приемного блока 6, A-й выход первой группы выходов 32 блока фильтрации 12 соединен также с A-м входом первой группы входов ответной матрицы 10 и матрицы загрузки 9, группа выходов 33 которой соединена соответственно с вторыми группами входов ответной матрицы 10, адресной матрицы 11, блока фильтрации 12 и блока согласования 5, группа выходов 29 которого соединена соответственно со второй группой входов матрицы загрузки 9, выход 30 которой соединен с входом блока согласования 5, B-й выход второй группы выходов 26 которого соединен соответственно с четвертым входом B-го приемного блока 6, второй выход 25 которого соединен с B-м входом первой группы входом блока согласования 5, третья группа входов которого соединена соответственно с группой входов 28 ответной матрицы 10, B-й информационный 17 и сигнальный 19 входы устройства соединены соответственно со вторым и третьим входами B-го приемного блока 6, первый выход которого соединен с B-м сигнальным выходом 18 устройства, B-й информационный 20 и запросный 22 выходы которого соединены соответственно с первым и вторым выходами B-го передающего блока 7, второй вход которого соединен с B-м запросным входом 21 устройства, третий выход 44 B-го передающего блока 7 соединен с B-м входом первой группы входов матрицы сопряжения 15, B-й выход 43 которой соединен с пятым входом B-го приемного блока 6, третий выход 40 которого соединен с B-м входом первой группы входов информационной матрицы 13, B-й выход 42 которой соединен с третьим входом B-го передающего блока 7, четвертый выход 23 которого соединен с B-м входом третьей группы входов матрицы управления 14, B-й выход третьей группы выходов 16 которой соединен с четвертым входом B-го передающего блока 7, вторые группы входов информационной матрицы 13 и матрицы сопряжения 15 соединены соответственно со второй группой выходов 41 матрицы управления 14, первая группа выходов 37 которой соединена соответственно с третьей группой входов блока фильтрации 12, вторая 38 и третья 39 группы выходов которого соединены соответственно с первой и второй группой входов матрицы управления 14, в каждом блоке согласования 5 B-й вход 25 первой группы входов соединен с первым входом B-го элемента И 48 выход которого соединен с единичным входом B-го триггера 49 первой группы, нулевой динамический вход которого соединен с выходом B-го элемента ИЛИ 47, M входов которого соединены соответственно с M входами B-й группы второй группы входов 33 блока согласования 5, вход 30 которого соединен о вторым входом B-го элемента И 48, третий вход которого соединен с инверсным выходом B-го триггера 50 второй группы, прямой выход которого соединен с входом B-го формирующего элемента 46, выход которого соединен с B-м выходом первой 29 и второй 26 группы выходов блока согласования 5, B-й вход третьей группы входов 28 которого соединен с нулевым входом B-го триггера 50 второй группы, единичный динамический вход которого соединен с прямым выходом B-го триггера 49 первой группы, инверсный выход которого соединен с входами всех элементов И 48 кроме B-х, первый вход каждого приемного блока 6 соединен с первым входом второго элемента И 54, вторыми входами четвертого 61 и пятого 65 элементов И и со счетным входом первого счетчика 52, выход которого соединен с первым входом первого элемента И 51, выход которого соединен со вторым выходом 25 приемного блока 6, второй вход 17 которого соединен с информационным входом приемного регистра 59, группа выходов которого, соответствующая прямым выходам триггера, содержащих адрес ЭВМ назначения, соединена соответственно с группой выходов 34 блока 6, третий вход 19 которого соединен с первым входом шестого элемента И 67, выход которого соединен с первым выходом 18 приемного блока 6, четвертый вход 26 которого соединен с нулевым входом второго триггера 55, прямой выход которого соединен со вторым входом первого элемента И 51, пятый вход 43 приемного блока 6 соединен с единичным динамическим входом первого триггера 53 и с нулевым динамическим входом третьего триггера 60, прямой выход которого соединен с управляющим входом приемного регистра 59, информационный выход которого соединен с третьим выходом 40 приемного блока 6, прямой выход первого триггера 53 приемного блока 6 соединен со вторым входом второго элемента И 54 и со вторым входом второго элемента ИЛИ 66, выход которого соединен с первым входом пятого элемента И 65, выход которого соединен с тактовым входом приемного регистра 59, информационный выход триггера последнего разряда которого соединен с единичным динамическим входом пятого триггера 63, прямой выход которого соединен с первым входом четвертого элемента И 61 выход которого соединен с суммирующим входом второго счетчика, 56 вычитающий вход которого соединен с выходом второго элемента И 54, информационная группа выходов второго счетчика 56 соединена соответственно с группой входов первого элемента ИЛИ 57, выход которого соединен с нулевыми динамическими входами первого 53 и четвертого 62 триггера, инверсный выход которого соединен с первым входом второго элемента ИЛИ 66, прямые выходы триггеров разрядов второго счетчика 56 приемного блока 6, соответствующие числу битов в пакете информации, соединены соответственно с входами третьего элемента И 58, выход которого соединен с единичными динамическими входами второго 55, третьего 60 и четвертого 62 триггеров и с нулевым динамическим входом пятого триггера 63, выход первого элемента ИЛИ 57 приемного блока 6 соединен с входом элемента НЕ 64, выход которого соединен с вторым входом шестого элемента И 67, первый вход 42 каждого передающего блока 7 соединен со счетным входом второго счетчика 71 и со вторым входом первого элемента И 69, выход которого соединен со счетным входом первого счетчика 70 выход которого соединен с инверсным входом первого триггера 68 и с четвертым выходом 23 передающего блока 7, второй вход 21 которого соединен с нулевым входом второго триггера 73, инверсный выход которого соединен с первым входом третьего элемента И 74, выход которого соединен с третьим выходом 44 передающего блока 7, третий вход 42 которого соединен с прямым входом первого триггера 68 и с первым выходом 20 передающего блока 7, четвертый вход 16 которого соединен с входом элемента задержки 45 и с единичным динамическим входом второго триггера 73, прямой выход которого соединен со вторым входом второго элемента И 72, выход которого соединен со вторым выходом 22 передающего блока 7, выход второго счетчика 71 передающего блока 7 соединен с первым входом второго элемента И 72, выход элемента задержки 45 передающего блока 7 соединен со вторым входом третьего элемента И 74, прямой выход первого триггера 68 передающего блока 7 соединен с первым входом первого элемента И 69, группа входов 35 блока выбора маршрута 8 соединена соответственно с группой входов постоянного запоминающего устройства 77 блока выбора маршрута 8, первый 31 и второй 32 входы которого соединены соответственно с управляющим входом группового элемента И 75 и с входом установки в "O" регистра 76, A-й вход первой группы входов 32 матрицы загрузки 9 соединен с входом A-го элемента задержки 79, выход которого соединен с нулевыми входами триггеров 80 A-й строки матрицы загрузки 9, B-й вход второй группы входов 29 которой соединен с первыми входами элементов И 81 B-го столбца матрицы загрузки 9, инверсный выход A, B-го триггера 80 матрицы загрузки 9 соединен с вторым входом A, B-го элемента И 81, выход которого соединен с единичным входом A, B-го триггера 80, прямой выход которого соединен с A, B-м выходом 33 матрицы загрузки 9 и с B-м входом A-го элемента ИЛИ-НЕ 78, выход которого соединен с A-м входом элемента ИЛИ 82, выход которого соединен с выходом 30 матрицы загрузки 9, выход первого элемента ИЛИ-НЕ 87 78,1 матрицы загрузки 9 соединен с третьими входами элементов И 81 первой строки, первым и вторым входом элемента И-НЕ 83,1 и со вторым входом второго элемента И-НЕ 83,2, выходы третьего 78,3 и второго 78,2 элементов ИЛИ-НЕ матрицы загрузки 9 соединены соответственно с третьими входами третьей и второй строк элементов И 81 матрицы загрузки 9, выход второго элемента ИЛИ-НЕ 78,2 матрицы загрузки 9 соединен с первым входом второго элемента И-НЕ 83,2, выход A-го элемента И-НЕ 83 матрицы загрузки 9 соединен с четвертыми входами A+1-й строки элементов И 81 матрицы загрузки 9, A, B-й вход второй группы входов 33 отверстий матрицы 10 соединен со вторым входом A, B-го элемента И 84, выход которого соединен с A-м входом B-го элемента ИЛИ 85, выход которого соединен с B-м выходом 28 ответной матрицы 10, A-й вход первой группы входов 32 которой соединен с первыми входами A-го столбца элементов И 84 ответной матрицы 10, a, B-й вход второй группы входов 33 адресной матрицы 11 соединен с управляющим входом A, B-го группового элемента И 86, группа выходов которого соединена соответственно с B-й группой входов A-го группового элемента ИЛИ 87, группа выходов которого соединена соответственно с A-й групповой выходов 35 адресной матрицы 11, B-я группа первой группы входов 34 которой соединена соответственно с группой с группой информационных входов B-го столбца групповых элементов И 86 адресной матрицы 11, S-й вход R-й группы входов группового элемента ИЛИ 87 соединен с R-м входом S-го элемента ИЛИ 88, выход которого соединен с S-м выходом 35 группового элемента ИЛИ 87, B-й вход A-й группы второй группы входов 33 блока фильтрации 12 соединен с B-м входом A-го группового элемента И 89, B-й выход которого соединен с A-м входом B-го элемента ИЛИ 92 второй группы, выход которого соединен с B-м выходом второй группы выходов 38 блока фильтрации 12, B-й вход третьей группы входов 37 которого соединен со вторыми входами B-й строки матрицы элементов И 91 блока фильтрации 12, выход A, B-го элемента И 91 блока фильтрации 12 соединен с A-м входом B-м выходом третьей группы выходов 39 блока фильтрации 12, A, B-й вход первой группы входов 36 которого соединен с первым входом A, B-го элемента И 91, выход которого соединен с B-м входом A-го элемента ИЛИ 90, выход которого соединен с управляющим входом A-го группового элемента И 89 и с A-м выходом первой группы выходов блока фильтрации 12, B, B-й вход второй группы входов 41 информационный матрицы 13 соединен со вторым входом B, B-го элемента И 94, выход которого соединен с B-м входом B-го элемента ИЛИ 95, выход которого соединен с B-м выходом 42 информационной матрицы 13, B-й вход первой группы входов которой 40 соединен с первыми входами B-го столбца элементов И 94 информационной матрицы 13, B, B-й вход второй группы входов 41 матрицы сопряжения 15 соединен со вторым входом B, B-го элемента И 96, выход которого соединен с B-м выходом B-го элемента ИЛИ 97, выход которого соединен с B-м выходом 43 матрицы сопряжения 15, B-й вход первой группы входов 44 который соединен с первыми входами B-го столбца элементов И 96 матрицы сопряжения 15, B-й вход первой группы входов 38 матрицы управления 14 соединен с первыми входами элементов И 99 B-го столбца матрицы управления 14, B-й вход второй группы входов 39 который соединен со вторыми входами элементов И 99 B-й строки матрицы управления 14, выход B, B-го элемента И 99 матрицы управления 14 соединен с единичным входом B, B-го триггера 98, инверсный выход которого соединен с третьим входом B, B-го элемента И 99, прямой выход B, B-го триггера 98 матрицы управления 14 соединен с B, B-м выходом второй группы выходов 41 матрицы управления 14 и с B-м входом B-го элемента ИЛИ 100, выход которого соединен с B-м выходом третьей группы выходов 16 матрицы управления 14 и с выходом B-го элемента НЕ 101, выход которого соединен с B-й вход третьей группы входов 23 которой соединен с нулевыми входами триггеров 98 матрицы управления 14.

группа входов первой группы входов 34 которой соединена соответственно с группой выходов B-го приемного блока 6, A-й выход первой группы выходов 32 блока фильтрации 12 соединен также с A-м входом первой группы входов ответной матрицы 10 и матрицы загрузки 9, группа выходов 33 которой соединена соответственно с вторыми группами входов ответной матрицы 10, адресной матрицы 11, блока фильтрации 12 и блока согласования 5, группа выходов 29 которого соединена соответственно со второй группой входов матрицы загрузки 9, выход 30 которой соединен с входом блока согласования 5, B-й выход второй группы выходов 26 которого соединен соответственно с четвертым входом B-го приемного блока 6, второй выход 25 которого соединен с B-м входом первой группы входом блока согласования 5, третья группа входов которого соединена соответственно с группой входов 28 ответной матрицы 10, B-й информационный 17 и сигнальный 19 входы устройства соединены соответственно со вторым и третьим входами B-го приемного блока 6, первый выход которого соединен с B-м сигнальным выходом 18 устройства, B-й информационный 20 и запросный 22 выходы которого соединены соответственно с первым и вторым выходами B-го передающего блока 7, второй вход которого соединен с B-м запросным входом 21 устройства, третий выход 44 B-го передающего блока 7 соединен с B-м входом первой группы входов матрицы сопряжения 15, B-й выход 43 которой соединен с пятым входом B-го приемного блока 6, третий выход 40 которого соединен с B-м входом первой группы входов информационной матрицы 13, B-й выход 42 которой соединен с третьим входом B-го передающего блока 7, четвертый выход 23 которого соединен с B-м входом третьей группы входов матрицы управления 14, B-й выход третьей группы выходов 16 которой соединен с четвертым входом B-го передающего блока 7, вторые группы входов информационной матрицы 13 и матрицы сопряжения 15 соединены соответственно со второй группой выходов 41 матрицы управления 14, первая группа выходов 37 которой соединена соответственно с третьей группой входов блока фильтрации 12, вторая 38 и третья 39 группы выходов которого соединены соответственно с первой и второй группой входов матрицы управления 14, в каждом блоке согласования 5 B-й вход 25 первой группы входов соединен с первым входом B-го элемента И 48 выход которого соединен с единичным входом B-го триггера 49 первой группы, нулевой динамический вход которого соединен с выходом B-го элемента ИЛИ 47, M входов которого соединены соответственно с M входами B-й группы второй группы входов 33 блока согласования 5, вход 30 которого соединен о вторым входом B-го элемента И 48, третий вход которого соединен с инверсным выходом B-го триггера 50 второй группы, прямой выход которого соединен с входом B-го формирующего элемента 46, выход которого соединен с B-м выходом первой 29 и второй 26 группы выходов блока согласования 5, B-й вход третьей группы входов 28 которого соединен с нулевым входом B-го триггера 50 второй группы, единичный динамический вход которого соединен с прямым выходом B-го триггера 49 первой группы, инверсный выход которого соединен с входами всех элементов И 48 кроме B-х, первый вход каждого приемного блока 6 соединен с первым входом второго элемента И 54, вторыми входами четвертого 61 и пятого 65 элементов И и со счетным входом первого счетчика 52, выход которого соединен с первым входом первого элемента И 51, выход которого соединен со вторым выходом 25 приемного блока 6, второй вход 17 которого соединен с информационным входом приемного регистра 59, группа выходов которого, соответствующая прямым выходам триггера, содержащих адрес ЭВМ назначения, соединена соответственно с группой выходов 34 блока 6, третий вход 19 которого соединен с первым входом шестого элемента И 67, выход которого соединен с первым выходом 18 приемного блока 6, четвертый вход 26 которого соединен с нулевым входом второго триггера 55, прямой выход которого соединен со вторым входом первого элемента И 51, пятый вход 43 приемного блока 6 соединен с единичным динамическим входом первого триггера 53 и с нулевым динамическим входом третьего триггера 60, прямой выход которого соединен с управляющим входом приемного регистра 59, информационный выход которого соединен с третьим выходом 40 приемного блока 6, прямой выход первого триггера 53 приемного блока 6 соединен со вторым входом второго элемента И 54 и со вторым входом второго элемента ИЛИ 66, выход которого соединен с первым входом пятого элемента И 65, выход которого соединен с тактовым входом приемного регистра 59, информационный выход триггера последнего разряда которого соединен с единичным динамическим входом пятого триггера 63, прямой выход которого соединен с первым входом четвертого элемента И 61 выход которого соединен с суммирующим входом второго счетчика, 56 вычитающий вход которого соединен с выходом второго элемента И 54, информационная группа выходов второго счетчика 56 соединена соответственно с группой входов первого элемента ИЛИ 57, выход которого соединен с нулевыми динамическими входами первого 53 и четвертого 62 триггера, инверсный выход которого соединен с первым входом второго элемента ИЛИ 66, прямые выходы триггеров разрядов второго счетчика 56 приемного блока 6, соответствующие числу битов в пакете информации, соединены соответственно с входами третьего элемента И 58, выход которого соединен с единичными динамическими входами второго 55, третьего 60 и четвертого 62 триггеров и с нулевым динамическим входом пятого триггера 63, выход первого элемента ИЛИ 57 приемного блока 6 соединен с входом элемента НЕ 64, выход которого соединен с вторым входом шестого элемента И 67, первый вход 42 каждого передающего блока 7 соединен со счетным входом второго счетчика 71 и со вторым входом первого элемента И 69, выход которого соединен со счетным входом первого счетчика 70 выход которого соединен с инверсным входом первого триггера 68 и с четвертым выходом 23 передающего блока 7, второй вход 21 которого соединен с нулевым входом второго триггера 73, инверсный выход которого соединен с первым входом третьего элемента И 74, выход которого соединен с третьим выходом 44 передающего блока 7, третий вход 42 которого соединен с прямым входом первого триггера 68 и с первым выходом 20 передающего блока 7, четвертый вход 16 которого соединен с входом элемента задержки 45 и с единичным динамическим входом второго триггера 73, прямой выход которого соединен со вторым входом второго элемента И 72, выход которого соединен со вторым выходом 22 передающего блока 7, выход второго счетчика 71 передающего блока 7 соединен с первым входом второго элемента И 72, выход элемента задержки 45 передающего блока 7 соединен со вторым входом третьего элемента И 74, прямой выход первого триггера 68 передающего блока 7 соединен с первым входом первого элемента И 69, группа входов 35 блока выбора маршрута 8 соединена соответственно с группой входов постоянного запоминающего устройства 77 блока выбора маршрута 8, первый 31 и второй 32 входы которого соединены соответственно с управляющим входом группового элемента И 75 и с входом установки в "O" регистра 76, A-й вход первой группы входов 32 матрицы загрузки 9 соединен с входом A-го элемента задержки 79, выход которого соединен с нулевыми входами триггеров 80 A-й строки матрицы загрузки 9, B-й вход второй группы входов 29 которой соединен с первыми входами элементов И 81 B-го столбца матрицы загрузки 9, инверсный выход A, B-го триггера 80 матрицы загрузки 9 соединен с вторым входом A, B-го элемента И 81, выход которого соединен с единичным входом A, B-го триггера 80, прямой выход которого соединен с A, B-м выходом 33 матрицы загрузки 9 и с B-м входом A-го элемента ИЛИ-НЕ 78, выход которого соединен с A-м входом элемента ИЛИ 82, выход которого соединен с выходом 30 матрицы загрузки 9, выход первого элемента ИЛИ-НЕ 87 78,1 матрицы загрузки 9 соединен с третьими входами элементов И 81 первой строки, первым и вторым входом элемента И-НЕ 83,1 и со вторым входом второго элемента И-НЕ 83,2, выходы третьего 78,3 и второго 78,2 элементов ИЛИ-НЕ матрицы загрузки 9 соединены соответственно с третьими входами третьей и второй строк элементов И 81 матрицы загрузки 9, выход второго элемента ИЛИ-НЕ 78,2 матрицы загрузки 9 соединен с первым входом второго элемента И-НЕ 83,2, выход A-го элемента И-НЕ 83 матрицы загрузки 9 соединен с четвертыми входами A+1-й строки элементов И 81 матрицы загрузки 9, A, B-й вход второй группы входов 33 отверстий матрицы 10 соединен со вторым входом A, B-го элемента И 84, выход которого соединен с A-м входом B-го элемента ИЛИ 85, выход которого соединен с B-м выходом 28 ответной матрицы 10, A-й вход первой группы входов 32 которой соединен с первыми входами A-го столбца элементов И 84 ответной матрицы 10, a, B-й вход второй группы входов 33 адресной матрицы 11 соединен с управляющим входом A, B-го группового элемента И 86, группа выходов которого соединена соответственно с B-й группой входов A-го группового элемента ИЛИ 87, группа выходов которого соединена соответственно с A-й групповой выходов 35 адресной матрицы 11, B-я группа первой группы входов 34 которой соединена соответственно с группой с группой информационных входов B-го столбца групповых элементов И 86 адресной матрицы 11, S-й вход R-й группы входов группового элемента ИЛИ 87 соединен с R-м входом S-го элемента ИЛИ 88, выход которого соединен с S-м выходом 35 группового элемента ИЛИ 87, B-й вход A-й группы второй группы входов 33 блока фильтрации 12 соединен с B-м входом A-го группового элемента И 89, B-й выход которого соединен с A-м входом B-го элемента ИЛИ 92 второй группы, выход которого соединен с B-м выходом второй группы выходов 38 блока фильтрации 12, B-й вход третьей группы входов 37 которого соединен со вторыми входами B-й строки матрицы элементов И 91 блока фильтрации 12, выход A, B-го элемента И 91 блока фильтрации 12 соединен с A-м входом B-м выходом третьей группы выходов 39 блока фильтрации 12, A, B-й вход первой группы входов 36 которого соединен с первым входом A, B-го элемента И 91, выход которого соединен с B-м входом A-го элемента ИЛИ 90, выход которого соединен с управляющим входом A-го группового элемента И 89 и с A-м выходом первой группы выходов блока фильтрации 12, B, B-й вход второй группы входов 41 информационный матрицы 13 соединен со вторым входом B, B-го элемента И 94, выход которого соединен с B-м входом B-го элемента ИЛИ 95, выход которого соединен с B-м выходом 42 информационной матрицы 13, B-й вход первой группы входов которой 40 соединен с первыми входами B-го столбца элементов И 94 информационной матрицы 13, B, B-й вход второй группы входов 41 матрицы сопряжения 15 соединен со вторым входом B, B-го элемента И 96, выход которого соединен с B-м выходом B-го элемента ИЛИ 97, выход которого соединен с B-м выходом 43 матрицы сопряжения 15, B-й вход первой группы входов 44 который соединен с первыми входами B-го столбца элементов И 96 матрицы сопряжения 15, B-й вход первой группы входов 38 матрицы управления 14 соединен с первыми входами элементов И 99 B-го столбца матрицы управления 14, B-й вход второй группы входов 39 который соединен со вторыми входами элементов И 99 B-й строки матрицы управления 14, выход B, B-го элемента И 99 матрицы управления 14 соединен с единичным входом B, B-го триггера 98, инверсный выход которого соединен с третьим входом B, B-го элемента И 99, прямой выход B, B-го триггера 98 матрицы управления 14 соединен с B, B-м выходом второй группы выходов 41 матрицы управления 14 и с B-м входом B-го элемента ИЛИ 100, выход которого соединен с B-м выходом третьей группы выходов 16 матрицы управления 14 и с выходом B-го элемента НЕ 101, выход которого соединен с B-й вход третьей группы входов 23 которой соединен с нулевыми входами триггеров 98 матрицы управления 14.

Устройство для коммутации сообщений работает следующим образом.

Передача сообщений коммутируемых устройством осуществляется в виде пакетов. Каждый пакет кроме передаваемой информации содержит также адрес ЭВМ назначения и начинается с единичного бита. Устройство позволяет коммутировать пакеты информации передаваемые по K дуплексным каналам связи и обрабатываемые с помощью M блоков выбора маршрута. На представленных чертежах изображено устройство для коммутации сообщений с числом K=4 и M=3, однако в общем случае числами K и M могут быть любые целые числа.

Перед началом работы триггера 49,1-49,4 блока 5 согласования, счетчики 52, 56, триггеры 53, 55, 62, 63 регистр 59 приемного блока 6, триггеры 68, 73, счетчики 70, 71 передающего блока 7, регистр 76 блока выбора маршрута 8, триггеры 80,1 - 80,34 матрицы загрузки 9, триггеры 98,11 - 98,44 матрицы управления 14 устанавливаются в исходное (нулевое) состояние (входы установки в исходное состояние условно не указаны).

Процесс обработки пакета информации начинается с его поступления в последовательном коде на один из информационных входов устройства 17.1-17.4.

Предположим, что по второму информационному входу 17.2 устройства поступил пакет информации. Факт поступления пакета отождествляется с появлением единичного сигнала И 1 на прямом выходе последнего разряда приемного регистра 59 приемного блока 6.2 (фиг. ). Пакет информации, поступающий с информационного входа 17.2 устройства на информационный вход приемного регистра 59, побитно в него записывается тактовыми импульсами, поступающими с генератора 1 тактовых импульсов по связи 24 через открытый элемент И 65 на тактовый вход приемного регистра 59. Регистр 59 аналогичен по своей конструкции регистру задержки данных (например, как микросхема К555ИР9). В приемном регистре 59 осуществляется хранение пакета информации на все время его обработки в устройстве. Сигнал И. 1 поступает на динамический единичный вход триггера 63 и своим передним фронтом устанавливает его в единичное состояние, в результате чего на прямом выходе триггера 63 проявляется потенциал единичного уровня П.1. Потенциал П.1 поступает на второй вход элемента И 61 и открывает его для прохождения импульсов с генератора 1 тактовых импульсов по связи 24 на первый счетный вход второго счетчика 56. Счетчик 56 является реверсивным счетчиком, поэтому по первому счетному входу он осуществляет суммирование тактовых импульсов генератора 1 (его содержимое в этом случае соответствует числу приятых битов пакета), а по второму счетному входу он производит вычитание тактовых импульсов генератора 1 и его содержимое в этом случае равно числу битов пакета, которые еще не переданы. При подсчете тактовых импульсов счетчиком 56 на его информационных выходах появляются потенциалы единичного уровня, в результате чего на выходе первого элемента ИЛИ 57 постоянно присутствует потенциал единичного уровня П.2. С выхода элемента ИЛИ 57 потенциал П.2 поступает на вход элемента Не 64, инвертируется в нем и, поступая на второй вход элемента И 67, закрывает его. Это свидетельствует о том, что приемный блок 6 (в данном случае 6,2) в данный момент времени не готов к приему других пакетов.

Так как прямые выходы разрядов счетчика 56, соответствующие числу битов в пакете в двоичном коде, соединены с входами элемента И 58, то появление потенциала единичного уровня П.3 на выходе элемента и 58 свидетельствует о том, что приемный регистр 59 принял весь пришедший пакет информации. Потенциал П.3 поступает на динамический единичный вход триггера 62 и своим передним фронтом устанавливает его в единичное состояние, в результате этого на его инверсном выходе появляется потенциал нулевого уровня. На выходе элемента ИЛИ 66 также появляется потенциал нулевого уровня, что приводит к закрытию элемента И 65 для поступления тактовых импульсов с генератора 1 на тактовый вход приемного регистра 59. Этот же потенциал П.3, поступая на динамический единичный вход триггера 55, своим передним фронтом устанавливает его в единичное состояние. На прямом выходе триггера 55 появляется потенциал единичного уровня и элемент И 51 открывается. Потенциал П.3 поступает на единичный вход триггера 60 и своим передним фронтом устанавливает его в единичное состояние, в результате чего потенциал единичного уровня с прямого выхода триггера 60 поступает на управляющий вход приемного регистра 59 и останавливает в нем трансляцию информации.

Первый счетчик 52 выполняет функции делителя частоты следования импульсов. Он осуществляет подсчет заданного числа тактовых импульсов генератора 1, после чего он самопроизвольно устанавливается в исходное состояние и на его выходе появляется импульс И. 2. Импульс И.2 проходит через открытый элемент И 51 и появляется на связи 25.2 устройства, что свидетельствует о запросе приемного блока 6,2 на установление коммутации с произвольным свободным блоком 8 выбора маршрута.

По связи 25.2 импульс И.2 поступает на первый вход элемента И 48.2 блока 5 согласования (фиг. 2). Если окажется, что все блоки 8.1-8.3 заняты обработкой пакетов, то на связи 30 устройства будет установлен потенциал нулевого уровня, который поступает на вход блокировки блока 5 согласования и закрывает по пятому входы элементы И 48.1-48.4. В этом случае блок 6.2 генерирует повторно импульс И.2 через период времени, определяемый периодом следования импульсов с генератора 1 и коэффициентом пересчета счетчика 52 приемного блока 6.2. Если же окажется свободным хотя бы один блок 8 выбора маршрута, то на связи 30 устройства будет присутствовать разрешающий потенциал единичного уровня, который не будет препятствовать прохождению импульсов запроса И. 2 через элементы И 48.1-48.4. После прохождения импульса И.2 через открытый элемент И 48.2 он поступает на единичный вход триггера 49,2 и устанавливает его в единичное состояние, в результате чего на прямом выходе триггера 49.2 появляется потенциал единичного уровня П.4, а на его инверсном выходе появляется потенциал нулевого уровня П.5. потенциал П.5 поступает на входы элементов И 48.1, 48.3, 48.4 и закрывает их для прохождения импульсов И.2 по связям 25.1, 25.3, 25.4. потенциал П.4 триггера 49.2 поступает на единичный динамический вход триггера 50.2 и своим передним фронтом устанавливает его в единичное состояние. При переходе триггера 50.2 в единичное состояние на его прямом выходе появляется потенциал единичного уровня. На изменение потенциалов с нулевого уровня на единичный реагирует формирующий элемент 104.2 и формирует импульс И.3, который появляется на связях 29.2, 26.2 устройства. На инверсном выходе триггера 50.2 появляется потенциал нулевого уровня П.6. Потенциал П.6 поступает третий вход элемента 48.2 и закрывает его для прохождения других импульсов И.2 приемного блока 6.2. Импульс И.3 по связи 26.2 поступает на нулевой вход триггера 55 приемного блока 6.2 и устанавливает его в нулевое состояние. В результате этого на прямом выходе триггера 55 появляется потенциал нулевого уровня, элемент И 51 закрывается и это препятствует появлению новых импульсов И.2 на связи 25.2 устройства. Таким образом, на связях 29.1-29.4 в любой момент времени может появиться не более одного импульса И.3. В данном случае импульс И.3 появился на связи 29.2 устройства.

По связи 29.2 устройства импульс И.3 поступает на первые входы элементов И. 81.12, 81.22, 81.32 матрицы загрузки 9 (фиг. 6) и появляется только на выходе элемента И 81.12, так как первоначально все блоки 8 выбора маршрута не заняты обработкой пакетов. Далее импульс И.3 поступает на единичный вход триггера 80,12 и переводит его в единичное состояние, в результате чего на прямом и инверсном выходах триггера 80,12 появляются соответственно потенциалы единичного П.7 и нулевого П.8 уровней. Потенциал П.8 поступает на второй вход элемента И 81.12 и закрывает его для прохождения других импульсов И. 3 по первому входу элемента И 81.12. Потенциал П.7 поступает на второй вход элемента ИЛИ-НЕ 78.1, в результате чего на его выходе появляется потенциал П.9 нулевого уровня, который поступает на первый и второй входы элемента И-НЕ 83.1, и на его выходе появляется потенциал П.10 единичного уровня. Потенциал П.10 поступает на четвертые входы элементов И 81.21-81.24, открывает их и подготавливает тем самым к загрузке на обработку блок 8.2 выбора маршрута. Кроме того, потенциал П.9 поступает на третьи входы элементов И 81.11-81.14, блокирует их от принятия других запросов блоком 8.1 выбора маршрута. Потенциал П.9 с соответствующих выходов элементов И-НЕ 78 поступают также на вход элемента ИЛИ 82, причем, как только все блоки 8 выбора маршрута станут загружены обработкой пакетов, то на выходе элемента ИЛИ 82 появится блокирующий потенциал нулевого уровня, который по связи 30 устройства поступает в блок 5 согласования. Таким образом, в любой момент времени, в любом столбце или в любой строке матрицы загрузки 9 может находится в единичном состоянии не больше одного триггера 80. Появление потенциала П.7 на связи 33.12 устройства приводит к тому, что на выходе элемента ИЛИ 47.2 также появляется потенциал П.7, который поступает на нулевой динамический вход триггера 49.2 и своим передним фронтом устанавливает его в нулевое состояние. Таким образом, триггер 49 блока согласования 5 находится в единичном состоянии только на время установления коммутации между соответствующим приемным блоком 6 и выбранным блоком 8 выбора маршрута.

Потенциал П. 7 по связи 33.12 устройства поступает также на управляющий вход группового элемента И 86.12 адресной матрицы 11 (фиг. 8), открывает его и в результате адрес ЭВМ назначения пришедшего пакета с группы информационных выходов приемного регистра 59 по группе связей 34.2 через групповой элемент И 86.12 поступает на вторую группу входов группового элемента ИЛИ 87.1. Так как число элементов ИЛИ 88 группового элемента ИЛИ 87 (фиг. 9) соответствует числу битов адреса ЭВМ назначения пришедшего пакета и выходы групповых элементов И 86 скоммутированы так, как это показано на фиг. 9, то на выходе группового элемента ИЛИ 87 появляется адрес ЭВМ назначения пришедшего пакета.

Этот адрес по группе связей 35.1 поступает на ПЗУ 77 блока 8.1 выбора маршрута (фиг. 5). ПЗУ 77 содержит маршрутные таблицы. По адресной части пакета, содержащей адрес ЭВМ назначения, из ПЗУ 77 выбирается номер канала выдачи (т. е. номер передающего блока 7), который заносится в регистр 76. В результате на информационных выходах регистра 76 ( а следовательно, и на информационных входах группового элемента И 75) появляется код, соответствующий номеру передающего блока 7. Предположим, что для дальнейшей передачи пакета информации выбран передающий блок 7.3 (т.е. третий канал выдачи).

Первый счетчик 2 устройства представляет собой делитель числа импульсов, поступающих с генератора 1 тактовых импульсов. При достижении установленного в нем коэффициента пересчета он самопроизвольно (автономно) устанавливается в исходное состояние и на его выходе появляется импульс, который поступает на счетный вход второго счетчика 3. Максимальный коэффициент пересчета счетчика 3 выбирается таким образом, чтобы счетчик 3 имел столько состояний, сколько в устройстве содержится блоков 8 выбора маршрута. В данном случае счетчик 3 может находиться только в трех состояниях 01, 10, 11 (состояние 00 в данном случае считается запрещенным). Дешифратор 4 производит дешифрацию содержимого счетчика 3, в результате чего поочередно на его выходах появляется импульсы И.4. Длительность импульсов И.4 зависит главным образом от периода следования тактовых импульсов с генератора 1 и от коэффициента пересчета счетчика 2 и определяется временем установления коммутации между выбранным блоком 8 выбора маршрута и соответствующим передающим блоком 7. С первого выхода дешифратора 4 импульс И.4 по соответствующей связи 31 устройства поступает на управляющий вход группового элемента И 75. В результате этого номер выбранного передающего блока 7.3 поступает по группе связей 36.1 устройства на первые входы группы элементов 91.11-91.14 блока фильтрации 12 (фиг. 10). В указанном случае будет присутствовать импульс Т.4 только на связи 36.13. Если бы передающий блок 7.3 был занят передачей другого пакета информации, то в этом случае присутствовал бы запрещающий потенциал нулевого уровня с матрицы управления 14 по связи 37.3 устройства, и импульс И.4 не был бы пропущен через элемент И 91.13. Но так как первоначально передающий блок 7.3 свободен от передачи других пакетов информации, то импульс И.4 появляется на выходе элемента Т91.13, поступает на первый вход элемента ИЛИ 93.3 и появляется на связи 39.3 устройства. Импульс Т.4 проходит также через элемент ИЛИ 90.1, поступает на управляющий вход группового элемента И 89.1 и переписывает адрес приемного блока 6 с группы связей 33.11-33.14 устройства через групповой элемент И 89.1, через группу элементов ИЛИ 92.1-92.4 на группу связей 38.1-38.4. Так как длительность импульса И.4 больше суммарного времени срабатывания элементов ИЛИ 90.1 и группового элемента И 89.1, то с выходов блока фильтрации 12 на связях 38.1-38.4 и 39.1-39.4 появляются соответственно и одновременно номер приемного блока 6.2 и номер передающего блока 7.3. В данном случае появятся импульсы И.5 единичного уровня на связях 38.2 и 39.3 устройства. Кроме того, импульс И.4 с элемента ИЛИ 90.1 поступает на связь 32.1 устройства, проходит через открытый элемент Т 84.12 ответной матрицы 10 (фиг. 7) (так как на втором входе элемента И 84.12 присутствует потенциал единичного уровня со связи 33.12 устройства), через элемент ИЛИ 85.2 ответной матрицы 10 и по связи 28.2 поступает на нулевой вход триггера 50.2 и устанавливает его в нулевое состояние. Со связи 32.1 импульс И. 4 поступает на вход элемента задержки 79.1 матрицы загрузки 9 (фиг. 6), с выхода которого поступает на нулевые входы триггеров 80.11-80.14 и устанавливает триггер 80.12 в нулевое состояние (у триггеров 80.11, 80.13, 80.14 подтверждает нулевое состояние). Величина задержки элемента задержки 79 несколько больше суммарного времени срабатывания элементов И 84 и ИЛИ 85 ответной матрицы 10.

После этого вновь прибывший пакет информации поступает на обработку в блок 8.2 выбора маршрута при условии, что блок 8.1 выбора маршрута еще остается занятым обработкой пакета.

Импульсы И 5 по связям 38.2 и 39.3 поступают на матрицу управления 14 (фиг. 13). В элементе И 99.32 происходит совпадение этих импульсов, в результате чего триггер 98.32 переводится в единичное состояние и на его прямом и инверсном выходах проявляются соответственно потенциалы единичного П.8 и нулевого П. 9 уровней. Потенциал П.9 поступает на третий вход элемента И 99.32 и блокирует его для других импульсов, а потенциал П.8 появляется на связи 41.32 устройства. При появлении потенциала П.8 на связи 41.32 устройства открываются элементы И 94.32 информационной матрицы 13 (фиг. 11), И 96.23 матрицы сопряжения 15 (фиг. 14). Кроме того, потенциал П.8 с выхода триггера 98.32 матрицы управления 14 проходит через элемент ИЛИ 100, появляется на связи 16.3 устройства и инвертируется в элементе НЕ 101.3. Потенциал нулевого уровня с выхода элемента НЕ 101.3 по связи 37.3 поступает в блок фильтрации 12 и блокирует установление всех других возможных коммутаций с передающим блоком 7.3. Потенциал П.8 по связи 16.3 устройства поступает на единичный динамический вход триггера 73 и через элемент задержки 105 на второй вход элемента И 74 передающего блока 7.3 (фиг. 4), в результате чего триггер 73 при появлении потенциала П.8 переходит в единичное состояние и своим потенциалом единичного уровня с прямого выхода открывает элемент И. 72. Величина задержки элемента задержки 45 несколько больше времени срабатывания триггера 73.

Счетчик 71 передающего блока 7 (фиг. 4) выполняет роль делителя числа тактовых импульсов генератора 1. При своем переполнении счетчик 71 автономно устанавливается в исходное состояние и на его выходе появляется импульс И.6. Импульс И. 6 проходит через открытый элемент И 72 и появляется на запросном выходе 22.3 устройства, что свидетельствует о запросе передающего блока 7.3 к передаче пакета информации. Если абонент готов к приему пакета информации, то на запросном входе 21.3 устройства появляется импульс И. 7, в противном случае передающий блок 7 генерирует новый импульс запроса на передачу пакета информации на запросном выходе 22.3 устройства. Импульс И. 7 с запросного выхода 21.3 устройства поступает на нулевой вход триггера 73, в результате чего элемент И 72 закрывается, а на выходе элемента И 74 появляется потенциал П. 9 единичного уровня, который по связи 44.3 устройства проходит через открытый элемент И 96.23, элемент ИЛИ 97.2 матрицы сопряжения 15 и по связи 43.2 поступает на единичный вход триггера 53 приемного блока 6.2. Передний фронт потенциала П. 9 переводит триггер 53 в единичное состояние, в результате чего открываются элементы И 65, 54. Кроме того, передний фронт потенциала П.9 переводит триггер 60 в нулевой состояние. На прямом выходе триггера 60 появляется потенциал нулевого уровня, в результате чего в приемном регистре 59 устанавливается режим транзита информации. Тактовыми импульсами, поступающими с генератора 1 через элемент И 65 на тактовый вход приемного регистра 59, осуществляется побитная выдача пакета информации на связь 40.2 устройства, а содержимое счетчика 56 уменьшается в соответствии с числом выдаваемых битов пакета.

Пакет информации в последовательном коде со связи 40.2 устройства проходит через открытый элемент И 94.32, элемент ИЛИ 95.3 информационной матрицы 13 на связь 42.3 устройства, откуда он поступает на информационный выход 20.3 устройства, а следовательно, и в канал связи.

Как только из приемного регистра 59 приемного блока 6.2 будут выданы все биты пакета информации, счетчик 56 установится в исходное состояние и на выходе элемента ИЛИ 57 произойдет смена потенциала с единичного уровня на нулевой. Эта смена потенциала соответствует заднему фронту потенциала П. 2. Задний фронт потенциала П. 2, поступая на динамические нулевые входы триггеров 53 и 62, устанавливает их в исходное (нулевое) состояние. После этого цикл работы приемного блока 6 повторяется снова при поступлении нового пакета информации.

Передача первого же бита по связи 42.3 (он всегда является единичным) приводит к тому, что триггер 68 передающего блока 72 (фиг. 4) устанавливается в единичное состояние. Потенциал единичного уровня с его прямого выхода открывает элемент И 69 и тактовые импульсы с генератора 1 поступают на счетный вход счетчика 70. Максимальный коэффициент пересчета счетчика 70 равен числу битов в пакете. После достижения максимального коэффициента пересчета счетчик 70 устанавливается в нулевое состояние и на его выходе появляется импульс И. 8. Импульс И. 8 устанавливает триггер 68 в нулевое состояние, прекращая подачу тактовых импульсов на счетный вход счетчика 70, и появляется на связи 23.3 устройства. По связи 23.3 импульс И. 8 поступает на нулевые входы триггеров 98.31-98.34 матрицы управления 14 и устанавливает триггер 98.32 в нулевое состояние, а у триггеров 98.31, - 98.34 подтверждает нулевое состояние.

После этого цикл работы устройства повторяется снова.