с

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный коммутатор | 1991 |

|

SU1800605A1 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ СООБЩЕНИЙ | 1994 |

|

RU2110837C1 |

| Матричный коммутатор | 1987 |

|

SU1499364A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Коммутационное устройство | 1989 |

|

SU1621041A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

Изобретение относится к дискретной автоматике и вычислительной технике и может быть использовано в системах передачи денных иерархических АСУ. Матричный коммутатор содержит блок прямого согласования 1, матрицу загрузки 2, блок обратного согласования 3, матрицу прямой коммутации 4, матрицу обратной коммутации 5, блок управления 6, внутренние связи 7-10, 19, группы кодовых входов 11 .группу сйгнальнЫх входов обратного канала 12, труппу запросных вхбдЪв квантрв обработки 13, группу запросных входов сообщений 14, группу информацйбнных входов прямого канала 15, группу информационных вы- хо;д6в прямого канала ; 16. группу информационных входбв рб ратногб канала 17, группу информационных выходов обратного канала 18.1 з.п. ф-лы, 5 ил.

//./

;.

ПЛ с±ф

VJ

00 00 00

Изобретение относится к дискретной автоматике и вычислительной технике и может быть использовано в системах передачи данных иерархических АСУ.

Известно матричное устройство коммутации, содержащее матрицу коммутаторов, каждый из которых содержит М х N запоминающих элементов, организованных в матрицу из М строк и N столбцов, и М х N управляемых ключей, управляющий вход каждого из которых соединен с выходом одного из запоминающих элементов, в каждой строке каждого коммутатора объединены входы управляемых ключей, а в каждом столбце каждого коммутатора выходы управляемых ключей, управляющие входы запоминающих элементов подключены к управляющим шинам выбора строки и выбора столбца.

Однако это устройство коммутирует потоки информации только в прямом направлении и не позволяет осуществлять коммутацию потоков информации в обратном направлении.

Наиболее близким по технической сущности и достигаемому положительному эффекту является матричный коммутатор, содержащий матрицу загрузки, матрицы прямой и обратной коммутации, блоки прямого и обратного согласования, дифференцирующий элемент, диод, элемент ИЛИ, причем группа сигнальных входов прямого канала соединена с первой группой входов блока прямого согласования, вторая группа входов которого соединена с первой группой сигнальных входов обратного канала соединена с первой группой входов блока обратного согласования, выход которого соединен с первым входом блока прямого согласования, второй вход которого соединен через последовательно соединенные диод и дифференцирующий элемент с выходом элемента ИЛИ, входы которого соединены с выходами матрицы загрузки и управляющими входами матриц прямой и обратной коммутации, входы которых соединены с группами информационных входов соответственно прямого канала и обратного канала, а выходы с группами информационных входов соответственно прямого канала и обратного канала, а выходы с группами информационных выходов соответственно прямого канала и обратного канала, выходы блока прямого согласования соединены с группой входов матрицы загрузки, группа входов-выходов которой соединена с группой входов-выходов блока обратного согласования.

Однако данное устройство, принятое за прототип, не позволяет коммутировать запросы одного источника сообщений на несколько средств обработки одновременно, что обуславливает низкие функциональные возможности известного устройства, в результате чего оно не находит широкого применения.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности коммутации

0 любого входа матричного коммутатора на требуемое число его входов.

Поставленная цель достигается тем, что в матричный коммутатор содержащий блок прямого согласования, матрицу загрузки,

5 блок обратного согласования, матрицу прямой коммутации, матрицу обратной коммутации, причем группа запросных входов сообщений соединена соответственно с первой группой входов блока прямого со0 гласования, первая группа выходов которого соединена соответственно с первой группой входов матрицы загрузки, вторая группа выходов которой соединена соответственно с первыми группами входов матриц5 прямой и обратной коммутации, первая группа выходов матрицы загрузки соединена соответственно с группой входов блока обратного согласования, группа выходов которого соединена соответственно со второй

0 группой входов матрицы загрузки, группа сигнальных входов обратного канала соединена соответственно с третьей группой вхо- дов матрицы загрузки, выход блока обратного согласования соединен с первым

5 входом блока прямого согласования, группа информационных входов прямого канала соединена соответственно со второй группой входов матрицы прямой коммутации, группа выходов которой соединена соот0 ветственно с группой информационных выходов прямого канала, группа информационных входов обратного канала соединена соответственно со второй группой входов матрицы обратной коммутации,

5 группа выходов которой соединена соответственно с группой информационных выходов обратного канала, причем блок прямого согласования содержит группу триггеров и первую группу элементов И, первые входы

0 которых соединены соответственно с первой группой входов, выходы элементов И первой группы элементов И соединены с S-входами соответствующих триггеров группы, инверсные выходы которых соеди5 нены с входами элементов И первой группы элементов И, соответствующих остальным триггерам группы, причем блок обратного согласования элемент ИЛИ, первую и вторую группы элементов ИЛИ-НЕ, входы блока обратного согласования соединены с

соответствующими входами элементов ИЛИ-НЕ первой группы, выходы которых соединены с входами элемента ИЛИ и входами соответствующих элементов ИЛИ-НЕ второй группы, выходы которых соединены соответственно с выходами блока обратного согласования, выход элемента ИЛИ соединен с выходом блока обратного согласования, причем матрица загрузки содержит элементы матрицы, состоящие из элемента И и триггера, третья группа входов матрицы загрузки соединена соответственно с R-входами триггеров соответствующего столбца матрицы загрузки, инверсные выходы триггеров соединены с вторыми входами соответствующих им элементов И матрицы загрузки, выходы которых соединены с S-входами соответствующих им триггеров матрицы загрузки, выходы триггеров матрицы загрузки соединены соответственно с первой и второй группой выходов матрицы загркуки, входы первой группы входов матрицы загрузки соединены с первыми входами соответствующих элементов И строк матрицы загрузки входы второй группы матрицы загрузки соединены со вторыми входами соответствующих элементов И столбцов матрицы загрузки, причем матрицы прямой и обратной коммутации содержат матрицу элементов И и группу элементов ИЛИ, выходы которых соединены с выходами матриц прямой и обратной коммутации, первые входы элементов И столбцов матрицы элементов И соединены с соответствующими входами второй группы входов матриц прямой и обратной коммутации, выходы элементов И строки матрицы элементов И соединены с входами соответствующего элемента ИЛИ группы элементов ИЛИ, вторые входы элементов И матрицы элементов И соединены с соответствующими входами первой группы входов матриц прямой и обратной коммутации, дополнительно введены блок управления и в блок прямого согласования вторая группа элементов И, причем вторая группа выходов блока прямого согласования соединена соответственно с группой входов блока управления, группы входов которого соединены соответственно с группами кодовых входов устройства, выход блока обратного согласования соединен с входом блока управления, выход которого соединен с вторым входом блока прямого согласования, вторая группа входов которого соединена соответственно с группой запросных входов квантов обработки устройства, причем вторая группа входов блока прямого согласования соединена соответственно с первыми входами элементов И второй группы блока прямого

согласования, вторые входы которых соединены с первым входом блока прямого согла- сования, второй вход блока прямого согласования соединен с R-входами тригге- 5 ров блока прямого согласования, прямые выходы которых соединены соответственно с выходами второй группы выходов блока прямого согласования и с третьими входами одноименных элементов И второй группы

0 блока прямого согласования, выходы которых соединены соответственно с первыми выходами блока прямого согласования, причем блок управления содержит группу регистров, группу формирующих элементов,

5 группу групповых элементов И, групповой элемент ИЛИ, счетчик, два формирующих элемента, элемент ИЛИ-НЕ группы входов блока управления соединены соответственно с группами информационных входов ре0 гистров, информационные выходы которых соединены соответственно с соответствующими информационными входами одноименных групповых элементов И, группы информационных выходов которых соеди5 нены соответственно с группами входов группового элемента ИЛИ, группа выходов которого соединена с информационной группой входов счетчика, группа информационных выходов счетчика соединена с

0 группой входов элемента ИЛИ-НЕ, выход которого соединен с входом второго формирующего элемента, выход которого соединен с выходом блока управления, группа входов блока управления соединена с соот5 ветствующими входами группы формирующих элементов, выходы которых соединены соответственно с управляющими входами одноименных групповых элементов И, вход блока управления соединен с входом перво0 го формирующего элемента, выход которого соединен с вычитающим входом счетчика блока управления.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство

5 отличается наличием новых элементов: группы элементов И, блока управления и соответствующими связями с остальными элементами схемы, что соответствует критерию новизны технического решения.

0 В научно-технической литературе не найдено устройство с описанной совокупностью новых признаков. Это позволяет сделать вывод о соответствии технического решения критерию существенные отли5 чия.

При использовании предлагаемого изобретения может быть получен положительный эффект, заключающийся в повышении коэффициента загрузки средств обработки.

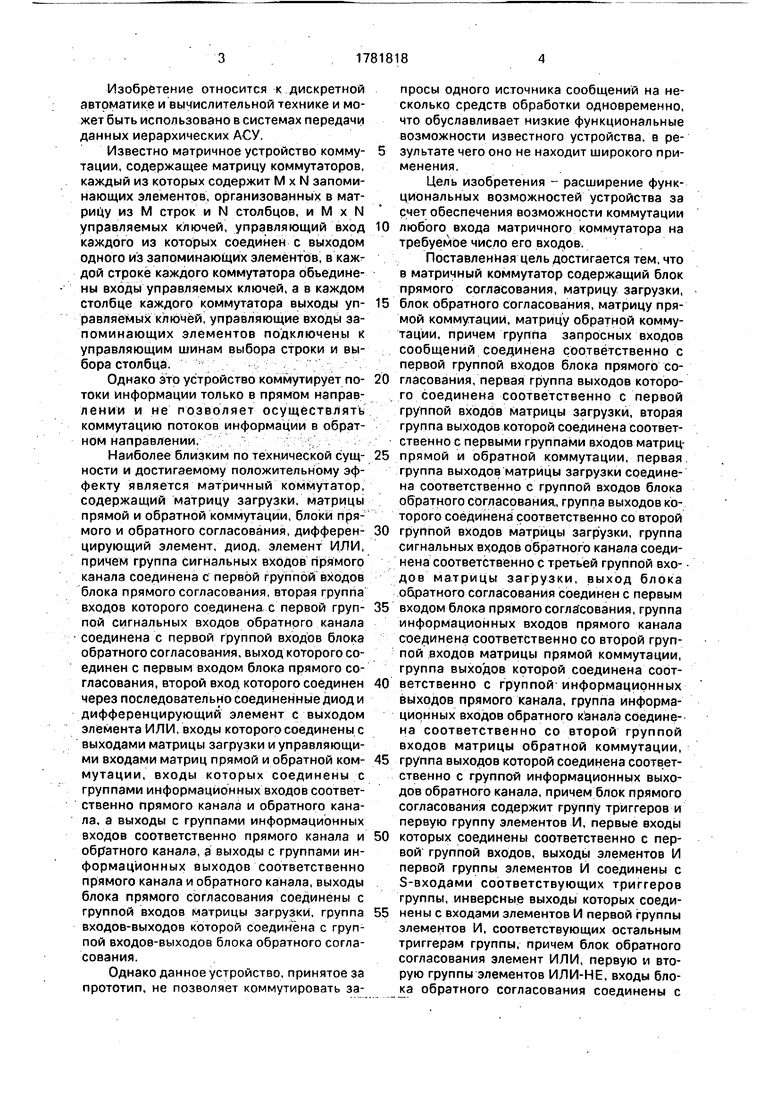

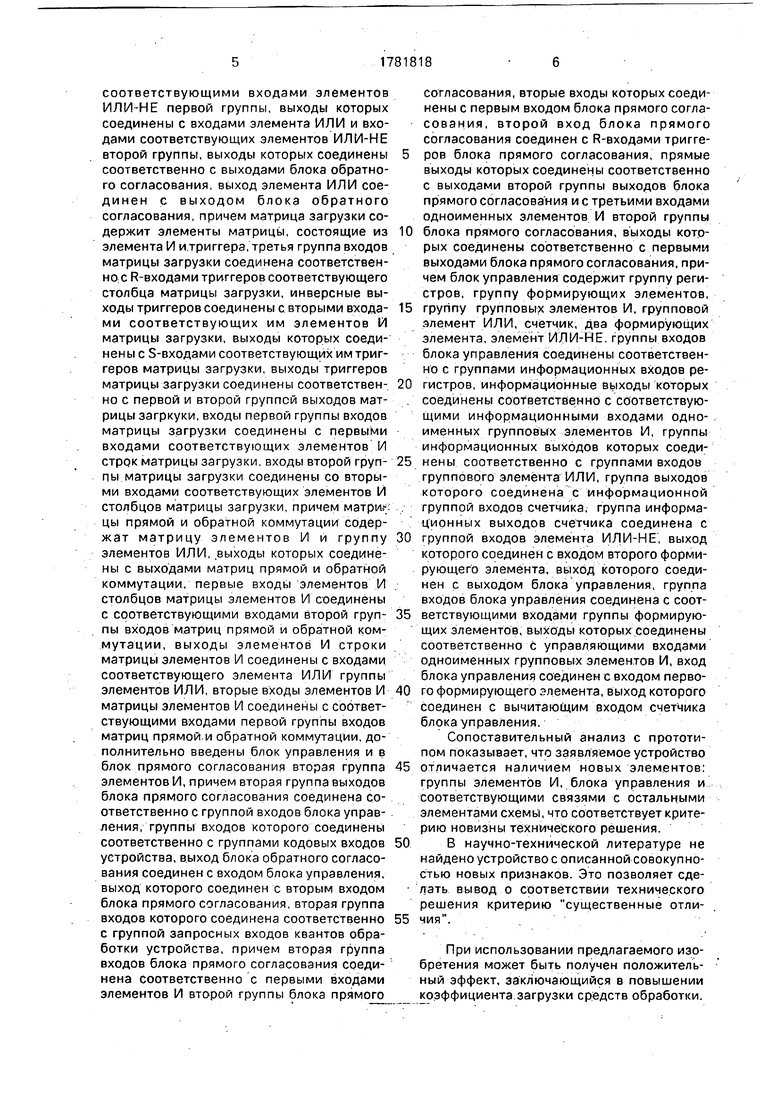

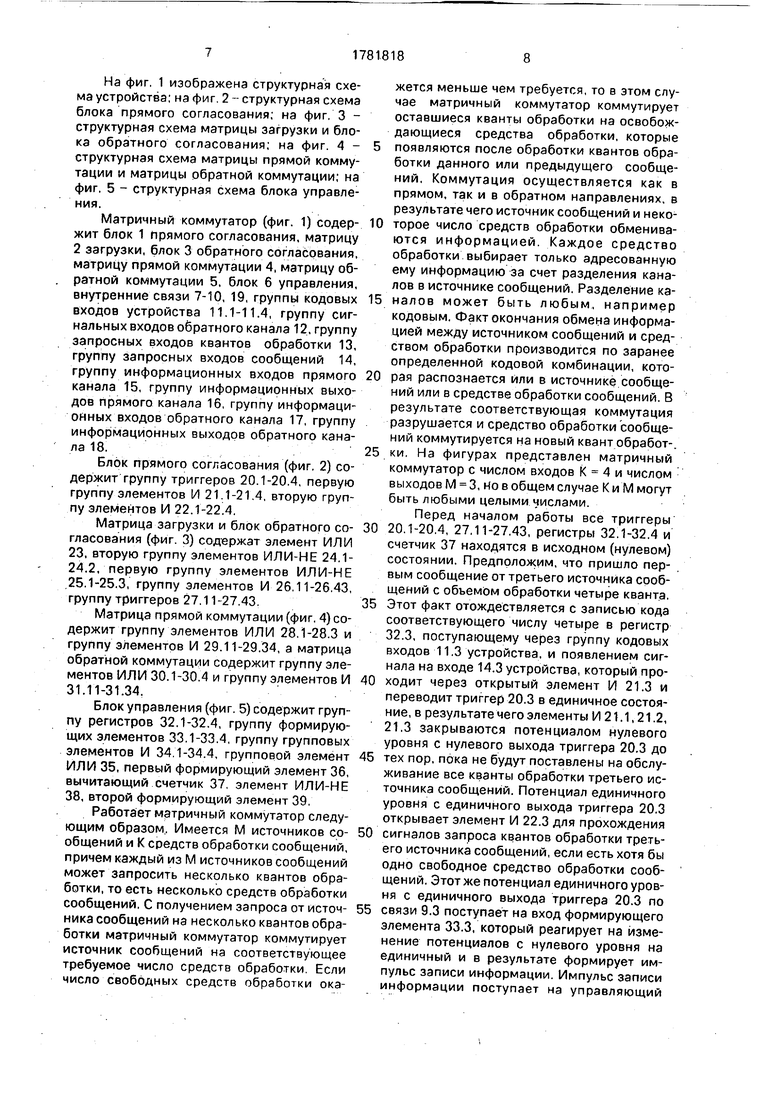

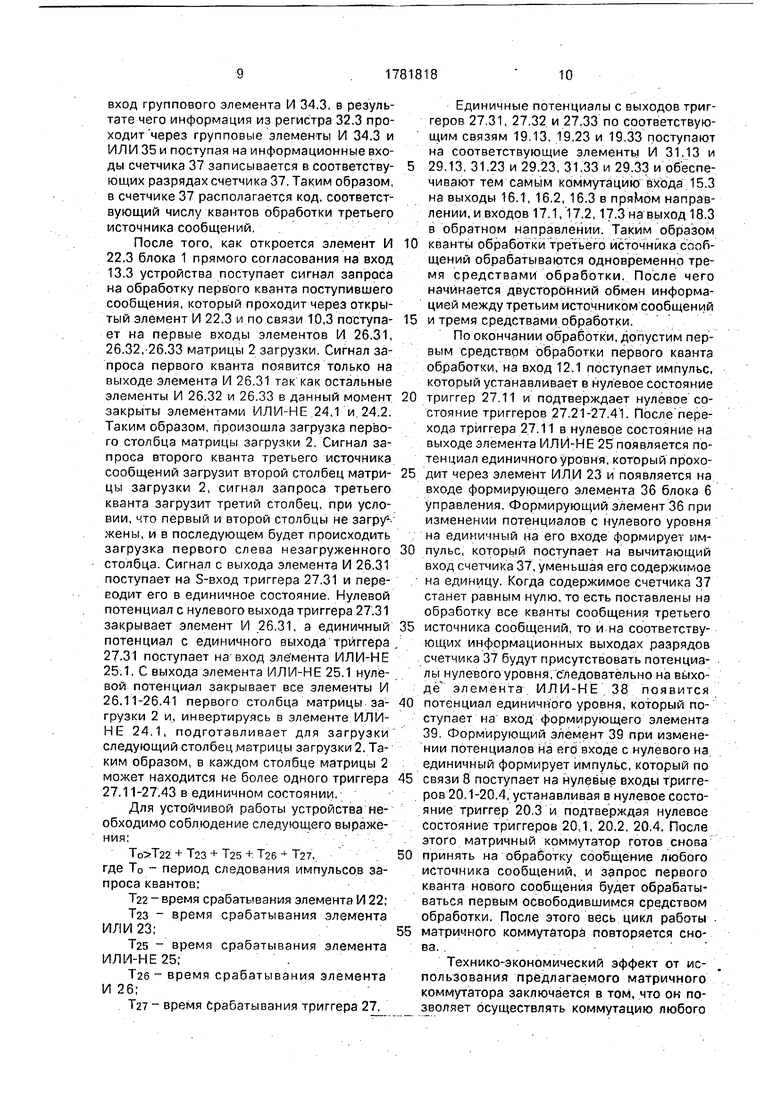

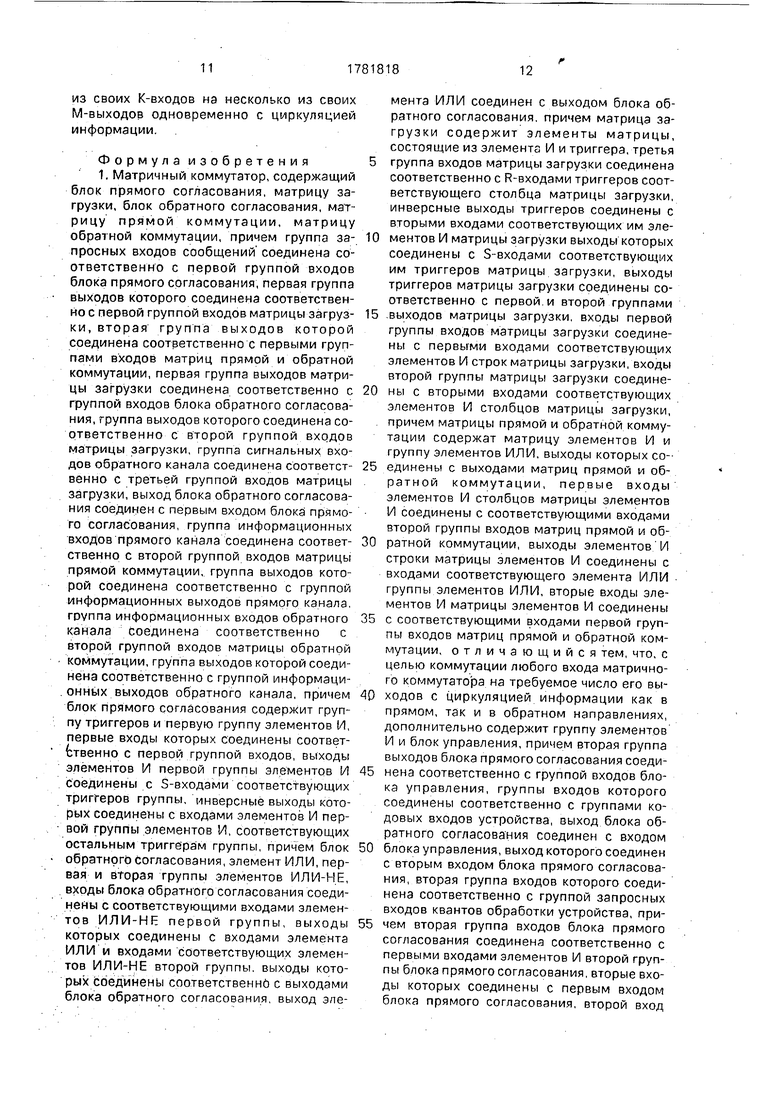

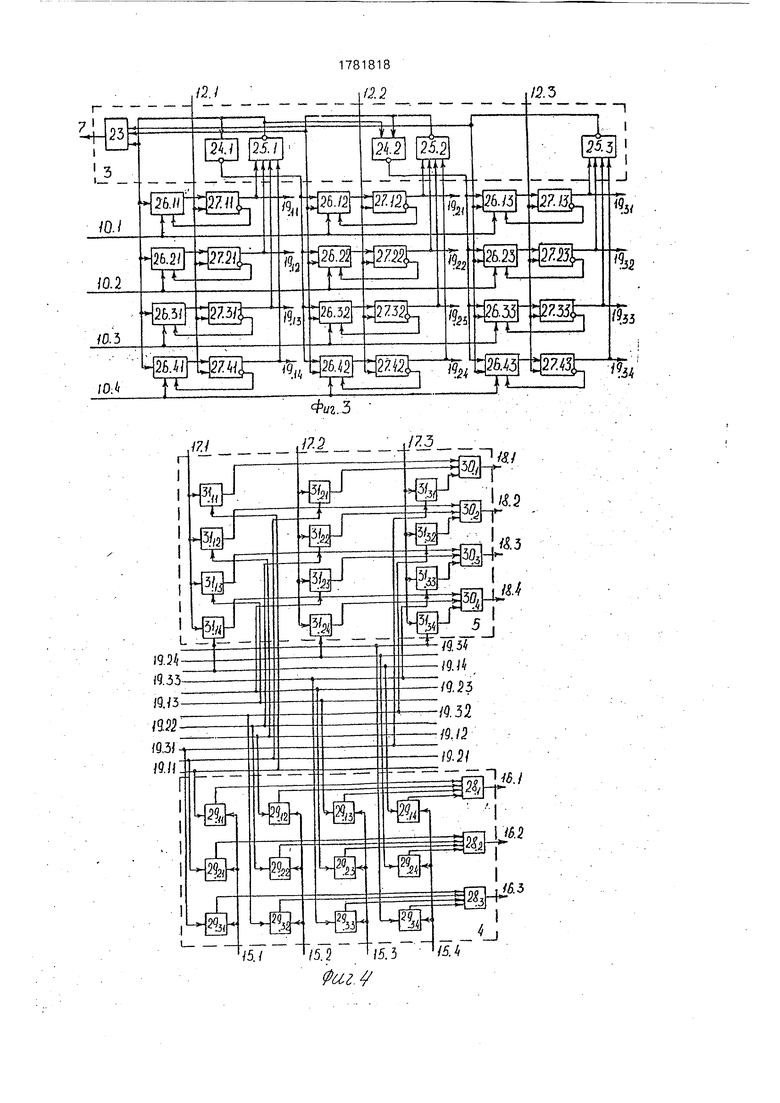

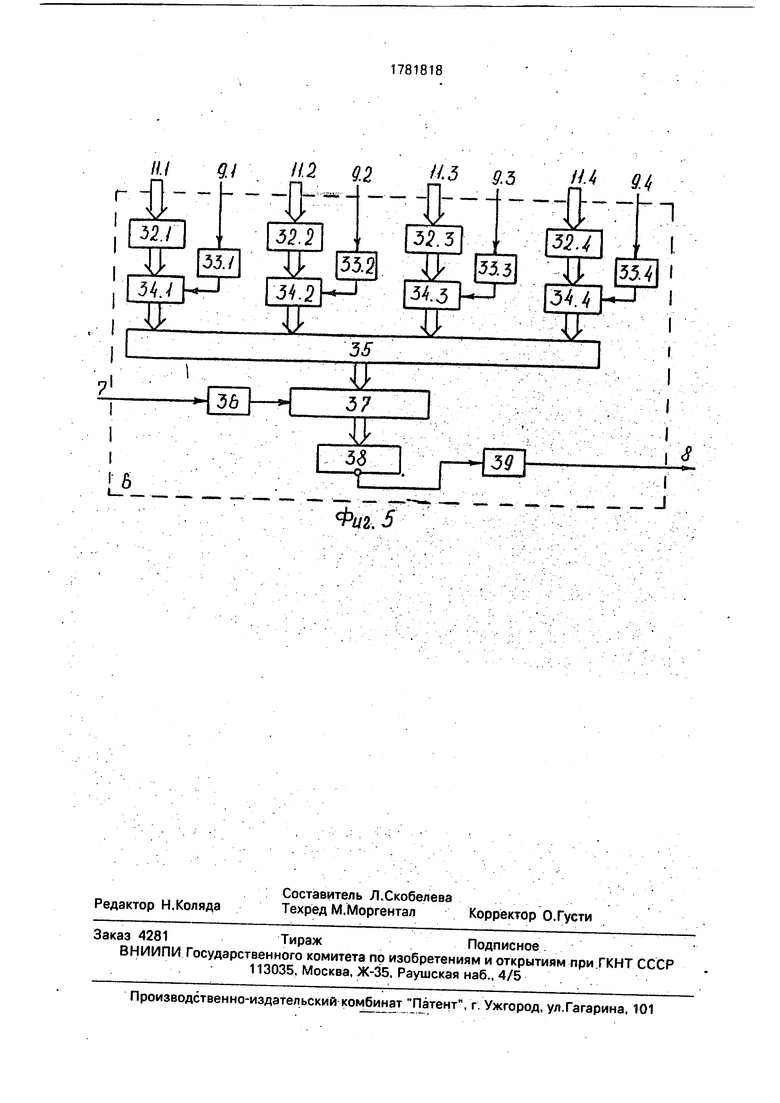

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока прямого согласования; на фиг. 3 - структурная схема матрицы загрузки и блока обратного согласования; на фиг. 4 - структурная схема матрицы прямой коммутации и матрицы обратной коммутации; на фиг. 5 - структурная схема блока управления.

Матричный коммутатор (фиг. 1) содержит блок 1 прямого согласования, матрицу 2 загрузки, блок 3 обратного согласования, матрицу прямой коммутации 4, матрицу обратной коммутации 5, блок б управления, внутренние связи 7-10, 19, группы кодовых входов устройства 11.1-11.4, группу сигнальных входов обратного канала 12, группу запросных входов квантов обработки 13, группу запросных входов сообщений 14, группу информационных входов прямого канала 15, группу информационных выходов прямого канала 16, группу информационных входов обратного канала 17, группу информационных выходов обратного канала 18.

Блок прямого согласования (фиг. 2) содержит группу триггеров 20.1-20.4, первую группу элементов И 21.1-21.4, вторую группу элементов И 22.1-22.4.

Матрица загрузки и блок обратного согласования (фиг. 3) содержат элемент ИЛИ 23, вторую группу элементов ИЛИ-НЕ 24.1- 24.2, первую группу элементов ИЛИ-НЕ 25.1-25.3, группу элементов И 26.11-26.43, группу триггеров 27.11 -27.43.

Матрица прямой коммутации (фиг. 4) содержит группу элементов ИЛИ 28.1-28.3 и группу элементов И 29.11-29.34, а матрица обратной коммутации содержит группу элементов ИЛИ 30.1-30.4 и группу элементов И 31.11-31.34.

Блок управления (фиг. 5) содержит группу регистров 32.1-32.4, группу формирующих элементов 33.1-33.4, группу групповых элементов И 34.1-34.4, групповой элемент ИЛИ 35, первый формирующий элемент 36, вычитающий счетчик 37, элемент ИЛИ-НЕ 38, второй формирующий элемент 39,

Работает матричный коммутатор следующим образом. Имеется М источников сообщений и К средств обработки сообщений, причем каждый из М источников сообщений может запросить несколько квантов обработки, то есть несколько средств обработки сообщений, С получением запроса от источника сообщений на несколько квантов обработки матричный коммутатор коммутирует источник сообщений на соответствующее требуемое число средств обработки Если число свободных средств обработки окажется меньше чем требуется, то в этом случае матричный коммутатор коммутирует оставшиеся кванты обработки на освобождающиеся средства обработки, которые

появляются после обработки квантов обработки данного или предыдущего сообщений, Коммутация осуществляется как в прямом, так и в обратном направлениях, в результате чего источник сообщений и неко0 торое число средств обработки обмениваются информацией. Каждое средство обработки выбирает только адресованную ему информацию за счет разделения каналов в источнике сообщений. Разделение ка5 налов может быть любым, например кодовым. Факт окончания обмена информацией между источником сообщений и средством обработки производится по заранее определенной кодовой комбинации, кото0 рая распознается или в источнике сообщений или в средстве обработки сообщений. В результате соответствующая коммутация разрушается и средство обработки сообщений коммутируется на новый квант обработ-.

5 ки. На фигурах представлен матричный коммутатор с числом входов К 4 и числом выходов М 3, Ио в общем случае К и М могут быть любыми целыми числами.

Перед началом работы все триггеры

0 20.1-20.4, 27.11-27.43, регистры 32.1-32.4 и счетчик 37 находятся в исходном (нулевом) состоянии. Предположим, что пришло первым сообщение от третьего источника сообщений с объемом обработки четыре кванта.

5 Этот факт отождествляется с записью кода соответствующего числу четыре в регистр 32.3, поступающему через группу кодовых входов 11.3 устройства, и появлением сигнала на входе 14.3 устройства, который про0 ходит через открытый элемент И 21.3 и переводит триггер 20.3 в единичное состояние, в результате чего элементы И 21.1,21.2, 21.3 закрываются потенциалом нулевого уровня с нулевого выхода триггера 20.3 до

5 тех пор, пока не будут поставлены на обслуживание все кванты обработки третьего источника сообщений. Потенциал единичного уровня с единичного выхода триггера 20.3 открывает элемент И 22.3 для прохождения

0 сигналов запроса квантов обработки третьего источника сообщений, если есть хотя бы одно свободное средство обработки сообщений. Этот же потенциал единичного уровня с единичного выхода триггера 20.3 по

5 связи 9.3 поступает на вход формирующего элемента 33.3, который реагирует на изменение потенциалов с нулевого уровня на единичный и в результате формирует импульс записи информации. Импульс записи информации поступает на управляющий

вход группового элемента И 34.3, в результате чего информация из регистра 32.3 проходит через групповые элементы И 34.3 и ИЛИ 35 и поступая на информационные входы счетчика 37 записывается в соответствующих разрядах счетчика 37. Таким образом, в счетчике 37 располагается код, соответствующий числу квантов обработки третьего источника сообщений.

После того, как откроется элемент И 22.3 блока 1 прямого согласования на вход 13.3 устройства поступает сигнал запроса на обработку первого кванта поступившего сообщения, который проходит через открытый элемент И 22.3 и по связи 10,3 поступает на первые входы элементов И 26.31, 26.32, 26.33 матрицы 2 загрузки. Сигнал запроса первого кванта появится только на выходе элемента И 26.31 так как остальные элементы И 26.32 и 26.33 в данный момент закрыты элементами ИЛИ-НЕ 24,1 и 24.2, Таким образом, произошла загрузка первого столбца матрицы загрузки 2. Сигнал запроса второго кванта третьего источника сообщений загрузит второй столбец матрицы загрузки 2, сигнал запроса третьего кванта загрузит третий столбец, при условии, что первый и второй столбцы не загру5- жены, и в последующем будет происходить загрузка первого слева незагруженного столбца. Сигнал с выхода элемента И 26.31 поступает на S-вход триггера 27.31 и переводит его в единичное состояние. Нулевой потенциал с нулевого выхода триггера 27.31 закрывает элемент И 26.31, а единичный потенциал с единичного выхода триггера 27.31 поступает на вход эле мента ИЛИ-НЕ 25.1. С выхода элемента ИЛИ-НЕ 25.1 нулевой потенциал закрывает все элементы И 26.11-26.41 первого столбца матрицы загрузки 2 и, инвертируясь в элементе ИЛИ- НЕ 24.1, подготавливает для загрузки следующий столбец матрииы загрузки 2. Таким образом, в каждом столбце матрицы 2 может находится не более одного триггера 27.11-27,43 в единичном состоянии.

Для устойчивой работы устройства необходимо соблюдение следующего выражения:

+ Т23 + Т25 + Т26 Т27,

где Т0 - период следования импульсов запроса квантов;

Т22 - время срабатывания элемента И 22;

Т23 - время срабатывания элемента ИЛИ 23;

Т25 - время срабатывания элемента ИЛИ-НЕ 25;

Т26 - время срабатывания элемента И 26;

Та - время Срабатывания триггера 27,

Единичные потенциалы с выходов триггеров 27.31, 27.32 и 27,33 по соответствующим связям 19.13, 19.23 и 19.33 поступают на соответствующие элементы И 31.13 и 29.13, 31.23 и 29.23, 31.33 и 29.33 и обеспечивают тем самым коммутацию входа 15.3 на выходы 16.1, 16.2, 16.3 в прямом направлении, и входов 17.1,17.2,17.3 на выход 18.3 в обратном направлении. Таким образом

0 кванты обработки третьего источника сообщений обрабатываются одновременно тремя средствами обработки. После чего начинается двусторонний обмен информацией между третьим источником сообщений

5 и тремя средствами обработки.

По окончании обработки, допустим первым средством обработки первого кванта обработки, на вход 12.1 поступает импульс, который устанавливает в нулевое состояние

0 триггер 27.11 и подтверждает нулевое состояние триггеров 27.21-27.41. После перехода триггера 27.11 в нулевое состояние на выходе элемента ИЛИ-НЕ 25 появляется потенциал единичного уровня, который прохо5 дит через элемент ИЛИ 23 и появляется на входе формирующего элемента 36 блока 6 управления. Формирующий элемент 36 при изменении потенциалов с нулевого уровня на единичный на его входе формирует им0 пульс, который поступает на вычитающий вход счетчика 37, уменьшая его содержимое на единицу. Когда содержимое счетчика 37 станет равным нулю, то есть поставлены на обработку все кванты сообщения третьего

5 источника сообщений, то и на соответствующих информационных выходах разрядов счетчика 37 будут присутствовать потенциалы нулевого уровня,следовательно на выходе элемента ИЛИ-НЕ 38 появится

0 потенциал единичного уровня, который поступает на вход формирующего элемента 39. Формирующий элемент 39 при изменении потенциалов на его входе с нулевого на единичный формирует импульс, который по

5 связи 8 поступает на нулевые входы триггеров 20.1-20.4, устанавливая в нулевое состояние триггер 20.3 и подтверждая нулевое состояние триггеров 20.1, 20.2, 20.4. После этого матричный коммутатор готов снова

0 принять на обработку сообщение любого источника сообщений, и запрос первого кванта нового сообщения будет обрабатываться первым освободившимся средством обработки. После этого весь цикл работы

5 матричного коммутатора повторяется снова.

Технико-экономический эффект от использования предлагаемого матричного коммутатора заключается в том, что ок позволяет осуществлять коммутацию любого

из своих К-входов на несколько из своих М-выходов одновременно с циркуляцией информации.

Формула изобретения 1. Матричный коммутатор, содержащий блок прямого согласования, матрицу загрузки, блок обратного согласования, матрицу прямой коммутации, матрицу обратной коммутации, причем группа запросных входов сообщений соединена соответственно с первой группой входов блока прямого согласования, первая группа выходов которого соединена соответственно с первой группой входов матрицы загрузки, вторая группа выходов которой соединена соответственно с первыми группами входов матриц прямой и обратной коммутации, первая группа выходов матрицы загрузки соединена соответственно с группой входов блока обратного согласования, группа выходов которого соединена соответственно с второй группой входов матрицы загрузки, группа сигнальных входов обратного канала соединена соответственно с третьей группой входов матрицы загрузки, выход блока обратного согласования соединен с первым входом блока прямого согласования, группа информационных входов прямого канала соединена соответственно с второй группой входов матрицы прямой коммутации, группа выходов которой соединена соответственно с группой информационных выходов прямого канала группа информационных входов обратного канала соединена соответственно с второй группой входов матрицы обратной коммутации, группа выходов которой соединена соответственно с группой информационных выходов обратного канала, причем блок прямого согласования содержит группу триггеров и первую группу элементов И, первые входы которых соединены соответ- Ьтвенно с первой группой входов, выходы элементов И первой группы элементов И соединены с S-входами соответствующих триггеров группы, инверсные выходы которых соединены с входами элементов И первой группы элементов И, соответствующих остальным триггерам группы, причем блок обратного согласования, элемент ИЛИ, первая и вторая группы элементов ИЛИ-ИЕ, входы блока обратного согласования соединены с соответствующими входами элемен- тов ИЛИ-НЕ первой группы, выходы которых соединены с входами элемента ИЛИ и входами соответствующих элементов ИЛИ-НЕ второй группы, выходы которых соединены соответственнб с выходами блока обратного согласования выход элемента ИЛИ соединен с выходом блока обратного согласования, причем матрица загрузки содержит элементы матрицы, состоящие из элемента И и триггера, третья

группа входов матрицы загрузки соединена соответственно с R-входами триггеров соответствующего столбца матрицы загрузки, инверсные выходы триггеров соединены с вторыми входами соответствующих им эле0 ментов И матрицы загрузки выходы которых соединены с S-входами соответствующих им триггеров матрицы загрузки, выходы триггеров матрицы загрузки соединены соответственно с первой и второй группами

5 выходов матрицы загрузки, входы первой группы входов матрицы загрузки соединены с первыми входами соответствующих элементов И строк матрицы загрузки, входы второй группы матрицы загрузки соедине0 ны с вторыми входами соответствующих элементов И столбцов матрицы загрузки, причем матрицы прямой и обратной коммутации содержат матрицу элементов И и группу элементов ИЛИ, выходы которых со5 единены с выходами матриц прямой и обратной коммутации, первые входы элементов И столбцов матрицы элементов И соединены с соответствующими входами второй группы входов матриц прямой и об0 ратной коммутации, выходы элементов И строки матрицы элементов И соединены с входами соответствующего элемента ИЛИ группы элементов ИЛИ, вторые входы элементов И матрицы элементов И соединены

5 с соответствующими входами первой группы входов матриц прямой и обратной коммутации, отличающийся тем, что, с целью коммутации любого входа матричного коммутатора на требуемое число его вы0 ходов с циркуляцией информации как в прямом, так и в обратном направлениях, дополнительно содержит группу элементов И и блок управления, причем вторая группа выходов блока прямого согласования соеди5 нена соответственно с группой входов блока управления, группы входов которого соединены соответственно с группами кодовых входов устройства, выход блока обратного согласования соединен с входом

0 блока управления, выход которого соединен с вторым входом блока прямого согласования, вторая группа входов которого соединена соответственно с группой запросных входов квантов обработки устройства, при5 чем вторая группа входов блока прямого согласования соединена соответственно с первыми входами элементов И второй группы блока прямого согласования, вторые входы которых соединены с первым входом блока прямого согласования, второй вход

блока прямого согласования соединен с R- входами триггеров блока прямого согласования, прямые выходы которых соединены соответственно с выходами второй группы выходов блока прямого согласования и с третьими входами одноименных элементов И второй группы блока прямого согласования, выходы которых соединены соответственно с первыми выходами блока прямого согласования.

/3.2 W.2Ш /43

Фиг. 2

формационными входами одноименных групповых элементов И, группы информационных входов которых соединены соответственно с группами входов группового элемента ИЛИ, группа выходов которого соединена с информационной группой входов реверсивного счетчика, группа информационных выходов реверсивного счетчика соединена с группой входов элемента ИЛИ-НЕ, выход которого соединен с входом второго формирующего элемента, выход которого соединен с выходом блока управления, группа входов блока управления соединена с соответствующими входами группы формирующих элементов, выходы которых соединены соответственно с управляющими входами одноименных групповых элементов И, вход блока управления соединен с входом первого формирующего элемента, выход которого соединен с вычитающим входом реверсивного счетчика.

/J.4 ПА

Фиг. 5

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Матричный коммутатор | 1989 |

|

SU1661985A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-15—Публикация

1990-10-03—Подача