Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь фазоманипулированного кода в бинарный код (см. авторское свидетельство СССР N 1774501 от 08.01.90, МКИ: Н 03 М 5/12, "Преобразователь кода", В.Л. Котляров, С.В. Мотыжев, Л.В. Ольшевская, опубл. 07.11.92, Бюл. N 41), содержащий первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого объединен с входом элемента задержки и является входом преобразователя, выход соединен с C-входом триггера, инверсный выход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым выходом преобразователя. Прямой выход триггера является вторым выходом преобразователя. Первый вход и выход мажоритарного элемента подключены, соответственно, к прямому выходу и D-входу триггера. Первый выход элемента задержки соединен со вторым входом мажоритарного элемента, второй выход - со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и третьим входом мажоритарного элемента.

Недостатком известного преобразователя кода является низкая помехоустойчивость, обусловленная пропусканием на информационный выход входного сигнала логического "0" или логической "1" с любой длительностью не менее заданной величины и пропусканием на тактовый выход любых входных сигналов, просуммированных с выходными информационными, что существенно затрудняет выделение полезной информации из потока входных сигналов потребителем информации.

Известен преобразователь фазоманипулированного кода в бинарный код (см. авторское свидетельство СССР N 1383510 от 30.10.86, МКИ: H 03 М 13/00, "Устройство для декодирования манчестерского кода", Г.И. Готлиб, В.Я.Загурский, опубл. 23.03.88, Бюл. N 11), содержащий селектор, для выделения преамбулы, состоящий из блока сравнения, триггера и элемента ИЛИ-НЕ, блок дифференцирования, вход которого служит информационным входом устройства, элемент задержки, синхронизатор, делитель частоты, регистр. Выход триггера соединен с первым входом элемента ИЛИ-НЕ и является первым выходом устройства. Выход блока дифференцирования соединен через синхронизатор с тактовыми входами делителя частоты и регистра. Выход делителя частоты соединен с управляющим (тактовым) входом регистра и является вторым (тактовым) выходом устройства. Вход элемента задержки подключен к информационному входу устройства. Выход элемента задержки соединен с информационным входом регистра. Выход нулевого разряда регистра соединен с первым входом блока сравнения, вторым входом элемента ИЛИ-НЕ и является третьим (информационным) выходом устройства, выходы остальных разрядов регистра соединены с соответствующими вторыми входами блока сравнения, выход которого соединен с входом установки в "1" триггера и третьим входом элемента ИЛИ-НЕ. Вход установки в "0" триггера является входом "Сброс" устройства. Выход элемента ИЛИ-НЕ (выход селектора) соединен с управляющим входом (R-входом) делителя частоты.

Синхронизатор содержит элемент ИЛИ-НЕ и элемент задержки, включенный между выходом элемента ИЛИ-НЕ и его первым входом. Второй вход элемента ИЛИ-НЕ является входом синхронизатора, а выход - выходом синхронизатора.

Блок сравнения предназначен для выделения синхросигнала (преамбулы) информационной посылки и содержит сумматоры по модулю два (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ), число N которых на единицу больше числа разрядов синхросигнала, и многовходовый элемент ИЛИ.

Одним из недостатков преобразователя является низкая помехоустойчивость, поскольку в режиме ожидания информационной посылки на тактовом выходе постоянно присутствуют импульсы, синхронизируемые входными сигналами, и входные сигналы непрерывно преобразуются и поступают на информационный выход. Ситуация усугубляется тем, что в предложенной схеме синхронизатора короткие импульсы помехи, поступающие на его вход через блок дифференцирования, в любой момент времени могут вызвать раздвоение выходного импульса положительной полярности, а следовательно, повышение частоты выходных импульсов и нарушение работоспособности преобразователя.

Другим недостатком известного преобразователя является низкая надежность функционирования, связанная с использованием аналоговой схемы синхронизатора, обладающего низкой точностью и стабильностью формирования временных интервалов и определяющего возможность нарушения работоспособности преобразователя. Ситуация, как и в случае воздействия помех, усугубляется возможностью раздвоения положительного выходного импульса синхронизатора, если его длительность станет больше длительности выходного импульса блока дифференцирования. К снижению надежности приводит также возможность нарушения работоспособности преобразователя в случае реализации схемы на быстродействующих элементах в связи с тем, что импульс на выходе элемента ИЛИ-НЕ может оказаться недостаточной длительности для управления делителем.

К недостаткам известного преобразователя можно отнести также схемные ограничения на выбор формы преамбулы в связи с неопределенностью фазы выходных сигналов делителя частоты в момент ее начала. Предложенная форма является практически единственной возможной.

Необходимо отметить, что предложенная схема синхронизатора исключает возможность использования простейших элементов задержки в виде интегрирующих RC-цепей, требуя применения линий задержки или устройств задержки, построенных по принципу счета числа импульсов.

Задачей, решаемой предлагаемым техническим решением, является создание преобразователя фазоманипулированного кода в бинарный код, обладающего более высокими помехоустойчивостью и надежностью функционирования.

Технический результат, заключающийся в повышении помехоустойчивости и надежности функционирования, достигается тем, что в преобразователь фазоманипулированного кода в бинарный код, содержащий блок дифференцирования, первый выход которого соединен с первым входом синхронизатора, выход которого соединен с тактовым входом делителя частоты, R-вход которого соединен с выходом селектора, а выход является тактовым выходом преобразователя и соединен с тактовым входом регистра, выход которого является информационным выходом преобразователя, информационный вход блока дифференцирования является информационным входом преобразователя, введен генератор импульсов, в блок дифференцирования введены тактовый вход, второй и третий выходы, в синхронизатор введены второй и третий входы, блок дифференцирования состоит из сдвигающего регистра и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым выходом блока дифференцирования, а первый и второй входы - с соответствующими выходами сдвигающего регистра, D-вход и C-вход которого соединены, соответственно, с информационным и тактовым входами блока дифференцирования, второй и третий выходы которого соединены, соответственно, с первым и вторым выходами его сдвигающего регистра, информационный вход регистра соединен с третьим выходом блока дифференцирования, второй выход которого соединен с информационным входом селектора, выход которого соединен с третьим входом синхронизатора и R-входом регистра, выход генератора импульсов соединен с тактовыми входами блока дифференцирования и селектора и со вторым входом синхронизатора, вход "Сброс" селектора является входом "Сброс" преобразователя. Кроме того, селектор содержит первый, второй, третий, четвертый и пятый элементы ИЛИ-НЕ, первый, второй и третий элементы И-НЕ, инвертор, первый и второй счетчики, интегрирующую RC-цепь, причем первые входы первого элемента ИЛИ-НЕ и первого элемента И-НЕ соединены через интегрирующую RC-цепь с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход - с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ, а выход - с первым входом второго элемента И-НЕ, выход которого соединен с R-входом первого счетчика, C-вход которого соединен с выходом четвертого элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого счетчика, вторым входом первого элемента ИЛИ-НЕ и с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход - с R-входом второго счетчика, C-вход которого соединен с выходом пятого элемента ИЛИ-НЕ, первый вход которого соединен с выходом второго счетчика и с входом инвертора, выход которого соединен со вторым входом первого элемента И-НЕ и с выходом селектора, первые входы первого элемента ИЛИ-НЕ и первого элемента И-НЕ соединены с информационным входом селектора, вторые входы четвертого и пятого элементов ИЛИ-НЕ соединены с тактовым входом селектора, второй вход второго элемента И-НЕ соединен с входом "Сброс" селектора. Кроме того, синхронизатор содержит счетчик и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются, соответственно, первым и третьим входом синхронизатора, а выход соединен с R-входом счетчика, C-вход и выход которого является, соответственно, вторым входом и выходом синхронизатора. Кроме того, преобразователь содержит счетчик символов, C-вход которого соединен с выходом делителя частоты, R-вход - с выходом селектора, а выход - с входом "Сброс" преобразователя.

Указанная совокупность признаков позволяет повысить помехоустойчивость преобразователя путем:

- разрешения формирования сигналов на тактовом и информационном выходах только после опознания синхросигнала на время приема информационной посылки;

- построения схемы синхронизатора, исключающей раздвоение выходных сигналов;

- жесткой привязки входных сигналов к внутренней временной шкале, практически исключающей влияние коротких импульсных помех на функционирование преобразователя.

Одновременно повышается надежность функционирования преобразователя путем:

- построения преобразователя с использованием только цифровых устройств, обеспечивающих высокую стабильность параметров в диапазоне температур, с жесткой синхронизацией их работы, исключающей несоответствие импульсов друг другу по длительности и влияние задержек сигналов в элементах и цепях на функционирование устройства;

- построения синхронизатора на основе счетчика импульсов с возможностью синхронизации его работы внешними информационными сигналами.

В предложенной схеме преобразователя может использоваться любая необходимая форма синхросигнала, не только цифровая, но и аналоговая с фиксированной длительностью импульса и паузы, не кратной целому числу периодов тактовых импульсов, наиболее предпочтительная для конкретных условий эксплуатации с учетом помеховой обстановки, при соответствующей реализации схемы селектора. В данном варианте преобразователя синхросигнал имеет длительность в три промежутка времени передачи одного двоичного разряда, в первой половине синхросигнала передается уровень логической "1", во второй - уровень логического "0" (указанный синхросигнал отличается по структуре от фазоманипулированного кода отсутствием обязательных перепадов в первом и третьем тактах).

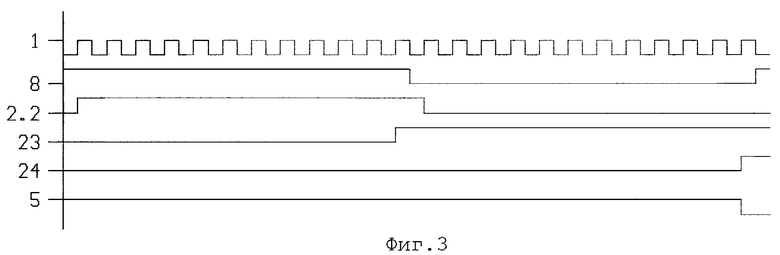

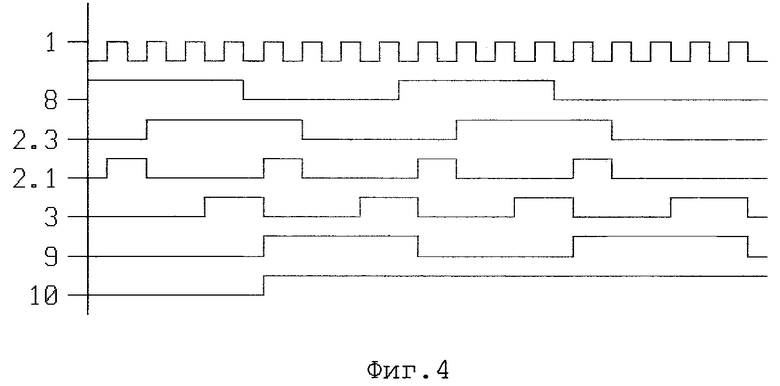

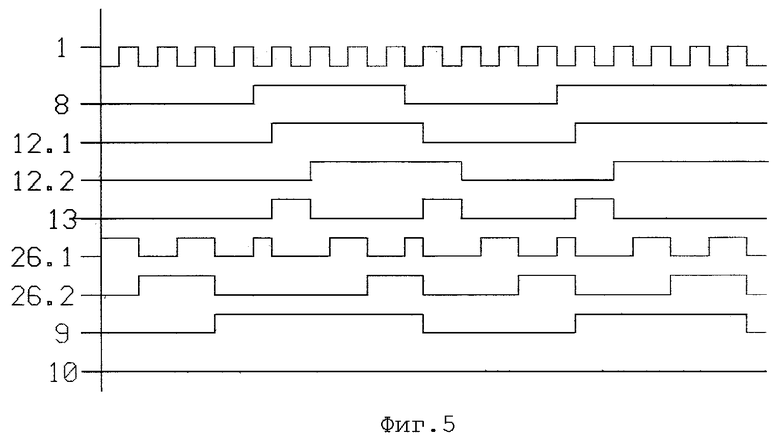

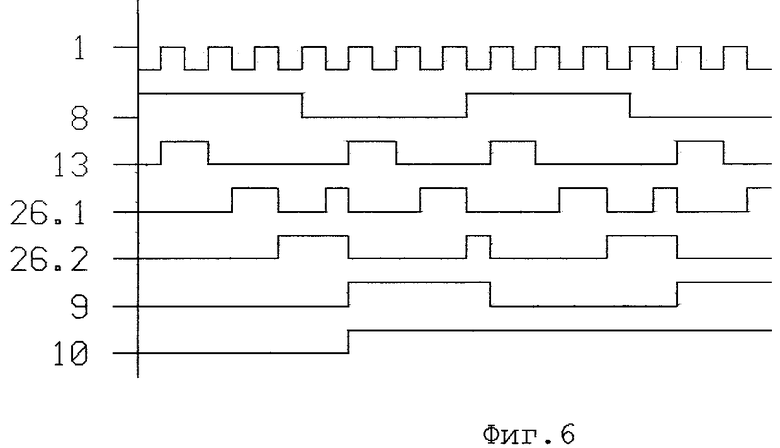

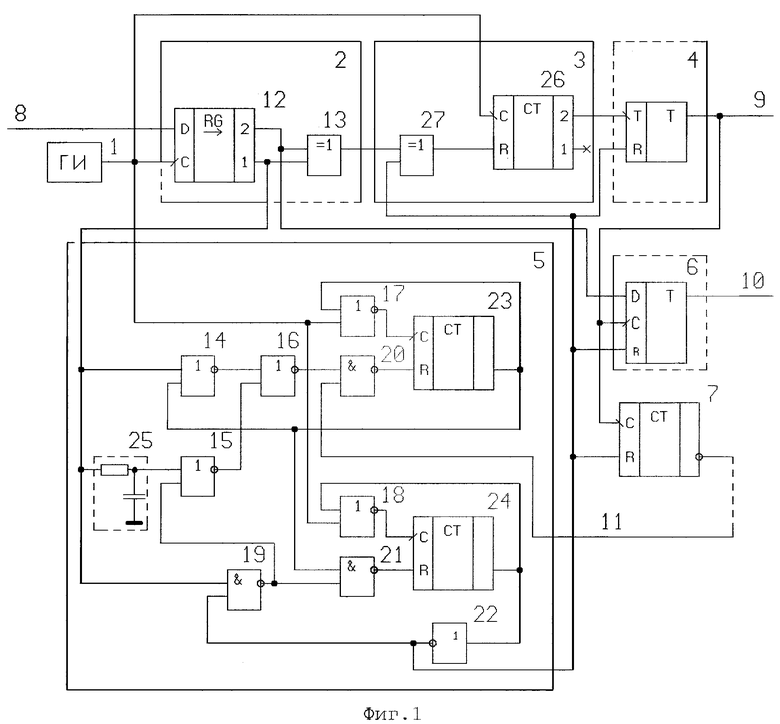

На фиг. 1 приведена принципиальная электрическая схема преобразователя, на фиг. 2 - вид синхросигнала, на фиг. 3 - диаграммы работы преобразователя в режиме приема синхросигнала, на фиг. 4 - диаграммы работы преобразователя в режиме преобразования логической "1", на фиг. 5 - диаграммы работы преобразователя в режиме преобразования логического "0", на фиг. 6 - диаграммы работы преобразователя при уменьшении временного интервала между перепадами входного сигнала, на фиг. 7 - диаграммы работы преобразователя при увеличении временного интервала между перепадами входного сигнала.

Преобразователь содержит (см. фиг. 1) генератор 1 импульсов, блок 2 дифференцирования, синхронизатор 3, делитель 4 частоты, селектор 5, регистр 6, счетчик 7 символов, информационный вход 8, тактовый выход 9, информационный выход 10 и вход 11 "Сброс".

Первый выход блока 2 дифференцирования соединен с первым входом синхронизатора 3, выход которого соединен с тактовым входом делителя 4 частоты. R-вход делителя 4 частоты соединен с выходом селектора 5, а выход является тактовым выходом 9 и соединен с тактовым входом регистра 6. Выход регистра 6 является информационным выходом 10. Информационный вход блока 2 дифференцирования является информационным входом 8.

Блок 2 дифференцирования состоит из сдвигающего регистра 12 и элемента 13 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым выходом блока 2 дифференцирования, а первый и второй входы - с соответствующими выходами его сдвигающего регистра 12. D-вход и C-вход сдвигающего регистра 12 соединены соответственно с информационным и тактовым входами блока 2 дифференцирования. Второй и третий выходы блока 2 дифференцирования соединены соответственно с первым и вторым выходами его сдвигающего регистра 12. Информационный вход регистра 6 соединен с третьим выходом блока 2 дифференцирования, второй выход которого соединен с информационным входом селектора 5, выход которого соединен с третьим входом синхронизатора 3 и R-входом регистра 6. Выход генератора 1 импульсов соединен с тактовыми входами блока 2 дифференцирования и селектора 5, а также со вторым входом синхронизатора 3. Вход "Сброс" селектора 5 является входом 11 "Сброс".

Селектор 5 содержит первый 14, второй 15, третий 16, четвертый 17 и пятый 18 элементы ИЛИ-НЕ, первый 19, второй 20 и третий 21 элементы И-НЕ, инвертор 22, первый 23 и второй 24 счетчики, интегрирующую RC-цепь 25. Первые входы элемента 14 ИЛИ-НЕ и элемента 19 И-НЕ соединены через интегрирующую RC-цепь 25 с первым входом элемента 15 ИЛИ-НЕ, второй вход которого соединен с выходом элемента 19 И-НЕ, а выход - с первым входом элемента 16 ИЛИ-НЕ. Второй вход элемента 16 ИЛИ-НЕ соединен с выходом элемента 14 ИЛИ-НЕ, а выход - с первым входом элемента 20 И-НЕ, выход которого соединен с R-входом счетчика 23. C-вход счетчика 23 соединен с выходом элемента 17 ИЛИ-НЕ, первый вход которого соединен с выходом счетчика 23, вторым входом элемента 14 ИЛИ-НЕ и с первым входом элемента 21 И-НЕ. Второй вход элемента 21 И-НЕ соединен с выходом элемента 19 И-НЕ, а выход с R-входом счетчика 24, C-вход которого соединен с выходом элемента 18 ИЛИ-НЕ. Первый вход элемента 18 ИЛИ-НЕ соединен с выходом счетчика 24 и с входом инвертора 22, выход которого соединен со вторым входом элемента 19 И-НЕ и с выходом селектора 5. Первые входы элемента 14 ИЛИ-НЕ и элемента 19 И-НЕ соединены с информационным входом селектора 5. Вторые входы четвертого 17 и пятого 18 элементов ИЛИ-НЕ соединены с тактовым входом селектора 5. Второй вход элемента 20 И-НЕ соединен с входом "Сброс" селектора 5.

Синхронизатор 3 содержит счетчик 26 и элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются, соответственно, первым и третьим входами синхронизатора 3, а выход соединен с R-входом счетчика 26, C-вход и выход которого являются, соответственно, вторым входом и выходом синхронизатора 3.

C-вход счетчика 7 символов соединен с выходом делителя 4 частоты, R-вход - с выходом селектора 5, а выход - с входом 11 "Сброс".

Генератор 1 импульсов может быть реализован по схеме кварцевого генератора (см. Потемкин И.С. "Функциональные узлы цифровой автоматики", М.: Энергоатомиздат, 1988, с. 240, рис. 7.9). Частота работы генератора 1 импульсов должна превышать частоту передачи информационных разрядов. В данном варианте преобразователя частота работы генератора 1 импульсов в 8 раз превышает частоту передачи информационных разрядов.

В качестве делителя 4 частоты используется счетный триггер и может быть реализован по схеме счетчика с непосредственной связью (см. Потемкин И.С. "Функциональные узлы цифровой автоматики", М.: Энергоатомиздат, 1988, с.254, рис. 9.2).

В качестве регистра 6 используется D-триггер и может быть реализован по схеме сдвигающего регистра (см. Потемкин И. С. "Функциональные узлы цифровой автоматики", М.: Энергоатомиздат, 1988, с. 277, рис.10.1).

Преобразователь работает следующим образом.

При подаче логического "0" на вход 11 "Сброс" преобразователь устанавливается в исходное состояние. В исходном состоянии на информационном входе 8 - уровень логического "0". На первом, втором и третьем выходах блока 2 дифференцирования - уровни логического "0". На выходе селектора 5 - уровень логической "1", который удерживает в нулевом состоянии синхронизатор 3, делитель 4 частоты, регистр 6 и счетчик 7 символов. На тактовом выходе 9, а также на информационном выходе 10 - уровни логического "0".

Информация поступает на вход преобразователя в виде слов. Каждое слово начинается с сигнала пословной синхронизации (синхросигнала), за которым следуют информационные разряды. Синхросигнал имеет длительность, равную трем промежуткам времени передачи одного двоичного разряда, в первой половине синхросигнала передается уровень логической "1", во второй - уровень логического "0". Вид синхросигнала приведен на фиг. 2, где B - первый информационный разряд, T - время передачи одного двоичного разряда.

При поступлении слова на информационный вход 8 (фиг. 3, поз. 8) по фронту импульса генератора 1 импульсов (фиг. 3, поз. 1) на втором выходе блока 2 дифференцирования (фиг. 3, поз. 2.2) устанавливается логическая "1", которая поступает на вход интегрирующей RC-цепи 25, а также на первые входы элемента 14 ИЛИ-НЕ и элемента 19 И-НЕ, на выходе которых устанавливается логический "0". На выходе элемента 15 ИЛИ-НЕ устанавливается логическая "1". Элемент 16 ИЛИ-НЕ остается в нулевом состоянии. Через время задержки интегрирующей RC-цепи 25 на выходе элемента 15 ИЛИ-НЕ устанавливается логический "0". Элемент 16 ИЛИ-НЕ устанавливается в единичное состояние, на выходе элемента 20 И-НЕ формируется логический "0", который снимает удерживающий в нулевом состоянии потенциал с R-входа счетчика 23, разрешая его работу. Далее по фронтам импульсов генератора 1 импульсов счетчик 23 осуществляет счет импульсов и, отсчитав 11 импульсов, устанавливает на своем выходе логическую "1" (фиг. 3, поз. 23).

Если на информационный вход 8 поступает неверный синхросигнал (либо наводка, помеха) и перепад уровня синхросигнала происходит ранее начала формирования фронта последнего (одиннадцатого) импульса генератора 1, то по фронту импульса генератора 1 на втором выходе блока 2 дифференцирования установится логический "0", который через элементы 14 и 16 ИЛИ-НЕ, дважды проинвертировавшись, поступит на первый вход элемента 20 И-НЕ. На выходе элемента 20 И-НЕ установится логическая "1", которая сбросит в нулевое состояние счетчик 23. В этом случае селектор 5 синхросигнал не выделит, а установится в исходное состояние - состояние готовности к приему синхросигнала.

Логическая "1", установленная на выходе счетчика 23 при правильном синхросигнале, поступает на первый вход элемента 17 ИЛИ-НЕ, устанавливая его в нулевое состояние и запрещая, таким образом, дальнейшее прохождение счетных импульсов на C-вход счетчика 23, на второй вход элемента 14 ИЛИ-НЕ, блокируя сброс счетчика 23 обязательным отрицательным перепадом уровня синхросигнала, и на первый вход элемента 21 И-НЕ. После прихода отрицательного перепада синхросигнала по фронту импульса генератора 1 импульсов на втором выходе блока 2 дифференцирования устанавливается логический "0", который поступает на вход интегрирующей RC-цепи 25, а также на первые входы элемента 14 ИЛИ-НЕ и элемента 19 И-НЕ. На выходе элемента 19 И-НЕ устанавливается логическая "1", которая поступает на вторые входы элементов 15 ИЛИ-НЕ и 21 И-НЕ, устанавливая на выходе последнего логический "0", который снимает удерживающий в нулевом состоянии потенциал с R-входа счетчика 24, разрешая его работу. Через время задержки интегрирующей RC-цепи 25 на первом входе элемента 15 ИЛИ-НЕ устанавливается логический "0", который не изменяет его состояния. Далее по срезам импульсов генератора 1 импульсов счетчик 24 осуществляет счет импульсов и, отсчитав 11 импульсов, устанавливает на своем выходе логическую "1" (фиг. 3, поз. 24).

Если на информационный вход 8 поступает неверный синхросигнал (либо наводка, помеха) и перепад уровня синхросигнала происходит ранее начала формирования фронта последнего (одиннадцатого) импульса генератора 1, то по фронту импульса генератора 1 на втором выходе блока 2 дифференцирования установится логическая "1", которая через элементы 19 и 21 И-НЕ, дважды проинвертировавшись, поступит на R-вход счетчика 24 и сбросит его в нулевое состояние. Логический "0" с выхода элемента 19 И-НЕ поступит на второй вход элемента 15 ИЛИ-НЕ, на первый вход которого логическая "1" придет с некоторой задержкой за счет действия интегрирующей RC-цепи 25. В результате на выходе элемента 15 ИЛИ-НЕ сформируется единичный импульс, который через элемент 16 ИЛИ-НЕ и элемент 20 И-НЕ, дважды проинвертировавшись, поступит на R-вход счетчика 23 и сбросит его в нулевое состояние. В этом случае селектор 5 синхросигнал не выделит, а установится в исходное состояние - состояние готовности к приему синхросигнала.

Логическая "1", установленная на выходе счетчика 24 при нормальном синхросигнале, поступает на первый вход элемента 18 ИЛИ-НЕ, устанавливая его в нулевое состояние и запрещая, таким образом, дальнейшее прохождение счетных импульсов на C-вход счетчика 24 и на вход элемента 22 НЕ. На выходе элемента 22 НЕ устанавливается логический "0", который, поступая на второй вход элемента 19 И-НЕ, блокирует сброс счетчика 24 положительным перепадом уровня на информационном входе 8. На выходе элемента 19 И-НЕ устанавливается логическая "1", которая, поступая на второй вход элемента 15 ИЛИ-НЕ, удерживает его в нулевом состоянии, предотвращая переключение за счет задержки интегрирующей RC-цепи 25. На выходе селектора 5 (фиг. 3, поз. 5) устанавливается логический "0", который снимает удерживающий в нулевом состоянии потенциал с синхронизатора 3, делителя 4 частоты, регистра б и счетчика 7 символов. Преобразователь готов к приему и преобразованию информационного блока.

Следует отметить, что после прихода положительного и отрицательного перепадов синхросигнала по фронту импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логическая "1", на выходе элемента 27 ИСКЛЮЧАЮЩЕЕ ИЛИ установится логический "0", который снимет удерживающий в нулевом состоянии потенциал с R-входа счетчика 26, разрешая его работу, а по срезу этого импульса происходит переключение счетчика 26 (на его выходе 1 устанавливается логическая "1"). Далее, по фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логический "0", на выходе элемента 27 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается логическая "1", которая сбрасывает счетчик 26 в нулевое состояние. Рассмотренные процессы не изменяют состояние логического "0" на выходе синхронизатора 3.

Преобразование логической "1" в фазоманипулированном коде выполняется следующим образом.

После прихода на информационный вход 8 (фиг. 4, поз. 8) логической "1" в фазоманипулированном коде по фронту импульса генератора 1 импульсов (фиг. 4, поз. 1) на первом выходе блока 2 дифференцирования (фиг. 4, поз.2.1) устанавливается логическая "1", которая через элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на R-вход счетчика 26 и устанавливает последний в нулевое состояние. По фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логический "0", который через элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ снимает удерживающий в нулевом состоянии потенциал с R-входа счетчика 26, а по его срезу и срезам двух последующих импульсов происходит переключение счетчика 26. Таким образом, на выходах 1 и 2 последнего устанавливается логическая "1". Далее, по фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логическая "1", которая сбрасывает синхронизатор 3 (фиг. 4, поз. 3) в нулевое состояние. На выходе синхронизатора 3 формируется отрицательный перепад, который переключает делитель 4 частоты в единичное состояние. На тактовом выходе 9 преобразователя (фиг. 4, поз. 9) устанавливается логическая "1". Регистр 6 по сформированному фронту импульса на тактовом входе записывает логическую "1", которая установлена на третьем выходе блока 2 дифференцирования (фиг. 4, поз. 2.3), на свой выход и, соответственно, на информационный выход 10 (фиг. 4, поз.10). По фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логический "0", который через элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ снимает удерживающий в нулевом состоянии потенциал с R-входа счетчика 26, а по его срезу и срезам двух последующих импульсов происходит переключение счетчика 26. Таким образом, на выходах 1 и 2 последнего устанавливается логическая "1". Далее, по фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логическая "1", которая сбрасывает синхронизатор 3 в нулевое состояние. На выходе синхронизатора 3 формируется отрицательный перепад, который переключает делитель 4 частоты в нулевое состояние. На тактовом выходе 9 преобразователя устанавливается логический "0". Происходит переключение счетчика 7 символов по сформированному срезу импульса на его C-входе.

Преобразование логического "0" в фазоманипулированном коде выполняется следующим образом.

С приходом на информационный вход 8 (фиг. 5, поз.8) логического "0" в фазоманипулированном коде по срезам первых трех импульсов генератора 1 импульсов (фиг. 5, поз.1) происходит переключение счетчика 26. Таким образом, на выходах 1 и 2 последнего устанавливается логическая "1". Далее, по срезу следующего импульса генератора 1 импульсов происходит переключение счетчика 26 в нулевое состояние. На выходе синхронизатора 3 (фиг. 5, поз. 3) формируется отрицательный перепад, который переключает делитель 4 частоты в единичное состояние. На тактовом выходе 9 (фиг. 5, поз. 9) устанавливается логическая "1". Регистр 6 по сформированному фронту импульса на его тактовом входе записывает логический "0", который установлен на третьем выходе блока 2 дифференцирования (фиг. 5, поз. 2.3), на свой выход и, соответственно, на информационный выход 10 (фиг. 5, поз. 10). По срезу следующего импульса генератора 1 импульсов происходит переключение счетчика 26 (на его выходе 1 устанавливается логическая "1"). Фронтом последующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования (фиг. 5, поз. 2.1) устанавливается логическая "1", которая сбрасывает синхронизатор 3 в нулевое состояние. По фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логический "0", который через элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ снимает удерживающий в нулевом состоянии потенциал с R-входа счетчика 26, а по его срезу и срезам двух последующих импульсов происходит переключение счетчика 26. Таким образом, на выходах 1 и 2 последнего устанавливается логическая "1". Далее по фронту следующего импульса генератора 1 импульсов на первом выходе блока 2 дифференцирования устанавливается логическая "1", которая сбрасывает синхронизатор 3 в нулевое состояние. На выходе синхронизатора 3 формируется отрицательный перепад, который переключает делитель 4 частоты в нулевое состояние. На тактовом выходе 9 устанавливается логический "0". Происходит переключение счетчика 7 символов по сформированному срезу импульса на его C-входе.

Таким образом, на тактовом выходе 9 формируются тактовые импульсы, а на информационном выходе 10 - декодированный сигнал в бинарном коде. По срезам импульсов, формирующихся на выходе делителя 4 частоты, происходит переключение счетчика 7 символов. После преобразования всего информационного блока на выходе счетчика 7 символов устанавливается логический "0", который поступает на вход "Сброс" селектора (вход 11 "Сброс" преобразователя) и устанавливает преобразователь в исходное состояние - состояние готовности приема следующего слова.

Преобразователь выполняет безошибочное декодирование входного сигнала в диапазоне флуктуаций (фазовой дрожи) перепадов входного сигнала. Допуск на флуктуацию составляет ± (1/8) периода следования битов (или ± 1 период импульсов генератора 1 импульсов).

В частности, при уменьшении временного интервала между перепадами входного сигнала (фиг. 6, поз. 8) формирование отрицательных перепадов на выходе синхронизатора 3 (фиг. 6, поз. 3), необходимых для переключения делителя 4 частоты (фиг. 6, поз. 4), осуществляется за счет сброса синхронизатора 3 в нулевое состояние уровнями логической "1" на первом выходе блока 2 дифференцирования (фиг. 6, поз. 2) после прихода перепада логического уровня входного сигнала.

При увеличении временного интервала между перепадами входного сигнала (фиг. 7, поз. 8) формирование отрицательных перепадов на выходе синхронизатора 3 (фиг. 7, поз. 3), необходимых для переключения делителя 4 частоты (фиг. 7, поз. 4), осуществляется как за счет сброса синхронизатора 3 в нулевое состояние уровнями логической "1" на первом выходе блока 2 дифференцирования (фиг. 7, поз. 2) после прихода перепада логического уровня входного сигнала, так и за счет нормального счета импульсов генератора 1 импульсов (фиг. 7, поз. 1) счетчиком 26 и установки его и, соответственно, синхронизатора 3 в нулевое состояние при отсчете четырех импульсов.

Таким образом, описание работы подтверждает работоспособность заявляемого преобразователя.

Изготовлен лабораторный макет преобразователя фазоманипулированного кода в бинарный код, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| РЕЛЕ ВРЕМЕНИ | 1997 |

|

RU2119245C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Достигаемый технический результат - повышение помехоустойчивости и надежности функционирования. Преобразователь содержит блок дифференцирования, синхронизатор, делитель частоты, селектор и генератор импульсов. Преобразователь выполняет безошибочное декодирование входного сигнала в диапазоне флуктуаций входного сигнала. Допуск на флуктуацию составляет + 1/8 периода следования битов. 2 з.п. ф-лы, 7 ил.

| Устройство для декодирования манчестерского кода | 1986 |

|

SU1383510A1 |

| ДАТЧИК ЭЛЕКТРОМАГНИТНОГО РАСХОДОМЕРА | 0 |

|

SU187342A1 |

| Преобразователь кода | 1990 |

|

SU1774501A1 |

| Огнетушитель | 0 |

|

SU91A1 |

| Экономайзер | 0 |

|

SU94A1 |

| Способ определения места замыкания жилы в кабельной линии | 1977 |

|

SU750398A1 |

Авторы

Даты

2001-02-20—Публикация

1999-06-22—Подача