Изобретение относится в общем случае к передатчикам, приемникам, системам и способам с упреждающим исправлением ошибок, использующим пунктированное сверточное кодирование и декодирование, конкретнее, к таким передатчикам, приемникам, системам и способам, в которых последовательный поток бит передатчика и/или приемника разделяется на два потока бит. Информационные сигналы упреждающего исправления ошибки, имеющие пунктированные коды 2/3 или 6/7, посылаются в разные моменты времени геосинхронным спутником на первом и втором энергетических уровнях соответственно на наземный принимающий объект, содержащий антенну со сферическим зеркалом с диаметром не более 1 м.

В передатчике со сверточным кодированием и упреждающим исправлением ошибок двоичный поток бит разделяется на первый и второй потоки бит соответственно, включая последовательные биты P1(0), P1(1), P1(2), P1(3), P1(4) т.д. и P2(0), P2(1), P2(2), P2(3), P2(4) и т.д. При сверточном кодировании с половинной скоростью первый и второй поток бит формируются путем объединения смежных битов в первоначальный поток бит в соответствии с функцией по модулю 2 путем использования одноразрядных сумматоров с двумя входами (сумматоров по модулю 2), реагирующих на смежные биты.

Благодаря этой избыточности в первом и втором потоке бит появляется возможность удалить некоторые биты из этих потоков бит без значительной потери информации. Такое удаление бит из первого и второго потока бит называется пунктированием. Оптимальные коды пунктурирования для этих потоков бит описываются Ясудой и др. в статье "Разработка декодера Viterbie переменной скоростью и его рабочие характеристики", 6-я Международная конференция по цифровой спутниковой связи, Феникс, Аризона, 1983, сентябрь. Здесь описывают оптимальные скорости пунктурирования от 2/3 до 16/17. Код или скорость пунктурирования 2/3 представляется следующим образом (табл. 1).

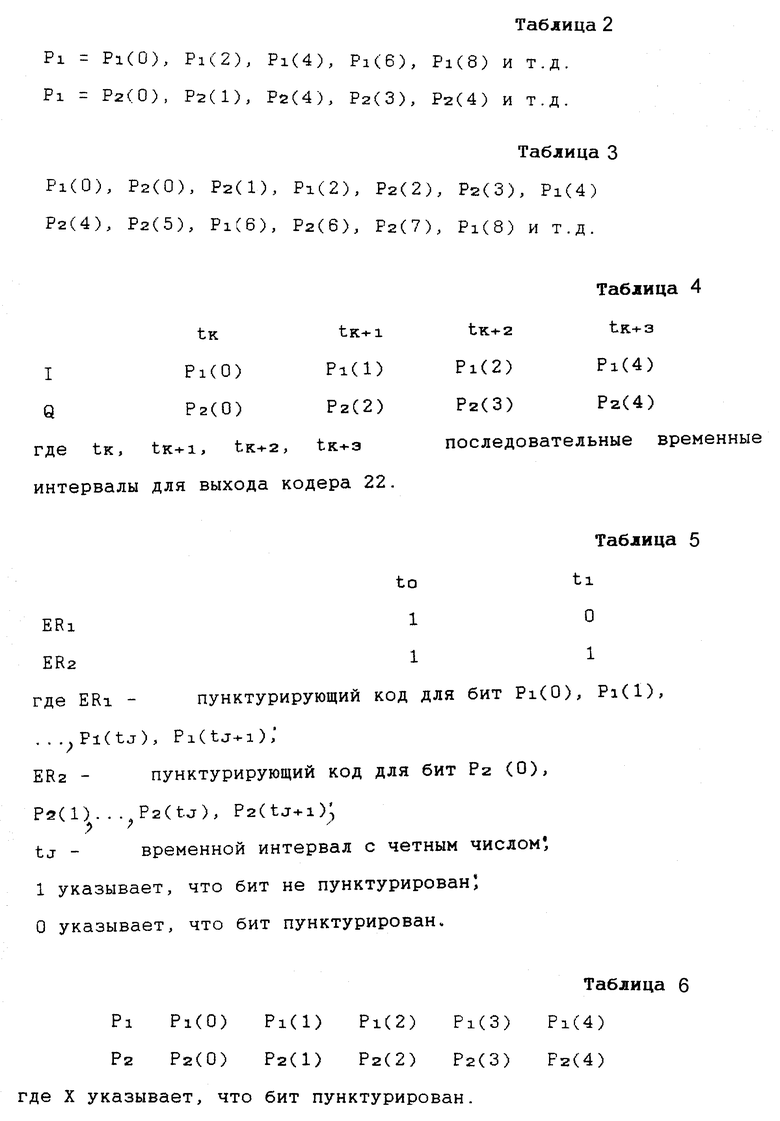

Строки 1 и 2 табл. 1 соответственно указывают операции пунктурирования, производимые над битами первого и второго потока бит. Первое место в строке 1 указывает операции пунктурирования, которые нужно произвести над битами P1(0), P1(2), P1(4) и т.д. первого потока бит; второе место в строке 1 указывает операции пунктурирования, производимые над битами P1(1), P1(3), P1(5) и т. д. первого потока бит; первое место в строке 2 табл. 1 указывает операции пунктурирования, производимые над битами P2(0), P2(2), P2(4) и т.д. второго потока бит; второе место в строке 2 указывает операции над битами P2(1), P2(3), P2(5) и т.д. Значения 1 или 2 в табл. 1 соответственно указывают на то, что пунктурирования нет и что пунктурирование есть. Код пунктурирования табл. 1 прилагается к первому и второму потоку бит для создания пунктурированных потоков бит (табл. 2).

Таким образом, биты P1(1), P1(3), P1(5), P1(7) и т.д. были удалены, т.е. пунктурированы из второго потока бит. Ясуда и др. указывают, что потоки бит на табл. 2 могут быть объединены в один последовательный поток бит с помощью регистра обратного магазинного типа ("первым пришел - первым обслужен") так, что выход первого в первом выходном регистре выглядит следующим образом (табл. 3).

Сформированный таким образом последовательный поток бит подается в модулятор. Предполагается, что последовательный поток бит, поданный на модулятор, - это реплика выхода регистра обратного магазинного типа, заставляющая модулятор выдавать сигнал сдвига кода с двойной частотой или сигнал сдвига кода с двойной фазой. Однако большинство систем спутниковой связи, работающих на двоичных данных, используют два ортогональных канала, которые специалисты обычно называют каналами I и Q. Ясуда и др. полностью умалчивают о том, как последовательный сигнал, полученный из регистра обратного магазинного типа, можно разделить на каналы I и Q. Более того, Ясуда и др. не описывают никакого приемного устройства для пунктурированного сверточного кодированного сигнала.

Известна разработанная ранее двухканальная (I и Q) система, использующая метод сверточного пунктурирования с упреждающим исправлением ошибок для обработки только двух конкретных пунктурированных кодов, а именно 3/4 и 7/8. В этих предыдущих системах сигналы, кодированные методом свертки, пунктурируются непосредственно, т.е. не образуется последовательного потока бит, как описано Ясудой и др. Поэтому разработанная ранее двухканальная приемно-передаточная система ориентирована только на два пунктурированных кода и не может быть использована для всех оптимальных скоростей или кодов с пунктурированием, описанных Ясудой и др.

Соответственно цель изобретения - создание нового и улучшенного способа, а также передатчика и приемника, способных обрабатывать все оптимальные пунктурированные коды.

В ближайшем будущем будет создана система, в которой цифровые кодированные информационные сигналы (в частности телевизионные программы) будут передаваться с наземного объекта через геосинхронный спутник на принимающий объект, имеющий антенну со сферическими зеркалами диаметром не более 1 м, которая передает сигнал на домашние телевизоры. Сейчас предусматриваются две системы, соответственно использующие сферические зеркала наземной принимающей антенны с диаметром приблизительно 60 и 90 см.

При использовании системы со сферическим зеркалом 60 см нужно, чтобы геосинхронный спутник выдавал сверточно кодированный со скоростью 1/2 сигнал, имеющий пунктурированный код 2/3 с энергетическим уровнем 10 Вт, который и принимают антенны. После начального периода вхождения в фазу излучаемая мощность должна быть увеличена на 3 дБ, до 20 Вт. Вначале думалось, что для более высоких энергетических уровней можно использовать пунктурированный код 7/8. В результате проведенного анализа на вероятность ошибки стало понятно, что пунктурированный код 7/8 неприемлем и что для достижения приемлемых результатов на более высоком энергетическом уровне нужно использовать пунктурированный код 6/7.

Соответственно другая цель изобретения - создание нового устройства и метода с улучшенной передачей с упреждающим исправлением ошибок, использующих многие пунктурированные коды и многие энергетические уровни.

Другая цель изобретения - создание нового и улучшенного способа и устройства, предназначенных для передачи информационных сигналов с пунктированным кодированием (в особенности кодированных сигналов телевизионных программ) через геосинхронный спутник на наземные объекты, имеющие антенны с отражающими сферическими зеркалами диаметром не более 1 м.

Один аспект этого изобретения посвящен способу упреждающего исправления ошибок, когда входные биты, представляющие информационный сигнал, кодируются на уровне передатчика по разным параллельным последовательным потокам бит - первому и второму, - так что (а) ряд входящих битов преобразуется в набор битов первого и второго параллельного потока бит и (б) первый и второй параллельный поток бит имеет последовательные временные интервалы 1, 2, ..., j,. . . , M так, что в каждом временном интервале имеется бит из каждого потока бит. Первый и второй параллельный поток бит соединяется и пунктурируется в последовательный пунктурированный поток бит с временными интервалами 1, 2, . .., K, ..., N, таким образом, что: а) для временного интервала j1, не имеющего битов, (i) временные интервалы k1 и (k1+1) соответственно содержат биты во временном интервале j1 первого и второго потока бит, (ii) временной интервал (k1 - 1) содержит бит, являющийся результатом бита во временном интервале (j1-1) первого и второго потока бит при условии, что временной интервал (j1-1) первого и второго потока бит имеет как минимум один неудаленный бит, и (iii) временной интервал (k1+2) содержит бит, являющийся результатом бита во временном интервале (j1 + 1) при условии, что временной интервал (j1 + 1) первого и второго потоков бит имеет как минимум один неудаленный бит; б) для временного интервала j2 первого и второго потоков бит, имеющего один неудаленный бит и один удаленный бит (1), временной интервал k2 содержит неудаленный бит, (2) временной интервал (k2 - 1) содержит бит, являющийся результатом бита во временном интервале (j2 - 1) первого и второго потоков бит при условии, что временной интервал (j2 - 1) первого и второго потоков бит содержит как минимум один неудаленный бит, временной интервал (k2 + 1) содержит бит, являющийся результатом бита во временном интервале (j2 + 1) первого и второго потока бит при условии, что временной интервал (j2 + 1) первого и второго потока бит содержит как минимум один неудаленный бит; в) для временного интервала j3 первого и второго потока бит, содержащего только удаленные биты, в последовательном потоке удаленных бит не имеется временного интервала. Ряд параллельных пунктурированных потоков бит, включая биты последовательного потока бит, формируется как реакция на последовательный поток. Носитель модулируется в зависимости от битов в ряде параллельных пунктурированных битовых потоков так, что носитель одновременно модулируется рядом параллельных потоков бит. В приемнике переданный модулированный носитель преобразуется в пятый и шестой параллельные потоки бит, аналогичные ряду параллельных потоков бит. Пятый и шестой потоки бит декодируются в сигнал, аналогичный информационному сигналу.

В соответствии с другим аспектом этого изобретения система передачи с упреждающим исправлением ошибок с пунктурированными сверточно-кодированными потоками бит в приемнике содержит средство, реагирующее на сигнал, полученный приемником с целью извлечения первого последовательного пунктурированного потока бит, имеющего первую скорость передачи бит. Этот первый последовательный поток бит аналогичен последовательному пунктурированному потоку бит на уровне передатчика, на который реагирует приемник. Регистр обратного магазинного типа имеет входной синхронизирующий терминал, выходной синхронизирующий терминал, вход для данных и выход для данных. Вход данных реагирует на первый последовательный пунктурированный поток бит. Второй сверточно-кодированный последовательный поток бит, имеющий вторую скорость передачи бит, получается на выходе данных.

Синхронизатор получает последовательность бит канала и последовательность пунктурированных синхроимпульсов. Входной синхронизирующий терминал реагирует на последовательность синхронизованных импульсов канала. Схема, реагирующая на пунктурированный поток синхронизованных импульсов, выдает последовательность импульсов на выходной терминал синхронизатора. Это устройство может использоваться для всех оптимальных пунктурирующих кодов и скоростей, описанных Ясудой и др., и тем самым применимо повсеместно.

В предпочтительном варианте реализации приемное устройство содержит универсальное средство, которое реагирует на модулированный сигнал, включающий первый и второй каналы. Средство для формирования первого последовательного пунктурированного потока бит реагирует на модулированный сигнал с целью формирования двух параллельных потоков бит, содержащий биты первого и второго каналов. Пара параллельных потоков бит, содержащая канальные биты модулированного сигнала, объединяется для получения первого потока бит.

Дополнительный аспект этого изобретения посвящен приемнику с упреждающим исправлением ошибок, реагирующему на сигнал, содержащий каналы I и Q, включающий пунктурированные сверточно-кодированные биты с некоторой скоростью, с пунктурированным кодом и схемой пунктурирования. Приемник содержит элементы, реагирующие на каналы I и Q для объединения их бит в один последовательный сигнал так, что биты каналов I и Q во временном интервале tk - это соответственно последовательные биты bJ и bJ+1 одного последовательного сигнала, где tk - каждый из последовательных временных интервалов t1, t2, .. ., tN.

Синхронизатор данных выдает синхроимпульсы, имеющие пунктурированную структуру, соответствующую структуре пунктурирования каналов I и Q. Устройство, реагирующее на последовательный сигнал и на синхроимпульсы синхронизатора данных, выдает первый и второй параллельные выходные потоки бит, каждый из которых содержит последовательные временные интервалы с битами с обоих каналов I и Q.

Такой приемник может обрабатывать все оптимальные пунктурирующие коды. Предпочтительно, чтобы средство для получения третьего и четвертого выходных потоков бит включало в себя запоминающее устройство для хранения двоичных битов, соответствующих пунктурирующим структурам. Это запоминающее устройство имеет адресацию в ответ на синхроимпульсы синхронизатора данных.

Дополнительный аспект этого изобретения предполагает передачу сверточно-кодированного сигнала с упреждающим исправлением ошибок, имеющего первый сверточно-кодированный поток бит с последовательными битами P1(0), P1(1), P1(2), P1(3), P1(4) и второй сверточно-кодированный поток бит с последовательными битами P2(0), P2(1), P2(2), P2(3), P2(4) путем пунктурирования только каждого другого бита первого потока бит для получения пунктурированного первого потока бит и реагирования на первый пунктурированный поток бит и второй поток бит для получения параллельных I и Q каналов. Четыре последовательных временных интервала Tk, tk+1, tk+2, tk+3 канала 1 соответственно состоят из битов P1(0), P2(1), P2(2), P1(4), а соответствующие временные интервалы tk, tk+1, tk+2, tk+3 канала Q соответственно состоят из битов P2(0), P1(2), P2(3), P2(4). Носитель одновременно модулируется двумя битами каналов I и Q во временных интервалах tk, tk+1, tk+2, tk+3.

Это изобретение также относится к созданию приемника, реагирующего на сверточно-кодированный информационный сигнал ряда каналов (I и Q), пунктурированный с заранее определенной скоростью. Приемник содержит средство, реагирующее на ряд каналов сигнала для получения последовательного сигнала, имеющего последовательные биты I(0), I(1), I(2) и т.д. временных интервалов tk, tk+1, tk+2 канала I и последовательные биты Q(0), Q(1), Q(2) и т.д. канала Q, в то же время временные интервалы tk, tk+1, tk+2 последовательно выдаются в последовательном сигнале как I(0), Q(0), I(1), Q(1), I(2), Q(2) и т.д.

Получается пунктурированный синхроимпульс, синхронизированный с последовательными битами последовательного сигнала. Пунктурированный синхроимпульс, синхронизированный с последовательными битами последовательного сигнала, объединяется с последовательными битами последовательного сигнала. Получается пара выходных последовательностей импульсов G1 и G2, включая последовательные биты каналов I и Q и фиктивные биты, вставленные в последовательный сигнал. Серии битов G1 и G2 включают в себя биты каналов I и Q. Имеется средство для указания, какие из битов в серии бит G1 и G2 являются фиктивными.

Кроме того, это изобретение направлено на создание приемника, реагирующего на полученный по первому и второму каналу (I и Q) сверточно-кодированный информационный сигнал с упреждающим исправлением ошибок, пунктурированный с заранее определенной скоростью. Информационный сигнал принимается от передатчика, где получаются первая и вторая серии кодированных со скоростью 1/2 данных. Сверточно-кодированные со скоростью 1/2 серии данных преобразуются в пунктурированные каналы I и Q, которые приблизительно те же самые, что и сверточно-кодированный информационный сигнал с упреждающим исправлением ошибок. Канал I на уровне передатчика включает в себя последовательные биты первого и второго сигнала в разных временных интервалах; канал Q на уровне передатчика включает в себя другие последовательные биты первого и второго сигнала в других отличных временных интервалах. Приемник содержит устройство, реагирующее на ряд каналов сигнала для получения последовательного сигнала с последовательными битами, так что последовательные биты I(0), I(1), I(2) и т.д. временных интервалов tk, tk+1, tk+2 принятого канала I и последовательные биты Q(0), Q(1), Q(2) и т.д. принятого канала Q с теми же временными интервалами tk, tk+1, tk+2 последовательно получаются в последовательном сигнале как I(0), Q(0), I(1), Q(1), I(2), Q(2) и т.д. Получается пунктурированный синхроимпульс, синхронизированный с последовательными битами последовательного сигнала и комбинируется с последовательными битами последовательного сигнала. Получается пара выходных серий импульсов G1 и G2, включая последовательные биты принятых каналов I и Q и фиктивные биты, вставленные в последовательный сигнал. Серия битов G1 включает в себя только биты первой серии импульсов и фиктивные биты, тогда как серия битов G2 включает в себя только биты второй серии импульсов и фиктивные биты. Фиктивные биты в сериях бит G1 и G2 указаны.

В одном варианте реализации приемник содержит мультиплексор, имеющий первый и второй входы, соответственно реагирующий на принимаемые каналы I и Q, и выходной терминал для получения последовательного сигнала. Источник синхроимпульсов приводит в действие мультиплексор, так что каналы I и Q соединяются с выходным терминалом один раз в разные моменты времени в течение одного символьного времени принимаемых каналов I и Q. Предпочтительно, чтобы средство для получения пары выходных серий импульсов содержало схемы, синхронизируемые пунктурированным синхроимпульсом и реагирующие на последовательный сигнал для получения серий бит G1 и G2 с частотой первой и второй последовательности сверточно-кодированных со скоростью 1/2 данных. В одном варианте реализации синхронизированная схема содержит регистр обратного магазинного типа, имеющий входной и выходной сигнальные терминалы и входной и выходной терминалы синхроимпульсов; выходной терминал синхроимпульсов реагирует на пунктурированный синхроимпульс.

Входной сигнальный терминал реагирует на выход мультиплексора, тогда как входной терминал синхроимпульсов реагирует на синхроимпульсы, имеющие частоту, которая синхронизирует каждый бит на выходном терминале мультиплексора, направляя его в регистр. Преобразователь последовательного кода в параллельный, имеющий выход, реагирующий на выход регистра, включает в себя пару выходных терминалов, на которых получаются серии бит G1 и G2.

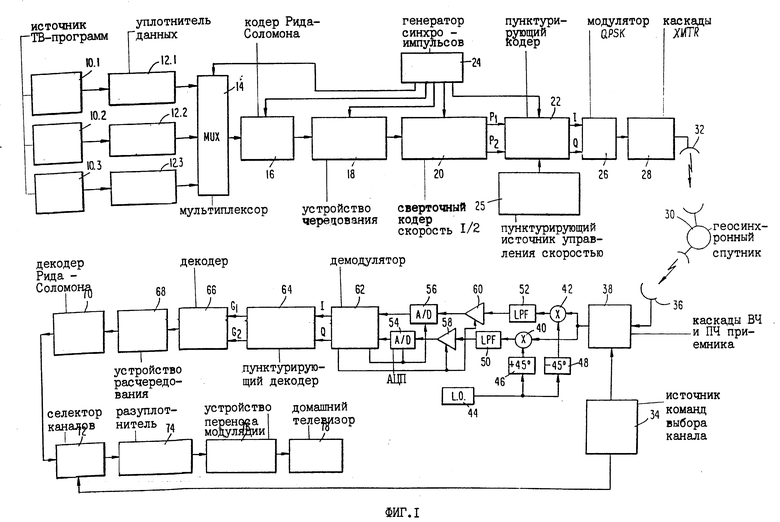

На фиг. 1 приведена общая блок-схема способа и устройства передачи и приема данных с упреждающим исправлением ошибок в соответствии с предпочтительным вариантом реализации настоящего изобретения;

на фиг. 2 - блок-схема предпочтительного первого варианта реализации универсального пунктурированного кодера в передатчике фиг. 1;

на фиг. 3 - блок-схема предпочтительного первого варианта реализации универсального пунктурированного кодера в приемнике фиг. 1;

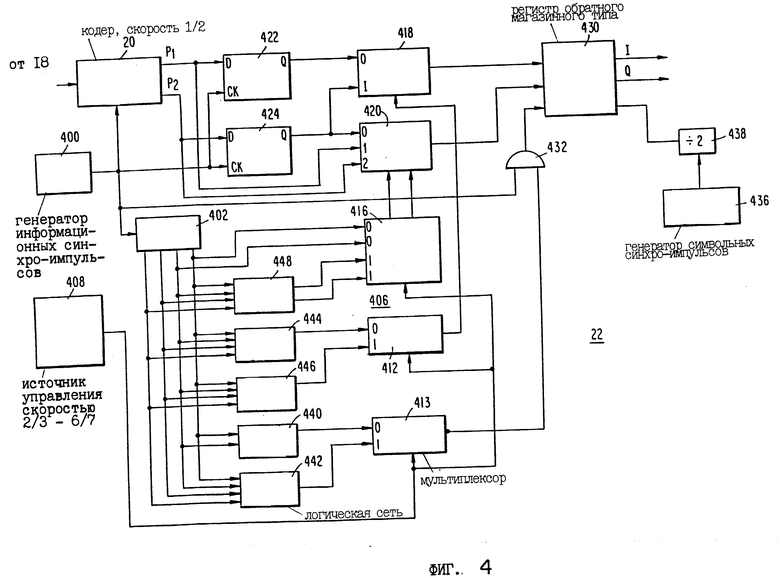

на фиг. 4 - блок-схема второго варианта реализации пунктурированного кодера, в особенности способного обрабатывать пунктурированные коды 2/3 и 6/7;

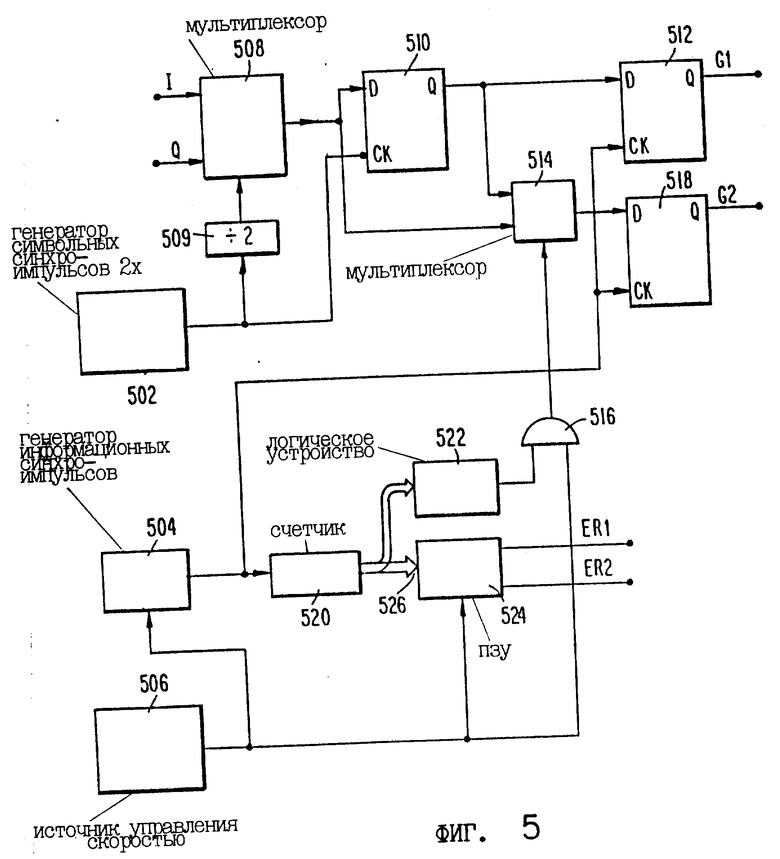

на фиг. 5 - блок-схема второго варианта реализации пунктурированного декодера, в особенности способного обрабатывать пунктурированные коды 2/3 и 6/7.

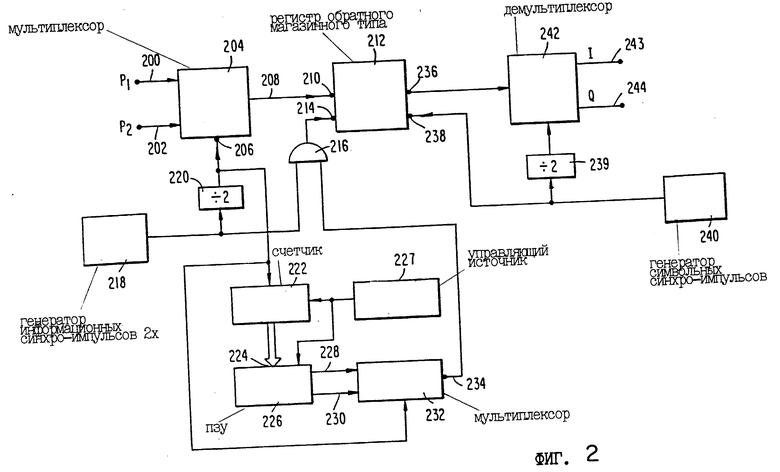

На фиг. 1 представлена блок-схема системы, включающая некоторые характеристики изобретения, в которой источники телевизионных программ 10.1, 10.2 и 10.3 соответственно подают широкополосные аудио- и видеосигналы на уплотнители информации 12.1, 12.2 и 12.3. Уплотнители 12.1, 12.2 и 12.3 выдают двоичные серии бит, соответственно указывающие на частотно-уплотнительные версии аудио- и видеоинформации источников 10.1, 10.2, 10.3. Двоичные серии импульсов, полученные от уплотнителей 12.1, 12.2 и 12.3, объединяются в мультиплексоре 14 с временным разделением с формированием одного двоичного сигнала, который подается в кодер 16 Рида-Соломона. Получающаяся двоичная серия бит от кодера 16 Рида-Соломона подается на обычное устройство 18 чередования, выход которого соединен со сверточным кодером 20 с половинной скоростью работы. Сверточный кодер 20 выдает пару параллельных двоичных потоков бит P1 и P2, имеющих последовательные биты P1(0), P1(1), P1(2) и т.д. и P2(0), P2(1), P2(2) во временных интервалах 0, 1, 2 и т.д. Выходы кодера 20 P1 и P2 соединены с пунктурирующим кодером 22. Все устройства - мультиплексоры 14, кодер 16, устройство чередования 18 и кодер 22 - реагируют на импульсы от источника 24 синхроимпульсов. Пунктурирующий кодер 22 реагирует на сигналы, поступающие от кодера 20 и источника синхроимпульсов 24, а также на командный сигнал с пунктурированным кодом от управляемого оператором источника 25 с получением пары параллельных пунктурированных последовательных двоичных потоков бит, которые подаются на входы I и Q квадратурного фазового модулятора 26 с переключением регистров.

Модулятор 26 реагирует на двоичные потоки бит, подаваемые на него, с получением квадратурной фазовой серии импульсов с переключением регистров, подаваемой на передатчик 28, имеющий выходную излучающую антенну 32, посылающую сигналы на ответчик или повторитель на геосинхронном спутнике 30. Схемы на геосинхронном спутнике 30 реагируют на сигнал от передатчика 28 и антенны 32 с формированием микроволнового сигнала, имеющего чрезвычайно широкий луч, на многочисленные наземные принимающие объекты, один из которых показан на фиг. 1. Сигнал, передаваемый от спутника 30 на наземный принимающий объект, обычно находится в полосе C или полосе Ku.

Обычный наземный принимающий объект содержит отражающую сферу антенны 36 с диаметром не более 1 м и оптимально имеющую параболическую форму. В первом и втором конкретном варианте реализации сфера антенны 36 имеет соответственно диаметр 60 и 90 см. Сигнал, преобразованный активным элементом, связанным со сферой 36, усиливается и преобразуется в промежуточную частоту (ПЧ) каскадами высокой частоты (ВЧ) и ПЧ 38, реагирующими на управляемый оператором сигнал выбора канала от источника 39. Каскады 38 имеют ПЧ-аналоговый выход, подключенный параллельно к преобразователям частоты 40 и 42, подключенным к выходу гетеродина 44 с фиксированной частотой через фазовращатели +/-45o 46 и 48. Выходы преобразователей частоты соединены с согласованными фильтрами нижних частот 50 и 52, имеющие широкополосные выходы I и Q, которые соответственно соединены с аналого-цифровыми преобразователями 54 и 56 через усилители 58 и 60 с регулируемым усилением и для нормирования амплитуды входных сигналов, подаваемых на преобразователи, так что максимальный уровень аналогов входа, подаваемого на преобразователь, равен максимальному уровню напряжения, который преобразователи предназначены обрабатывать.

Преобразователи 54 и 56 реагируют на широкополосные сигналы I и Q, подаваемые на них, для получения многобитовых цифровых сигналов, имеющих значения, соизмеримые с величиной и полярностью широкополосных сигналов I и Q, подаваемых на преобразователи, так что наиболее значимые биты, выдаваемые преобразователями, представляют полярность, тогда как оставшиеся биты представляют амплитуду.

Аналого-цифровые преобразователи 54 и 56 соединены с аналоговыми выходами усилителей 58 и 60 и выходами демодулятора 62, с которого селекторные импульсы подаются для получения многобитовых цифровых сигналов. Демодулятор 62, предпочтительно имеющий конфигурацию, описанную в совместно рассматриваемой заявке (серийный номер 07/998.300 Ицхак Гуранц, Йоав Гольденберг и Шри Рагхаван. Демодулятор для потребительских целей, N 07/998300, 30.12.92 г. ). Демодулятор 62 выдает: а) селекторные импульсы, которые подаются на аналого-цифровые преобразователи 54 и 56; б) сигналы управления коэффициентом усиления для усилителей с регулируемым усилением 58 и 60; в) несущий сигнал отслеживания ошибок, используемый в демодуляторе для корректирования ошибок по частоте и фазе гетеродина 44 относительно частоты и фазы ПЧ-выхода каскадов 38; г) выходные сигналы каналов I и Q. Для каждой выборки, взятой преобразователями 54 и 56, демодулятор 62 выдает три параллельных двоичных выходных бита в каждом из своих выходных каналов I и Q. Самый значимый бит каждой триады битов представляет полярность выборки, скорректированную схемой отслеживания несущей, и два дополнительных двоичных бита обеспечивают меру качества первого бита, скорректированного схемой отслеживания несущей.

Самый значимый бит каждой триады из трех бит в выходе демодулятора 62, таким образом, указывает двоичное значение, связанное с каждой выборкой, взятой аналого-цифровыми преобразователями 54 и 56, а два наименее значимых бита указывают фактор доверительности для двоичного значения самого значимого бита.

Выходные сигналы каналов I и Q демодулятора 62 подаются в пунктурирующий декодер 64, установленный на пунктурированный код пунктурирующего кодера 22 на уровне передатчика, т.е. либо 2/3, либо 6/7. Декодер 64 устанавливается оператором для правильного пунктурированного кода или же им можно управлять автоматически. Пунктурирующий декодер 64 реагирует на выходы I и Q демодулятора 62 с получением двоичной индикации каждой выборки, взятой аналого-цифровыми преобразователями 54 и 56; двоичные выходы декодера 64, связанные с каналами I и Q, выданными демодулятором 62, - это последовательности данных, обозначенные соответственно как G1 и G2. Декодер 64 также выдает на выводах 65 и 67 сигналы, указывающие, являются или нет его одновременно выдаваемые выходы G1 и G2 фиктивными битами. Пунктурирующий декодер 64 также вставляет фиктивные биты во временные интервалы, соответствующие временным интервалам, которые пунктурированы, т.е. удалены пунктурирующим кодером 22 на уровне передатчика, и выдает пунктурированный информационный синхроимпульс, имеющий скорость, соответствующую последовательностям данных G1 и G2 и синхронизированную с ними.

Все рассмотренные выходы пунктурирующего декодера 64 подаются на декодер Viterbi 66, который выдает одну серию последовательных двоичных сигналов, вполне аналогичную двоичной серии импульсов, подаваемых на кодер 20.

Двоичная последовательная серия сигналов, выдаваемая декодером Viterbi 66, поступает в устройство расчередования 68, выход которого подается на декодер Рида-Соломона 70, имеющий многобитовый последовательный выход, который является приблизительной репликой сигнала, подаваемого на кодер Рида-Соломона 16 на уровне передатчика.

Двоичный выходной сигнал декодера Рида-Соломона 70 подается на селектор канала 72, реагирующий на сигнал выбора канала от телевизора на принимающем объекте. Селектор канала 72 выбирает двоичные биты в выходном сигнале декодера Рида-Соломона 70, связанные с источником телевизионных программ 10.1, 10.2 или 10.3, выбранным пользователем телевизора на принимающем объекте. Двоичные биты, связанные с выбранным источником программ, заводятся на видеоразуплотнитель 74 для исключения двоичных бит, связанных с другими источниками программ на уровне передатчика. Видеоразуплотнитель 74 реагирует на значения двоичных сигналов, подаваемых на него, для получения аналогового сигнала, который является приблизительной репликой аудио- и видеоинформации выбранного источника программ 10.1 - 10.3.

Аналоговый выходной сигнал разуплотнителя 74 подается на устройство переноса модуляции 76, которое преобразует подаваемый на него сигнал в обычный телевизионный сигнал в любом из принятых форматов, таких как NTSC, PAL или SECAM. Сигнал, выданный устройством переноса модуляции 76, модулируется на стандартной широкополосной телевизионной несущей частоте, такой как несущая частота, связанная с каналом 3 или 4, как он выбирается переключателем на принимающем объекте. Стандартный телевизионный сигнал, выдаваемый при этом устройством переноса модуляции 76, подается в обычный домашний телевизор 78. В качестве альтернативы в домашний телевизор включены элементы, аналогичные элементам 38 - 76.

Система (фиг. 1) ранее предлагалась другими, разве что предлагаемые ранее пунктурированные коды для пунктурирующего кодера 22 и пунктурирующего декодера 64 были 2/3 и 7/8. Установлено, что пунктурированный код 2/3 нужно излучать со схем спутника 30 на уровне 10 Вт и что другой пунктурированный код нужно излучать со спутника на уровне 20 Вт. Проведя анализ вероятности ошибки (в битах), обнаружено что пунктурированный код 7/8 является избыточным для успешной работы системы с излучениями на уровне 20 Вт с геосинхронного спутника 30, но что излучения на уровне 20 Вт при пунктурированном коде 6/7 приемлемы.

Когда кодер 22 установлен для пунктурирования на скорости 2/3, биты P1(0), P1(1), P1(2), P1(3), P1(4) в потоке бит P1 во временных интервалах t0, t1, t2, t3, t4 и биты P2(0), P2(1), P2(2), P2(3), P2(4) в потоке бит P2 в соответствующих временных интервалах преобразуются пунктурирующим кодером 22 в сигналы I и Q, которые подаются в модулятор 26 (табл. 4).

Кодер 22 реагирует на последовательные биты в потоках бит P1 и P2 аналогично тому, как это описано для бит P1(0), P1(4) и бит P2(0), P2(4) для получения последовательных выходов I и Q кодера. С этой целью кодер 22 включает пунктурирующий код для бит P1(0), P1(1), и P2(0), P2(1) (табл.5).

Пунктурирующий код табл. 5 прилагается к потокам бит P1 и P2 следующим образом (табл. 6).

В одном предпочтительном варианте реализации этого изобретения непунктурированные биты табл. 6 сформированы в последовательный сигнал в соответствии с

P1(0), P2(0), P2(1), P1(2), P2(2), P2(3), P1(4), P2(4). (1)

Биты с нечетными числами в выражении (1), т.е. биты P1(0), P2(1), P2(2), P1(4), заводятся кодером 22 на выход кодера 1, тогда как биты с четными номерами в выражении (1), т.е. биты P2(0), P1(2), P2(3), P2(4), заводятся на выход кодера Q, что образует последовательности бит I и Q табл. 4.

Когда пунктурирующий кодер 22 установлен на пунктурирование со скоростью 6/7, последовательные биты во временных интервалах t0 - t11 выходов P1 и P2 кодера 20 преобразуются кодером 22 в выходные сигналы каналов I и Q (табл. 7).

Кодер 22 реагирует на последовательные биты в потоках бит P1 и P2 аналогично тому, как это описано для бит P1(0) P1(11) и P2(0) P2(11) для получения выходных бит I и Q кодера. С этой целью кодер 22 включает пунктурирующий код для бит P1(0), P1(5) и P2(0), P2(5) (табл. 8).

В одном варианте реализации пунктурирующий код табл. 8 приложен к потокам бит P1 и P2 следующим образом (табл. 9).

Непунктурированные биты табл. 9 формируются в последовательный сигнал в соответствии с

P1(0), P2(0), P2(1), P2(2), P1(3), P2(4), P1(5), P1(6), P2(6), P2(7), P2(8), P1(9), P2(10), P1(11).(2)

Биты с нечетными номерами в выражении (2), т.е. биты P1(0), P2(1), P1(3), P1(5), P2(6), P2(8), P2(10), заводятся на выход I кодера 22, тогда как биты с четными номерами в выражении (2), т.е. биты P2(0), P2(2), P2(4), P1(6), P2(7), P1(9), P1(11), заводятся на выход Q кодера, что образует последовательности бит табл. 7.

Аналогичным образом, но противоположным способом декодер 64 установлен на пунктурированный код 2/3 или 6/7. Декодер 64 реагирует на сигналы выходов I и Q демодулятора 62 и разделяет эти сигналы G1 и G2, аналогичные входам P1 и P2 пунктурирующего кодера 22, и указывает, какие биты, выданные декодером, связаны с битами, которые были пунктурированы кодером 22. Декодер 64 содержит пунктурирующие коды, идентичные пунктурирующим кодам табл. 5 и 7 для скоростей 2/3 и 6/7.

Если пунктурирующий декодер 64 установлен на пунктурированный код 2/3, он реагирует на последовательные биты потоков бит I и Q, выданных демодулятором 62 и на код табл. 5 для получения выходных сигналов G1 и G2, которые являются близкой репликой сигналов P1 и P2, подаваемых в пунктурирующий кодер 22, так что последовательные биты I(0) I(8) и Q(0) Q(8) каналов I и Q во временных интервалах t0 - t11 получаются в соответствие с табл. 10:

где X - "фиктивный" бит, т.е. бит, имеющий значение, не соотнесенное со значением бита в I(0) I(8) или Q(0) Q(8).

Для формирования последовательностей бит табл. 10 в одном варианте реализации, последовательности бит I(0) I(8) и Q(0) Q(8) и структура удаления табл. 5 комбинируются для образования последовательности, включая "фиктивные" биты (табл. 10), следующим образом:

I(0), Q(0), X, I(1), Q(1), I(2), X, Q(2),

I(3), I(3), X, I(4), Q(4), I(5), X, Q(5),

I(6), Q(6), X, I(7), Q(7), I(8), X, Q(8).(3)

Декодер 64 заводит последовательности бит выражения (3) на свои выходы G1 и G2, так что биты с нечетными и четными номерами последовательности соответственно получаются на выходах G1 и G2 в соответствии с табл. 10.

Когда пунктурирующий декодер 64 установлен на скорость 6/7, он реагирует на последовательные биты в потоках бит I и Q на выходе демодулятора 62 и на пунктурирующий код табл. 8 для получения последовательностей бит G1 и G2 в соответствии с табл. 11.

Для образования последовательностей бит табл. 1 в одном варианте реализации последовательности бит I(0) I(6) и Q(0) Q(6) и структура удаления табл. 8 комбинируются с формированием последовательно последовательности, включая "фиктивные" биты, следующим образом:

I(0), Q(0), X, I(1), X, Q(1), I(2), X, X, Q(2), I(3), X, Q(3), I(4), X, Q(4), X, I(5), Q(5), X, X, I(6), Q(6), X. (4)

Декодер 64 заводит последовательность бит выражения (4) на свои выходы G1 и C2, так что биты последовательности с нечетными и четными номерами соответственно получаются на выходах G1 и G2 в соответствии с табл. 11.

Изучение данных табл. 10 и 11 показывает, что имеются повторяющиеся структуры фиктивных бит; в табл. 10 структура "фиктивных" бит повторяется после каждой пары временных интервалов; в табл. 11 битовая комбинация первых шести временных интервалов повторяется во втором наборе временных интервалов. Последовательный поток выражения (3) образуется путем преобразования в последовательную форму потоков бит I и Q, так что I(k) находится непосредственно перед Q(k) и Q(k) находится непосредственно перед I(k+l); затем "фиктивный" бит вставляется у третьего временного интервала в каждой последовательности четырех бит в конечном преобразованном в последовательную форму потоке бит; например, первый "фиктивный" бит следует за битами I(0), Q(0) и находится непосредственно перед I(1) для образования первых четырех бит в конечном преобразованном в последовательную форму потоке бит. Выражение (4) образуется путем преобразования в последовательную форму потоков бит I и Q и включения "фиктивных" бит у третьего, пятого, восьмого, девятого и двенадцатого временного интервала в каждой последовательности 12 бит в конечном преобразованном в последовательную форму потоке бит. Включение "фиктивных" бит в конечные преобразованные в последовательную форму потоки бит управляется положениями значений "0" в табл. 5 и 8.

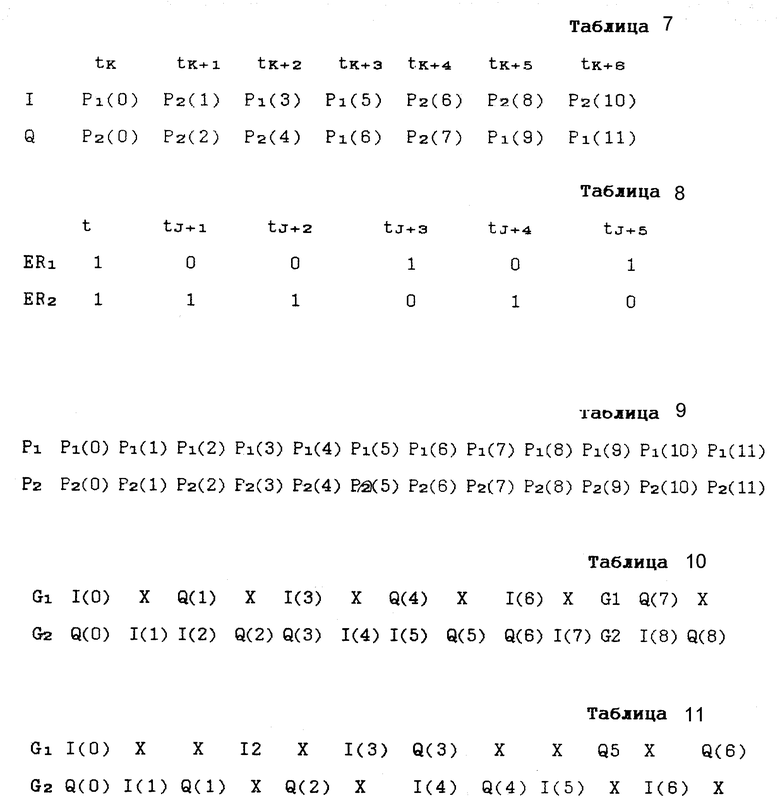

На фиг. 2 представлена блок-схема универсального устройства для преобразования потоков информационных бит P1 и P2 на выводах 200 и 202, полученных из сверточного кодера 20, в пару пунктурированных потоков бит каналов I и Q. Устройство фиг. 2 можно использовать с потоками бит P1 и P2 для любых оптимально пунктурированных кодов, описанных Ясудой и др., т.е. 1/2, 2/3, 4/5, 5/6, 6/7, 7/8, 8/9, 9/10, 10/11, 11/12, 12/13, 13/14, 14/15, 15/16, 16/17. Информационные биты на выводах 200 и 202 подаются на электронный мультиплексор 204, работающий на частоте, в два раза превышающей скорость передачи данных на выводах 200 и 202, в ответ на информационный синхроимпульс с волной в виде меандра на терминале 206. Информационный синхроимпульс на терминале 206 и данные на выводах 200 и 202 имеют одну и ту же частоту и фазу, причем этот результат достигается обычной схемой синхронизации (не показана). Мультиплексор 204 реагирует на уровни "один" на терминале 206 для переключения сигнала на выводе 200 на выходной вывод 208; в ответ на нулевой уровень на терминале 206 сигнал на выводе 202 заводится на выходной вывод 208.

Результирующая последовательная последовательность бит P1(0), P2(0), P1(1), P2(1), P1(2), P2(2) и т.д. на выводе 208 подается на входной информационный терминал 210 регистра обратного магазинного типа 212, содержащего входной терминал синхроимпульсов 214. Входной терминал синхроимпульсов 214 реагирует на пунктурированные информационные синхроимпульсы, получаемые от вентиля И 216, один вход которого реагирует на серию импульсов от источника синхроимпульсов 218, который выдает синхроимпульсы, синхронизованные с частотой синхроимпульсов терминала 206 и имеющие частоту, в два раза большую этой частоты.

Синхроимпульсы, полученные из источника 218, заводятся непосредственно на один вход элемента И 216, тогда как входной терминал 206 мультиплексора 204 реагирует на импульсы от источника синхроимпульсов 218, модифицированные делителем частоты 220, делящим на 2.

Другой вход элемента И 216 соединен с выходом мультиплексора 234. Информационные синхроимпульсы делителя частоты 220 подаются на счетный вход счетчика 222, многобитовый выход которого соединен с адресным входом 224 запоминающего устройства (ЗУ) 226. Счетчик 222 и ЗУ 226 реагируют на управляющий сигнал от источника 227, указывающий на то, какой нужно использовать из кодов удаления, приведенных Ясудой и др. Счетчик 222 установлен на максимальный отсчет как реакция на управляющий сигнал от источника 227 и непрерывно упорядочивается от нуля до своего максимального отсчета информационными синхроимпульсами от делителя 220. Отсчет в генераторе 222 управляет адресным входом 324 ЗУ 226.

ЗУ 226 загружается парой структур удаления для каждого из кодов удаления, указанных в статье Ясуды и др. Выбор кода удаления производится управляющим источником 227. Последовательные биты двух структур удаления выбранного кода удаления подаются на выводы 228 и 230 посредством ЗУ 226 как реакция на последовательные адреса, подаваемые на вход 224. Например, если выбранный код удаления имеет скорость 2/3, то генератор 222 реагирует на первые три информационных синхроимпульса от делителя 220 для подачи адресов 0000, 0001, 0000 в последовательности на адресный вход 224, а ЗУ 226 реагирует на эти адресные сигналы для подачи на выводы 228 и 230 последовательных двоичных бит 10 и 11 соответственно; последовательности на выводах 228 и 230 соответственно соответствуют последовательностям строк 1 и 2 табл. 5.

Аналогичная последовательность получается на выводах 228 и 230 в ответ на каждую следующую триаду последовательных информационных синхроимпульсов. Если управляющий источник 227 установлен на пунктурированный код 6/7, генератор адресов 222 реагирует на первые шесть информационных синхроимпульсов от делителя 220 для получения адресов 0000, 0001, 0010, 0011, 0100, 0101, что заставляет ЗУ 226 подавать на выводы 228 и 230 двоичные последовательности 100101 и 111010 соответственно; эти последовательности соответствуют последовательностям в строках 1 и 2 табл. 8 и повторяются для каждых шести последовательных информационных синхроимпульсов.

Для вышеуказанной ситуации 2/3 последовательности бит на выводе 234 и на выходе элемента И 216 это соответственно повторяющиеся последовательности 1101 и 10100010; для ситуации 6/7 последовательности бит на выводе 234 и на выходе элемента И 216 это соответственно повторяющиеся последовательности 110101100110 и 101000100010100000101000. Регистр обратного магазинного типа 212 реагирует на фронт каждой 1 в выходе элемента И 216, чтобы синхронизированно выдать двоичное значение, одновременно находящееся на терминале 210 в регистр обратного магазинного типа. Поэтому двоичные значения, которые появляются на терминале 210, когда выход элемента И 216 равен 0, не заводятся в регистр обратного магазинного типа 212, поэтому удаляются, т.е. пунктурируются. Для ситуации 2/3 регистр обратного магазина типа 212 реагирует на последовательную комбинацию сигналов P1 и P2 на терминале 210 и на пунктурированные синхроимпульсы на терминале 208 для того, чтобы загрузиться пунктурированной последовательностью P1(0), P2(0), P2(1), P1(2), P2(2), P2(3), P1(4), P2(4) и т.д. Для ситуации 6/7 регистр 212 загружается пунктурированной последовательностью P1(0), P2(0), P2(1), P2(2), P1(3), P2(4), P1(5), P1(6), P2(6), P2(7), P2(8) и т.д.

Регистр обратного магазинного типа 212 включает в себя выходной терминал данных 236 и терминал синхроимпульсов 238 для управления скоростью, с которой биты подаются регистром обратного магазинного типа на терминал 236. Терминал 238 реагирует на источник символьных синхроимпульсов 240, имеющий частоту, равную двойной частоте, и символы подаются на выходы I и Q 234 и 244. Синхроимпульсы, полученные от источника синхроимпульсов 240, подаются через делитель частоты 239 с делением на 2 на преобразователь последовательного кода в параллельный, т.е. демультиплексор 242, вход данных которого реагирует на импульсы на выходе 236 регистра обратного магазинного типа 212. Преобразователь 242 реагирует на синхроимпульсы от источника 240, так что сигнал на терминале 236 заводится на выводы 243 и 244, когда синхроимпульсы имеют значения ноль и единица соответственно. Благодаря пунктурированию скорость передачи символов меньше скорости передачи данных; в одном варианте реализации скорость передачи данных на выводах 200 и 202 составляет 20 мгбит/с, тогда как скорость передачи данных на выводах 243 и 244 составляет 15 мгбит/с для пунктурированного кода 2/3.

Регистр обратного магазинного типа 212 реагирует на последовательность, загруженную в него, и на синхроимпульс на терминале 238 для получения на терминале 236 той же последовательной последовательности, которая загружается в регистр обратного магазинного типа на терминале 210. Эта последовательность считывается с терминала 236 с частотой синхроимпульсов, подаваемых на терминале 238, которая в два раза больше частоты символьных синхроимпульсов.

Для скорости 2/3 демультиплексор 242, переключающийся со скоростью вдвое выше частоты символьных синхроимпульсов в ответ на противоположные уровни частоты выходных символьных синхроимпульсов делителя 239, реагирует на последовательность на терминале 236, так что последовательности I(0), I(1), I(2), I(3), I(4) и Q(0), Q(1), Q(2), Q(3), Q(4) на выводах 243 и 244 это соответственно P1(0), P2(1), P2(2), P1(4) и т.д. и P2(0), P2(2), P2(3), P2(4) и т.д.; для скорости 6/7 последовательности на выводах 243 и 244 это соответственно P1(0), P2(1), P1(3), P1(5) P2(6), P2(8), P2(10) и т.д., и P2(0), P2(2), P2(4), P1(6), P2(7), P1(9), P1(11) и т.д.

На фиг. 3 показана блок-схема предпочтительного варианта реализации пунктурирующего декодера 64. Пунктурирующий декодер, показанный на фиг. 3, имеет структуру, очень похожую на структуру пунктирующего кодера, показанного на фиг. 2, что позволяет изготавливать пунктурирующий кодер и пунктурирующий декодер из одного и того же фотошаблона для печатной схемы с незначительными изменениями в соединениях. Пунктурирующий декодер, представленный на фиг. 3, также универсально применим ко всем оптимальным пунктурированным кодам, описанным Ясудой и др.

Пунктурирующий декодер на фиг. 3 включает в себя мультиплексор 304, регистр обратного магазинного типа 312, демультиплексор 342, элемент И 316, счетчик 322, ЗУ 326 и мультиплексор 332, которые соответствуют соответствующим элементам 204, 212, 242, 216, 222, 226 и 232 фиг. 2. Мультиплексор 304 реагирует на выходы I и Q демодулятора 62 и имеет выход, соединенный с входом данных регистра обратного магазинного типа 312 таким же образом, как выход мультиплексора 204 соединен с входом данных регистра обратного магазинного типа 212. Выход данных регистра 312 подается на вход демультиплексора 242 таким же образом, как выход данных регистра 212 соединяется с входом демультиплексора 342.

Демультиплексор 342 выдает последовательности бит G1 и G2, включая фиктивные биты, которые подаются на декодер Viterbi 66. Счетчик 322, ЗУ 326, мультиплексор 332 и элемент И 316 соединены друг с другом так же, как соединены друг с другом счетчик 222, ЗУ 226, мультиплексор 332 и элемент 216.

Пунктурирующий декодер на фиг. 3 также содержит источники синхроимпульсов с волной в виде меандра 318 и 340, соответственно имеющие частоты, равные двойной частоте последовательностей данных G1 и G2, подаваемых демультиплексором 342 на выводы 343 и 344, и двойной частоте символов I и Q, подаваемых в мультиплексор 304 через выводы 300 и 302. Источники синхроимпульсов 318 и 340 синхронизированы относительно принимаемых символов способом, хорошо известным специалистам, с помощью непоказанного устройства. Выход генератора символьных синхроимпульсов 318, в два раза превышающий скорость последовательностей данных G1 и G2, подается на элемент И 316, так что вентиль И 316 выдает пунктурированную последовательность синхроимпульсов идентичным образом, что и элемент И 216, выдающий пунктурированную последовательность синхроимпульсов. Выход элемента И 316 подается на выходной терминал информационных синхроимпульсов 338 регистра обратного магазинного типа 312; в отличие от этого выходной терминал информационных синхроимпульсов регистра обратного магазинного типа 212 реагирует на частоту, равную двойной частоте передачи символов, как она получена из источника синхроимпульсов 240. Регистр обратного магазинного типа 312 реагирует на положительные проходящие фронты на терминале 338, так что регистр обратного магазинного типа выдает на терминале 336 двоичную последовательность бит, такую же как последовательность бит, подаваемая на регистр обратного магазинного типа.

Демультиплексор 342 имеет управляющий вход с частотой, равной частоте передачи данных в последовательностях G1 и G2, как они выдаются делителем 320 с делением на 2, который в свою очередь соединен с выходом источника информационных синхроимпульсов 318. Тем самым вывод 343 реагирует на двоичный уровень на терминале 336, когда выход делителя частоты 320 имеет двоичное значение 1 и выход на терминале 336 подается на вывод 344, тогда как выход делителя имеет двоичный уровень 0. Поэтому демультиплексор 342 переключается с частотой, в два раза большей частоты источника информационных синхроимпульсов 318.

Выход источника синхроимпульсов 340 с частотой, в два раза большей частоты символов I и Q на выводах 300 и 302, подается на входной терминал информационных синхроимпульсов 314 регистра обратного магазинного типа 312. Управляющий вход 306 мультиплексора 304 реагирует на делящий на два выход источника синхроимпульсов 340, как он получен от делителя 339 частоты с делением на 2, так что биты I и Q на выводах 300 и 302 поочередно подключаются к входу данных 310 регистра обратного магазинного типа 312 через вывод 308 с частотой, в два раза большей частоты символов I и Q на выводах 300 и 302. Счетчик 322 и ЗУ 326 реагируют на сигналы от управляющего источника 327, указывающие на то, какой из оптимальных кодов передается в приемник. Управляющий источник 327 может запускаться/управляться сигналом, выданным передатчиком в момент начала последовательности передачи или иным способом.

Для пунктурированного кода 2/3 последовательные символы I и Q, подаваемые на выводы 300 и 302, соответственно представлены как

I(0), I(1), I(2), I(3), I(4), I(5) и т.д., (5)

Q(0), Q(1), Q(2), Q(3), Q(4), Q(5) и т.д. (6)

Мультиплексор 304 реагирует на последовательности I и Q на выводах 300 и 302 с получением на выводе 308 сигнала в соответствии с

I(0), Q(0), I(1), Q(1), I(2), Q(2), I(3), Q(3), I(4), Q(4), I(5), Q(5) и т.д. (7)

Приведенная выше последовательность двоичных разрядов загружается в регистр обратного магазинного типа 312, который реагирует на пунктурированный синхроимпульсы, получаемые от элемента И 316, для получения на выводе 336 последовательности:

I(0), Q(0), X, I(1), Q(1), I(2), X, Q(2), I(3), Q(3), X, I(4), Q(4), I(5), X, Q(5) и т.д. (8)

где

X - "фиктивный" бит на выходе 336.

Демультиплексор 342 реагирует на представленную выше последовательность на терминале 336 для подачи на выводы 343 и 344 последовательностей G1 и G2 соответственно в соответствии с

G1 = I(0), X, Q(1), X, I(3), X, Q(4), X и т.д., (9)

G2 = Q(0), I(1), I(2), Q(2), Q(3), I(4), I(5), Q(5) и т.д. (10)

Замена значений P1 и P2, подаваемых на пунктурирующий кодер 22, на значения

I(0), I(1), I(2), I(3), I(4), I(5), и т.д. и Q(0), Q(1), Q(2), Q(3), Q(4), Q(5) и т.д.

указывает, что выход пунктурирующего декодера 64 упорядочен таким же образом, что и вход пунктурирующего кодера 22, за исключением вставки "фиктивных" бит. Наличие "фиктивных" бит сигнализируется декодеру Viterbi 66 посредством выхода мультиплексора 332 наличием 0 на выходе мультиплексора.

Для пунктурированного кода 6/7 входы и выход мультиплексора 304 и вход данных 310 регистра обратного магазинного типа 312 тождественны ранее описанной ситуации для пунктурированного кода 2/3. Однако для ситуации 6/7 выход элементов И 216 и 316 отличается от выхода для скорости 2/3; выходы элементов И 216 и 316 для пунктурированного кода 6/7 тождественны. Регистр обратного магазинного типа 312 реагирует на пунктурированный выход информационных синхроимпульсов элемента И 316 и на сигнал, подаваемый на него, для получения на терминале 336 последовательности в соответствии с

I(0), Q(0), X, I(1), X, Q(1), I(2), X, X, Q(2), I(3), X. (11)

Демультиплексор 342 реагирует на последовательность на выходе 336 регистра обратного магазинного типа 312 для получения на выводах 343 и 344 последовательностей данных в соответствии с

I(0), X, X, I(2), X, I(3) и т.д. (12)

Q(0), I(1), Q(1), X, Q(2), X и т.д. (13)

Устройство, показанное на фиг. 3, предназначено для ситуации, когда демодулятор 62 выдает один бит для каждого символа I и Q. Однако во многих ситуациях демодулятор 62 выдает самый значимый бит, указывающий на значения I и Q, и один или несколько дополнительных битов, указывающих на доверительные уровни самых значимых битов для правильных значений I и Q. Дополнительные биты выдаются параллельно с самыми значимыми битами I и Q и имеют соответствующие временные интервалы. Дополнительные биты обрабатываются устройством, аналогичным указанному на фиг. 3 так, что для каждого дополнительного бита имеются мультиплексор, регистр обратного магазинного типа и демультиплексор.

Мультиплексор, регистр обратного магазинного типа и демультиплексор для дополнительных бит приводятся в действие в параллель теми же самыми сериями информационных синхроимпульсов, сериями пунктурированных информационных синхроимпульсов и сериями символьных синхроимпульсов, которые приводят в действие мультиплексор 304, регистр обратного магазинного типа 312 и демультиплексор 342. Дополнительные биты подаются на декодер Viterbi 66 и обрабатываются им, устройством чередования 68 и декодером Рида-Соломона 70 способом, хорошо известным для обычных специалистов.

На фиг. 4 дана блок-схема второго варианта реализации пунктурирующего кодера 22, специально предназначенного только для получения пунктурированных сигналов 2/3 и 6/7 в ответ на выходные сигналы P1 и P2 кодера 20, передаваемые со скоростью 1/2. Сигналы P1 и P2, выданные кодером 20, соответственно подаются на входы D D-(данные)-триггеров 422 и 424, входы синхронизации (СК) которых реагируют на источник синхроимпульсов с информационной волной в виде меандра 400, также подсоединенный к кодеру 20 для управления скоростью, т. е. частотой, с которой сигналы P1 и P2 считываются с кодера. Сигналы на выходных Q-терминалах триггеров 422 и 424 соответственно подаются на входные сигнальные терминалы "0" мультиплексора с двойным входным сигналом 418 и мультиплексора с тройным входным сигналом 420. Мультиплексор 418 содержит входной сигнальный терминал "1", реагирующий на сигнал на выходе Q триггера 424, тогда как мультиплексор 420 содержит входной сигнальный терминал "1", реагирующий на выход P1 кодера 20. Выход P2 кодера 20 заводится на входной сигнальный терминал "2" мультиплексора 420. Мультиплексор 418 содержит один управляющий входной терминал двойного уровня (0 и 1), тогда как мультиплексор 420 содержит два управляющих входных терминала двойного уровня.

Мультиплексоры 418 и 420 приведены в действие, так что с них всегда одновременно снимается выходной сигнал. Выходные сигналы мультиплексоров 418 и 420 подаются на параллельные сигнальные входные терминалы регистра обратного магазинного типа 430, с которого получаются сигналы, представляющие символы I и Q. Выходные сигналы регистра обратного магазинного типа 430 выдаются со скоростью, равной половине частоты источника символьных синхроимпульсов 436, который возбуждает выходной терминал синхроимпульсов регистра обратного магазинного типа через делитель на 2 частоты 438. Скорость, с которой биты заводятся на сигнальные входные терминалы регистра обратного магазинного типа 430, регулируется элементом И 423, который в свою очередь реагирует на логическую комбинацию выхода информационных синхроимпульсов 400 и на пунктурирующий управляющий сигнал, получаемый от мультиплексора 434. Выход элемента 432 подается на входной синхронизационный терминал регистра обратного магазинного типа. Сигналы, представляющие символы I и Q, полученные регистром 430, соответственно реагируют только на выходы мультиплексоров 418 и 420.

Управление мультиплексорами 418 и 420 осуществляется с помощью логической сети 406, содержащей мультиплексоры 412, 416 и 434. Элемент И 432 реагирует на сигнал, подаваемый на него мультиплексором 434 и выходом с волной вида меандра генератора синхроимпульсов, имеющего заранее определенную "частоту". Пунктурированный выход элемента 432 - это последовательность двоичных уровне 1 и 0, организованных таким образом, что некоторые двоичные уровни 1 удаляются из выхода с волной вида меандра источника синхроимпульсов 400. Для скорости 2/3 элемента 432 реагирует на сигналы, подаваемые на него мультиплексором 434, и на последовательность 10101010 от источника синхроимпульсов 400 для получения последовательности 10101000.

Для скорости 6/7 элемент 432 реагирует на сигнал, подаваемый на него мультиплексором 434 и на последовательность 101010101010101010101010 от источника синхроимпульсов 400 для получения последовательности 101000100010100010001000. Каждая их указанных последовательностей, полученных от элемента 432, после этого повторяется. Поэтому для выхода элемента 432, имеющего "частоту" CKout, волна вида меандра, полученная из источника синхроимпульсов 400, имеет частоту CKin = 1,333CKout для скорости пунктурирования 2/3; для скорости пунктурирования 6/7 частота CKin волны вида меандра, полученной от генератора синхроимпульсов 400, равна 1,71429 CKout. С этой целью мультиплексор 416 содержит два выходных вывода, с которых получаются четыре возможных значения двоичных разрядов для управления мультиплексором 420; используются только три из четырех значений. Мультиплексор 412 содержит один выходной вывод, с которого получаются два двоичных уровня бит для управления состоянием мультиплексора 418. Выходные комбинации мультиплексора 416 контролируют, прошел ли сигнал на входном сигнальном терминале 0, 1 или 2 мультиплексора 420 на выход этого мультиплексора, или же выход мультиплексора 420 развязан с сигналами на его входных сигнальных терминалах.

Управление мультиплексорами 412, 416 и 434 производится в ответ на двоичный уровень, полученный от источника управления скоростью 408. Источник управления скоростью 408 выдает уровни 0 и 1, когда соответственно выбираются скорости пунктурирования 2/3 и 6/7. Двоичный выход источника 408 подается в параллель на входные управляющие терминалы мультиплексоров 412, 416 и 434. В ответ на двоичные уровни 0 и 1 источника 408 входы на входных сигнальных терминалах "0" и "1" мультиплексоров 412, 416 и 434 соответственно заводятся на выходной сигнальный терминал каждого мультиплексора.

Сигналы, подаваемые входными сигнальными терминалами 0 и 1 мультиплексоров 412, 416 и 434, получаются путем подачи выхода генератора информационных синхроимпульсов 400 на счетчик 12 состояний 402, ведущий отсчет в диапазоне от 0 до 11 и имеющий четырехразрядную выходную шину. Два наименее значимые выходные бита счетчика 402 подаются на логическую сеть 440, которая выдает двоичный уровень 1 в ответ на эти биты, имеющие значения, которые указывают на цифры 0, 1 или 2 (двоичные значения 00, 01, 10), и двоичный уровень 0 в ответ на два наименее значимые бита, имеющие числовое значение 3 (двоичное значение 11). Выход логической сети 440 подается на входной сигнальный терминал 0 мультиплексора 434. Все четыре двоичных выходных разряда счетчика 402 подаются на логическую сеть 442, которая выдает двоичное значение 1 в ответ на выход счетчика, представляющий любое из чисел 0, 1, 3, 5, 6, 8 или 10; логическая схема 442 выдает двоичное значение 0 в ответ на эти четыре бита, полученные от счетчика 402 и представляющие любые из цифр 2, 2, 7, 9 или 11. Двоичный уровень, выданный логической сетью 442, подается на входной сигнальный терминал "1" мультиплексора 434. Результирующий выход мультиплексора 434 подается на элемент И 432 для управления заведением информационных бит от мультиплексоров 418 и 420 на регистр обратного магазинного типа 430.

Выходные сигнальные терминалы 0 и 1 мультиплексора 412 соответственно реагируют на выходы логических сетей 444 и 446, обе из которых в свою очередь реагируют на четырехразрядный выход счетчика 402. Сеть 444 выдает двоичный выход 1 в ответ на выходные биты счетчика 402, представляющие собой любую из цифр 1 - 3, 5 - 7 или 9 - 11; логическая сеть 444 выдает двоичный выход 0 в ответ на четырехразрядный выход счетчика 402, представляющий собой любую из цифр 0, 4 или 8.

Логическая сеть 446 реагирует на четырехразрядный выход счетчика 402 для получения двоичного уровня 1 в ответ на выход счетчика, представляющий собой любую из цифр 1, 2, 4 или 6 - 11. Двоичный уровень 0 получается от логической сети 446 в ответ на отсчет счетчика 402, представляющий собой любую из цифр 0, 3 или 5.

Мультиплексор 416 содержит один управляющий входной терминал, первый и второй выходной терминал и четыре входных сигнальных терминала, обозначенных как первый и второй входной сигнальный терминал "0" и первый и второй входной сигнальный терминал "1". В ответ на двоичный ноль, подаваемый на входной управляющий терминал, двоичные уровни на первом и втором входном сигнальном терминале "0" соответственно заводятся на первый и второй выходной терминал мультиплексора; в ответ на двоичную единицу на входных управляющих терминалах уровни на первом и втором сигнальном терминале "1" соответственно заводятся на первый и второй выходной терминал мультиплексора.

Наименее значимый выходной бит и следующий за ним наименее значимый выходной бит счетчика 402, представляющие собой цифры 0 - 3, соответственно подаются на первый и второй входной сигнальный терминал 0 мультиплексора 416 и заводятся на первый и второй выходной терминал мультиплексора, а оттуда - на управляющие входы мультиплексора 420, в ответ на выход двоичного 0 источника 408, приложенный к управляющему входу мультиплексора 416. Первый и второй входной сигнальный терминал 1 мультиплексора 416 соответственно реагирует на первый и второй выходной бит логической сети 448, которая в свою очередь реагирует на все четыре выходных бита счетчика 402. В ответ на отсчет счетчика 402, представляющий собой цифру 0, логическая сеть 448 выдает уровень двоичного 0 на каждый - первый и второй - входной сигнальный терминал 1 мультиплексора 416.

В ответ на счетчик 402, выдающий сигнал, представляющий собой цифры 5, 8 и 10, сигнал двоичной 1 подается сетью 448 на первый входной сигнальный терминал "1" мультиплексора 416, тогда как уровень 0 подается на второй входной сигнальный терминал "1" мультиплексора. Для всех других цифровых значений выходов счетчика 402 уровень двоичного 0 подается логической сетью 448 на первый входной "1" терминал мультиплексора 416, тогда как уровень двоичной 1 подается на второй входной терминал 1 мультиплексора 416. Поэтому в ответ на управляющий источник 408, выдающий уровень двоичной 1, когда счетчик 402 выдает двоичную последовательность 0000, мультиплексор 416 подает сигнальные биты 00 на управляющий вход мультиплексора 420 для заведения сигнала у выхода Q триггера 424 на выход мультиплексора 420. Тогда как источник 408 выдает уровень двоичной 1, а счетчик 402 выдает двоичный сигнал, связанный с цифрами 5, 8 и 10, мультиплексор 416 подает уровни сигнала 1 и 0 на управляющие входы мультиплексора 420, заводя выход P1 кодера 20 на выход мультиплексора 420. В ответ на источник 408, выдающий уровень двоичной 1, когда счетчик 402 выдает двоичный сигнал, связанный с цифрами 1, 2, 3, 4, 6, 7, 9 и 11, мультиплексор 416 подает в мультиплексор 420 сигнальные биты 0 и 1, заставляя мультиплексор 420 подавать выход P2 кодера 20 на входной сигнальный терминал регистра обратного магазинного типа 430.

Сигналы каналов I и Q, полученные от регистра 430, имеют последовательности, идентичные последовательностям, полученным от демультиплексора 242 для скоростей пунктурирования 2/3 и 6/7. Схемы фиг. 4 обрабатывают последовательности P1 и P2, полученные от кодера 20 на параллельной основе. Параллельные последовательности пунктурируются регистром обратного магазинного типа 432, выдающим параллельные каналы I и Q. Схемы фиг. 4 не содержат ПЗУ и связанную с ним управляющую схему, которая требуется в схемах на фиг. 2.

Однако схемы фиг. 4 не имеют преимущества универсальной применимости ко всем оптимальным скоростям пунктурирования, описанным Ясудой и др.

На фиг. 5 показана блок-схема второго варианта реализации пунктурирующего декодера 64, особенно применимого для кодов пунктурирования 2/3 и 6/7. Устройство, изображенное на фиг. 5, реагирует на выходы I и Q демодулятора 62 и содержит источник символьных синхроимпульсов с волной вида меандра 502, имеющий частоту, равную удвоенной частоте символов, выдаваемых демодулятором 62, и источник информационных синхроимпульсов с волной в виде последовательности прямоугольных импульсов 504. Обычное устройство синхронизации (не показано) синхронизирует источники символов и информационных синхроимпульсов 502 и 504 относительно символов I и Q, получаемых от демодулятора 62. Устройство на фиг. 5 также содержит управляющий источник 506, селективно имеющий значения 0 и 1, соответственно указывающие на пунктурированные коды 2/3 и 6/7. Выход источника 506 управляет последовательностями бит источников 502 и 504. Поскольку источник символьных синхроимпульсов 502 - это волна вида меандра, полученная при этом последовательность это 101010101010 и т.д. для обоих пунктурированных кодов; для пунктурированного кода 2/3 выход источника информационных синхроимпульсов 504 - это повторяющаяся пунктурированная последовательность 100010100010 и т.д.; для пунктурированного кода 6/7 повторяющаяся пунктурированная последовательность информационных синхроимпульсов - это 10101010101000 и т.д. Период каждого двоичного ноля и одно значение в предыдущей последовательности те же самые, т.е. 12,5 нанос.

Приспособление, представленное на фиг. 5, выдает последовательности G1 и G2, которые подаются на декодер Viterbi 66, а также сигналы ER1 и ER2, имеющие значения двоичной 1, когда биты G1 и G2 имеют значения, идеально соответствующие значениям последовательностей P1 и P2; сигналы ER1 и ER2 имеют уровни двоичного 0, когда отсутствует предсказуемое соответствие между значениями бит G1 и G2 и P1 и P2, т.е. когда G1 и G2 - это фиктивные биты. Последовательности бит G1, G2, ER1 ER2 не имеют одинаковой длины для каждого принимаемого символа. Для пунктурированного кода 2/3 длина каждого третьего бита в последовательностях G1, G2, ER1, ER2 в два раза больше, чем у остальных бит и занимает два периода выходного сигнала источника синхроимпульсов 502. Для пунктурированного кода 6/7 каждый седьмой бит в последовательностях G1, G2, ER1, ER2 в два раза длиннее остальных бит этих последовательностей и занимает два периода источника синхроимпульсов 502.

С этой целью последовательные выходные биты I и Q демодулятора 62, т.е. I(0), I(1), I(2) и т.д. и Q(0), Q(1), Q(2) и т.д., подаются на мультиплексор 508, который переключается с частотой, в два раза большей частоты символов I и Q, в ответ на последовательные уровни двоичных 1 и 0, полученные от делящего на два делителя частоты 509, который в свою очередь реагирует на выход источника символьных синхроимпульсов 502. Мультиплексор 508 реагирует на выход делителя 509 тем же самым образом, каким мультиплексор 304 реагирует на выходы I и Q демодулятора 62, что заставляет выход мультиплексора 508 быть в виде последовательности бит I(0), Q(0), I(1), Q(1), I(2), Q(2) и т.д.

Последовательность бит, формируемая мультиплексором 508, подается на вход D D-триггера 510, тактовый вход которого реагирует на выход с волной в виде меандра источника синхроимпульсов 502 и выход Q, заводимый на мультиплексор 514, и на вход D D-триггера 512, тактовый вход которого реагирует на выход с волной в виде последовательности прямоугольных импульсов генератора информационных синхроимпульсов 504. Триггер 512 включает в себя выход Q, реагирующий на двоичные последовательности, подаваемые на D, и на тактовые входы триггера, причем с этого выхода снимается последовательность G1. Поскольку информационный тактовый вход триггера 512 от источника 504 пунктурирован, состояние триггера не меняется при каждом изменении бит I и Q, подаваемых на мультиплексор 508. Поэтому для пунктурированного кода 2/3 выход триггера 512 - это последовательность I(0), Q(0), Q(0), Q(1), I(2), I(2), I(3), Q(3), Q(3) и т.д.; для пунктурированного кода 6/7 выход триггера 512 - это последовательность I(0), Q(0), I(1), I(2), Q(2), I(3), Q(3). Для пунктурированного кода 2/3 указывающая на "фиктивный" бит схема, описанная выше, посылает ИНФРА-сигнал, что значения бит Q(0), I(2), Q(3) на выходе триггера G1 декодер 66 должен проигнорировать, поскольку это "фиктивные" биты. Для пунктурированного кода 6/7 указывающая на "фиктивные" биты схема дает сигнал, что биты Q(0), I(1), Q(3) должны быть проигнорированы как "фиктивные".

Чтобы получить последовательность G2, выходы мультиплексора 508 и выход Q триггера 510 подаются на мультиплексор 514, управляющий вход которого реагирует на выход вентиля И 516. Один вход элемента И 516 реагирует на выход управляющего источника 506, чтобы заблокировать элемент И 516 в ответ на управляющий источник 506, выдающий уровень двоичного 0, связанный с пунктурированным кодом 2/3.

Таким образом, уровень двоичного 0 всегда подается на управляющий вход мультиплексора 514, тогда когда выбирается пунктурированный код 2/3, что вводит выход мультиплексора 508 на D-вход триггера 518, чей синхронизирующий вход присоединен к выходу источника информационных синхроимпульсов 504, а с выхода Q которого получается последовательность бит G. Для пунктурированного кода 2/3 выход триггера 518 представляет собой последовательность Q(0), I(1), I(1), I(2), Q(2), Q(2), Q(3), I(1) и т.д. В этой последовательности нет фиктивного бита. Вторые значения I(1), Q(2) считываются и интерпретируются как информационные биты декодером 66 и схемами, приводимыми в действие декодером.

Для пунктурированного кода 6/7 один вход и элемент И 516 реагируют на выход двоичной единицей управляющего источника 506 и сигнал с двоичной единицей подается на другой вход элемента И 516 один раз в ответ на каждые шесть выходов с двоичной единицей источника информационных синхроимпульсов. С этой целью выход источника информационных синхроимпульсов 504 подается на счетчик 520, имеющий шесть состояний, последовательно связанных с 000, 001, 010, 011, 100, 101. Результирующий трехбитовый выход счетчика 520 подается на логическую схему 522, которая выдает уровень двоичной единицы в ответ на выход счетчика 520, имеющий значение 011. Мультиплексор 514 реагирует на выход двоичной единицы элемента И 516 для заведения двоичного уровня на выходе Q триггера 510 на вход D триггера 518 с исключением выхода мультиплексора 508. Для всех других ситуаций выход мультиплексора 508 заводится через мультиплексор 514 на вход D триггера 518. Таким образом, результирующая последовательность G на выходе Q триггера 518 - это Q(0), I(1), Q(1), Q(1), Q(2), Q(2), Q(3), I(4). Указывающая на "фиктивный" бит схема дает сигнал, что первые появления Q(2) и Q(3) в этой последовательности - это "фиктивные" биты.

Схема для указания "фиктивных" бит в последовательностях бит G1 и G включает в себя ПЗУ.

ПЗУ 524 содержит управляющий вход, реагирующий на выход управляющего источника 506 так, что пунктурирующие коды, связанные с пунктурированными кодами 2/3 и 6/7, соответственно выбираются в ответ на выход управляющего источника 506, имеющего уровни двоичных 0 и 1.

ПЗУ 524 также содержит многобитовый адресный вход 526, реагирующий на трехразрядный выход счетчика 520. ПЗУ 524 содержит пару одноразрядных выходов ER1 и ER2, на которых формируются уровни двоичных 1 и 0, которые указывают на то, настоящие или "фиктивные" биты двоичные уровни в последовательностях G1и G2, полученных от выходов Q триггеров 512 и 518, соответственно. ПЗУ 524 запрограммировано таким образом, что в ответ на двоичный 0 на выходе управляющего источника 506 последовательности бит на выходах ER1 и ER2 ПЗУ - это соответственно 101010 и 111111 в ответ на шесть последовательных выходных отсчетов счетчика 520. В ответ на выход с двоичной 1 управляющего источника 506 ПЗУ 524 реагирует на шесть последовательных выходных отсчетов счетчика 520 для получения значения ER1 и ER2 в соответствии с 100101 и 111010 соответственно. Уровни двоичного 0, полученные от ПЗУ 524, заводятся на декодер Viterbi 66 для подачи сигнала о том, какие из бит в последовательностях бит G1 и G2 "фиктивные".

Устройство, показанное на фиг. 5, можно также использовать для ситуации, когда каждый из выходов I и Q демодулятора 62 - это многобитовый параллельный сигнал. В таком случае каждый из дополнительных бит I и Q заводится на схему, тождественную мультиплексору 508, триггерам 510, 512 и 518, а также на мультиплексор 514. Управляющие входы мультиплексоров для дополнительных бит, соответствующие мультиплексорам 508 и 514, идентичны представленным на фиг. 5. Синхронизирующие входы триггеров для дополнительных бит, соответствующие триггерам 510, 512 и 518, тождественны тем, что показаны на фиг. 5.

Хотя здесь были описаны и проиллюстрированы многие конкретные варианты реализации этого изобретения, будет ясно, что различия в подробностях конкретно проиллюстрированных и описанных вариантов реализации могут осуществляться не отходя от рамок этого изобретения, которые не определяются в прилагаемой формуле изобретения.

Цифровые информационные сигналы (в частности кодированные сигналы телевизионной программы) передаются от передатчика на наземный приемник посредством сверточного кодирования и преобразования в первый и второй сигнал в течение разных периодов, представляя сигнал со скоростью 1/2. В течение разных периодов два сигнала комбинируются и пунктурируются в один последовательный пунктурированный поток бит для получения сверточно-кодированного сигнала с упреждающим исправлением ошибок, имеющего выбираемую вручную или автоматически скорость, например, скорость 2/3 или 6/7. Сигналы, кодируемые в различных переменных скоростях, передаются во взаимно исключающие друг друга моменты времени на первом и втором энергетическом уровне на приемник через спутник. Параллельные пунктурированные потоки бит с переменными скоростями получаются одновременно и одновременно модулируют пару ортогональных носителей (несущих) (QPSK). Улучшенный способ пунктурирования дает возможность обрабатывать все оптимальные пунктурированные коды и предполагает использование пунктурированного генератора синхроимпульсов, мультиплексора, регистра обратного магазинного типа, ЗУПВ, ПЗУ, источника управления скоростью. Пунктурированный генератор синхроимпульсов используется для получения пары серий импульсов, содержащих последовательные биты каналом I и Q и фиктивные биты, вставленные в последовательный сигнал. Приемник реагирует на носитель QPSK и выдает сначала последовательный сигнал, имеющий один последовательный поток чередующихся бит обоих каналов I и Q. Далее они последовательно перегруппируются как сигналы I и Q в тех же самых временных интервалах. 4 с. и 17 з.п. ф-лы, 5 ил., 11 табл.

| EP, патент, 0301161, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-08-10—Публикация

1994-05-24—Подача