Изобретение относится к вычислительной технике и может использоваться в синтезаторах частот и цифровых устройствах фазовой синхронизации.

Для изменения направления счета используются счетчики импульсов на основе синхронных триггеров с объединенными тактовыми входами, причем выходы триггеров младших разрядов счетчика соединены с входами триггеров в смежных младших разрядах через комбинационные логические блоки [1]. Направление счета в таких устройствах задается подаваемым на управляющие входы коммутаторов напряжением того или иного логического уровня. Недостатком известных реверсивных счетчиков является жесткость их структуры, исключающая возможность электронного регулирования модуля счета.

Известны также счетчики импульсов с произвольным модулем счета, также состоящие из синхронных триггеров с управляемыми комбинационными блоками между ними, общее число состояний которых, т.е. модуль счета, может изменяться при поступлении управляющего сигнала [2]. Недостатком таких устройств является ограниченный набор значений модуля счета, а также невозможность изменения направления счета.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является общеизвестный накапливающий сумматор [3], работающий в режиме прибавления-вычитания единицы. Устройство-прототип состоит из подключенного тактовым входом к зажиму входных импульсов регистра и параллельного сумматора. Если входным числом сумматора служит единица, а сам сумматор работает с числами в дополнительном коде, то он выполняет функции блока добавления-вычитания единицы. Для управления направлением счета устройство достаточно снабдить управляющим входом, соединенным с зажимом сигнала направления счета. Недостатком устройства-прототипа является невозможность электронной перестройки модуля счета.

Целью настоящего изобретения является обеспечение возможности реверса счета в счетчике импульсов с переменным, задаваемым электронным путем модулем счета. Такое устройство необходимо, в частности, для осуществления синтеза частот и цифровой фазовой синхронизации способом управляемой селекции фазы многофазного опорного генератора (см., например, [4]).

Поставленная цель достигается за счет введения в накапливающий сумматор на основе подключенного тактовым входом к зажиму входных импульсов регистра и блока добавления-вычитания единицы, соединенного управляющим входом с зажимом сигнала направления счета дополнительных блоков: компаратора, мультиплексора, блока конъюнкторов, элемента ИЛИ и элемента И. Указанные блоки отвечают за переход устройства из состояния (M-1) в состояние 0 в режиме суммирования импульсов и за переход из состояния 0 в состояние (М-1) в режиме вычитания импульсов, где М - значение задаваемого извне модуля счета.

Для этого многоразрядный выход блока добавления-вычитания единицы присоединен к первому многоразрядному входу компаратора и через блок конъюнкторов, у которых вторые входы подключены к выходу компаратора, - к многоразрядному входу регистра. Многоразрядный выход регистра соединен одновременно с группой первых входов мультиплексора и с группой входов элемента ИЛИ-НЕ. Группа вторых входов мультиплексора и второй многоразрядный вход компаратора подключены к группе зажимов цифрового кода модуля счета, а выход элемента ИЛИ-НЕ через элемент И присоединен к адресному входу мультиплексора. Оставшийся вход элемента И подключен к зажиму сигнала направления счета, а многоразрядный вход блока добавления-вычитания единицы присоединен к группе выходов мультиплексора.

Блок добавления-вычитания единицы в предпочтительном варианте исполнения состоит из разрядных логических схем. Первые входы разрядных логических схем образуют многоразрядный вход, первые выходы - многоразрядный выход, а объединенные управляющие входы - управляющий вход блока добавления-вычитания единицы. При этом второй выход каждой разрядной логической схемы соединен с вторым входом смежной старшей разрядной логической схемы, а второй вход младшей разрядной логической схемы подключен к шине логической единицы.

Каждая разрядная логическая схема в зависимости от управляющего сигнала может работать как полусумматор или как полувычитатель. Она состоит из двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, причем объединенные первые входы обоих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ служат первым входом разрядной логической схемы, а объединенные вторые входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И - вторым входом разрядной логической схемы. Второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ служит управляющим входом разрядной логической схемы. Выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является первым выходом, а выход элемента И, у которого оставшийся вход соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, - вторым выходом разрядной логической схемы.

Компаратор может быть построен в виде группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы каждого из которых являются входами первого и второго сравниваемых чисел соответствующих разрядов, а выходы соединены с соответствующими входами выходного элемента ИЛИ-НЕ.

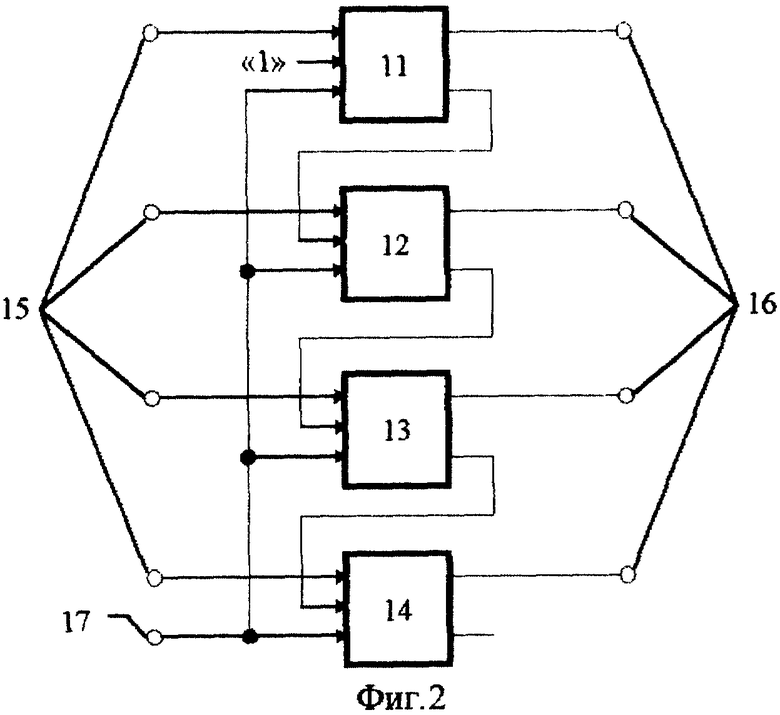

Фиг. 1 - электрическая функциональная схема реверсивного счетчика импульсов с переменным модулем счета согласно настоящему изобретению.

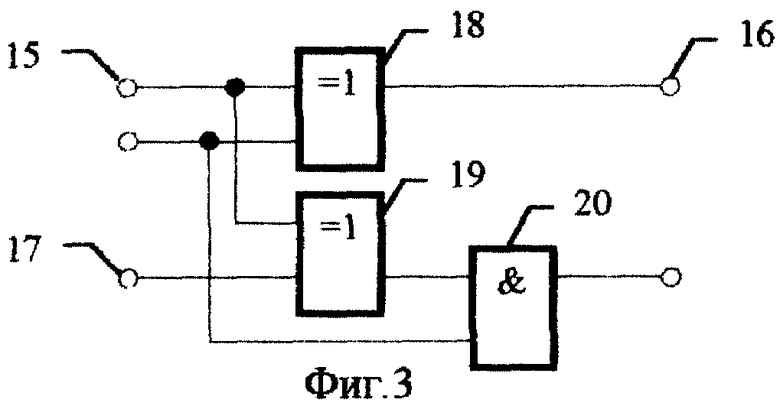

Фиг.2 - схема предпочтительного варианта блока добавления-вычитания единицы, входящего в состав реверсивного счетчика импульсов с переменным модулем счета (фиг.1).

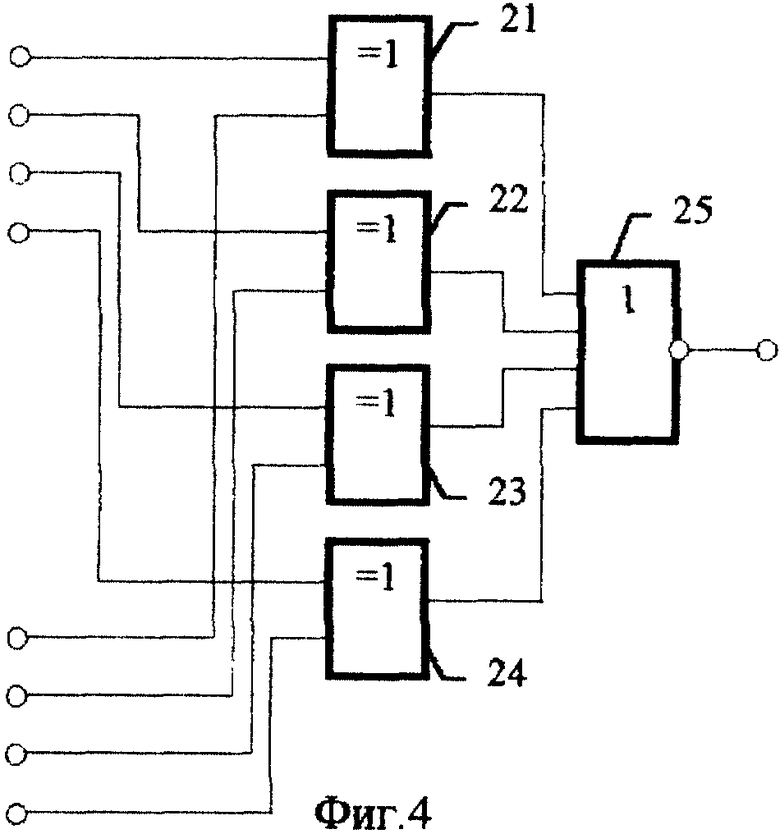

Фиг. 3 - вариант построения разрядной логической схемы в составе блока добавления-вычитания единицы, показанного на фиг.2.

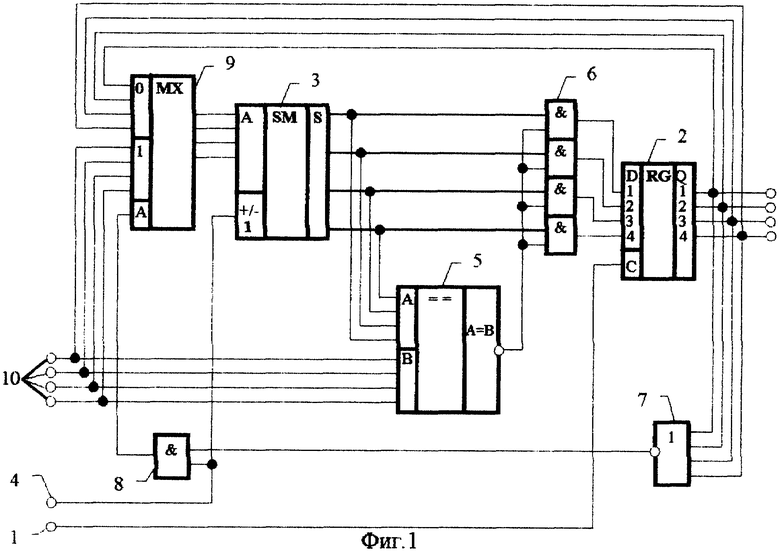

Фиг. 4 - функциональная схема компаратора, входящего в структуру реверсивного счетчика импульсов с переменным модулем счета (фиг.1).

Показанная на фиг.1 функциональная схема реверсивного счетчика импульсов с переменным модулем счета состоит из подключенного тактовым входом к зажиму входных импульсов 1 регистра 2 и блока 3 добавления-вычитания единицы, соединенного управляющим входом с зажимом 4 сигнала направления счета. Кроме того схема включает компаратор 5, блок 6 конъюнкторов, элемент 7 ИЛИ-НЕ, элемент 8 И и мультиплексор 9.

Многоразрядный выход блока 3 добавления-вычитания единицы присоединен к первому многоразрядному входу компаратора 5 и через блок 6 конъюнкторов, у которых вторые входы подключены к выходу компаратора 5, - к многоразрядному входу регистра 2. Многоразрядный выход регистра 2 соединен одновременно с группой первых входов мультиплексора 9 и с группой входов элемента 7 типа ИЛИ-НЕ. Группа вторых входов мультиплексора 9 и второй многоразрядный вход компаратора 5 подключены к группе зажимов 10 цифрового кода модуля счета, а выход элемента 7 ИЛИ-НЕ через элемент 8 И присоединен к адресному входу мультиплексора 9. Оставшийся вход элемента 8 И подключен к зажиму 4 сигнала направления счета, а многоразрядный вход блока 3 добавления-вычитания единицы присоединен к группе выходов мультиплексора 9.

Блок добавления-вычитания единицы, предпочтительная схема которого представлена на фиг.2, состоит из идентичных разрядных логических схем 11...14. Первые входы разрядных логических схем образуют многоразрядный вход 15, первые выходы - многоразрядный выход 16, а объединенные управляющие входы - управляющий вход 17 блока добавления-вычитания единицы. Второй выход каждой разрядной логической схемы соединен с вторым входом смежной старшей разрядной логической схемы, а второй вход младшей разрядной логической схемы подключен к шине логической единицы.

Каждая разрядная логическая схема 11...14 представляет собой универсальный полусумматор-полувычитатель. Структуры полусумматора и полувычитателя синтезируются формально и являются общеизвестными [5]. Показанная на фиг.3 разрядная логическая схема получена комбинацией названных блоков и состоит из двух элементов 18, 19 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента 20 И. Объединенные первые входы обоих элементов 18 и 19 ИСКЛЮЧАЮЩЕЕ ИЛИ служат первым входом разрядной логической схемы, а объединенные вторые входы первого элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента 20 И - вторым входом разрядной логической схемы. Второй вход второго элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ служит управляющим входом разрядной логической схемы. Выход первого элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ является первым выходом, а выход элемента 20 И, у которого оставшийся вход соединен с выходом второго элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, - вторым выходом разрядной логической схемы 11...14.

Схема компаратора, изображенная на фиг. 4, содержит группу элементов 21. . . 24 ИСКЛЮЧАЮЩЕЕ ИЛИ, входы каждого из которых являются входами первого и второго сравниваемых чисел соответствующих разрядов, а выходы соединены с соответствующими входами элемента 25 ИЛИ-НЕ. Первые входы всех элементов 21. . . 24 ИСКЛЮЧАЮЩЕЕ ИЛИ служат первым многоразрядным входом 26, а вторые их входы - вторым многоразрядным входом 27 компаратора 5. Выход элемента 25 ИЛИ-НЕ является выходом 28 компаратора.

Рассмотрим вначале принципы действия основных блоков, входящих в устройство.

Компаратор 5, схема которого изображена на фиг.4, при равнозначности сравниваемых чисел на своих первом 26 и втором 27 многоразрядных входах вырабатывает на своем выходе 28 напряжение логического нуля, в противном случае на выходе 28 удерживается уровень логической единицы.

Разрядная логическая схема 11 (идентичная остальным схемам 12...14 - фиг. 2), представленная на фиг.3, в зависимости от уровня управляющего сигнала на входе 17 выполняет либо сложение двух одноразрядных двоичных чисел, либо их вычитание без учета сигнала переноса или заема. Если управляющий сигнал нулевой, то схема работает как полусумматор. При этом второй элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ не инвертирует логического уровня на входе 15 перед его поступлением на вход элемента 20 И. Поэтому на первом выходе 16 вырабатывается значение суммы  , а на втором выходе (выходе элемента 20) - значение переноса с1=ab, где а и b - значения входных одноразрядных операндов. Если управляющий сигнал на входе 17 имеет уровень логической единицы, то схема работает как полувычитатель. В данном режиме второй элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ инвертирует логический уровень со входа 15 перед его передачей на вход элемента 20 И. За счет этого схема вырабатывает на своем первом выходе 16 значение разности, которое также равно

, а на втором выходе (выходе элемента 20) - значение переноса с1=ab, где а и b - значения входных одноразрядных операндов. Если управляющий сигнал на входе 17 имеет уровень логической единицы, то схема работает как полувычитатель. В данном режиме второй элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ инвертирует логический уровень со входа 15 перед его передачей на вход элемента 20 И. За счет этого схема вырабатывает на своем первом выходе 16 значение разности, которое также равно  , а на втором выходе - значение заема, равное

, а на втором выходе - значение заема, равное  .

.

Описанные разрядные логические схемы позволяют построить упрощенную структуру блока 3 добавления-вычитания единицы, в которой первый операнд является многоразрядным двоичным числом, а второй - одноразрядной единицей с тем или иным знаком. В схеме фиг.2 разрядные логические схемы соединены последовательно по цепи распространения сигнала переноса-заема. Число, к которому добавляется или из которого вычитается единица, поступает на входы 15, т.е. на первые входы всех разрядных логических схем 11...14. Второй вход разрядной логической схемы 11 младшего разряда подключен к шине логической единицы. Управляющие входы всех разрядных логических схем 11...14 подключены к входу 17 управляющего сигнала. Если на этом входе 17 присутствует логический "0", то схема осуществляет прибавление единицы к входному многоразрядному двоичному числу, если логическая "1" - вычитание. Результат образуется на группе первых выходов 16 разрядных логических схем 11...14.

Реверсивный счетчик импульсов с переменным модулем счета (фиг.1) работает в следующем порядке. Направление счета устанавливается логическим уровнем сигнала на зажиме 4 сигнала направления счета: при нулевом его уровне осуществляется режим суммирования, при единичном - режим вычитания. Значение модуля счета задается двоичным числом M, поступающим на группу зажимов 10 цифрового кода модуля счета.

В режиме суммирования, когда на зажиме 4 сигнала направления счета присутствует уровень логического нуля, блок 3 добавления-вычитания единицы прибавляет единицу к числу, поступающему на его многоразрядный вход с многоразрядного выхода мультиплексора 9. Так как на одном из входов элемента 8 И удерживается уровень логического "0" с зажима 4 сигнала направления счета, то на его выходе также вырабатывается уровень логического "0". Поэтому мультиплексор по адресу "0" подключает к своему многоразрядному выходу первую группу своих входов, т.е. выходы регистра 2, являющиеся выходами устройства в делом. На выходе блока 3 добавления-вычитания единицы формируется следующее значение выходного числа устройства, которое в момент поступления очередного входного импульса на зажим 1 записывается в регистр 2 через блок 6 конъюнкторов, у которых на вторых объединенных входах имеется уровень логической "1" с выхода компаратора 5. Так продолжается до тех пор, пока компаратор 5 не зафиксирует равенство подготовленного блоком 3 добавления-вычитания единицы нового значения числа значению модуля счета М. Тогда компаратор 5 выработает на своем выходе уровень логического "0", что обусловливает возникновение нулевых уровней напряжения на всех информационных входах регистра 2 и запись числа 0 в регистр 2 в момент прихода очередного входного импульса на зажим 1. Таким образом, в режиме суммирования входных импульсов выходное число устройства циклически принимает состояния от 0 до (М-1).

В режиме вычитания на зажиме 4 сигнала направления счета присутствует уровень логической "1", в результате чего блок 3 добавления-вычитания единицы уменьшает на 1 число, поступающее на его многоразрядный вход с выхода мультиплексора 9. Если выходное число устройства на выходе регистра 2 больше 0, то элемент 7 ИЛИ-НЕ вырабатывает уровень логического "0", который через элемент 8 И удерживает равным "0" адрес мультиплексора 9. Поэтому мультиплексор 9 передает на вход блока 3 добавления-вычитания единицы выходное число регистра 2 и с каждым входным импульсом на зажиме 1 происходит уменьшение на 1 этого числа. Когда выходное число устройства достигает в процессе вычитания 1 нулевого значения, элемент 7 ИЛИ-НЕ вырабатывает на своем выходе уровень логической "1", и ввиду совпадения единиц на входах элемента 8 И адрес мультиплексора 9 изменяется с "0" на "1". Мультиплексор 9 подключает к входу блока 3 добавления-вычитания единицы число М с зажимов 10 цифрового кода модуля счета, поэтому на выходе блока 3 добавления-вычитания единицы образуется число, равное (M-1). В момент поступления очередного входного импульса на зажим 1 в регистр записывается именно это число (М-1). Таким образом в данном режиме устройство циклически принимает состояния от (М-1) до 0.

Реверсивный счетчик импульсов с переменным модулем счета предназначен для использования в технике синтеза частот и цифровой фазовой синхронизации с расширенным частотным диапазоном.

Литература

1. Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. - М.: Мир, 1982, стр. 348, рис.20.7.

2. Алексенко А.Г., Шагурин И.И. Микросхемотехника. - М.: Радио и связь, 1990, стр.222, рис.5.9.

3. Угрюмов Е. П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987, стр.196, рис. 11.14.

4. Устройство фазовой синхронизации. Патент РФ 2119717, бюл. 1998, 27.

5. Токхейм Р. Основы цифровой электроники. - М.: Мир, 1988, стр.213, рис.9.4, стр.219, рис.9.9.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА | 2000 |

|

RU2170490C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С НОРМИРОВАННЫМ ФАЗОВЫМ ШУМОМ | 1998 |

|

RU2133552C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2133076C1 |

| Устройство для контроля состояния канала связи | 1987 |

|

SU1434550A1 |

| СУММАТОР С ПЕРЕМЕННЫМ МОДУЛЕМ СЛОЖЕНИЯ | 2000 |

|

RU2183347C2 |

Изобретение относится к вычислительной технике и может быть использовано в синтезаторах частот и цифровых устройствах фазовой синхронизации. Техническим результатом является обеспечение возможности реверса счета в счетчике импульсов с переменным задаваемым электронным путем модулем счета. Устройство содержит мультиплексор, компаратор, регистр, блок добавления-вычитания единицы, блок конъюнкторов, элементы И, ИЛИ-НЕ. 3 з.п. ф-лы, 4 ил.

| УГРЮМОВ Е.П | |||

| Проектирование элементов и узлов ЭВМ | |||

| - М.: Высшая школа, 1987, с.196, рис | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ТИТЦЕ У., ШЕНК К | |||

| Полупроводниковая схемотехника | |||

| Справочное руководство | |||

| - М.: Мир, 1982, с.348, рис | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| АЛЕКСЕНКО А.Г., ШАГУРИН И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1990, с.222, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ТОКХЕЙМ Р | |||

| Основы цифровой электроники | |||

| - М.: Мир, с.213, рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1574146A1 |

| ЮЗНАЯ .п-г:йГ1<9"Т?ХНЙЧЕ1Нй^|^.^^. | 0 |

|

SU281094A1 |

| Молотильный барабан | 1940 |

|

SU62541A1 |

| US 5146479 А, 08.09.1992. | |||

Авторы

Даты

2002-02-20—Публикация

2000-04-07—Подача