Од СП 4

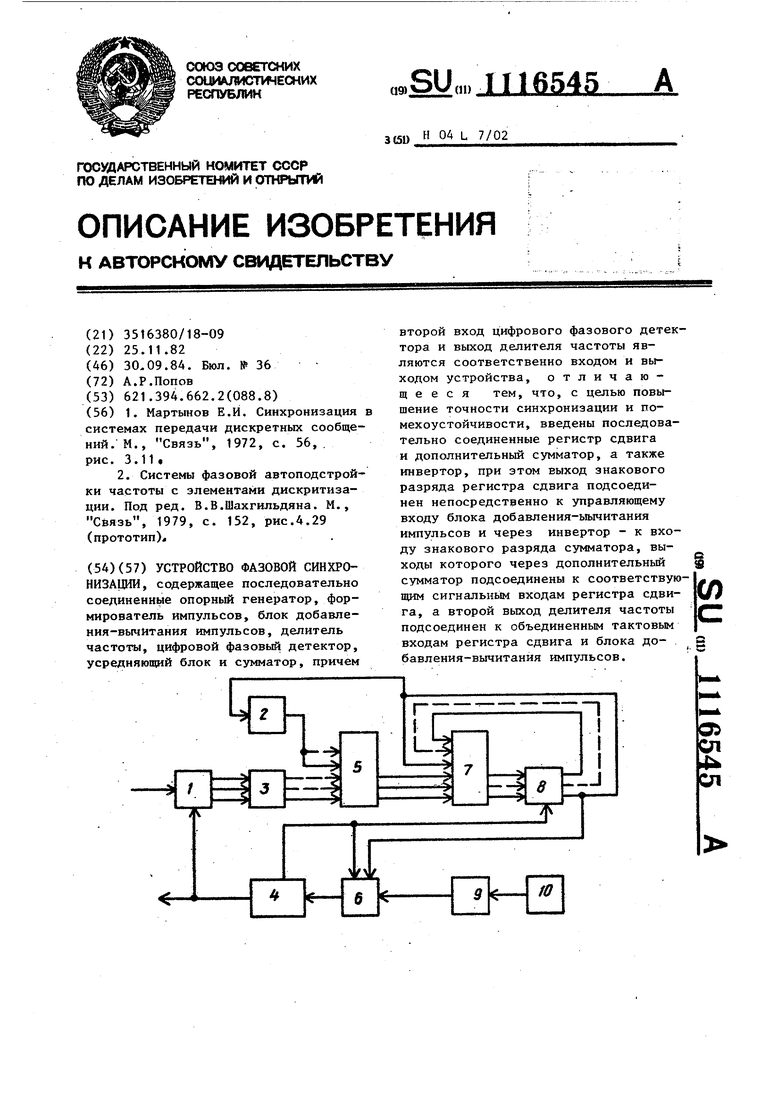

сл 1 Изобретение относится к технике электросвязи и может быть испрльзов но для фазовой синхронизации в приемниках дискретнс й информации. Известно устройство фазовой синхронизации, содержащее последовательно соединенные фазовьм дискри минатор, первый усредняющий блок, второй усредняюпщй блок, астатическ звено регулирования, первый блок добавления - вычитания импульсов, опорный генератор, второй блок добавления-вычитания импульсов и делитель частоты, выход, которого подсоединен к входу фазового дискриминатора, а первый и второй выходы первого усредняющего блока подсоеди нены соответственно к второму и третьему входам второго блока добав ления - вычитания импульсов С1. Недостатком известного устройства фазовой синхронизации являются низкие точность синхронизации и помехоустойчивость . Наиболее близким к предлагаемо является устройство фазовой синхронизации, содержащее последовательно соединенные опорный генератор, форм рователь импульсов, блок добавления вычитания импульсов, делитель частот цифровой фазовый детектор, усредняющий блок и сумматор, причем второй вход цифрового фазового детектора и выход делителя частоты являются соответственно входом и выходом устройства, первый и второй выходы цифрового фазового детектора через ЦИФРОВОЙ интегратор и сумматор подсоединены соответственно .к второму и третьему входам блока добавлениявычитания импульсов, а дополнительн вход цифрового интегратора подключе к дополнительному выходу опорного генератора 21. Недостатком известного устройст фазовой синхронизации являются низкие точность синхронизации и помехо устойчивость. Цель изобретения - повышение то ности синхронизации и помехоустойчивости. Поставленная цель достигается тем, что в устройство фазовой синхронизации, содержащее последователь соединенные опорный генератор, формироватепь импульсов, блок добавления-вычитания импульсов, делитель частоты, цифровой фазовый детектор. 5 усредняющий блок и сумматор, причем второй вход цифрового фазового детектора и выход делителя частоты являются соответственно входом и выходом устройства, введены последовательно соединенные регистр сдвига и дополнительный сумматор, а также инвертор, при этом выход знакового разряда регистра сдвига подсоединен непосредственно к управляющему входу блока добавления-вычитания импульсов и через инвертор - к входу знакового разряда сумматора, выходы которого через дополнительный сумматор подсоединены к соответствующим сигнальным входам регистра сдвига, а второй выход-делителя частоты подсоединен к объединенным тактовым входам регистра сдвига и блока добавления-вычитания импульсов. На чертеже приведена структурная электрическая схема устройства фазовой синхронизации. Устройство фазовой синхронизации содержит цифровой фазовый детектор 1, инвертор 2, усредняющий блок 3, делитель 4 частоты, сумматор 5, блок 6.добавления-вычитания импульсов, дополнительный сумматор 7, регистр сдвига 8, формирователь 9 импульсов и опорный генератор 10. Устройство фазовой синхронизации работает следующим образом. На второй вход цифрового фазового детектора 1 поступает входной сигнал. подверженный действию помех, а на первый вход цифрового фахового детектора 1 - последовательность импульсов с выхода делителя 4 частоты. В зависимости от фазового сдвига импульсов делителя 4 частоты и входного сигнала на выходе цифрового фазового детектора 1 формируется код, абсолютная величина и знак которого соответствуют значению фазового рассогласования входного и выходного сигналов. Если фазовое рассогласование отсутствует, то с выхода цифрового фазового детектора 1 на вход усредняющего блока 3 поступает нулевой код. Усредняющий блок 3 предназначен для уменьшения действия помех на точность подстройки фазы, а также для получения требуемых динамических характеристик. С выхода усредняющего блока 3 на входы сумматора 5 поступает код U , соответствующий значению фазового рассогласования. На вход знакового разряда .

сумматора 5 поступает прямой или дополнительный код постоянного числа С в зависимости от знака числа, хранящегося в регистре 8.

При поступлении прямого кода цисла С происходит его сложение с кодом и усредняющего блока 3, а при поступлении дополнительного кода число С вычитается из U . В дополнительном сумматоре 7 код, хранящийся в регистре 8, складывается с выходным кодом сумматора 5. На тактовый вход регистра 8 поступают импульсы с выхода делителя 4 частоты. С приходом тактового импульса выходной код дополнительного сумматора 7 переписьшается в регистр 8. Знаковый разряд регистра 8 соединен с управляющим входом блока 6 добавления-вычитания импульсов. В зависимости от знака числа, хранящегося в регистре 8, в момент прихода тактового импуль са блок 6 добавления-вычитания вводит дополнительный или стирает один из импульсов в импульсной последовательности на входе блокя делителя 4 частоты. При этом фаза выходного сигнала йзменяетЬя соответственно на величину + Ш /N, где N коэффициент деления делителя частоты |Если с выхода усредняющего блока 3 Снимается нулевой код, число С через сумматор 5 поступает на входы дополнительного сумматора 7 без изменения. Так как код числа С имеет знак, противоположный числу, хранящемуся в регистре 8, то после суммирования

1165454

в каждом такте изменяется знак числа, |хранящегося в регистре В. Количество положительных и отрицательных подстроек совпадает, а частота выходного 5 сигнала равна среднему значению. Если код и больше нуля (меньше нуля), константа (J , компенсирующая рост абсолютной величины числа в регистре 8, вызванный суммированием (вычитанием) кода и, вычитается (добавляется) с частотой, пропорциональной коду (} . При этом разность между числом положительных и отрицательных подстроек определяется величиной и знаком кода и .

Наличие начальной расстройки по частоте между входным и выходным сигналами увеличивает количество значений фазового рассогласования одно.го знака, снимаемых с выхода цифрового фазового детектора 1. Код U усредняющего блока 3 изменяется, пока приращение частоты выходного сигнала не скомпенсирует частотнзто расстройку до остаточной величины, определяемой единицей приращения кода U .

В -предлагаемом устройстве фазовой синхронизации из-за уменьщения начальной расстройки по частоте обеспечивается возможность уменьшения шага коррекции фазы (или соответственно увеличения числа усредняемых значений фазового рассогласования), в результате чего по сравнению с известным устройством фазовой синхронизации повышаются точность синхронизации и помехоустойчивость. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство фазовой синхронизации | 1984 |

|

SU1181159A1 |

| Устройство фазовой синхронизации | 1985 |

|

SU1256226A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1288907A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1358103A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| Цифровое устройство фазовой синхронизации | 1984 |

|

SU1225034A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2010 |

|

RU2423798C1 |

УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ, содержащее последовательно соединенные опорный генератор, формирователь импульсов, блок добавления-вычитания импульсов, делитель частоты, цифровой фазовый детектор, усредняющий блок и сумматор, причем второй вход цифрового фазового детектора и выход делителя частоты являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повышение точности синхронизации и помехоустойчивости, введены последовательно соединенные регистр сдвига и дополнительный сумматор, а также инвертор, при этом выход знакового разряда регистра сдвига подсоединен непосредственно к управляющему входу блока добавления-ыычитания импульсов и через инвертор - к входу знакового разряда сумматора, выходы которого через дополнительный сумматор подсоединены к соответствуюО) щим сигнальным входам регистра сдвига, а второй выход делителя частоты с подсоединен к объединенным тактовым входам регистра сдвига и блока добавления-вычитания импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мартынов Е.И | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М., Связь, 1972, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Системы фазовой автоподстройки частоты с элементами дискритизации | |||

| Под ред | |||

| В.В.Шахгильдяна | |||

| М., Связь, 1979, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

Авторы

Даты

1984-09-30—Публикация

1982-11-25—Подача