Изобретение касается защитного интерфейса мощности.

Предлагаемый интерфейс мощности располагается в схеме между защитным интерфейсом и по крайней мере одним управляемым исполнительным механизмом.

Общеизвестно, что существует необходимость в согласовании выходного сигнала защитного интерфейса, состоящего из двоичных логических сигналов, с мощностью, потребляемой исполнительным механизмом.

Изобретение относится, в частности, к случаю, когда устройство подключается к выходу защитного интерфейса или модулю мажоритарной выборки, подобного описанному в заявке ЕЭС ЕР-526.350.

Упомянутый защитный интерфейс состоит из генератора типа кольцевого мультивибратора, состоящего из непарного количества инверторных элементов, входы питания которых являются функциональными входами интерфейса, в свою очередь подключенными к выходам автоматов.

В случае нарушения питания одного из входов генератор вырабатывает непрерывный сигнал. В случае внутренней неполадки в самом интерфейсе выходной сигнал не изменяется или же переводится в безопасное состояние, при котором колебания в генераторе отсутствуют.

Интерфейс защиты имеет схему, обеспечивающую выпрямление выходных сигналов генератора.

Таким образом, на выходе защитного интерфейса или модуля мажоритарной выборки, состоящего из защитных интерфейсов этого типа, получают сигналы малой мощности с двумя непрерывными логическими уровнями, один из которых соответствует безопасному состоянию.

В результате защитный интерфейс отличается высокой степенью надежности невзирая на все возможные неполадки, которые могут иметь место в нем.

В основу изобретения положена задача создания интерфейса мощности, обеспечивающего управление исполнительным механизмом, без нарушения степени защиты и/или наличия расположенных выше защитного интерфейса или модуля мажоритарной выборки.

Поставленная задача решается тем, что в интерфейсе мощности, имеющем вход для приема непрерывных логических двоичных входных сигналов, средства динамического кодирования непрерывных входных сигналов, средства управления интерфейсом мощности, подключенные к выходу средств динамического кодирования, и средства контроля состояния интерфейса, согласно изобретению интерфейс имеет по крайней мере два высокомощных транзистора, последовательно соединенных с исполнительным механизмом между зажимами источника питания.

При этом каждый транзистор имеет управляющий электрод, соединенный с соответствующим выходом средств управления, а интерфейс снабжен средствами самотестирования, подключенными к средствам контроля и имеющими средства подачи проверочных сигналов, передаваемых средствами управления к управляющим электродам транзисторов, образуя, таким образом, регулятор мощности для интерфейса защиты.

Согласно другому варианту выполнения средства самотестирования имеют средства вырабатывания синхронизирующих сигналов, подключенные к тестовому входу средств управления, а также средства детектирования величины напряжения на зажимах каждого из транзисторов и передачи средствам управления сигналов, имитирующих указанные напряжения, для обеспечения линейной проверки высокомощных транзисторов.

Кроме того, согласно изобретению средства динамического кодирования имеют генератор, вырабатывающий сигналы определенной частоты в случае, если входной сигнал принимает определенное непрерывное первое значение, и непрерывные сигналы, если входной сигнал принимает определенное второе непрерывное значение.

При этом второе непрерывное значение входного сигнала предпочтительно связано с состоянием безопасности исполнительного механизма.

Целесообразно, чтобы средства управления имели программируемую логическую схему, выдающую двум отдельным управляющим выходам, соответственно соединенным с каждым из транзисторов, прерывистые сигналы, когда выходные сигналы средств кодирования являются прерывистыми сигналами.

Кроме того, средства управления имеют средства установки, включенные между программируемой логической схемой и транзисторами для передачи управляющим электродам транзисторов управляющего сигнала насыщения, когда выходной сигнал, сформированный программируемой логической схемой, становится прерывистым сигналом, и блокирующего управляющего сигнала, когда указанный выходной сигнал является непрерывным сигналом.

Предпочтительно, чтобы программируемая логическая схема имела диагностический выход, вырабатывающий прерывистый сигнал в отсутствие внутренней неполадки в интерфейсе и непрерывный сигнал в случае наличия неполадки.

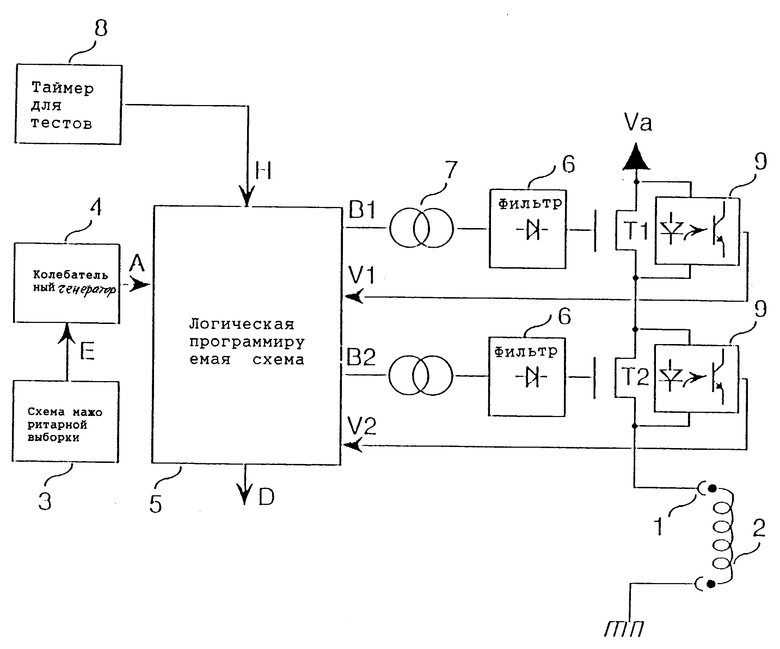

В дальнейшем изобретение поясняется описанием вариантов его выполнения со ссылками на сопровождающий чертеж.

Представленный на чертеже регулятор мощности состоит из двух высокомощных транзисторов Т1 и Т2, например типа МОП (металл - оксид - полупроводник), последовательно подключенных между блоком питания напряжения Va и выходом 1.

Исполнительный механизм 2 подключается между выходом 2 и массой.

Когда достигается насыщение транзисторов Т1 и Т2, напряжение питания Va поступает на зажимы исполнительного механизма 2.

В случае блокировки хотя бы одного из транзисторов на зажимы исполнительного механизма 2 напряжение не поступает.

В нормальном режиме работы выход защитного интерфейса или модуля мажоритарной выборки 3, например, подобного описанному в упомянутой ранее заявке ЕЭС, подключается к входу регулятора мощности, на который она подает логические двоичные непрерывные входные сигналы малой мощности Е. Входные сигналы Е поступают на вход колебательного контура 4, который осуществляет динамическое кодирование входных сигналов Е.

При достижении входным сигналом Е определенного логического уровня, например уровня 1, колебательный контур 4 выдает прерывистый сигнал А определенной частоты, например 500 кГц.

В случае же, если входной сигнал Е достигает второго определенного логического уровня, например уровня 0, колебательный контур 4 отключается и выдает непрерывный сигнал А на выходе.

Выход колебательного контура 4 подключен ко входу программируемой логической схемы 5, которая подает различные управляющие сигналы соответственно В1 и В2 транзисторам Т1 и Т2. В нормальном режиме работы, когда Е=1, схема 5 передает на эти выходы прерывистый сигнал А. Прерывистые сигналы В1, В2 соответственно подаются на управляющие электроды транзисторов Т1 и Т2 через фильтрующую и выпрямительную схему 6.

Предусмотрена схема 7 гальванической изоляции, например, трансформатор, который включен между каждой из схем 6 и соответствующим выходом схемы 5. Прерывистые сигналы В1 и В2 осуществляют, таким образом, регулирование уровня насыщения транзисторов Т1 и Т2 и подачу напряжения питания Va на зажимы исполнительного механизма 2.

С другой стороны, в случае, если входной сигнал Е равен 0, выходной сигнал А колебательного контура 4 преобразуется в непрерывный сигнал и программируемая логическая схема 5 выдает непрерывные сигналы В1 и В2.

Сигналы, подаваемые на управляющие электроды транзисторов Т1 и Т2, в этом случае являются блокирующими сигналами и на зажимы исполнительного механизма 2 напряжение не подается.

Все внутренние неполадки в программируемой логической схеме 5 приводят к блокировке при постоянном уровне напряжения ее входов и/или выходов. Сигналы В1 и В2, таким образом, не могут быть оба прерывистыми и, в результате, по крайней мере один из транзисторов блокирован и исполнительный механизм 2 обесточен.

То же самое происходит и в случае внутренней неполадки генератора 4, вызывающей прекращение колебания. Для обеспечения надежности исполнительный механизм 2 остается в безопасном состоянии, когда к нему не подается напряжение. Для обеспечения надежности установки входной сигнал Е интерфейса мощности находится на нижнем уровне в случае обнаружения неполадки в верхней части цепи, т.е. в защитном интерфейсе или в модуле мажоритарной выборки 3, что приводит к блокировке транзисторов Т1 и Т2 и к переводу исполнительного механизма 2 в безопасное состояние.

Некоторые внутренние неполадки в интерфейсе мощности также приводят автоматически исполнительный механизм в состояния безопасности.

Это происходит, в частности, в случае залипания в состоянии блокировки одного из транзисторов, размыкания одного из проводников регулятора или размыкания схемы гальванического разрыва 7 или схемы 6.

Некоторые неполадки не приводят автоматически к переводу исполнительного механизма в безопасное состояние. В частности, в случае залипания одного из транзисторов в состоянии насыщения. Такую неполадку следует рассматривать как серьезную и ее необходимо обнаружить.

С этой целью регулятор мощности комплектуется средствами обнаружения неполадок в транзисторах большой мощности.

Это осуществляется при помощи циклической линейной проверки высокомощных транзисторов. Проверка реализуется под контролем таймера 8, который подает на контрольный вход программируемой логической схемы 5 сигналы H, служащие временной базой для регистрации выполнения такого самотестирования. Такое самотестирование выполняется, например, каждые 20 микросекунд.

Для проверки состояния транзистора Т1 или Т2 схема контроля напряжения 9 подключена параллельно этому транзистору и выход его подсоединяется на вход схемы 5. Контур контроля напряжения 9 предпочтительно состоит из оптопары.

Выходной сигнал, VI или V2, схемы контроля напряжения 9 является представительным сигналом, характеризующим состояние соответствующего транзистора, напряжение на зажимах которого равно 0, когда он в насыщенном состоянии.

Когда Е= 1, сигналы А, В1 и В2 являются прерывистыми сигналами и транзисторы Т1 и Т2 находятся в насыщенном состоянии, подача сигнала H в схему 5 приводит к краткому разрыву сигнала управления одного из транзисторов, например Т1, и к проверке, посредством схемы 9 его блокировки. Указанный транзистор снова входит в насыщение, и данная операция повторяется и для второго транзистора Т2.

Тестирование выполняется небольшими импульсами, т.е. продолжительность блокировки достаточна для осуществления самого тестирования, но и слишком коротка, чтобы исполнительный механизм мог на нее реагировать.

Когда Е=0, осуществляется проверка блокировки транзисторов. В этом случае сигналы А, В1 и В2 непрерывны и транзисторы Т1 и Т2 сблокированы. Подача сигнала H в схему 5 приводит последовательно к подаче на каждый транзистор управляющего сигнала, позволяющего проверить переход его в насыщенное состояние.

Следует отметить, что когда транзисторы блокированы, поляризация их осуществляется посредством проверочной схемы 9.

При выполнении самотестирования сигналы V1 и V2, подаваемые на схему 5, анализируются ею. Таким образом, неполадки в одном из транзисторов обнаруживаются и могут быть предложены два режима работы схемы 5 в случае обнаружения неполадки.

Согласно первому режиму, в котором предпочтение отдается обеспечению надежности, схема 5 блокирует на определенном уровне напряжения свои выходы В1 и В2, что приводит к блокировке обоих транзисторов Т1 и Т2 или, если один из них залип в насыщенном состоянии, к блокировке второго, с тем чтобы перевести исполнительный механизм в безопасное состояние. Одновременно подается аварийный сигнал на один из диагностических выходов схемы 5. В отсутствие неполадки схема 5 передает на этот выход прерывистый сигнал D. При обнаружении неполадки сигнал D преобразуется в непрерывный сигнал.

Согласно второму режиму, где предпочтение отдается сохранению рабочего режима, схема 5 продолжает обеспечивать управляющие состояния транзисторов даже после обнаружения неполадки. Эта неполадка, как и предыдущая, приводит к выработке на диагностическом выходе непрерывного сигнала D. Для улучшения надежности системы может оказаться полезным различать эти два способа работы. В качестве неограничительного примера высокий уровень непрерывного сигнала D может соответствовать первому способу работы, в то время как низкий уровень этого непрерывного сигнала может соответствовать второму способу работы.

Система контроля, не представленная в данном тексте, воспринимающая сигналы D, может быть устроена так, чтобы сигнализировать различными условными сигналами о каждом из этих режимов работы оператору, который сможет оперативно определить степень срочности вмешательства.

Сигнал D также переходит в непрерывный сигнал в случае неполадки внутреннего характера в программируемой логической схеме 5.

Такое исполнение и тот факт, что предусматривается возможность линейной проверки, обеспечивает высокую надежность регулятора мощности (file-safe) независимо от характера неполадки и значения величины логического входного сигнала Е. Простые неполадки могут относиться как к системе управления исполнительного механизма, в частности к генератору 4, схеме 5 и трансформаторам 7, к контуру 6 и транзисторам, к питанию и к соединительным проводам, так и к системе самотестирования, т.е. к таймеру 8, схеме 5 и оптопаре 9.

Во всех случаях либо исполнительный механизм будет переведен в состояние безопасности, либо о неполадке будет подан диагностический сигнал D.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЬНО-КОМАНДНАЯ СИСТЕМА ЗАЩИТЫ | 1994 |

|

RU2134898C1 |

| СИСТЕМА НЕПРЕРЫВНОГО КОНТРОЛЯ ЭЛЕКТРОПРОВОДИМОСТИ СИСТЕМЫ ЭЛЕКТРОПИТАНИЯ ПЕРЕМЕННОГО ТОКА | 1994 |

|

RU2121150C1 |

| ЭЛЕКТРИЧЕСКИЙ ВЫКЛЮЧАТЕЛЬ С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 1994 |

|

RU2127924C1 |

| ИСПОЛНИТЕЛЬНЫЙ МЕХАНИЗМ С КАЧАЮЩИМСЯ РЫЧАГОМ ДЛЯ ПРЕРЫВАТЕЛЯ ЭЛЕКТРИЧЕСКОЙ ЦЕПИ С ФАЗНЫМ И НУЛЕВЫМ КОНТАКТАМИ | 1993 |

|

RU2096853C1 |

| МОДУЛЬНЫЙ МНОГОПОЛЮСНЫЙ ВЫКЛЮЧАТЕЛЬ | 1994 |

|

RU2126566C1 |

| ОДНОПОЛЮСНЫЙ ВЫКЛЮЧАТЕЛЬ С НЕЙТРАЛЬНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ЦЕПЬЮ | 1993 |

|

RU2077085C1 |

| ПРИВОДНОЙ МЕХАНИЗМ ДЛЯ ТРЕХПОЗИЦИОННОГО ПЕРЕКЛЮЧАТЕЛЯ | 1993 |

|

RU2126565C1 |

| СИЛОВАЯ УСТАНОВКА ЭЛЕКТРОМОБИЛЯ, ЭЛЕКТРОМОБИЛЬ И СПОСОБ ОБОГРЕВА АККУМУЛЯТОРНОЙ БАТАРЕИ ЭЛЕКТРОМОБИЛЯ | 2013 |

|

RU2600558C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ РОБОТОМ-МАНИПУЛЯТОРОМ | 2004 |

|

RU2277042C1 |

| КВАДРАТУРНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ДЕЛЕНИЕМ НА ТРИ | 2009 |

|

RU2479121C2 |

На вход защитного интерфейса мощности подают непрерывные логические сигналы. Эти сигналы динамически кодируют генератором и подают программируемой логической схемой на два последовательно соединенных высокомощных транзистора. Защитный интерфейс мощности реализует линейную самопроверку короткими импульсами. Программируемая логическая схема выдает прерывистый диагностический сигнал в отсутствие неполадки или непрерывный сигнал при обнаружении неполадки. Технический результат заключается в том, что интерфейс отличается надежностью, поскольку сигнализирует о неполадке или автоматически переключает управляемый исполнительный механизм на безопасный режим. 9 з.п.ф-лы, 1 ил.

| Стереофоторентгенограмметрический способ комплексного определения пространственных характеристик тела человека | 1973 |

|

SU526350A1 |

| Ключевой усилитель мощности | 1985 |

|

SU1356200A1 |

| SU 1485381 A, 07.06.89 | |||

| Усилитель мощности класса Д | 1987 |

|

SU1538223A1 |

| Мостовой усилитель мощности | 1973 |

|

SU845264A1 |

Авторы

Даты

1998-12-27—Публикация

1994-01-28—Подача