Уровень техники

Область техники, к которой относится изобретение

Раскрытые варианты реализации относятся к делителям частоты.

Уровень техники

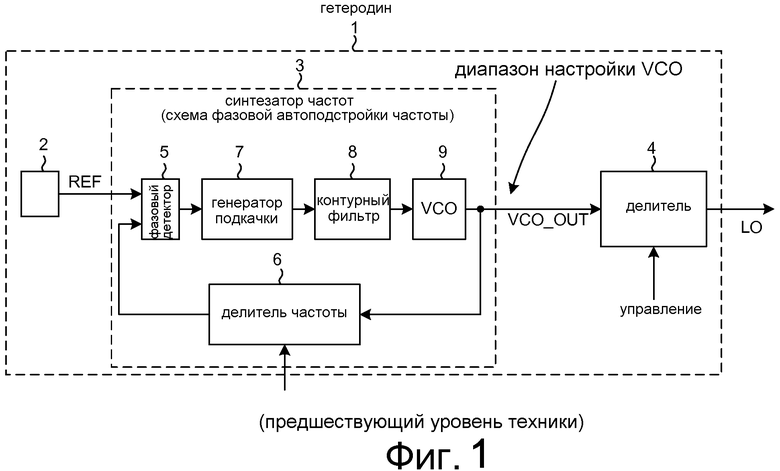

Фиг.1 (предшествующий уровень техники) является схемой одного примера местного генератора (гетеродина) 1. Радиоприемники и радиопередатчики, используемые, например, в сотовых телефонах, часто вмещают в себя множество подобных гетеродинов. Гетеродин этого типа обычно вмещает в себя источник 2 опорного тактового сигнала, схему 3 фазовой автоподстройки частоты и делитель 4 частоты. В проиллюстрированном примере фазовый детектор 5 принимает опорный тактовый сигнал REF от источника 2 опорного тактового сигнала, а также принимает сигнал обратной связи от делителя 6 частоты. Фазовый детектор 5 выводит сигнал фазовой ошибки, который подается на генератор 7 подкачки. Выходной сигнал генератора 7 подкачки фильтруется контурным фильтром 8, чтобы сформировать сигнал уровня напряжения. Сигнал уровня напряжения подается на управляющий входной вывод управляемого напряжением генератора (VCO) 9. Напряжение на управляющем входном выводе VCO 9 определяет частоту сигнала VCO_OUT, выводимого из VCO 9. Делитель 6 частоты делит частоту сигнала VCO_OUT и подает результирующий сигнал с разделенной частотой на фазовый детектор 5 в качестве сигнала обратной связи. Когда схема фазовой автоподстройки частоты синхронизирована, сигнал обратной связи и сигнал REF находятся в фазе, и частота сигнала VCO_OUT определяется коэффициентом деления, на которое делит делитель 6 частоты. Частота сигнала VCO_OUT представляет собой произведение коэффициента деления и частоты опорного тактового сигнала REF. Сигнал VCO_OUT обычно не выводится как выходной сигнал гетеродина (LO), а чаще сигнал VCO_OUT представляет собой сигнал с частотой, разделенной до более низкой частоты вторым делителем 4 частоты. Делитель 4 частоты может быть установлен, например, чтобы делить частоту на относительно малое целое число, например на два, или на четыре, или на восемь.

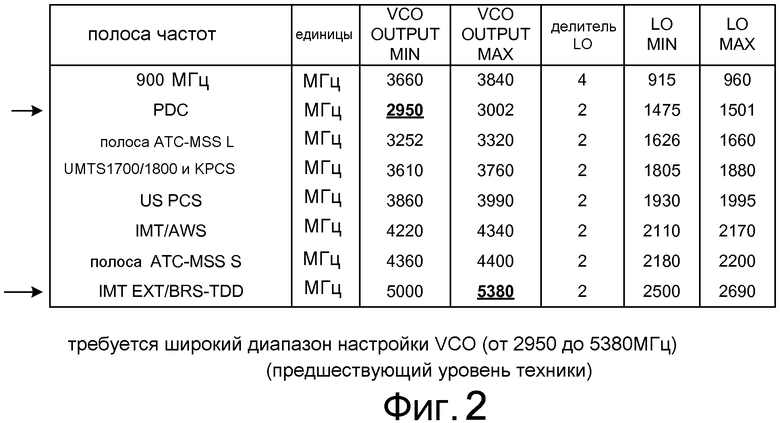

В случае интегральных схем приемопередатчика, интегрированных внутрь сотовых телефонов, часто бывает желательно сделать интегральную схему приемопередатчика такой, чтобы одна и та же конструкция интегральной схемы могла использоваться для связи в любой из множества различных полос частот. На Фиг.2 (предшествующий уровень техники) показаны примеры различных полос частот, по которым отдельному приемнику (в пределах интегральной схемы приемопередатчика сотового телефона) могло бы требоваться осуществлять связь. Крайние правые два столбца на Фиг.2 указывают выходные частоты сигналов гетеродина (LO), которые необходимо формировать. Столбец, обозначенный "LO DIVIDER" указывает число, на которое делит делитель 4 частоты. Два столбца, обозначенные "VCO OUTPUT MIN" и "VCO OUTPUT MAX", отображают соответствующие выходные частоты VCO, необходимые для формирования желаемых частот LO MIN и LO MAX, учитывая заданный в столбце LO DIVIDER коэффициент деления. Следует отметить, что для формирования требуемых выходных сигналов гетеродина с желаемыми частотами частота выходного сигнала VCO должна быть настраиваемой в пределах диапазона от 2950 мегагерц до 5380 мегагерц. Это относительно широкий диапазон настройки VCO. Может оказаться затруднительным реализовать VCO с широким диапазоном настройки, или, по другим причинам, может быть нежелательно предоставлять такой широкий диапазон настройки VCO.

Если делитель 4 частоты мог бы быть установлен на деление на три, то можно было бы уменьшить диапазон настройки VCO. Хотя делители частоты, которые делят частоту на три, известны, такие делители частоты обычно не используются, поскольку желаемый выходной сигнал гетеродина часто фактически представляет собой не только один сигнал (LO), а чаще пару сигналов, причем фаза одного из сигналов не совпадает на девяносто градусов относительно других сигналов. Такие сигналы LO называются как квадратурные сигналы, или, как принято говорить, сигнал гетеродина находится "в квадратуре". Символы I и Q часто используются для обозначения таких квадратурных сигналов. Квадратурные сигналы могут быть, например, затребованы другой схемой приемника, чтобы выполнить модуляцию фазовым сдвигом и/или выполнить подавление зеркальных помех.

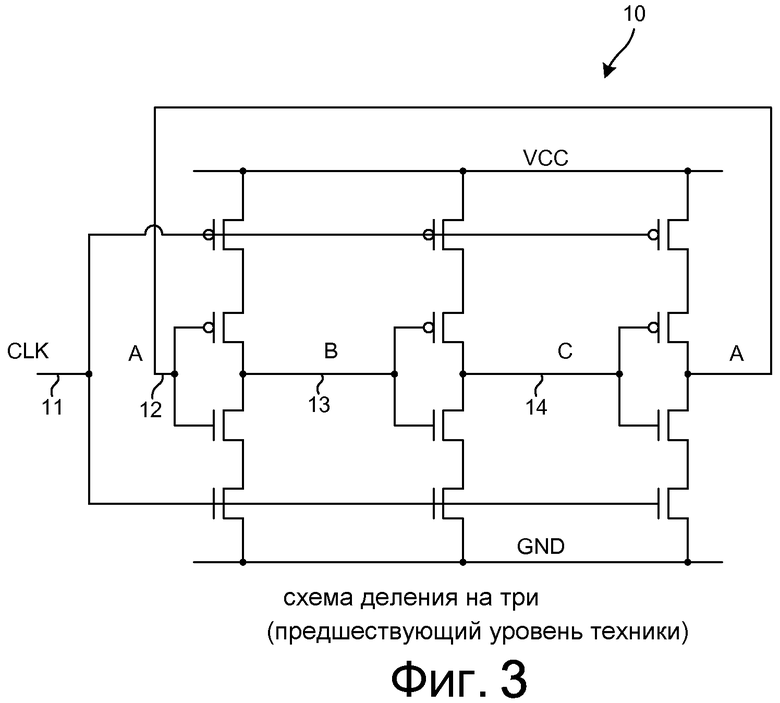

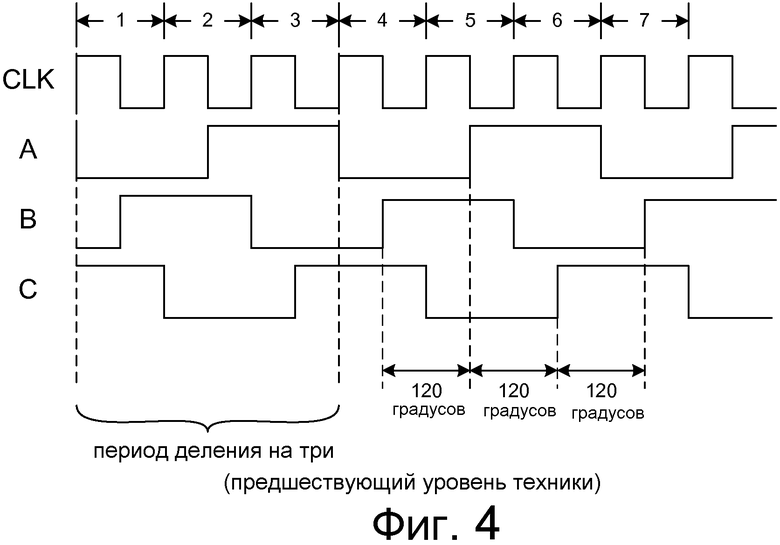

Фиг.3 (предшествующий уровень техники) является примером делителя 10 частоты с делением на три предшествующего уровня техники, изложенного в 1973 г. в статье, озаглавленной "Потребление малой мощности и высокая частота", Electronics Letters, Issue 17, vol. 9, August 23, 1973, авторы H. Oguey и C. Vittoz. Фиг.4 (предшествующий уровень техники) является временной диаграммой сигналов, иллюстрирующей работу схемы. Когда входной тактовый сигнал CLK частоты 3F подается на входной вывод 11, схема формирует три сигнала A, B и C на узлах 12, 13 и 14, соответственно, с частотой F. Никакие два из сигналов A, B и C не отличаются друг от друга на девяносто градусов, и делитель частоты не используется для делителя 4 частоты в гетеродине 1 на Фиг.1, если должны быть сформированы квадратурные выходные сигналы гетеродина.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Гетеродин включает в себя программируемый делитель частоты, соединенный с выходом управляемого напряжением генератора (VCO). Программируемый делитель частоты может быть установлен на деление на три. Независимо от числа, на которое делит программируемый делитель частоты, программируемый делитель частоты выводит квадратурные сигналы (I, Q) с коэффициентом заполнения пятьдесят процентов, которые отличаются друг от друга по фазе на девяносто градусов. Чтобы делить на три, делитель частоты включает в себя делитель частоты с делением на три. Делитель частоты с делением на три включает в себя схему деления на три, схему задержки, и схему обратной связи. Схема деления частоты на три делит входной сигнал, принятый от VCO, и формирует из него три сигнала C, A' и B, которые отличаются друг от друга по фазе на сто двадцать градусов. Схема задержки задерживает второй сигнал A', чтобы сформировать задержанную версию A второго сигнала. Схема обратной связи управляет схемой задержки так, чтобы задержанная версия A не совпадала по фазе на девяносто градусов относительно первого сигнала C. Задержанная версия A может быть использована как квадратурный сигнал I, а первый сигнал C может быть использован как квадратурный сигнал Q. Контур обратной связи автоматически корректирует изменения и/или вариации в работе схемы вследствие температурных изменений, изменений питающего напряжения и/или вариаций в технологической обработке полупроводника.

Программируемый делитель частоты может быть реализован в интегральной схеме RF приемопередатчика внутри сотового телефона. Исполняемые процессором команды в цифровой интегральной схеме основной полосы частот могут устанавливать коэффициент деления, на который программируемый делитель частоты делит, посредством передачи соответствующей управляющей информации через шину от цифровой интегральной схемы основной полосы частот на интегральную схему RF приемопередатчика.

В одном конкретном примере схема обратной связи включает в себя участок цифровой логики и участок схемы усреднения и сравнения. Участок цифровой логики принимает сигналы A и C и формирует цифровой сигнал, указывающий величину времени T1 между первым фронтом сигнала A и фронтом сигнала C. Участок цифровой логики формирует также цифровой сигнал, указывающий величину времени T2 между фронтом сигнала C и вторым фронтом сигнала A. Цифровой сигнал, указывающий величину времени T1, преобразуется в сигнал уровня напряжения, указывающий величину времени T1. Цифровой сигнал, указывающий величину времени T2, преобразуется в сигнал уровня напряжения, указывающий величину времени T2. Сигналы двух уровней напряжения подаются на входы операционного усилителя так, что операционный усилитель формирует сигнал управления. Сигнал управления преобразуется в сигнал управления напряжения смещения, который подается на схему задержки. Через этот контур обратной связи схема обратной связи работает для управления задержкой схемы задержки так, чтобы разность фаз между сигналом C и сигналом A составляла девяносто градусов.

Выше было дано краткое изложение сущности изобретения, и оно неизбежно содержит упрощения, обобщения и исключения подробностей; следовательно, специалистам в данной области техники должно быть очевидно, что это краткое изложение служит только иллюстративным целям и не предполагает каких-либо ограничений. Другие аспекты, признаки изобретения и преимущества описываемых здесь устройств и/или процессов, определяемые исключительно в соответствии с формулой, станут очевидными из приведенного не ограничивающего подробного описания.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 (предшествующий уровень техники) является схемой одного примера гетеродина, пригодного для использования в сотовом телефоне.

Фиг.2 (предшествующий уровень техники) - таблица, иллюстрирующая, что VCO гетеродина на Фиг.1 имеет нежелательно широкий диапазон настройки VCO.

Фиг.3 (предшествующий уровень техники) - схема делителя частоты с делением на три предшествующего уровня техники.

Фиг.4 (предшествующий уровень техники) - временная диаграмма сигналов, иллюстрирующая работу схемы делителя частоты с делением на три на Фиг.3 предшествующего уровня техники.

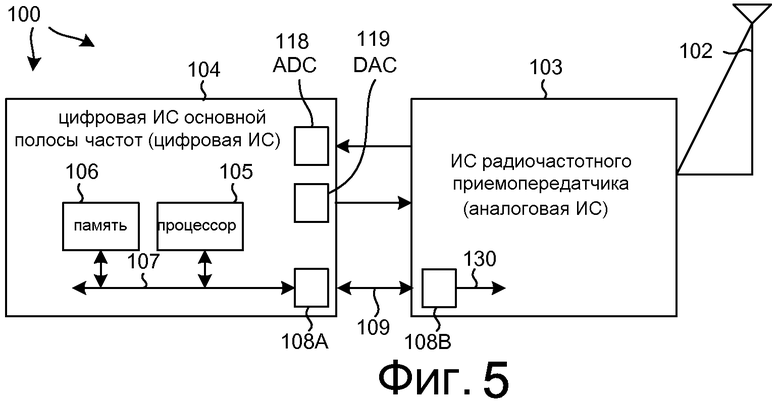

Фиг.5 - блок-схема высокого уровня устройства 100 мобильной связи в соответствии с одним новым аспектом.

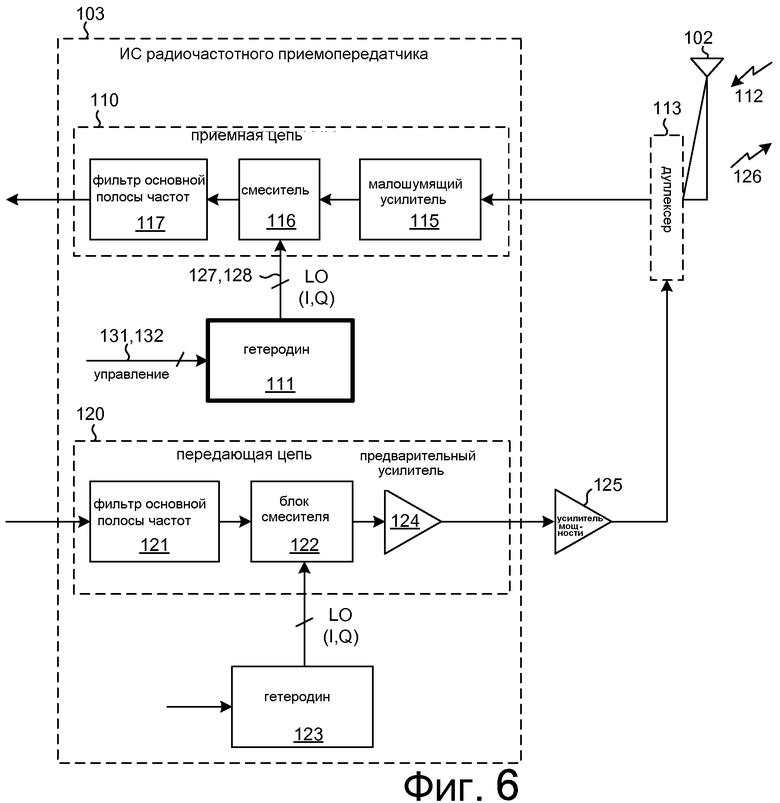

Фиг.6 - более подробная блок-схема интегральной схемы 103 RF приемопередатчика на Фиг.5.

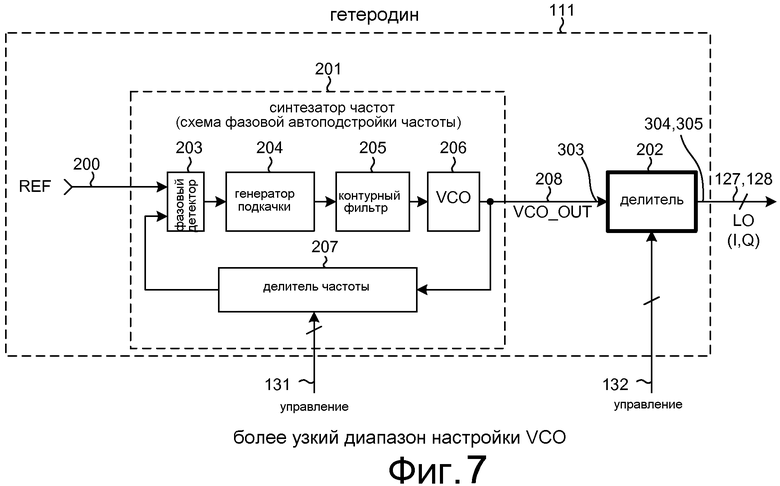

Фиг.7 - более подробная схема гетеродина 111 на Фиг.6.

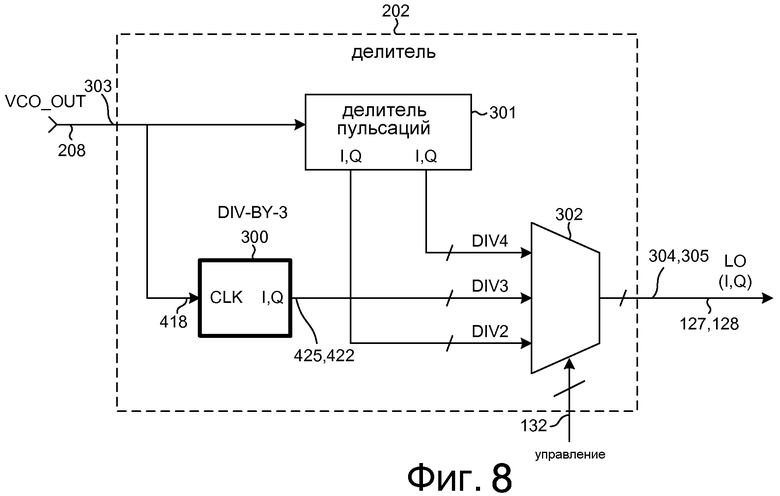

Фиг.8 - более подробная схема программируемого делителя 202 частоты гетеродина 111 на Фиг.7.

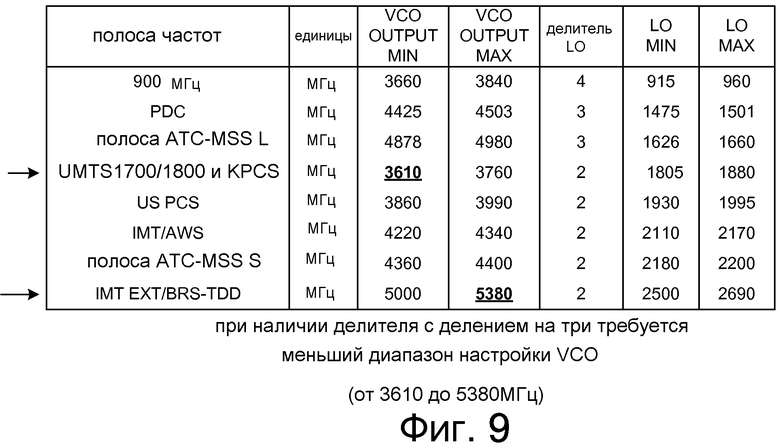

Фиг.9 - таблица, иллюстрирующая, что VCO гетеродина 111 на Фиг.7 имеет более узкий диапазон настройки VCO, чем схема VCO на Фиг.1 предшествующего уровня техники.

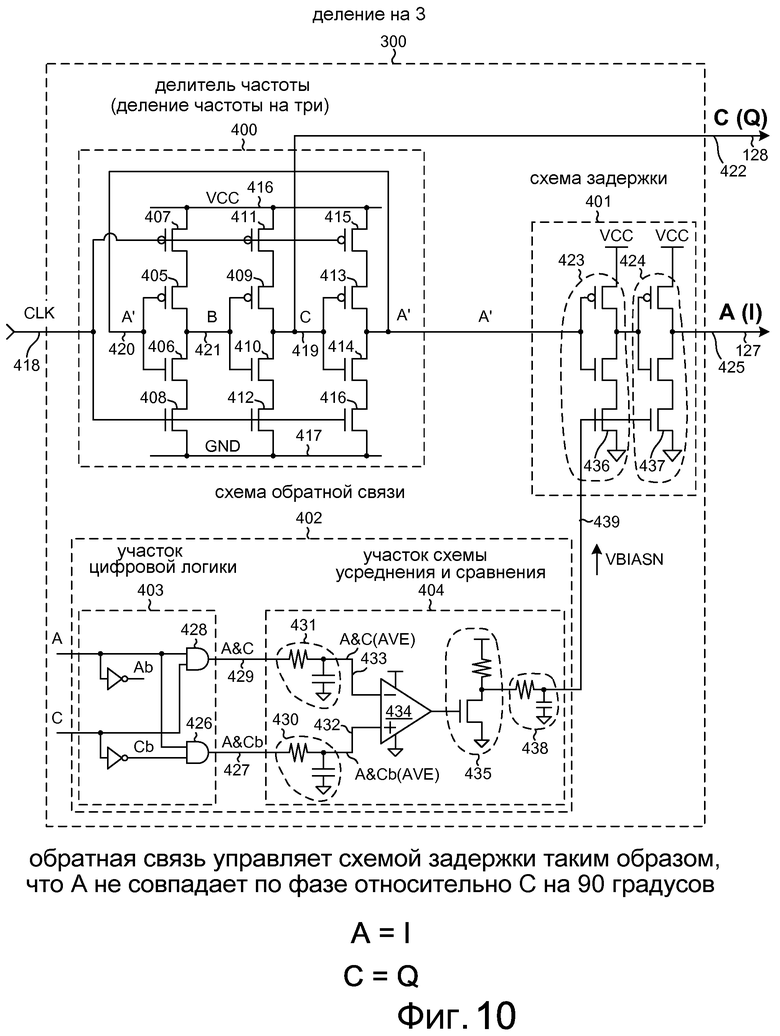

Фиг.10 - принципиальная схема нового делителя 300 частоты с делением на три из Фиг.8.

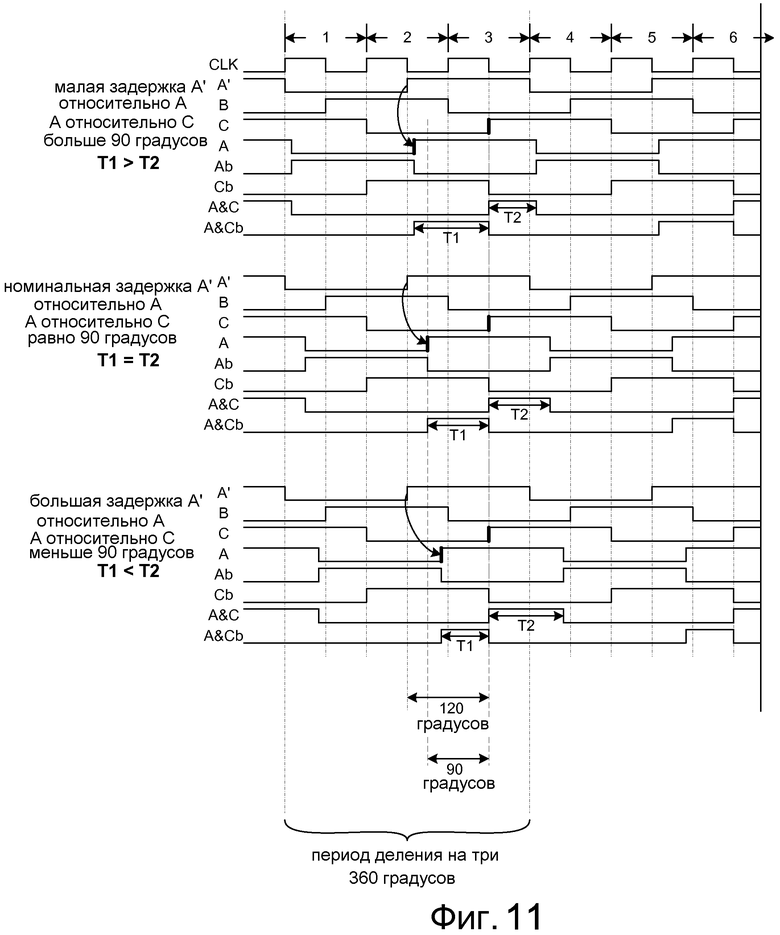

Фиг.11 - временная диаграмма сигналов, иллюстрирующая работу нового делителя 300 частоты с делением на три из Фиг.10.

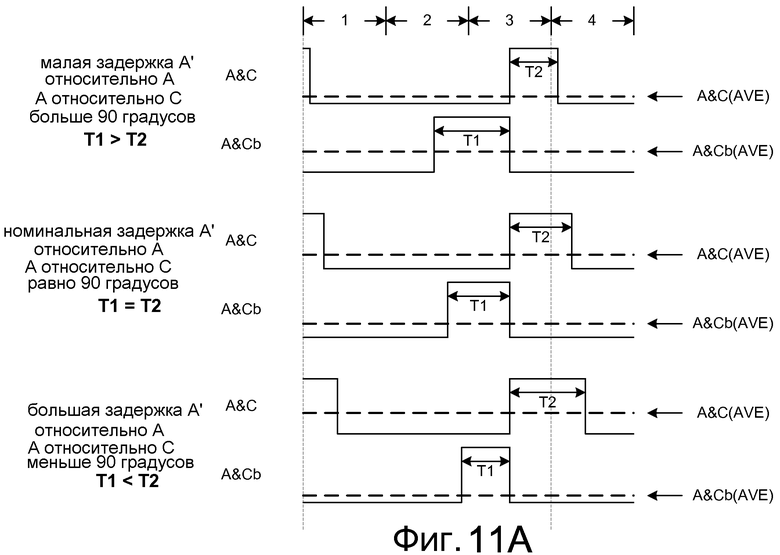

Фиг.11А - временная диаграмма сигналов, иллюстрирующая, как сигналы A&Cb и A&C преобразуются в соответствующие сигналы A&Cb (AVE) и A&C (AVE) уровня напряжения.

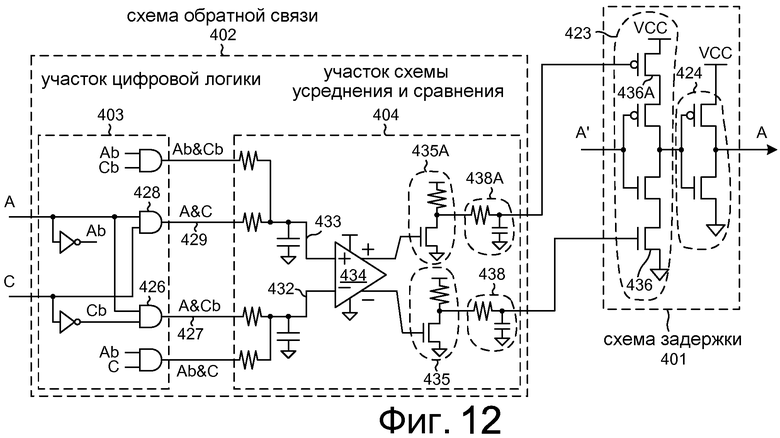

Фиг.12 - принципиальная схема другого варианта реализации схемы 402 обратной связи и схемы 401 задержки делителя 300 частоты с делением на три из Фиг.10.

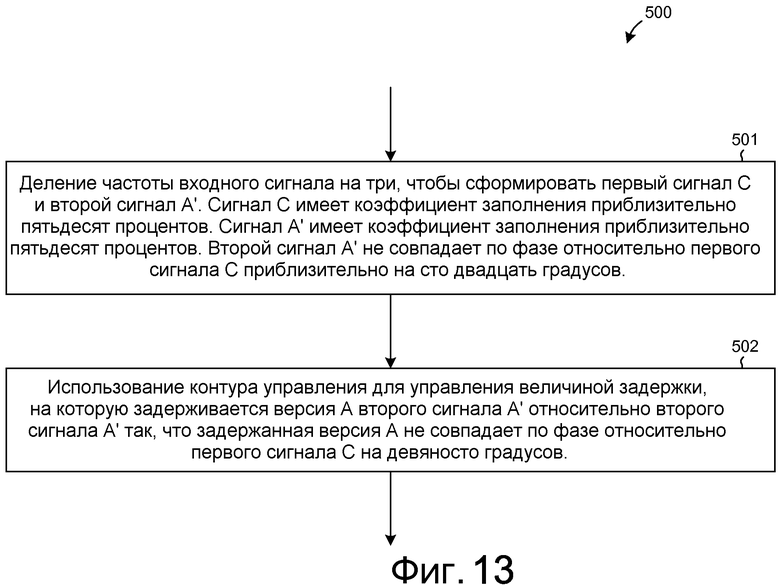

Фиг.13 - блок-схема последовательности операций способа 500 в соответствии с одним новым аспектом.

ПОДРОБНОЕ ОПИСАНИЕ

На Фиг.5 показана очень упрощенная блок-схема высокого уровня одного устройства 100 мобильной связи конкретного типа в соответствии с одним новым аспектом. В этом конкретном примере устройство 100 мобильной связи представляет собой 3G сотовый телефон, пригодный для работы или в соответствии с протоколом сотовой телефонной связи Множественного доступа с кодовым разделением каналов (CDMA), или в соответствии с протоколом сотовой телефонной связи GSM (Глобальная Система Мобильной Связи). Мобильный телефон включает в себя (среди некоторых других частей, не проиллюстрированных) антенну 102 и две интегральные схемы 103 и 104. Интегральную схему 104 называют "цифровой интегральной схемой основной полосы частот" или "интегральной схемой процессора основной полосы частот". Цифровая интегральная схема 104 основной полосы частот включает в себя, среди других частей, не проиллюстрированных, цифровой процессор 105, который исполняет команды, сохраняемые в процессорно-читаемом носителе 106. Процессор 105 может инициировать обмен информацией по шине 107, и интерфейсу 108A шины, и проводникам 109 шины, и в интерфейс 108B шины интегральной схемы 103. Интегральная схема 103 представляет собой интегральную схему RF приемопередатчика. Интегральную схему 103 RF приемопередатчика называют "приемопередатчиком", поскольку она включает в себя и передатчик, и приемник.

Фиг.6 является более подробной блок-схемой интегральной схемы 103 RF приемопередатчика из Фиг.5. Приемник включает в себя так называемую "приемную цепь" 110, а также гетеродин 111. Когда сотовый телефон принимает, высокочастотный сигнал 112 RF принимается антенной 102. Информация от сигнала 112 проходит через дуплексер 113 в приемную цепь 110. Сигнал 112 усиливается малошумящим усилителем (LNA) 115 и преобразуется с понижением частоты смесителем 116. Результирующий преобразованный с понижением частоты сигнал фильтруется фильтром 117 основной полосы частот и проходит на цифровую интегральную схему 104 основной полосы частот. Аналого-цифровой преобразователь 118 в цифровой интегральной схеме 104 основной полосы частот преобразует сигнал в цифровую форму, и результирующая цифровая информация обрабатывается цифровой схемой в цифровой интегральной схеме 104 основной полосы частот. Цифровая интегральная схема 104 основной полосы частот настраивает приемник, управляя частотой квадратурных сигналов I и Q гетеродина, подаваемых гетеродином 111 на смеситель 116 по проводникам 127 и 128.

Если сотовый телефон передает, то информация, которая должна быть передана, преобразуется в аналоговую форму цифроаналоговым преобразователем 119 в цифровой интегральной схеме 104 основной полосы частот и подается на "передающую цепь" 120. Фильтр 121 основной полосы частот отфильтровывает шум, обусловленный процессом цифроаналогового преобразования. Блок 122 смесителя под управлением гетеродина 123 затем преобразует сигнал с повышением частоты в высокочастотный сигнал. Предусилитель 124 и внешний усилитель 125 мощности усиливают высокочастотный сигнал для возбуждения антенны 102 так, чтобы высокочастотный RF сигнал 126 передавался антенной 102. Цифровая интегральная схема 104 основной полосы частот настраивает передатчик, управляя частотой квадратурных сигналов I и Q гетеродина, подаваемых гетеродином 123 на смеситель 122. Стрелка 130 представляет собой передачу информации от цифровой интегральной схемы 104 основной полосы частот через интерфейс 108A шины, по проводникам 109 шины, через интерфейс 108B шины, и через проводники 131 и 132 на гетеродин 111, чтобы установить коэффициент деления, на который делит делитель частоты в пределах гетеродина 111, как подробнее объясняется ниже.

На Фиг.7 показана более подробная схема гетеродина 111. Гетеродин 111 включает в себя источник 200 опорного тактового сигнала (обозначенный здесь посредством проводника), синтезатор 201 частоты, и новый программируемый делитель 202 частоты. Синтезатор 201 частоты в приведенном примере является аналогом схемы фазовой автоподстройки частоты (PLL), которая включает в себя фазовый детектор 203, генератор 204 подкачки, контурный фильтр 205, управляемый напряжением генератор (VCO) 206 и делитель 207 частоты. Приемник приемной цепи 110 настраивается установкой частоты выходных квадратурных сигналов I и Q гетеродина на проводниках 127 и 128, соответственно. Частота квадратурных сигналов I и Q определяется коэффициентом деления, на который делитель 207 частоты делит, и коэффициентом деления, на который делит программируемый делитель 202 частоты. Частота опорного тактового сигнала REF фиксирована. Коэффициент деления, на который делит делитель 207 частоты, устанавливается значением, подаваемым на проводники 131 управления. Коэффициент деления, на который делит делитель 202 частоты, устанавливается значением, подаваемым на проводники 132 управления. В этом примере цифровая интегральная схема 104 основной полосы частот из Фиг.5 управляет этими значениями коэффициента деления через шину 109.

На Фиг.8 показана более подробная схема нового программируемого делителя 202 частоты из Фиг.7. Программируемый делитель 202 частоты включает в себя новый делитель 300 частоты с делением на три, делитель 301 пульсаций, и схему 302 мультиплексирования. Сигнал VCO_OUT от VCO 206 принимается через проводник 208 на входной вывод 303 делителя 202 частоты. Делитель 301 пульсаций представляет собой двоичный делитель, который имеет несколько каскадов. Первый каскад выводит набор квадратурных сигналов, которые имеют частоту в половину частоты сигнала VCO_OUT. Эти сигналы обозначены как DIV2 на Фиг.8. Второй каскад выводит набор квадратурных сигналов, которые имеют частоту в одну четверть частоты сигнала VCO_OUT. Эти сигналы обозначены как DIV4 на Фиг.8. Новый делитель 300 частоты с делением на три делит частоту сигнала VCO_OUT на три и выводит набор квадратурных сигналов, частота которых составляет одну треть частоты VCO_OUT. Эти сигналы обозначены как DIV3 на Фиг.8. То, какой из трех наборов квадратурных сигналов выводится из делителя 202 частоты на выходные выводы 304 и 305, определяется цифровым значением на проводниках 132 управления. Хотя символ мультиплексора проиллюстрирован как представляющий функцию мультиплексирования, использование мультиплексора не необходимо. В одном примере три выходных I проводника от блоков 300 и 301 соединены вместе, и три выходных Q проводника от блоков 300 и 301 соединены вместе. Управляющее значение на проводнике 132 управления позволяет соответствующему одному из блоков 300 и 301 управлять соответствующим набором I и Q сигналов на выходных выводах 304 и 305. Каждый из выходных выводов 304 и 305 служит, поэтому, своего рода выводом проводной схемы ИЛИ.

На Фиг.9 показана таблица, иллюстрирующая преимущество, реализованное новым делителем 202 частоты. Делитель 202 частоты может делить частоту или на два, или на три, или на четыре. Для всех трех коэффициентов деления делитель 202 частоты выводит квадратурные сигналы I и Q. Следует отметить, что в таблице на Фиг.9 показаны те же самые полосы частот и те же самые частоты "LO MIN" и "LO MAX", что и в таблице на Фиг.2 предшествующего уровня техники, но следует отметить, что в таблице на Фиг.9 столбец "LO DIVIDER" указывает, что VCO_OUT является частотой, разделенной на три в двух случаях. В результате, диапазон настройки VCO уменьшается от широкого диапазона на Фиг.2 до более узкого диапазона перестройки от 3610 до 5380 мегагерц для случая на Фиг.9. Установка частоты VCO_OUT и установка значения "LO DIVIDER", при каждой ситуации рабочей полосы частот, управляются процессором 105 цифровой интегральной схемы 104 основной полосы частот, как объяснено выше. В одном преимущественном аспекте частота сигнала VCO_OUT и коэффициент деления, на который делит делитель 202 частоты, устанавливаются так, чтобы синтезатор 201 частоты мог быть такого типа, который имеет относительно узкий диапазон настройки VCO.

На Фиг.10 показана более подробная схема одного варианта осуществления нового делителя 300 частоты с делением на три из Фиг.8. Делитель 300 частоты включает в себя делитель 400 частоты с делением на три, схему задержки 401 и схему обратной связи 402. Схема 402 обратной связи, в свою очередь, включает в себя участок 403 цифровой логики и участок 404 схемы усреднения и сравнения.

В одном примере делитель 400 частоты представляет собой делитель частоты, проиллюстрированный выше на Фиг.3. Делитель 400 частоты включает в себя двенадцать полевых транзисторов (FET) 405-416, составляющих три каскада, как проиллюстрировано. Первый каскад вмещает в себя первый P-канальный FET полевой транзистор (PFET) 405, второй PFET 407, первый N-канальный полевой транзистор (NFET) 406, и второй NFET 408. Затворы PFET 405 и NFET 406 подключены между собой, и стоки PFET 405 и NFET 406 подключены между собой. Сток второго PFET 407 соединяется с истоком первого PFET 405, и сток второго NFET 408 соединяется с истоком первого NFET 406. Исток второго PFET 407 подключен с шиной 416 подачи напряжения, и исток второго NFET 408 подключен с земляной шиной 417. Второй и третий каскады транзисторов соединяются между собой подобным образом. Когда входной тактовый сигнал CLK с частотой 3F (VCO_OUT) подается на входной вывод 418, делитель 400 частоты формирует три сигнала C, A' и B на узлах 419, 420 и 421, соответственно. Каждый из этих сигналов имеет коэффициент заполнения приблизительно пятьдесят процентов. Второй сигнал A' не совпадает по фазе относительно первого сигнала C приблизительно на 120 градусов, и третий сигнал B не совпадает по фазе относительно второго сигнала А' приблизительно на 120 градусов, и первый сигнал C не совпадает по фазе относительно третьего сигнала B приблизительно на 120 градусов.

Первый сигнал C на узле 419 подается на выходной вывод 422 как квадратурный сигнал Q. Второй сигнал A' подается на схему 401 задержки. Схема 401 задержки формирует задержанную версию A второго сигнала A', пропуская второй сигнал через пару инвертирующих схем 423 и 424. Схема 401 задержки выводит результирующую задержанную версию A на выходной вывод 425 как квадратурный сигнал I.

Схема обратной связи 402 работает, чтобы управлять задержкой через схему 401 задержки так, чтобы сигнал на выходном выводе 425 не совпадал по фазе на девяносто градусов относительно сигнала C на выходном выводе 422. Участок 403 цифровой логики включает в себя первый логический элемент 426 И, который формирует цифровой сигнал на узле 427, который указывает величину времени Т1 между первым передним фронтом задержанной версии A второго сигнала и следующим передним фронтом первого сигнала C. Участок 403 цифровой логики включает в себя второй логический элемент 428 И, который формирует цифровой сигнал на узле 429, который указывает величину времени T2 между передним фронтом первого сигнала C и вторым задним фронтом задержанной версии A второго сигнала. Первый передний фронт задержанной версии A второго сигнала и второй задний фронт задержанной версии A второго сигнала определяют период высокого уровня импульсов задержанной версии A (длительность, когда задержанная версия A имеет высокий цифровой логический уровень).

В примере на Фиг.10, если периоды Т1 и T2 времени равны, то сигналы I и Q на выходных выводах 425 и 422 не будут совпадать по фазе друг относительно друга на девяносто градусов. Участок 404 схемы усреднения и сравнения имеет первый RC-фильтр 430 нижних частот, и второй RC-фильтр 431 нижних частот. Первый RC-фильтр 430 нижних частот грубо преобразует сигнал на узле 427 в соответствующий сигнал уровня напряжения на узле 432. Уровень напряжения на узле 432 указывает время Т1. Подобным образом, второй RC-фильтр 431 нижних частот грубо преобразует сигнал на узле 429 в соответствующий сигнал уровня напряжения на узле 433. Уровень напряжения на узле 433 указывает время T2. Операционный усилитель 434 принимает сигналы на узлах 432 и 433 на своих не инвертирующем и инвертирующем входных выводах, соответственно, и выводит сигнал управления. Сигнал управления преобразуется схемой 435 смещения в соответствующее напряжение смещения VBIASN, которое смещает транзисторы 436 и 437 схемы 401 задержки. Чем выше напряжение смещения VBIASN, подаваемое на затворы транзисторов 436 и 437, тем меньше потребляемый инвертирующими схемами 423 и 424 ток, и тем быстрее инвертирующие схемы 423 и 424 будут в состоянии переключать свои выходы. Соответственно, чем выше напряжение смещения VBIASN, тем меньше задержка при прохождении через схему 401 задержки.

Схема 438 предоставлена, чтобы добавить полюс на соответствующей частоте, чтобы препятствовать колебаниям контура управления. Если напряжение на узле 432 выше, чем напряжение на узле 433, то Т1 оказывается больше, чем T2, и управляющее напряжение на узле 439 уменьшается, чтобы увеличить задержку через схему 401 задержки так, чтобы сделать Т1 и T2 более равными. Если, с другой стороны, напряжение на узле 432 ниже, чем напряжение на узле 433, то Т1 оказывается меньше, чем T2, и управляющее напряжение на узле 439 увеличивается, чтобы уменьшить задержку через схему 401 задержки так, чтобы сделать Т1 и T2 более равными. Работа контура управления обратной связи такова, что Т1 и T2 управляются до их равенства, и такова, чтобы разность фаз между сигналами C и A составляла девяносто градусов.

Работа схемы на Фиг.10 дополнительно поясняется применительно к временной диаграмме сигналов на Фиг.11. Временная диаграмма сигналов на Фиг.11 фактически включает в себя три набора сигналов. Верхний набор диаграмм сигналов представляет собой ситуацию, в которой Т1 больше, чем T2. Средний набор диаграмм сигналов представляет собой ситуацию, в которой Т1 и T2 равны. Нижний набор диаграмм сигналов представляет собой ситуацию, в которой Т1 меньше, чем T2. Как можно видеть из диаграмм сигналов на Фиг.11, время Т1 представляет собой время, когда сигнал A&Cb имеет высокий цифровой логический уровень. Сигнал A&Cb - это сигнал, присутствующий на узле 427 на Фиг.10. Сигнал A&Cb формируется инвертированием первого сигнала C, чтобы сформировать инвертированную версию Cb сигнала C. Символ "b" в этом обозначении означает "инвертирование". Элемент И 426 выполняет логическую операцию И сигнала Cb и сигнала A. Обозначение "A&Cb" означает логическую операцию И сигналов "A" и "Cb". Таким же образом, время T2 представляет собой время, когда сигнал A&Cb имеет высокий цифровой логический уровень. Сигнал A&C - это сигнал, присутствующий на узле 429 на Фиг.10. Элемент И 428 выполняет логическую операцию И сигнала C и сигнала A. Обозначение "A&C" означает логическую операцию И сигналов "A" и "C".

На Фиг.11А проиллюстрировано, как сигналы A&Cb и A&C на узлах 427 и 429 преобразуются в соответствующие сигналы A&Cb (AVE) и A&C (AVE) уровня напряжения на узлах 432 и 433, соответственно. Сигналы A&Cb (AVE), и A&C (AVE) уровня напряжения представлены на Фиг.11А горизонтальными пунктирными линиями. Чем больше доля времени, когда сигнал, поданный на вход RC-фильтра нижних частот, имеет высокий уровень, тем больше доля времени, когда конденсатор RC-фильтра нижних частот будет заряжаться, и тем меньше доля времени, когда конденсатор будет разряжаться. Соответственно, чем больше доля времени, когда сигнал, поданный на вход RC-фильтра нижних частот, имеет высокий уровень, тем выше уровень сигнала напряжения, выходящего из RC-фильтра нижних частот.

Хотя один вариант реализации нового делителя 300 частоты с делением на три приведен на Фиг.10, имеются и другие варианты. На Фиг.12 приведен пример, в котором участок 403 цифровой логики формирует четыре цифровых сигнала Ab&Cb, A&C, A&Cb и Ab&C. Хотя операционный усилитель 434 на Фиг.10 выводит несимметричный сигнал управления так, что один сигнал VBIASN управления напряжением смещения управляет задержкой прохождения через схему 401 задержки, в примере на Фиг.12 операционный усилитель 434 выводит пару дифференциальных сигналов на соответствующую пару схем 435 и 435A смещения. Схема 435A смещения имеет связанную с ней схему 438A, чтобы добавить полюс для предотвращения колебаний контура управления. Одна схема 435 смещения выводит напряжение VBIASN смещения на затвор NFET 436. Вторая схема 435A смещения выводит напряжение VBIASP смещения на затвор PFET 436A. В примере схемы 401 задержки на Фиг.12 вторая инвертирующая схема 424 схемы 401 задержки представляет собой простой инвертор и вмещает в себя только два транзистора, как проиллюстрировано. Схема 402 обратной связи работает, изменяя задержку прохождения через схему 401 задержки, изменяя проводимость NFET 436 и PFET 436A.

На Фиг.13 показана блок-схема последовательности операций способа 500 в соответствии с одним новым аспектом. На первом этапе входной сигнал (например, VCO_OUT) имеет разделенную на три частоту (этап 501), чтобы сформировать первый сигнал C и второй сигнал А'. Первый сигнал C имеет коэффициент заполнения приблизительно пятьдесят процентов, и второй сигнал A' имеет коэффициент заполнения приблизительно пятьдесят процентов. Второй сигнал A' не совпадает по фазе относительно первого сигнала C приблизительно на сто двадцать градусов.

На втором этапе используется контур управления (этап 502), чтобы управлять величиной задержки, посредством которой задержанная версия A второго сигнала A' задерживается относительно второго сигнала A' так, что задержанная версия A второго сигнала не совпадает по фазе относительно первого сигнала C на девяносто градусов. В одном примере способа задержанная версия A второго сигнала и первого сигнала C используются как выходные сигналы гетеродина (квадратурные сигналы I и Q) в радиопередатчике и/или приемнике сотового телефона, и частота входного сигнала составляет, по меньшей мере, сто мегагерц.

В одном или более примерных вариантах реализации описанные функции могут быть осуществлены в аппаратном обеспечении, программном обеспечении, встроенном программном обеспечении, или в любой их комбинации. Если они осуществляются в программном обеспечении, функции могут быть сохранены, или переданы на компьютерно-читаемый или процессорно-читаемый носитель как одна или более команд или код. Компьютерно-читаемый и процессорно-читаемый носители включают в себя и компьютерные носители данных, и среду передачи, включая в себя любую среду, которая способствует переносу программы из одного места в другое. Носитель данных может быть любым доступным носителем, к которому может осуществлять доступ компьютер или процессор. В качестве не ограничивающего примера, такой носитель может содержать RAM, ROM, EEPROM, CD-ROM или другой оптический дисковый накопитель, магнитный дисковый накопитель или другие магнитные устройства хранения, или любой другой носитель, который может быть использован для переноса или хранения желаемого программного кода в виде команд или структур данных, и к которому может осуществлять доступ компьютер или процессор. Кроме того, подключение также следует называть компьютерно-читаемым носителем. Например, если программное обеспечение передается с веб-сайта, сервера, или другого удаленного источника с использованием коаксиального кабеля, оптоволоконного кабеля, витой пары, цифровой абонентской линии (DSL), или беспроводной технологии, например инфракрасной, радио, и микроволновой, то подключение коаксиальным кабелем, оптоволоконным кабелем, витой парой, DSL, или с помощью беспроводных технологий, например инфракрасной, радио, и микроволновой, включено в определение носителя. Используемые в данном документе понятия оптический диск и магнитный диск включают в себя компакт-диск (CD), лазерный диск, оптический диск, цифровой универсальный диск (DVD), гибкий диск и blu-ray диск, причем магнитные диски обычно воспроизводят данные магнитным образом, а оптические диски воспроизводят данные оптическим образом с помощью лазеров. Комбинации всего вышеупомянутого также должны быть включены в объем компьютерно-читаемых носителей. Исполнение процессором 105 набора команд, сохраняемых в процессорно-читаемом носителе 106 цифровой ИС 104 основной полосы частот, в некоторых вариантах реализации инициирует передачу цифровой информации от цифровой ИС 104 основной полосы частот через проводники 109 шины на новый делитель 202 частоты из Фиг.7, и новый делитель 202 частоты выполнен так, чтобы делить частоту на три и выводить пару квадратурных сигналов (I и Q), фазы которых различаются на девяносто градусов. Когда делитель 202 частоты установлен таким образом, сигнал VCO_OUT имеет частоту 3F, и квадратурные сигналы представляют собой сигналы частотой F с коэффициентом заполнения пятьдесят процентов.

Хотя определенные варианты реализации описаны выше в иллюстративных целях, принципы данного патентного документа общеприменимы и не ограничиваются описанными выше конкретными вариантами реализации. Схема 402 обратной связи может быть использована, чтобы выполнить квадратурные делители частоты, которые делят на коэффициенты деления, не равные 2N (N - целое число). Например, квадратурный делитель частоты, имеющий коэффициент деления 1,5, может быть осуществлен с применением удвоителя частоты, следующего за квадратурным делителем частоты с делением на три, описанным выше. Выходные сигналы I и Q делителя частоты с делением на три могут быть сигналами с коэффициентом заполнения двадцать пять процентов или сигналами с коэффициентом заполнения пятьдесят процентов. Соответственно, различные модификации, адаптации, и комбинации различных признаков описанных конкретных вариантов реализации могут быть осуществлены без отступления от объема представленной ниже формулы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАНИЕ СИГНАЛА ГЕНЕРАТОРА КОЛЕБАНИЙ С ПОДАВЛЕНИЕМ ПАРАЗИТНЫХ ПИКОВ В УСТРОЙСТВЕ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2454792C2 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| СПОСОБ ОБРАБОТКИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ФАЗИРОВАНИЯ АНТЕНН ПРИЁМА ШИРОКОПОЛОСНЫХ СИГНАЛОВ, ПРЕИМУЩЕСТВЕННО ДЛЯ АНТЕНН НЕЭКВИДИСТАНТНОЙ РЕШЁТКИ | 2015 |

|

RU2594385C1 |

| СПОСОБ ИМПУЛЬСНО-ДОПЛЕРОВСКОЙ РАДИОЛОКАЦИИ И УСТРОЙСТВО С АВТОДИННЫМ ПРИЁМОПЕРЕДАТЧИКОМ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2023 |

|

RU2803413C1 |

| ПАКЕТНЫЙ ДЕТЕКТОР И СПОСОБ ОБНАРУЖЕНИЯ ПАКЕТНОГО СИГНАЛА | 1995 |

|

RU2108681C1 |

| НЕКОГЕРЕНТНЫЙ ОБНАРУЖИТЕЛЬ РАДИОСИГНАЛОВ В ШУМАХ | 2000 |

|

RU2187198C2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| ЦИФРОВАЯ АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2015 |

|

RU2608637C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ, СХЕМА АВТОМАТИЧЕСКОЙ ФАЗОВОЙ ПОДСТРОЙКИ ЧАСТОТЫ, ПРИЁМОПЕРЕДАТЧИК, РАДИОСТАНЦИЯ И СПОСОБ ЧАСТОТНОГО РАЗДЕЛЕНИЯ | 2015 |

|

RU2668737C1 |

| Квазикогерентный демодулятор фазоманипулированных сигналов | 1990 |

|

SU1758897A1 |

Изобретение относится к делителям частоты. Техническим результатом является уменьшение диапазона настройки управляемого напряжением генератора (VCO). Способ деления частоты с делением на три содержит этапы, на которых: делят частоту входного сигнала на три, чтобы сформировать первый сигнал С и второй сигнал А', несовпадающий по фазе относительно первого сигнала С приблизительно на сто двадцать градусов, причем первый сигнал С имеет коэффициент заполнения приблизительно пятьдесят процентов, и второй сигнал А' имеет коэффициент заполнения приблизительно пятьдесят процентов; и управляют величиной задержки, на которую задержанная версия А второго сигнала А' задерживается относительно второго сигнала А', причем задержанной версией А второго сигнала А' управляют посредством контура управления так, чтобы она не совпадала по фазе относительно первого сигнала С на девяносто градусов. 5 н. и 27 з.п. ф-лы, 13 ил.

1. Способ деления частоты с делением на три, содержащий этапы, на которых: делят частоту входного сигнала на три, чтобы сформировать первый сигнал С и второй сигнал А', несовпадающий по фазе относительно первого сигнала С приблизительно на стодвадцать градусов, причем первый сигнал С имеет коэффициент заполнения приблизительно пятьдесят процентов, и второй сигнал А' имеет коэффициент заполнения приблизительно пятьдесят процентов; и управляют величиной задержки, на которую задержанная версия А второго сигнала А' задерживается относительно второго сигнала А', причем задержанной версией А второго сигнала А' управляют посредством контура управления так, чтобы она не совпадала по фазе относительно первого сигнала С на девяносто градусов.

2. Способ по п.1, причем управление величиной задержки А вмещает в себя этапы, на которых: выполняют логическую операцию И над первым сигналом С и задержанной версией А второго сигнала и, тем самым, формируют третий сигнал; инвертируют первый сигнал С и, тем самым, формируют инвертированную версию Сb первого сигнала; выполняют логическую операцию И над инвертированной версией Сb первого сигнала и задержанной версией А второго сигнала и, тем самым, формируют четвертый сигнал; и управляют величиной задержки задержанной версии А относительно второго сигнала А' на основе третьего и четвертого сигналов в контуре управления.

3. Способ по п.1, причем управление величиной задержки А вмещает в себя этапы, на которых: формируют третий сигнал, указывающий величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и формируют четвертый сигнал, указывающий величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

4. Способ по п.3, причем управление величиной задержки А дополнительно вмещает в себя этапы, на которых: преобразуют третий сигнал в первый уровень напряжения, причем первый уровень напряжения указывает величину времени Т1; преобразуют четвертый сигнал во второй уровень напряжения, причем второй уровень напряжения указывает величину времени Т2; и подают первый и второй уровни напряжения на операционный усилитель, причем сигнал, выходящий из операционного усилителя, определяет, насколько задержанная версия А второго сигнала задержана относительно незадержанной версии А' второго сигнала.

5. Способ по п.1, причем управление величиной задержки А вмещает в себя этапы, на которых: первый логический элемент формирует третий сигнал, указывающий величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и второй логический элемент формирует четвертый сигнал, указывающий величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

6. Способ по п.1, причем деление частоты входного сигнала дополнительно вмещает в себя этап, на котором формируют третий сигнал В, и причем управление величиной задержки А вмещает в себя этапы, на которых: выполняют логическую операцию И над одним из первого, второго и третьего сигналов, и другим из первого, второго и третьего сигналов; и выполняют логическую операцию И над упомянутым одним из первого, второго и третьего сигналов, и инверсией упомянутого другого из первого, второго и третьего сигналов.

7. Схема деления частоты с делением на три, содержащая: делитель частоты, который принимает входной сигнал с частотой 3F и выводит первый сигнал С с частотой F, и выводит второй сигнал А' с частотой F, причем первый сигнал С имеет коэффициент заполнения приблизительно пятьдесят процентов, и причем второй сигнал А' имеет коэффициент заполнения приблизительно пятьдесят процентов, причем второй сигнал А' не совпадает по фазе относительно первого сигнала С приблизительно на стодвадцать градусов;

схему задержки, которая принимает второй сигнал А' и выводит задержанную версию А второго сигнала; и схему обратной связи, которая управляет схемой задержки так, чтобы задержанная версия А второго сигнала не совпадала по фазе относительно первого сигнала С на девяносто градусов.

8. Схема по п.7, причем схема обратной связи содержит: схему, которая формирует третий сигнал, указывающий величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; схему, которая формирует четвертый сигнал, указывающий величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала; и схему дифференциального усилителя, которая принимает третий сигнал и четвертый сигнал и формирует из них сигнал управления, причем сигнал управления подается на схему задержки.

9. Схема по п.8, причем третий и четвертый сигналы представляют собой цифровые логические сигналы.

10. Схема по п.8, причем третий и четвертый сигналы представляют собой сигналы уровня напряжения.

11. Схема по п.8, причем схема, которая формирует третий сигнал, включает в себя первый цифровой логический элемент, и причем схема, которая формирует четвертый сигнал, включает в себя второй цифровой логический элемент.

12. Схема по п.7, причем схема обратной связи включает в себя: первый цифровой логический элемент, который имеет выходной вывод, который соединен с входным выводом первого фильтра нижних частот; второй цифровой логический элемент, который имеет выходной вывод, который соединен с входным выводом второго фильтра нижних частот; и схему дифференциального усилителя, которая принимает сигнал от первого фильтра нижних частот, и которая принимает сигнал от второго фильтра нижних частот, причем схема дифференциального усилителя подает сигнал управления на схему задержки.

13. Схема по п.7, причем делитель частоты содержит: первый каскад, содержащий первый Р-канальный полевой транзистор (PFET), второй PFET, первый N-канальный полевой транзистор NFET, и второй NFET, причем затвор первого PFET и затвор первого NFET соединены вместе, причем сток первого PFET и сток первого NFET соединены вместе, причем сток второго PFET соединен с истоком первого PFET, причем сток второго NFET соединен с истоком первого NFET; второй каскад, содержащий первый PFET, второй PFET, первый NFET, и второй NFET, причем затвор первого PFET и затвор первого NFET соединены вместе и со стоками первого PFET и первого NFET первого каскада, причем сток первого PFET и сток первого NFET соединены вместе, причем сток второго PFET соединен с истоком первого PFET, причем сток второго NFET соединен с истоком первого NFET; и третий каскад, содержащий первый PFET, второй PFET, первый NFET, и второй NFET, причем затвор первого PFET и затвор первого NFET соединены вместе и со стоками первого PFET и первого NFET второго каскада, причем сток первого PFET и сток первого NFET соединены вместе, причем сток второго PFET соединен с истоком первого PFET, причем сток второго NFET соединен с истоком первого NFET, причем стоки первого PFET и первого NFET соединены с затворами первого PFET и первого NFET первого каскада, причем затворы вторых PFET первого, второго и третьего каскадов и затворы вторых NFET первого, второго и третьего каскадов соединены, чтобы принимать входной сигнал.

14. Схема по п.7, причем схема представляет собой гетеродин в радиоприемнике, и причем входной сигнал имеет частоту, по меньшей мере, сто мегагерц.

15. Схема по п.7, причем схема обратной связи включает в себя: первый цифровой логический элемент, который выводит логическое И второго сигнала и инверсии первого сигнала; второй цифровой логический элемент, который выводит логическое И первого сигнала и второго сигнала; третий цифровой логический элемент, который выводит логическое И первого сигнала и инверсии второго сигнала; четвертый цифровой логический элемент, который выводит логическое И инверсии первого сигнала и инверсии второго сигнала; и схему, которая принимает сигналы, выходящие из первого, второго, третьего и четвертого цифровых логических элементов, и которая подает сигнал управления на схему задержки.

16. Схема по п.7, причем схема задержки включает в себя цифровой логический инвертор и N-канальный полевой транзистор (NFET), причем цифровой логический инвертор имеет сигнальный входной вывод, сигнальный выходной вывод, вывод подачи питания, и земляной вывод, причем земляной вывод имеет возможность резистивного соединения с потенциалом земли через NFET.

17. Схема по п.16, причем схема задержки дополнительно включает в себя Р-канальный полевой транзистор (PFET), причем вывод подачи питания цифрового логического инвертора имеет возможность резистивного соединения с подачей напряжения через PFET.

18. Схема деления частоты с делением на три, содержащая: схему деления на три, которая принимает входной сигнал с частотой 3F, и которая выводит первый сигнал С и второй сигнал А', причем первый сигнал С и второй сигнал А' имеют одну и ту же частоту F, причем первый сигнал С и второй сигнал А' не совпадают по фазе относительно друг друга приблизительно на сто двадцать градусов; схему задержки, которая принимает второй сигнал А' от схемы деления на три, и выводит задержанную версию А второго сигнала; и средство для управления схемой задержки в контуре управления с обратной связью так, чтобы задержанная версия А второго сигнала не совпадала по фазе относительно первого сигнала С на девяносто градусов.

19. Схема по п.18, причем схема представляет собой гетеродин в радиоприемнике и причем входной сигнал имеет частоту, по меньшей мере, сто мегагерц.

20. Носитель информации, имеющий сохраненные на нем процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять этапы, на которых: делят частоту входного сигнала на три, чтобы сформировать первый сигнал С и второй сигнал А', несовпадающий по фазе относительно первого сигнала С приблизительно на стодвадцать градусов, причем первый сигнал С имеет коэффициент заполнения приблизительно пятьдесят процентов, и второй сигнал А' имеет коэффициент заполнения приблизительно пятьдесят процентов; и управляют величиной задержки, на которую задержанная версия А второго сигнала А' задерживается относительно второго сигнала А', причем задержанной версией А второго сигнала А' управляют посредством контура управления так, чтобы она не совпадала по фазе относительно первого сигнала С на девяносто градусов.

21. Носитель информации по п.20, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительный этап, на котором: принимают входной сигнал от управляемого напряжением генератора (VCO).

22. Носитель информации по п.20, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительные этапы, на которых: выполняют логическую операцию И над первым сигналом С и задержанной версией А второго сигнала и, тем самым, формируют третий сигнал; инвертируют первый сигнал С и, тем самым, формируют инвертированную версию Сb первого сигнала; выполняют логическую операцию И над инвертированной версией Сb первого сигнала и задержанной версией А второго сигнала и, тем самым, формируют четвертый сигнал; и управляют величиной задержки задержанной версии А относительно второго сигнала А' на основе третьего и четвертого сигналов в контуре управления.

23. Носитель информации по п.20, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительные этапы, на которых: формируют третий сигнал, указывающий величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и формируют четвертый сигнал, указывающий величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

24. Носитель информации по п.23, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительные этапы, на которых: преобразуют третий сигнал в первый уровень напряжения, причем первый уровень напряжения указывает величину времени Т1; преобразуют четвертый сигнал во второй уровень напряжения, причем второй уровень напряжения указывает величину времени Т2; и подают первый и второй уровни напряжения на операционный усилитель, причем сигнал, выходящий из операционного усилителя, определяет, насколько задержанная версия А второго сигнала задержана относительно незадержанной версии А' второго сигнала.

25. Носитель информации по п.20, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительные этапы, на которых: первый логический элемент формирует третий сигнал, указывающий величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и второй логический элемент формирует четвертый сигнал, указывающий величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

26. Носитель информации по п.20, который имеет процессорно-исполняемые команды программного обеспечения, сконфигурированные для предписания процессору выполнять дополнительные этапы, на котором: формируют третий сигнал В; выполняют логическую операцию И над одним из первого, второго и третьего сигналов, и другим из первого, второго и третьего сигналов; и выполняют логическую операцию И над упомянутым одним из первого, второго и третьего сигналов, и инверсией упомянутого другого из первого, второго и третьего сигналов.

27. Схема деления частоты с делением на три, содержащая: средство для деления частоты входного сигнала на три, чтобы сформировать первый сигнал С и второй сигнал А', несовпадающий по фазе относительно первого сигнала С приблизительно на стодвадцать градусов, причем первый сигнал С имеет коэффициент заполнения приблизительно пятьдесят процентов, и второй сигнал А' имеет коэффициент заполнения приблизительно пятьдесят процентов; и средство для управления величиной задержки, на которую задержанная версия А второго сигнала А' задерживается относительно второго сигнала А', причем задержанной версией А второго сигнала А' управляют посредством контура управления так, чтобы она не совпадала по фазе относительно первого сигнала С на девяносто градусов.

28. Схема по п.27, в которой упомянутое средство для управления величиной задержки А дополнительно содержит: средство для выполнения логической операции И над первым сигналом С и задержанной версией А второго сигнала и, тем самым, формирования третьего сигнала; средство для инвертирования первого сигнала С и, тем самым, формирования логической операции И над инвертированной версией Сb первого сигнала и задержанной версией А второго сигнала и, тем самым, формирования четвертого сигнала; и средство для управления величиной задержки задержанной версии А относительно второго сигнала А' на основе третьего и четвертого сигналов в контуре управления.

29. Схема по п.27, в которой упомянутое средство для управления величиной задержки А дополнительно содержит: средство для формирования третьего сигнала, указывающего величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и средство для формирования четвертого сигнала, указывающего величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

30. Схема по п.29, в которой упомянутое средство для управления величиной задержки А дополнительно содержит: средство для преобразования третьего сигнала в первый уровень напряжения, причем первый уровень напряжения указывает величину времени Т1; средство для преобразования четвертого сигнала во второй уровень напряжения, причем второй уровень напряжения указывает величину времени Т2; и средство для подачи первого и второго уровней напряжения на операционный усилитель, причем сигнал, выходящий из операционного усилителя, определяет, насколько задержанная версия А второго сигнала задержана относительно незадержанной версии А' второго сигнала.

31. Схема по п.27, в которой упомянутое средство для управления величиной задержки А дополнительно содержит:

средство для формирования третьего сигнала, указывающего величину времени Т1 между первым фронтом задержанной версии А второго сигнала и фронтом первого сигнала С; и средство для формирования четвертого сигнала, указывающего величину времени Т2 между фронтом первого сигнала С и вторым фронтом задержанной версии А второго сигнала.

32. Схема по п.27, в которой упомянутое средство для деления частоты входного сигнала дополнительно содержит средство для формирования третьего сигнала В, и причем упомянутое средство для управления величиной задержки А дополнительно содержит: средство для выполнения логической операции И над одним из первого, второго и третьего сигналов, и другим из первого, второго и третьего сигналов; и средство для выполнения логической операции И над упомянутым одним из первого, второго и третьего сигналов, и инверсией упомянутого другого из первого, второго и третьего сигналов.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Патрон-газообразователь для спасательного пояса | 1943 |

|

SU70059A1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

Авторы

Даты

2013-04-10—Публикация

2009-08-18—Подача