Настоящее изобретение относится к полупроводниковому устройству памяти и способу изготовления указанного устройства, в частности к высокоинтегрированному полупроводниковому устройству памяти и способу изготовления указанного устройства, в котором эффективная площадь конденсатора может быть максимизирована без расширения площадей ячеек памяти.

Известный уровень техники.

В областях технологий полупроводниковой памяти были предприняты конкурирующие усилия для увеличения числа ячеек памяти в чипе. Для достижения этой цели важно минимизировать площадь матрицы ячеек памяти, на которой множество ячеек памяти формируется в пределах ограниченной поверхности чипа.

В реализации минимальной площади ячейки памяти хорошо известна DRAM /Динамическая Память с Произвольным Доступом/, в которой индивидуальная ячейка имеет единственный транзистор и единственный конденсатор. Поскольку в вышеупомянутой ячейке памяти большая часть площади занята конденсатором, с развитием более высокой плотности упаковки высокоинтегрированного полупроводникового устройства памяти становится более важным увеличение емкости конденсатора наряду с минимизацией части площади полупроводника, занятой конденсатором так, чтобы облегчить обнаружение информации и уменьшить нерегулярные ошибки, вызванные альфа-частицами.

Для того, чтобы минимизировать площадь, занятую конденсатором, и максимизировать емкость конденсатора памяти, как описано выше, была предложена структура ячеек с распределенными штабелированными конденсаторами /ниже обозначенными SSC/, в которой электрод хранения каждой ячейки памяти растянут до зоны соседней ячейки памяти. Такая общепринятая ячейка памяти, имеющая структуру ячеек с SSC, описана на стр. 31-34 докладов Международной конференции по электронике 1989 г.

В предыдущей технологии, упомянутой выше, первые электроды конденсатора формируют растянутыми до зон соседних ячеек памяти экспонированием области истока каждой ячейки памяти на полупроводниковой кремниевой подложке, в которой формируются транзисторы. 64 Мбит DRAM может быть достигнуто в вышеуказанной структуре ячейки с SSC. Однако имеется ограничение для достижения достаточной хранящей поверхности конденсатора, требуемой для 256 Мбит DRAM, потому что первый конденсатор должен формироваться между вторыми конденсаторами, которые формируются впоследствии. То есть поскольку размер каждого конденсатора первых ячеек памяти ограничен каждым конденсатором вторых ячеек памяти, то расширения конденсаторов вторых ячеек памяти, которые расширяются влево и вправо, должны быть ограничены, чтобы сохранить баланс с размером каждого конденсатора первых ячеек памяти. Соответственно, каждый конденсатор вторых ячеек памяти не мог бы быть полностью расширен до конденсатора первых ячеек памяти, расположенных рядом со вторыми ячейками памяти, чтобы перекрыть максимальные площади вместе с первыми ячейками памяти. Размер каждого конденсатора первых ячеек памяти должен быть увеличен для поддержания баланса с указанными из конденсаторов первых ячеек памяти, а также и для расширения полностью каждого конденсатора вторых ячеек памяти до конденсатора примыкающих первых ячеек памяти. Однако поскольку в традиционной структуре ячеек с SSC размер каждого конденсатора первых ячеек памяти ограничен конденсатором вторых ячеек памяти, то эта структура не удовлетворяет цели достижения эффективной площади конденсатора требуемой для 256 Мбит DRAM, размер ячейки которой меньше, чем размер ячейки 64 Мбит DRAM.

Краткое изложение существа изобретения.

Следовательно, задачей настоящего изобретения является разработка DRAM, в которой для решения вышеописанных проблем традиционных технологий матрица ячеек памяти образована чередующимся расположением ячейки с конденсатором магазинного типа и ячейки с конденсатором комбинированного магазинно-щелевого типа, примыкающими друг к другу.

Другой задачей настоящего изобретения является разработка способа изготовления, который эффективно изготавливает DRAM, имеющую вышеупомянутую структуру.

Для решения вышеупомянутых задач матрица ячеек памяти в соответствии с настоящим изобретением выполняется как высокоинтегрированное полупроводниковое устройство памяти, включающее в себя множество ячеек памяти, каждая из которых имеет переключающий транзистор, сформированный на полупроводниковой подложке, и конденсатор магазинного типа, расположенный на переключающем транзисторе, электрод хранения каждого конденсатора магазинного типа первых ячеек памяти среди указанных ячеек памяти расширен до зон вторых ячеек памяти, расположенных рядом с первыми ячейками памяти, и электрод хранения каждого конденсатора магазинного типа вторых ячеек памяти расширен до зон примыкающих первых ячеек памяти так, что расширенные электроды хранения вторых ячеек памяти расположены рядом с первыми ячейками памяти, частично перекрываясь с расширенными электродами хранения первых ячеек памяти, в котором каждый конденсатор первых ячеек памяти включает в себя конденсатор магазинного типа и конденсатор щелевого типа, сформированный в области истока переключающего транзистора и в полупроводниковой подложке таким способом, что соответствующие первые и вторые ячейки памяти расположены, чередуясь и примыкая друг к другу в направлении ряда и в направлении колонки.

Настоящий способ для изготовления матрицы ячеек памяти, имеющей вышеупомянутую структуру, включает в себя первый процесс очерчивания активных областей наращиванием пространственных оксидных слоев на полупроводниковой подложке с первым типом проводимости; второй процесс формирования транзисторов, которые являются элементами ячейки памяти, на активных областях и формирования первого изолирующего слоя над получающейся в результате структурой; третий процесс формирования разрядных проводов для подключения к каждой области стока транзисторов и формирования второго изолирующего слоя над получающейся в результате структурой; четвертый процесс формирования первых окон для экспонирования предопределенных участков областей истока для формирования первых ячеек памяти, имеющих конденсатор комбинированного магазинно-щелевого типа; пятый процесс формирования щелей в полупроводниковой подложке посредством использования первых окон; шестой процесс формирования конденсатора как на внутренней поверхности щели, так и на втором изолирующей слое и затем формирование третьего изолирующего слоя на получающейся в результате структуре; седьмой процесс формирования вторых окон посредством экспонирования областей истока транзисторов, примыкающх к первым ячейкам памяти в направлении ряда или в направлении колонки; и девятый процесс формирования конденсатора магазинного типа через второе окно.

Краткое описание чертежей.

Настоящее изобретение будет описано в виде вариантов осуществления со ссылкой на прилагаемые чертежи, в которых

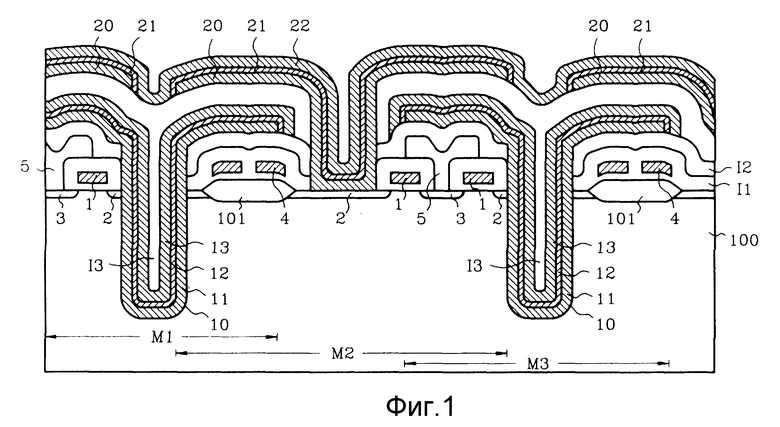

фиг. 1 - изображение частично в разрезе ячейки памяти в соответствии с настоящим изобретением;

фиг. от 2A до 2G показывают один вариант осуществления процесса для изготовления матрицы ячеек памяти в соответствии с настоящим изобретением и

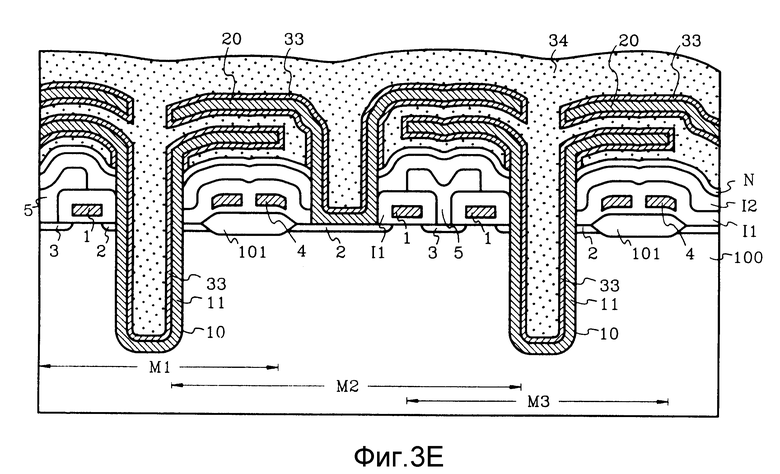

фиг. от 3A до 3E показывают другой вариант осуществления процессов для изготовления матрицы ячеек памяти в соответствии с настоящим изобретением.

Подробное описание предпочтительных вариантов осуществления.

В матрице ячеек памяти настоящего изобретения, как показано на фиг. 1, ячейки памяти М1 и М3, включающие в себя комбинированного магазинно-щелевого типа конденсаторы 11, 12 и 13, расположены, чередуясь и примыкая к ячейке памяти М2, имеющей конденсаторы 20, 21 и 22 магазинного типа. В ячейках памяти электроды 11 хранения /первые электроды конденсаторов/ первых и третьих ячеек М1 и М3 памяти расширены до примыкающей зоны вторых ячеек памяти, а электрод 20 хранения второй ячейки М2 памяти расширен до зон первых и третьих ячеек М1 и М3 памяти. Хотя матрица ячеек памяти, показанная на фиг. 1, иллюстрирована как имеющая ячейки памяти, примыкающие друг к другу в направлении ряда, матрица ячеек памяти в направлении колонки также имеет ячейки памяти, имеющие конденсатор комбинированного магазинно-щелевого типа, и ячейки памяти, имеющие конденсатор магазинного типа, которые расположены, примыкая друг к другу.

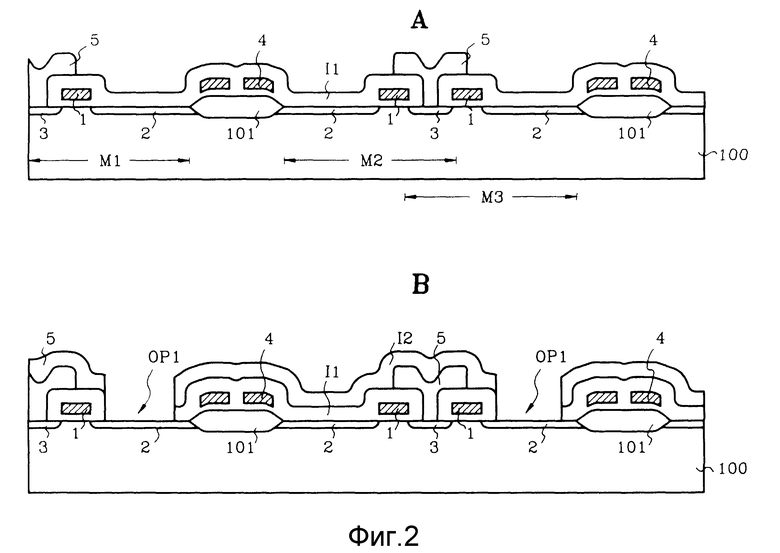

Фиг. от 2А до 2G иллюстрируют один вариант осуществления процессов для изготовления матрицы ячеек памяти в соответствии с настоящим изобретением.

Фиг. 2A иллюстрирует процесс для формирования транзисторов и разрядных линий 5 на полупроводниковой подложке 100, в которой активные области сначала очерчивают посредством наращивания пространственных оксидных слоев 101 в полупроводниковой подложке 100 с первым типом проводимости с помощью выборочного окисления. Легированные примесью первые слои поликристаллического кремния, которые должны быть электродами 1 затвора, формируют на активных областях введением оксидных слоев затвора и в то же время первые проводящие слои 4 транзисторов, например легированные примесью первые слои поликристаллического кремния, формируют на предопределенных участках пространственных оксидных слоев 101 так, что они соединяются с электродами затвора ячейки памяти, примыкающей к пространственным оксидным слоям. Область 2 истока и область 3 стока формируют на каждой стороне электродов 1 затвора в поверхности полупроводниковой подложки через ионную имплантацию, а затем первый изолирующий слой 11, например слой HTO /высокотемпературного оксида/ или слой LTO /низкотемпературного оксида/, имеющий толщину порядка  формируют над полной поверхностью вышеупомянутой структуры. С этого времени металлические слои 5, служащие в качестве разрядных линий, формируют после экспонирования некоторых участков стока. Здесь структура фиг. 2А включает в себя первые, вторые и третьи ячейки памяти М1, М2 и М3.

формируют над полной поверхностью вышеупомянутой структуры. С этого времени металлические слои 5, служащие в качестве разрядных линий, формируют после экспонирования некоторых участков стока. Здесь структура фиг. 2А включает в себя первые, вторые и третьи ячейки памяти М1, М2 и М3.

Фиг. 2B иллюстрирует процесс формирования второго изолирующего слоя 12 и первых окон ОР1, в которых после процесса, показанного на фиг. 2A, помещают второй изолирующий слой 12, имеющий толщину порядка  например слой HTO, и, используя на втором изолирующем слое шаблон маски, формируют первые окна ОР1 для экспонирования областей 2 истока первых и третьих ячеек М1 и М3 памяти.

например слой HTO, и, используя на втором изолирующем слое шаблон маски, формируют первые окна ОР1 для экспонирования областей 2 истока первых и третьих ячеек М1 и М3 памяти.

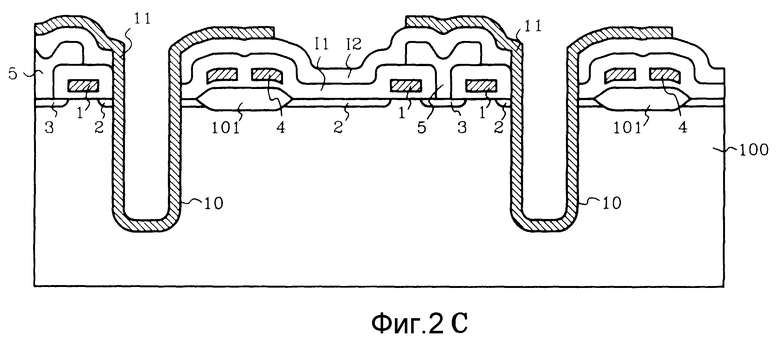

Фиг. 2C иллюстрирует процесс для формирования щелей 10 и вторых проводящих слоев 11, которые функционируют как первые электроды конденсаторов. Через первые окна ОР1 полупроводниковая подложка 100 вытравливается для формирования щелей 10, с этого времени вторые проводящие слои 11, служащие в качестве первых электродов конденсаторов, например легированные примесью вторые слои поликристаллического кремния, имеющие толщину порядка  помещают как на стенки щелей 10, так и на вторые изолирующие слои 12, формируя посредством этого рисунок электрода, как показано на фиг. 2C. Здесь глубина щели 10 может быть установлена в пределах около 0,5 мкм - 10 мкм в соответствии с заданным значением емкости.

помещают как на стенки щелей 10, так и на вторые изолирующие слои 12, формируя посредством этого рисунок электрода, как показано на фиг. 2C. Здесь глубина щели 10 может быть установлена в пределах около 0,5 мкм - 10 мкм в соответствии с заданным значением емкости.

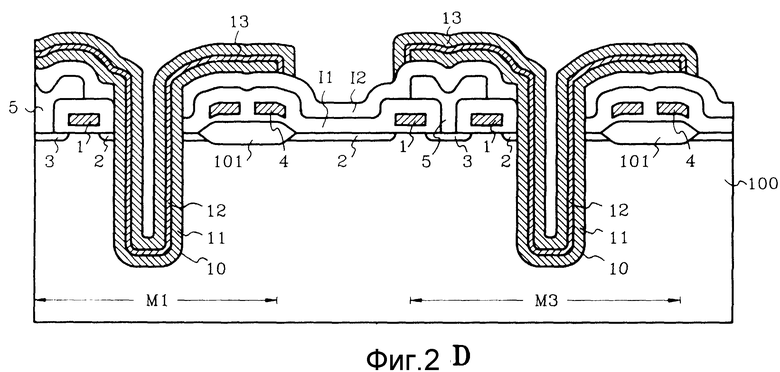

Фиг. 2D иллюстрирует процесс для формирования диэлектрических пленок 12 и третьих проводящих слоев 13, служащих в качестве вторых электродов конденсаторов. Диэлектрические пленки 12 и третьи проводящие слои 13, имеющие толщину порядка  , последовательно формируют, завершая тем самым первые ячейки М1 и М3 памяти, соответственно имеющие конденсаторы комбинированного магазинно-щелевого типа. Здесь диэлектрическая пленка 12 имеет структуру оксидного слоя, такую как слой HTO или слой LTO, или структуру оксид/нитрид/оксид, т. е. ONO-структуру, или структуру нитрид/оксид, т.е. NO-структуру. Здесь вместо комбинированного магазинно-щелевого конденсатора может быть сформирован внешний конденсатор щелевого типа, в котором заряд хранится во внешней области щели в полупроводниковой подложке.

, последовательно формируют, завершая тем самым первые ячейки М1 и М3 памяти, соответственно имеющие конденсаторы комбинированного магазинно-щелевого типа. Здесь диэлектрическая пленка 12 имеет структуру оксидного слоя, такую как слой HTO или слой LTO, или структуру оксид/нитрид/оксид, т. е. ONO-структуру, или структуру нитрид/оксид, т.е. NO-структуру. Здесь вместо комбинированного магазинно-щелевого конденсатора может быть сформирован внешний конденсатор щелевого типа, в котором заряд хранится во внешней области щели в полупроводниковой подложке.

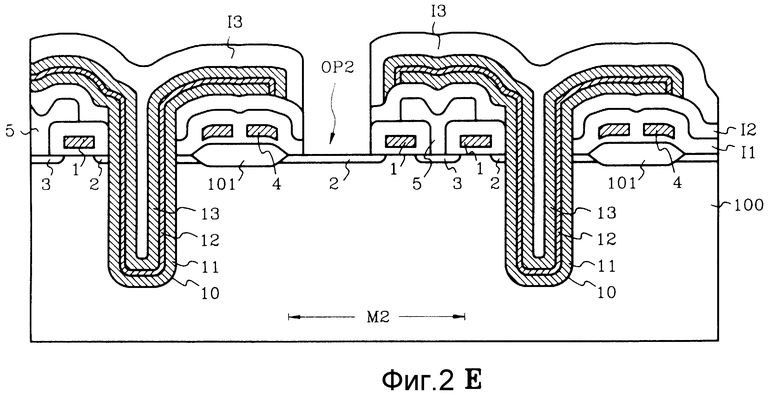

Фиг. 2E иллюстрирует процесс для формирования третьих изолирующих слоев 13 и второго окна ОР2. После процесса, показанного на фиг. 2D, наносят третий изолирующий слой 13, имеющий толщину порядка  например слой HTO, а затем формируют второе окно ОР2 для экспонирования области 2 истока второй ячейки М2 памяти. Здесь после нанесения BPSG (борофосфорное кремниевое стекло) слоя, имеющего толщину порядка

например слой HTO, а затем формируют второе окно ОР2 для экспонирования области 2 истока второй ячейки М2 памяти. Здесь после нанесения BPSG (борофосфорное кремниевое стекло) слоя, имеющего толщину порядка  может быть сформирован третий изолирующий слой посредством планаризации через процесс расплавления.

может быть сформирован третий изолирующий слой посредством планаризации через процесс расплавления.

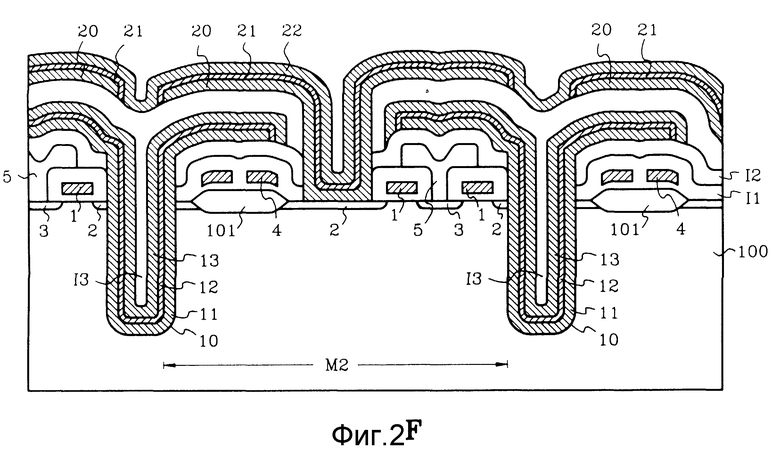

Фиг. 2F иллюстрирует процесс для формирования четвертого проводящего слоя 20, служащего в качестве первого электрода, диэлектрической пленки 21 и пятого проводящего слоя 22, служащего в качестве второго электрода конденсатора. После выполнения процесса, показанного на фиг. 2E, для образования электродного рисунка, как иллюстрируется на фиг. 2F, наносят четвертый проводящий слой 20, имеющий толщину порядка  который служит в качестве первого электрода конденсатора, например легированный примесью четвертый поликристаллический кремниевый слой. С этого момента над четвертым проводящим слоем 20 последовательно формируют диэлектрическую пленку 21 и пятый проводящий слой 22, имеющий толщину порядка

который служит в качестве первого электрода конденсатора, например легированный примесью четвертый поликристаллический кремниевый слой. С этого момента над четвертым проводящим слоем 20 последовательно формируют диэлектрическую пленку 21 и пятый проводящий слой 22, имеющий толщину порядка  который функционирует в качестве второго электрода конденсатора, посредством этого завершая вторую ячейку М2 памяти, имеющую конденсатор магазинного типа. Здесь диэлектрическая пленка 21 имеет структуру оксидного слоя, такую как слой НТО или слой LTO, ONO-структуру или NO-структуру.

который функционирует в качестве второго электрода конденсатора, посредством этого завершая вторую ячейку М2 памяти, имеющую конденсатор магазинного типа. Здесь диэлектрическая пленка 21 имеет структуру оксидного слоя, такую как слой НТО или слой LTO, ONO-структуру или NO-структуру.

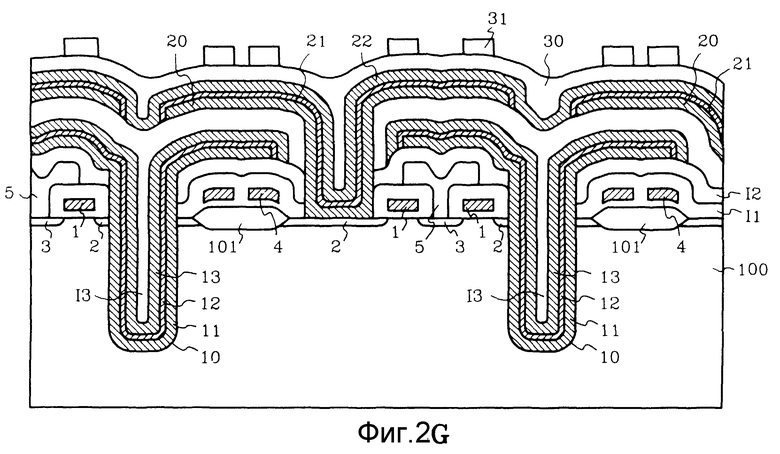

Фиг. 2G иллюстрирует процесс для формирования планаризирующего слоя 30 и металлических электродов 31, в котором после процесса, показанного на фиг. 2F, для планаризации наносят планаризирующий слой 30, например BPSG-слой, а затем формируют металлические электроды 31, посредством этого завершая DRAM, имеющую как ячейки с конденсатором магазинно-щелевого типа, так и ячейки с конденсатором магазинного типа.

Фиг. от 3A до 3E показывают другой вариант осуществления процесса для изготовления матрицы ячеек памяти в соответствии с настоящим изобретением.

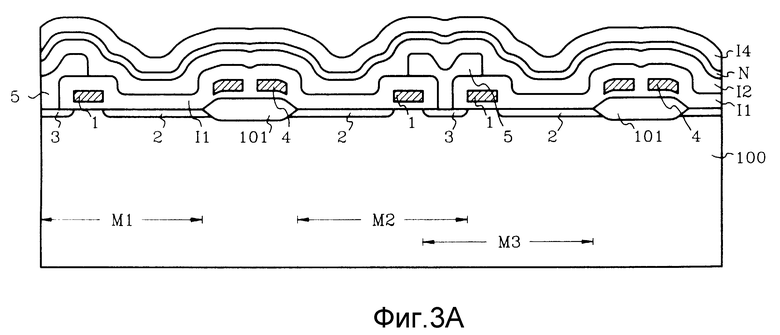

Процесс изготовления, предшествующий процессу фиг. 3A, идентичен процессу, описанному в связи с фиг. 2A, и поэтому опущен.

Фиг. 3A иллюстрирует процесс для формирования второго изолирующего слоя 12, нитридного слоя N и четвертого изолирующего слоя 14. После процесса, иллюстрируемого на фиг. 2A, формируют последовательно второй изолирующий слой 12, имеющий толщину порядка  например слой HTO, нитридный слой N, имеющий толщину порядка

например слой HTO, нитридный слой N, имеющий толщину порядка  и четвертый изолирующий слой 14, имеющий толщину порядка

и четвертый изолирующий слой 14, имеющий толщину порядка  например слой HTO.

например слой HTO.

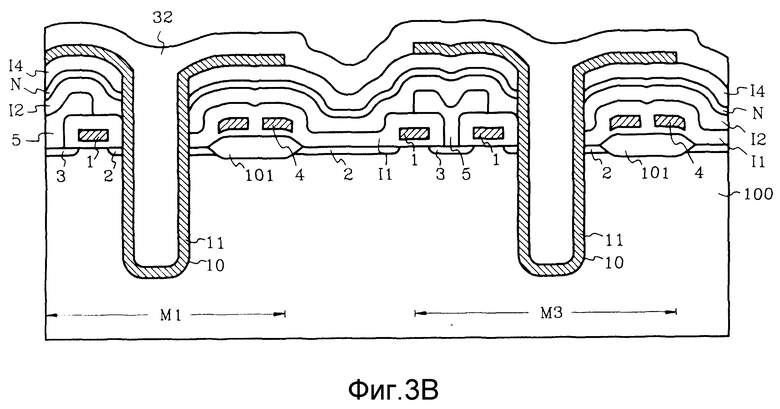

Фиг. 3B иллюстрирует процесс для формирования вторых проводящих слоев 11, служащих в качестве первых электродов конденсаторов, и взаимно планаризирующего слоя 32, в котором посредством наложения шаблона маски на четвертый изолирующий слой 14 формируют первые окна так, чтобы экспонировать области 2 истока первых и третьих ячеек М1 и М3 памяти. Полупроводниковую подложку вытравливают для формирования щелей 10 через первые окна, и с этого момента для формирования электродного рисунка наносят вторые проводящие слои 11, имеющие толщину порядка  которые служат в качестве электродов конденсаторов, например легированные примесью вторые поликристаллические кремниевые слои. Для планаризации наносят взаимно планаризирующий слой 32, например SOG (спин на стекле) слой. Во время процесса взаимно планаризирующий слой может быть сформирован из слоя, сложенного из SOG-слоя и слоя HTO, или слоя, сложенного из BPSG-слоя. Здесь глубина щели 10 может быть установлена в пределах около 0,5 мкм - 10 мкм в соответствии с желаемым значением емкости.

которые служат в качестве электродов конденсаторов, например легированные примесью вторые поликристаллические кремниевые слои. Для планаризации наносят взаимно планаризирующий слой 32, например SOG (спин на стекле) слой. Во время процесса взаимно планаризирующий слой может быть сформирован из слоя, сложенного из SOG-слоя и слоя HTO, или слоя, сложенного из BPSG-слоя. Здесь глубина щели 10 может быть установлена в пределах около 0,5 мкм - 10 мкм в соответствии с желаемым значением емкости.

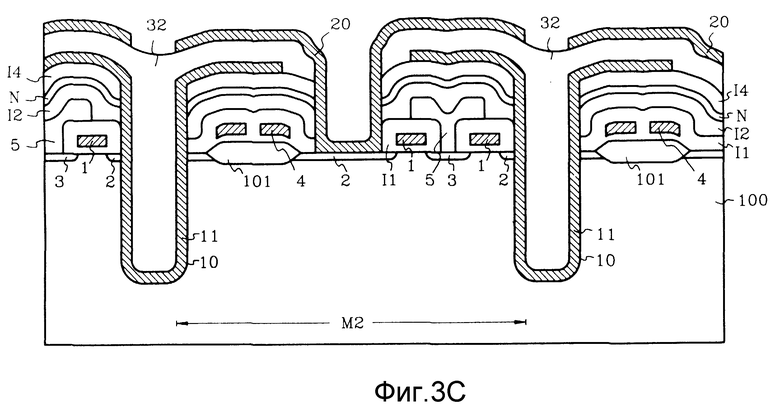

Фиг. 3C иллюстрирует процесс для формирования второго окна и четвертого проводящего слоя 20, который функционирует в качестве первого электрода конденсатора. После формирования взаимно планаризирующего слоя 32 формируют второе окно для экспонирования области 2 истока второй ячейки М2 памяти. С этого момента на обе поверхности второго окна и на взаимно планаризирующий слой 32 наносят четвертый проводящий слой 20, имеющий толщину порядка  который функционирует в качестве первого электрода конденсатора, например легированный примесью четвертый поликристаллический кремниевый слой, так, чтобы сформировать электродный рисунок, как показано на фиг. 3C.

который функционирует в качестве первого электрода конденсатора, например легированный примесью четвертый поликристаллический кремниевый слой, так, чтобы сформировать электродный рисунок, как показано на фиг. 3C.

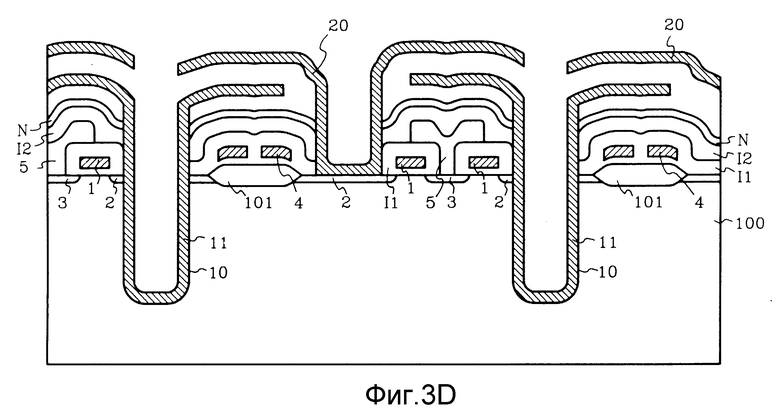

Фиг. 3D иллюстрирует процесс для удаления четвертого изолирующего слоя и взаимно планаризирующего слоя, в котором посредством использования нитридного слоя в качестве слоя, блокирующего травление, влажным травлением удаляют четвертый изолирующий слой и взаимно планаризирующий слой, который расположен между вторым проводящим слоем 11 и четвертым проводящим слоем 20, посредством этого увеличивая область поверхности первого электродного рисунка каждой ячейки памяти.

Фиг. 3E иллюстрирует процесс для формирования диэлектрической пленки 33 и шестого проводящего слоя 34, служащего в качестве второго электрода конденсатора. После процесса, показанного на фиг. 3D, диэлектрическую пленку 33 одновременно формируют как на втором проводящем слое 11, так и на четвертом проводящем слое 20, а затем наносят шестой проводящий слой 34, служащий в качестве второго электрода конденсатора, имеющего толщину порядка  например легированный примесью шестой поликристаллический кремниевый слой, посредством этого завершая первую и третью ячейки М1 и М3 памяти и вторую ячейку М2 памяти. Здесь диэлектрическая пленка 33 имеет структуру оксидного слоя или ONO-структуру, такую как слой HTO или слой LTO.

например легированный примесью шестой поликристаллический кремниевый слой, посредством этого завершая первую и третью ячейки М1 и М3 памяти и вторую ячейку М2 памяти. Здесь диэлектрическая пленка 33 имеет структуру оксидного слоя или ONO-структуру, такую как слой HTO или слой LTO.

После выполнения процесса, иллюстрируемого на фиг. 3E, планаризирующий слой, например BPSG-слой, наносят в целях планаризации, а затем формируют металлические электроды, посредством этого завершая DRAM, имеющую как ячейки с конденсатором магазинно-щелевого типа, так и ячейки с конденсатором магазинного типа.

Как описано выше, в качестве конденсатора в соответствии с настоящим изобретением используется конденсатор комбинированного магазинно-щелевого типа как первый конденсатор традиционной структуры с SSC и используется конденсатор магазинного типа как второй конденсатор традиционной структуры с SSC. Соответственно, при изготовлении конденсатора комбинированного магазинно-щелевого типа /или щелевого типа/ достаточная хранящая поверхность каждого конденсатора может быть получена без ограничения ее расстоянием между вторыми конденсаторами, т.е. конденсаторами магазинного типа. Вдобавок, в течение формирования второго конденсатора /конденсатора магазинного типа/ первый конденсатор, т. е. конденсатор комбинированного магазинно-щелевого типа /щелевого типа/ может заметно уменьшить проблему шагового перекрытия по сравнению с традиционным первым конденсатором, т.е. конденсатором магазинного типа, так, что процессы легко выполнить.

Кроме того, в матрице ячеек памяти настоящего изобретения, поскольку первые ячейки памяти, имеющие конденсаторы комбинированного магазинно-щелевого типа /или щелевого типа/, и вторые ячейки памяти, имеющие конденсаторы магазинного типа, располагают вплотную друг к другу как в направлении ряда, так и в направлении колонки, то поочередно формируются ячейки памяти, имеющие щель. В результате является преимуществом то, что ток утечки между ячейками памяти со щелью и нерегулярные ошибки, вызванные альфы-частицами, могут быть устранены. Кроме того, путем травления оксидного слоя и взаимно планаризирующего слоя, нанесенных под проводящим слоем, служащим в качестве первого электрода в конденсаторе второго варианта осуществления настоящего изобретения, поверхности верхнего участка бокового участка, а также нижнего участка проводящего слоя используют как первый электрод конденсатора, так что хранящая поверхность конденсатора может быть максимизирована. Следовательно, уменьшение емкости, вызванное увеличением плотности высокоинтегрированного полупроводникового устройства памяти, может быть компенсировано средствами структурного подхода.

Устройство включает в себя множество ячеек памяти, образованных поочередным нанесением ячейки с конденсатором магазинного типа и ячейки с конденсатором комбинированного магазинно-щелевого типа в направлениях как ряда, так и колонки. Каждый электрод хранения конденсатора ячейки памяти расширяют, чтобы перекрыть с электродом хранения конденсатора смежной ячейки памяти. Конденсатор комбинированного магазинно-щелевого типа формируют в подложке для увеличения хранящей емкости, что позволяет хранящую емкость конденсатора магазинного типа увеличить посредством расширения электрода хранения конденсатора. Благодаря чередующемуся расположению конденсатора магазинно-щелевого типа и конденсатора магазинного типа предупреждается шаговое перекрытие, ток утечки и нерегулярные ошибки конденсатора магазинно-щелевого типа. 2 с. и 15 з.п.ф-лы, 3 ил.

после шага формирования конденсатора первой ячейки памяти.

после шага формирования конденсатора первой ячейки памяти.

| С.Инау и др | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| ТЕДМ (Международная конференция по электронике), 3-6 декабря 1989, с.31-34 | |||

| УСТРОЙСТВО РЕЗОНАНСНОЙ ИМПУЛЬСНОЙ ЭЛЕКТРОМАГНИТНОЙ СВЯЗИ ДЛЯ ПОВЫШЕНИЯ ПЛОДОРОДИЯ ПОЧВ | 2002 |

|

RU2219690C1 |

| СПОСОБ ПОЛУЧЕНИЯ СТАБИЛЬНЫХ СОПОЛИМЕРОВ ТРИОКСАНА | 1992 |

|

RU2043999C1 |

| ИСПОЛНИТЕЛЬНЫЙ МЕХАНИЗМ РУЛЕВОГО НРИВОДА | 0 |

|

SU295709A1 |

| US 4742018 A, 1988 | |||

| US 4805147 A, 1988 | |||

| US 4811067 A, 1989 | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Полупроводниковая интегральная схема | 1978 |

|

SU820546A1 |

Авторы

Даты

1999-03-20—Публикация

1990-11-14—Подача