w

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации в корреляционном приемнике | 1983 |

|

SU1256224A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 1995 |

|

RU2099893C1 |

| СПОСОБ КОРРЕЛЯЦИОННОГО ПРИЁМА СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2237978C2 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Устройство для формирования синхроимпульсов | 1983 |

|

SU1083388A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

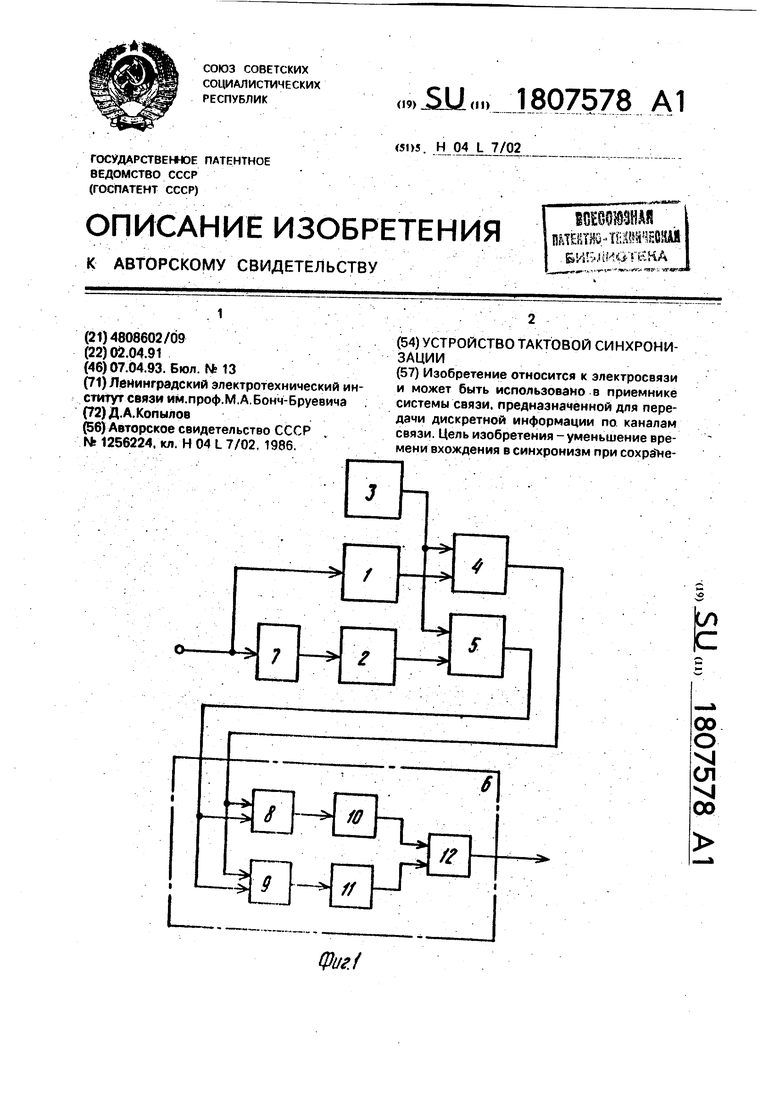

Изобретение относится к электросвязи и может быть использовано в приемнике системы связи, предназначенной для передачи дискретной информации по. каналам связи. Цель изобретения -уменьшение времени вхождения в синхронизм при сохрахе

Фм-f

нии точности и помехоустойчивости синхронизации в условиях несимметричного входного сигнала. Устройство тактовой синхронизации содержит первый и второй блоки выделения 1 и 2 синхронизации, генератор 3 импульсов, первый и второй блоки фазирования 4 и 5, дешифратор 6 и инвертор 7, причем в состав дешифратора 6 входят сумматор 8, блок вычисления 9 модуля разности 9, первый и второй пороговые блоки 10 и 11 и элемент исключающее ИЛИ 12. В устройстве в случае несимметричного входного сигнала происходит разделение синхроинформации на опережающую и заИзобретение относится к электросвязи и может быть использовано в приемнике системы передачи дискретной информации по каналам связи.

Целью изобретения является уменьше Vine времени вхождения в синхронизм при сохранении точности и помехоустойчивости синхронизации в условиях несимметричного входного сигнала.:

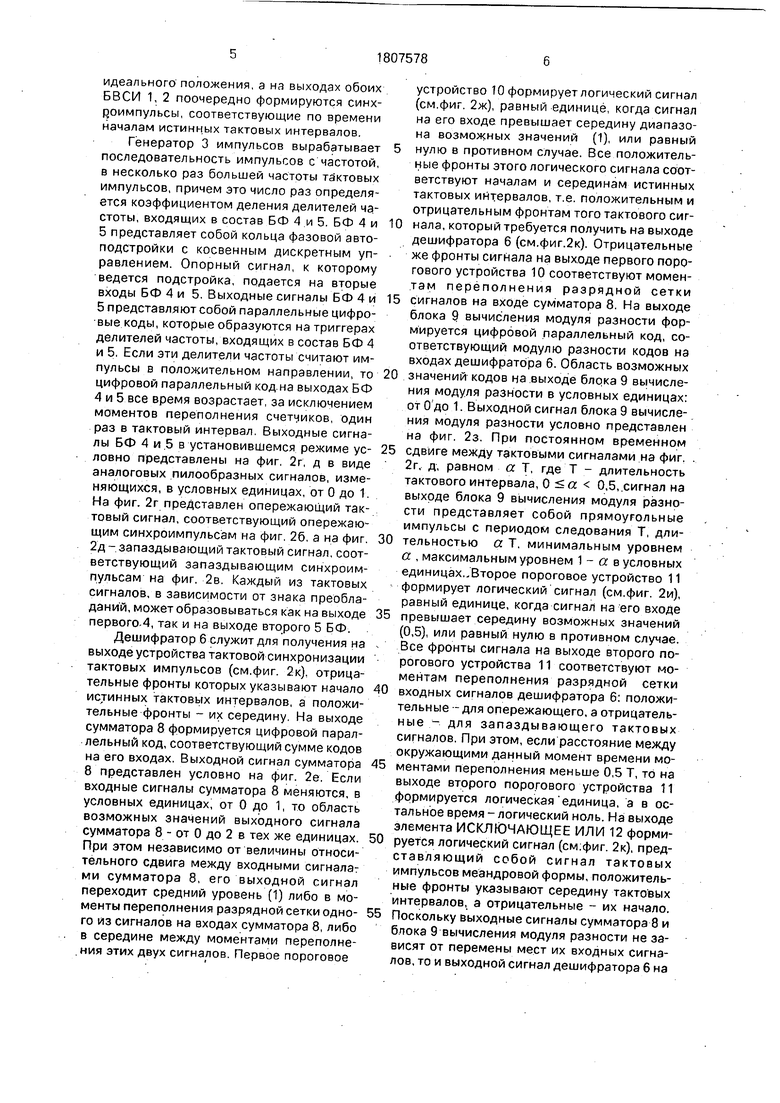

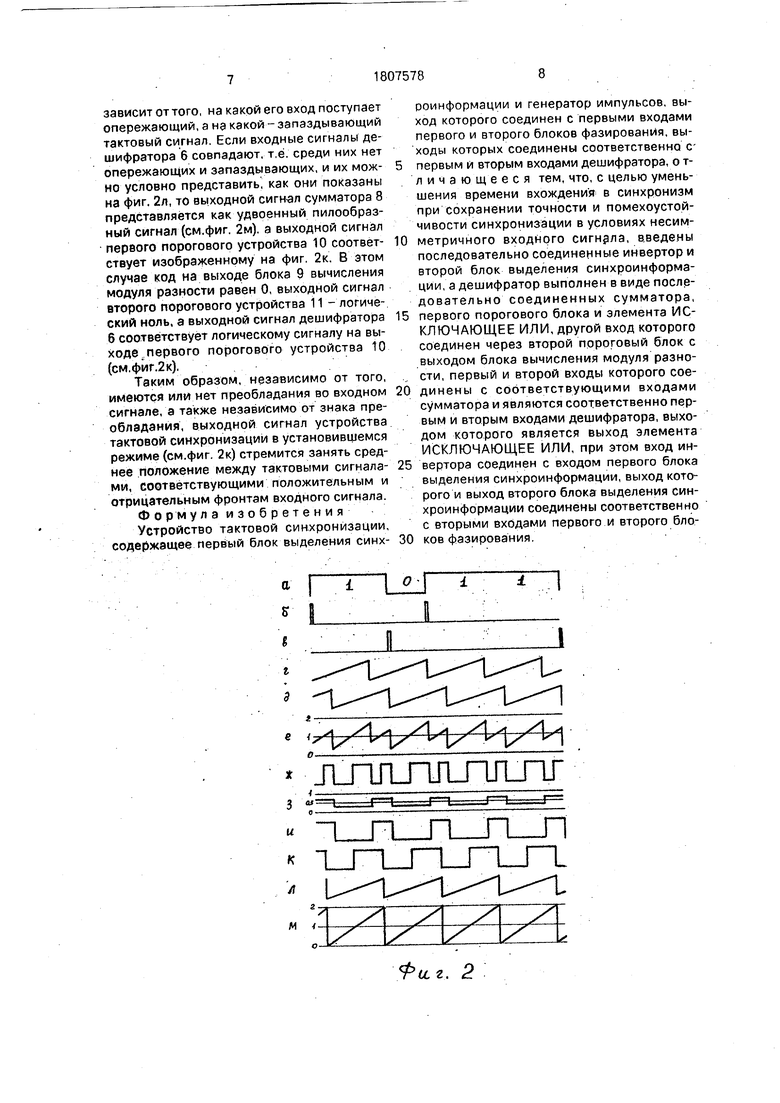

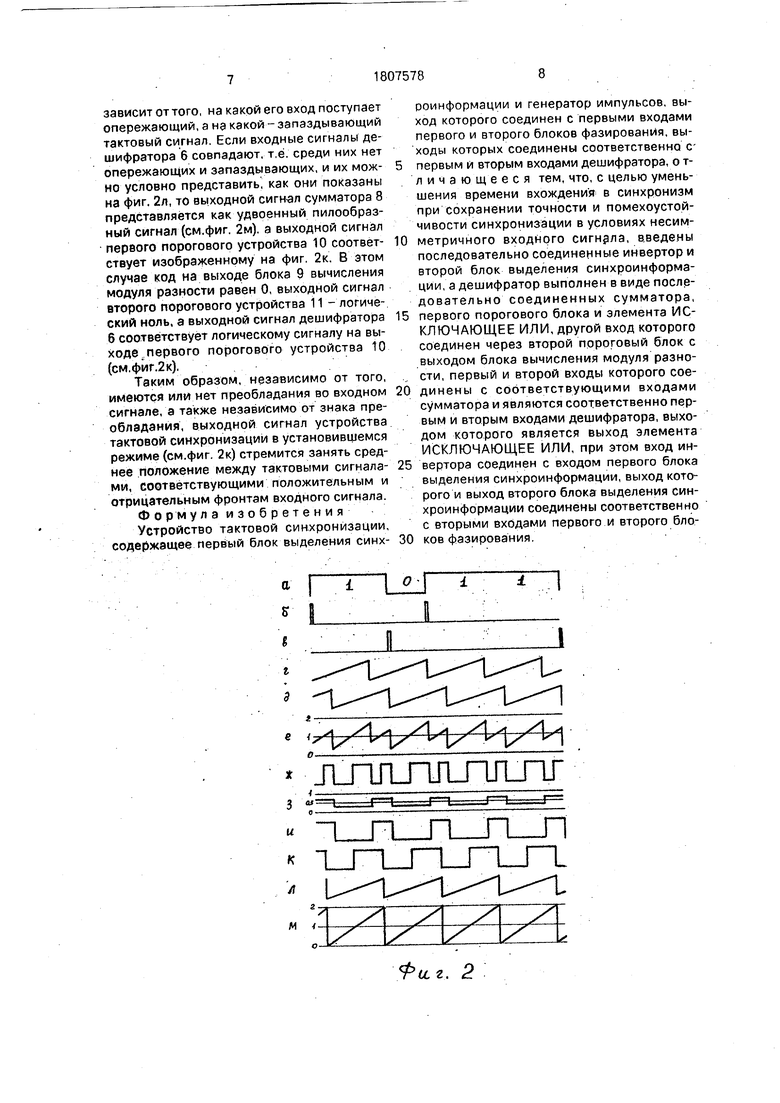

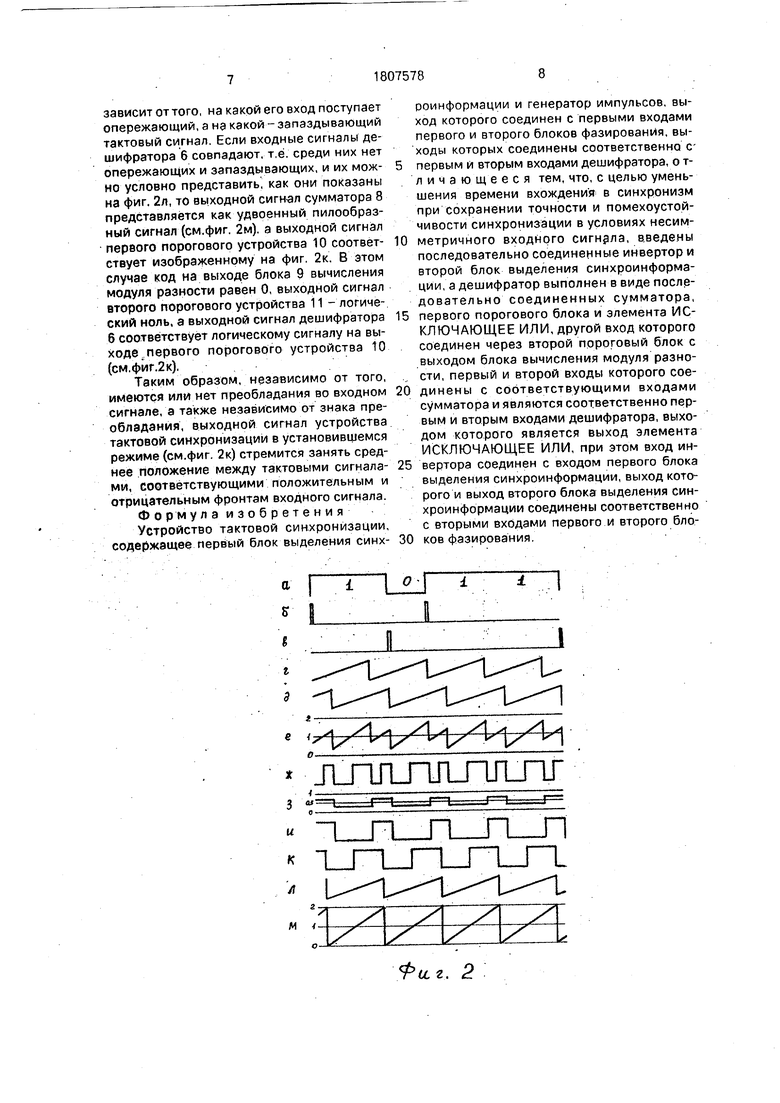

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство тактовой синхронизации содержит (см.фиг.1) первый 1 и второй 2 блоки выделения синхроинформации (БВСИ), генератор 3 импульсов, первый 4 и второй 5 блоки фазирования (БФ), дешифратор 6 и инвертор 7. Дешифратор 6 содержит сумматор 8, блок 9 вычисления модуля разности, первое 10 и второе 11 пороговые устройства и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

устройства тактовой синхронизации является входами первого БВСИ 1 и инвертора 7. Выход инвертора 7 соединен со входом второго БВСИ 2. Выход генератора 3 импульсов соединён с первыми входами первого и второго БФ 4 и 5. Выходы первого 1 и второго 2 БВСИ подключены ко вторым входам первого 4 и второго 5 БФ, соответственно. Выходы первого 4 и второго 5 БФ подключены к первому и второму входам дешифратора 6, соответственно. Первый и второй входы дешифратора 6 являются, соответственно, первыми и вторыми входами сумматора 8 и блока 9 вычисления модуля разности. Выходы сумматора 8 и блока 9 вычисления модуля разности Соединены со входами первого 10 и второго 11 пороговых устройств, соответственно. Выходы первого и второго пороговых устройств 10, 11 соединены с соответствуюпаздывающую в первом и втором блоках выделения 1 и 2 по разным фронтам входного сигнала, а дешифратор 6 формирует выходные импульсы, положительные фронты которых соответствуют по времени середине между положительными фронтами опережающих и запаздывающих тактовых импульсов, а отрицательные фронты - середине между отрицательными фронтами опережающих и запаздывающих, тактовых импульсов, что обеспечивает исключение вспомогательного инерционного процесса автоподстройки. 2 ил.

щими входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 является выходом дешифратора 6, Выход дешифратора 6 является выходом устройства.

Устройство тактовой синхронизации работает следующим образом. На вход устройства подается двоичный цифровой сигнал с выхода демодулятора. Неидеальность работы демодулятора может привести к тому, что входной сигнал окажется несимметричным. Пример несимметричного входного сигнала при наличии в нем преобладаний единицы представлен на

фиг. За. Положительные фронты такого сигнала смещены влево, а отрицательные - вправо относительно их идеального положения. При преобладаниях нуля, положительные фронты входного сигнала смещены

вправо, а отрицательные - влево. Каждый из БВСИ 1, 2 вырабатывает короткий положительный: .

синхроимпульс при приходе на его вход положительного фронта сигнала. При этом,

синхроимпульсы на выходе первого БВСИ 1 (см.фиг. 2б)соответствукхг по времени положительным фронтам входного сигнала устройства, а на выходе второго БВСИ 2 (см.фиг. 2в) - отрицательным фронтам того

же сигнала, в связи с наличием инвертора 7. При несимметричном входном сигнале с преобладаниями единицы на выходе первого БВСИ 1 формируются Опережающие синхроимпульсы, а на выходе второго БВСИ 2 запаздывающие синхроимпульсы. В случае входного сигнала с преобладаниями нуля на выходе первого БВСИ 1 формируются запаздывающие, а на выходе второго БВСИ 2 - опережающие синхроимпульсы. При отсутствии преобладаний фронты входного сигнала не смещены относительно их

идеального положения, а на выходах обоих БВСИ 1, 2 поочередно формируются синхроимпульсы, соответствующие по времени началам истинных тактовых интервалов.

Генератор 3 импульсов вырабатывает последовательность импульсов с частотой, в несколько раз большей частоты та ктовых импульсов, причем это число раз определяется коэффициентом деления делителей частоты, входящих в состав БФ 4 и 5. БФ 4 и 5 представляет собой кольца фазовой автоподстройки с косвенным дискретным управлением. Опорный сигнал, к которому ведется подстройка, подается на вторые входы БФ А и 5. Выходные сигналы БФ 4 и 5 представляют собой параллельные цифровые коды, которые образуются на триггерах делителей частоты/входящих в состав БФ 4 и 5. Если эти делители частоты считают импульсы в положительном направлении, то цифровой параллельный код на выходах БФ 4 и 5 все время возрастает, за исключением моментов переполнения счетчиков, один раз в тактовый интервал. Выходные сигналы БФ 4 и .5 в установившемся режиме условно представлены на фиг. 2г, д в виде аналоговых пилообразных сигналов, изменяющихся, в условных единицах, от 0 до 1. На фиг. 2г представлен опережающий тактовый сигнал, соответствующий опережающим синхроимпульсам на фиг. 26, а на фиг. 2д- запаздывающий тактовый сигнал, соответствующий запаздывающим синхроимпульсам на фиг. 2в. Каждый из тактовых сигналов, в зависимости от знака преобладаний, может образовываться как на выходе первого.4, так и на выходе второго 5 БФ.

Дешифратор 6 служит для получения на выходе устройства тактовой синхронизации тактовых импульсов (см.фиг. 2к), отрицательные фронты которых указывают начало истинных тактовых интервалов, а положительные фронты - их середину. На выходе сумматора 8 формируется цифровой параллельный код, соответствующий сумме кодов на его входах. Выходной сигнал сумматора 8 представлен условно на фиг. 2е. Если входные сигналы сумматора 8 меняются, в условных единицах; от 0 до 1, то область возможных значений выходного сигнала сумматора 8 - от 0 до 2 в тех же единицах. При этом независимо от величины относительного сдвига между входными сигнала ми сумматора 8, его выходной сигнал переходит средний уровень (1) либо в моменты переполнения разрядной сетки одного из сигналов на входах сумматора 8, либо в середине между моментами переполне- . ния этих двух сигналов. Первое пороговое

устройство 10 формирует логический сигнал (см.фиг. 2ж), равный единице, когда сигнал на его входе превышает середину диапазона возможных значений (1), или равный 5 нулю в противном случае. Все положительные фронты этого логического сигнала соответствуют началам и серединам истинных тактовых интервалов, т.е. положительным и отрицательным фронтам того тактового сиг0 нала, который требуется получить на выходе дешифратора 6 (см.фиг.2к). Отрицательные же фронты сигнала на выходе первого порогового устройства 10 соответствуют моментам переполнения разрядной сетки

5 сигналов на входе сумматора 8. На выходе блока 9 вычисления модуля разности формируется цифровой параллельный код, соответствующий модулю разности кодов на входах дешифратора 6. Область возможных

0 значений кодов на .выходе блрка 9 вычисления модуля разности в условных единицах: от 0 до 1. Выходной сигнал блока 9 вычисления модуля разности условно представлен на фиг. 2з. При постоянном временном

5 сдвиге между тактовыми сигналами на фиг. 2г, д, равном а Т, где Т - длительность тактового интервала, 0 а 0,5,.сигнал на выходе блока 9 вычисления модуля разности представляет собой прямоугольные импульсы с периодом следования Т, дли0 тельностью о. Т. минимальным уровнем G. , максимальным уровнем 1 - а в условных единицах.,Второе пороговое устройство 11 формирует логический сигнал (см.фиг. 2и), равный единице, когда сигнал на его входе

5 превышает середину возможных значений (0,5), или равный нулю в противном случае. Все фронты сигнала на выходе второго порогового устройства 11 соответствуют моментам переполнения разрядной сетки

0 входных сигналов дешифратора 6: положительные -для опережающего, а отрицательные - для запаздывающего тактовых сигналов. При этом, если расстояние между окружающими данный момент времени мо5 ментами переполнения меньше 0,5 Т, то на выходе второго порогового устройства 11 формируется логическая единица, а в остальное время -логический ноль. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 форми0 руется логический сигнал (см;фиг. 2к), пред- стэвляющий собой сигнал тактовых импульсов меандровой формы, положительные фронты указывают середину тактовых интервалов, а отрицательные - их начало.

5 Поскольку выходные сигналы сумматора 8 и блока 9 вычисления модуля разности не зависят от перемены мест их входных сигналов, то и выходной сигнал дешифратора 6 на

зависит от того, на какой его вход поступает опережающий, а на какой - запаздывающий тактовый сигнал. Если входные сигналы дешифратора 6 совпадают, т.е. среди них нет опережающих и запаздывающих, и их мож- но условно представить, как они показаны на фиг. 2л, то выходной сигнал сумматора 8 представляется как удвоенный пилообразный сигнал (см.фиг, 2м). а выходной сигнал первого порогового устройства 10 соответ- ствует изображенному на фиг. 2к. В этом случае код на выходе блока 9 вычисления модуля разности равен 0, выходной сигнал второго порогового устройства 11 - логический ноль, а выходной сигнал дешифратора б соответствует логическому сигналу на выходе первого порогового устройства 10 (см.фиг.2к).

Таким образом, независимо от того, имеются или нет преобладания во входном сигнале, а также независимо от знака преобладания, выходной сигнал устройства тактовой синхронизации в установившемся режиме (см.фиг. 2к) стремится занять среднее положение между тактовыми сигнала- ми, соответствующими положительным и отрицательным фронтам входного сигнала. Ф о р м у л а и з о б р е т е н и я Устройство тактовой синхронизации, содержащее первый блок выделения синх-

: I

s

« /JOinJTJUinJTT

роинформации и генератор импульсов, выход которого соединен с первыми входами первого и второго блоков фазирования, выходы которых соединены соответственна с- первым и вторым входами дешифратора, о т- л и ч а ю щ е е с я тем, что, с целью уменьшения времени вхождения в синхронизм при сохранении точности и помехоустойчивости синхронизации в условиях несимметричного входного сигнала, введены последовательно соединенные инвертор и второй блок выделения синхроинформа- ции, а дешифратор выполнен в виде последовательно соединенных сумматора, первого порогового блока и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход которого соединен через второй пороговый блок с выходом блока вычисления модуля разности, первый и второй входы которого соединены с соответствующими входами сумматора и являются соответственно первым и вторым входами дешифратора, выходом которого является выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом вход инвертора соединен с входом первого блока выделения синхроинформации, выход которого и выход второго блока выделения синхроинформации соединены соответственно с вторыми входами первого и второго блоков фазирования.

| Авторское свидетельство СССР | |||

| Устройство тактовой синхронизации в корреляционном приемнике | 1983 |

|

SU1256224A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-04-07—Публикация

1991-04-02—Подача