Изобретение относится к обработке сигнала, в частности к суммированию и объединению аналоговых сигналов.

Необходимость суммирования и объединения различных аналоговых сигналов обычно встречается во многих системах. Это используется в частотных модуляторах, где необходимо суммировать несколько входных сигналов и объединять до ввода в фазовый модулятор. Интегратор, однако, имеет очень высокий коэффициент передачи при постоянном токе и большинство входных сигналов будут иметь соответственно этому напряжение смещения постоянного тока. Следовательно, необходимы средства для уменьшения уровней смещения по постоянному току для защиты компонентов схемы интегратора от насыщения и для увеличения динамического диапазона выходного сигнала.

На фиг. 1 показана известная из предшествующего уровня техники схема сумматора/интегратора. Два или более входных сигнала 110 вначале суммируются сумматором 115, как это известно в данной области техники. Выход сумматора 120 связан с развязывающим по постоянному току конденсатором 130. Так как в типовом выполнении эта схема реализуется в виде интегральной микросхемы, а из-за того, что необходимые размеры развязывающего конденсатора должны быть гораздо больше допустимых для его выполнения в виде микросхемы, то такой развязывающий конденсатор представляет собой дискретный компонент, внешний по отношению к интегральной микросхеме. Связь развязывающего по постоянному току конденсатора с интегральной схемой осуществляется посредством выходных выводов 125 и 135 соответственно. Резистор 140 используется для подключения вывода фильтра высоких частот, состоящего из резистора и развязывающего по постоянному току конденсатора. Наконец, интегратор 150, как это известно в данной области техники, интегрирует сигнал и выдает выходной сигнал 155.

Примеры выполнения и особенности настоящего изобретения станут более очевидными из нижеследующего описания со ссылками на чертежи, на которых представлено следующее:

Фиг. 1 - схема, обеспечивающая функции суммирования и объединения в соответствии с известным уровнем техники.

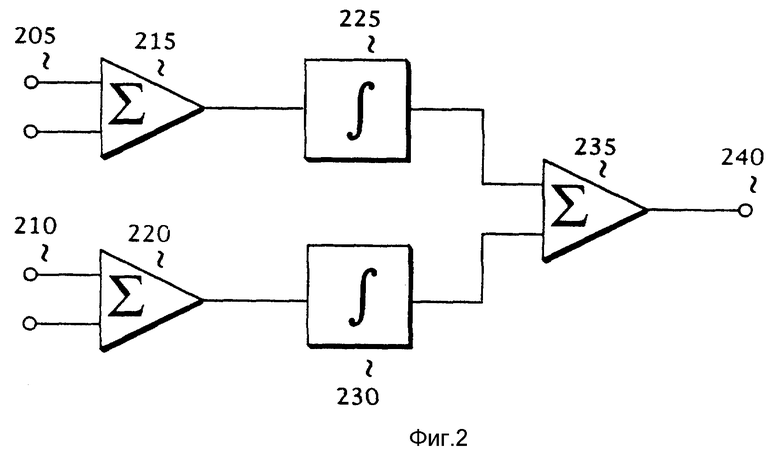

Фиг. 2 - блок-схема конфигурации схемы, выполненной в соответствии с настоящим изобретением.

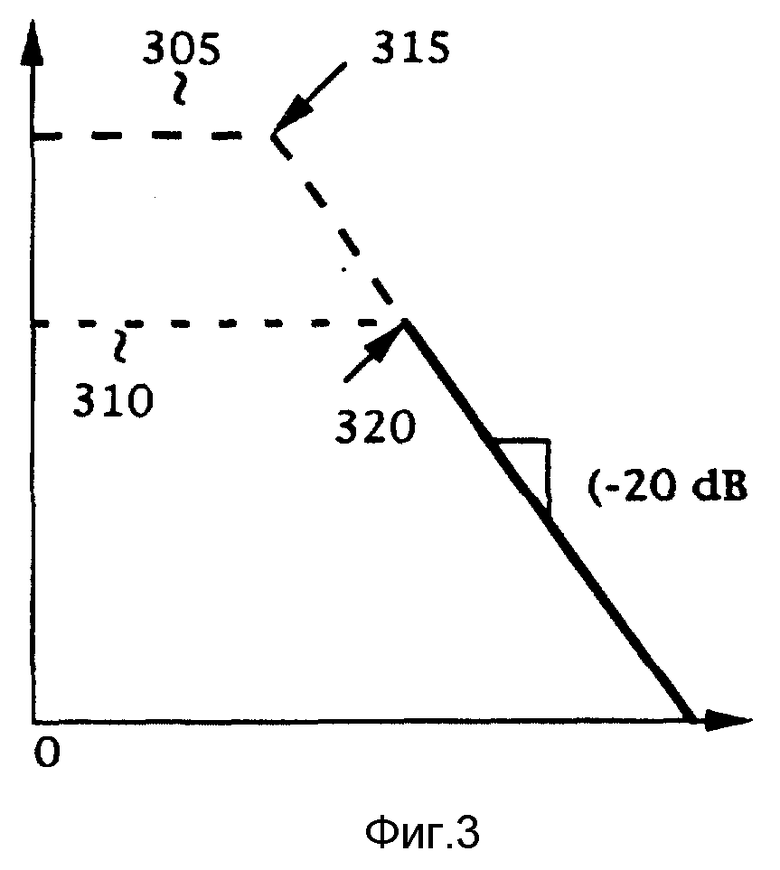

Фиг. 3 - график частотного отклика, иллюстрирующий частотную характеристику интеграторов в соответствии с настоящим изобретением.

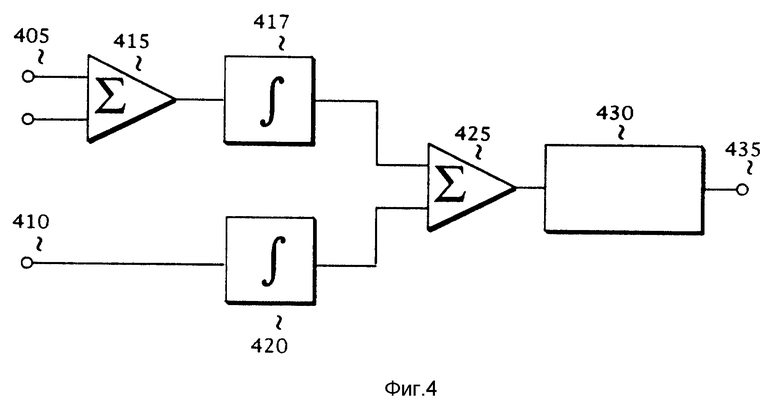

Фиг. 4 - блок-схема частотного модулятора в соответствии с настоящим изобретением.

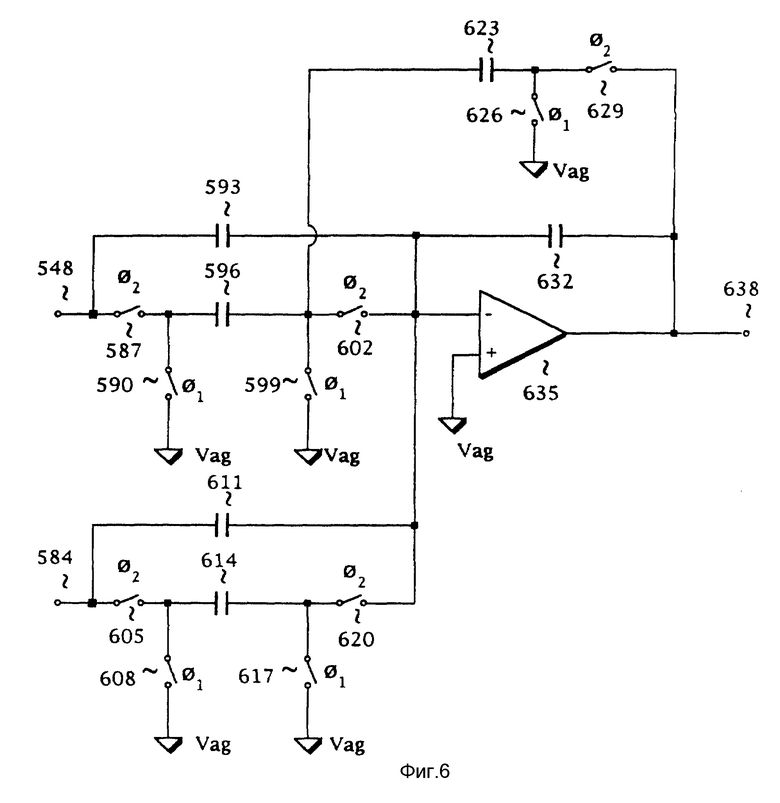

Фиг. 5 и 6 - схема, иллюстрирующая конфигурацию схемы коммутации конденсаторов в соответствии с настоящим изобретением.

Фиг. 7 - блок-схема радиопередатчика, выполненного в соответствии с настоящим изобретением.

Настоящее изобретение решает упомянутые выше и другие задачи за счет описанных ниже и иных признаков изобретения. Суммирование и объединение множества входных сигналов осуществляется без использования развязывающего по постоянному току конденсатора больших размеров.

В соответствии с настоящим изобретением предусмотрена конфигурация схемы, показанная на фиг. 2. Входные сигналы группируются в соответствии с их частотными диапазонами. Те, которые имеют низкочастотное содержимое, группируются в группу 205 входных сигналов, а те, которые имеют более высокочастотное содержимое, группируются в группу 210 входных сигналов. Низкочастотные и высокочастотные группы суммируются в сумматорах 215 и 220 соответственно. Просуммированные низкочастотные сигналы затем интегрируются интегратором с низкой опорной частотой 225, а высокочастотные сигналы интегрируются интегратором с высокой опорной частотой 230. Выходные сигналы обоих интеграторов суммируются в сумматоре 235 для выдачи на выход 240.

Как высокочастотная, так и низкочастотная группы входных сигналов имеют соответствующие им напряжения смещения постоянного тока. Для отмены необходимости в развязывающем по постоянному току конденсатора, необходимо уменьшить влияние этих напряжений смещения постоянного тока. Настоящее изобретение осуществляет это путем установки опорных частот /частот полюсов/ высоко- и низкочастотного интегратора таким образом, чтобы уменьшить влияние этих постоянных составляющих. Настоящее изобретение предусматривает полностью интегрированное устройство для объединения совокупности входных сигналов. Нет необходимости в конденсаторе большой емкости, развязывающем по постоянному току. Кроме того, не используются два входных и выходных вывода в интегральной схеме.

На фиг. 3 показан график частотной характеристики, который показывает частотные характеристики интеграторов как с высокой опорной частотой, так и с низкой опорной частотой. Группа низкочастотных входных сигналов имеет частотное содержимое, для которого необходима низкая опорная частота 315 для интегратора с низкой опорной частотой. Эта опорная частота определяет коэффициент передачи постоянного тока интегратора 305 с низкой опорной частотой. Высокочастотная группа входных сигналов не требует такой низкой опорной частоты и интегратор с высокой опорной частотой имеет более высокую опорную частоту 320. Это позволяет уменьшить коэффициент передачи по постоянному току интегратора 310 с высокой опорной частотой по сравнению с интегратором с низкой опорной частотой. Путем уменьшения коэффициента передачи этого интегратора уменьшаются составляющие постоянного тока, связанные с высокочастотной группой входных сигналов. Тем самым исключается необходимость в развязывающем по постоянному току конденсаторе.

На фиг. 4 показан частотный модулятор, выполненный в соответствии с настоящим изобретением. Три входных сигнала делятся на группу 405 двух сигналов с низкочастотным содержимым и на единичный сигнал 410 с высокочастотным содержимым. В соответствии с настоящим изобретением возможно использование любого количества входных сигналов или групп входных сигналов. В зависимости от частотного содержания входных сигналов и групп, создаваемых из них, возможны различные конфигурации интеграторов с суммированием их входов или без такого суммирования.

Каждый интегратор должен иметь опорную частоту /частоту полюса/, которая согласуется с частотой соответствующих входных сигналов. Сигналы с низкочастотным содержимым суммируются в сумматоре 415, а выходной сигнал сумматора интегрируется в интеграторе 417 с низкой опорной частотой. Высокочастотный входной сигнал интегрируется в интеграторе 420 с высокой опорной частотой. Два полученных в результате проинтегрированных сигнала суммируются в сумматоре 425 и выходной сигнал сумматора затем подается на вход фазового модулятора 430. Фазовый модулятор 430 путем объединения с функциями интегрирования и суммирования осуществляет частотную модуляцию сигналов с низкочастотным содержимым. На выходе фазового модулятора 435 формируется частотно-модулированный сигнал, промодулированный суммой входных сигналов.

На фиг. 5 и 6 показана конфигурация схемы коммутации конденсаторов в соответствии с настоящим изобретением. Элементами схемы коммутации конденсаторов являются переключатели, которые могут быть выполнены на полевых МОП-транзисторах N- или P-типа или с использованием комбинации обоих их типов, конденсаторы и операционные усилители, хорошо известные из предшествующего уровня техники. Для многих реализаций сумматор для суммирования группы входных сигналов может быть объединен с входной частью схемы интегратора для получения единой схемы, как показано на фиг. 5.

На фиг. 5 показаны два интегратора, первый интегратор с суммирующим входом и второй интегратор с единичным /не суммирующим/ входом, как показано на фиг. 4. Сигналы с низкочастотным содержимым 503 и 515 вводятся в схему через соответствующие переключатели 506 и 518. Переключатели 506 и 518 активизируются двухфазным тактовым сигналом, поступающим от источника /не показан/. Этот источник может быть внутренним по отношению к средству, такому, как радиопередатчик. Двухфазный тактовый сигнал ⊘ является неперекрывающимся и имеет две фазы, обозначенные как ⊘1 и ⊘2. Входные сигналы 503 и 515 подаются со стробированием на входные конденсаторы 512 и 524 соответственно. При ⊘1 переключатели 509, 521 и 545 замкнуты для очистки входных конденсаторов от заряда. Выборки входных сигналов объединяются посредством интегрирующего конденсатора 530 в течение фазы тактового сигнала ⊘2, когда переключатели 506, 518 и 527 замкнуты. Отрицательная обратная связь обеспечена конденсаторами обратной связи 536 и 530. Выходной сигнал стробируется в конденсатор обратной связи 536 на фазе тактового сигнала ⊘2, когда замкнут переключатель 539. Переключатели 533 и 545 обеспечивают разряд конденсатора обратной связи 536 перед приемом следующей выборки выходного сигнала. Опорная частота интегратора определяется отношением емкости конденсатора обратной связи 536 к емкости интегрирующего конденсатора 530. Коэффициент передачи по постоянному току для каждого входного сигнала определяется отношением емкости соответствующего входного конденсатора 512 или 524 к емкости конденсатора обратной связи 536.

Переключатель 545 является переключателем с автоматическим обнулением, который позволяет компенсировать входное опорное напряжение смещения операционного усилителя 542. Путем закорачивания выхода 548 усилителя 542 с его входом в течение такта ⊘1, напряжение смещения стробируется на входные конденсаторы 512 и 524 и конденсатор обратной связи 536. В течение такта ⊘2, заполненное /накопленное/ напряжение смещения затем вычитается в усилителе 542 и таким образом соответствующее смещение компенсируется.

Второй интегратор, показанный на фиг. 5, аналогичен первому интегратору. Однако на входе второго интегратора нет суммирующего входа. Входной сигнал 551 стробируется переключателем 554 и передается на входной конденсатор 560. Этот конденсатор разряжается с помощью переключателей 557 и 581. Входной сигнал интегрируется интегрирующим конденсатором 566, проходя через переключатель 563. Выходной сигнал 584 передается обратно через конденсатор обратной связи 569, переключатель 575 и интегрирующую емкость 566. Конденсатор обратной связи 569 разряжается посредством переключателей 572 и 581. Переключатель 581 с автоматическим обнулением обеспечивает компенсацию упомянутого смещения операционного усилителя 578.

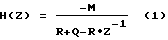

Функция Z - преобразования интегратора на конденсаторе с потерями, такого, как на фиг. 5, описывается следующим образом:

где M - входная емкость,

R - интегрирующая емкость,

Q - коммутирующая емкость обратной связи.

Входные сигналы будут представлять собой комбинацию составляющих постоянного тока и полезного сигнала, как показано ниже:

V503 = входной сигнал в 503 = V503пост + V503сигн;

V515 = входной сигнал в 515 = V515пост + V515сигн;

V551 = входной сигнал в 551 = V551пост + V551сигн,

где Vn.пост = составляющая постоянного тока во входном сигнале n;

Vnсигн = полезный сигнал во входном сигнале n

n = 503, 515, 548, 551 и 584.

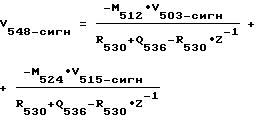

Применив уравнение /1/ к входным сигналам, получим:

и

где отношения -M512/Q536; -M524/Q536 и -M560/Q569 являются коэффициентами передачи по постоянному току входных сигналов, переданных через их соответствующие интеграторы. Так как коэффициент передачи по постоянному току интегратора с высокой опорной частотой существенно уменьшен по сравнению с коэффициентом передачи интегратора с низкой опорной частотой, то вклад составляющей выходного смещения постоянного тока интегратора с высокой опорной частотой, обусловленной входным сигналом 551, также значительно уменьшен. Именно такое уменьшение смещения позволяет отказаться от внешнего развязывающего по постоянному току конденсатора большой емкости, использовавшегося до сих пор.

Схемы по фиг. 5 и 6 могут быть реализованы в виде одной интегральной микросхемы. Размеры емкостей, соответствующих интеграторам, зависят от многих переменных. Например, для тактового сигнала ⊘, имеющего частоту 32 кГц, первый интегратор имеет полюс на частоте 1 Гц, второй интегратор имеет полюс на частоте 15 Гц, первый интегратор имеет коэффициент передачи по постоянному току 15, а второй интегратор имеет коэффициент передачи по постоянному току 1, величины конденсаторов вычисляются следующим образом. Из предшествующего уровня техники известно изготовление конденсаторов малых емкостей порядка 0,01 пФ. Для частот дискретизации, которые гораздо выше частот полюсов, эквивалентное сопротивление коммутируемой емкости приблизительно вычисляется следующим образом:

где Rэк - эквивалентное сопротивление,

FS - тактовая частота ⊘,

C - емкость коммутируемого конденсатора.

Для полюса на частоте 1 Гц отношение емкости интегрирующего конденсатора К емкости конденсатора обратной связи может быть определено из уравнения

где

R1 - емкость интегрирующего конденсатора первого интегратора;

Q1 - емкость коммутирующего конденсатора обратной связи первого интегратора,

тем самым получаем R1/Q1 = FS/2•π.

Коэффициент передачи по постоянному току интегратора определяется отношением входной емкости M, к емкости коммутирующего конденсатора обратной связи Q.

Коэффициент передачи по пост. току = -M/Q.

Для первого интегратора при Q1 = 0.01 пФ получим R1 = 50.93 пФ и M1 = 0.15 пФ, где M1 является входной емкостью первого интегратора.

Аналогичным образом, для второго интегратора, где Q2, R2 и M2 являются емкостью обратной связи, иинтегрирующей и входной емкостью соответственно, при Q2 = 0.01 пФ получаем R2 = 3.40 пФ и M2 = 0.01 пФ. Аналогично, общая суммарная емкость обоих каскадов интегратора приблизительно равна 55 пФ.

Для некоторых применений важно, чтобы коэффициенты передачи каждого интегратора мало отличались друг от друга так, чтобы в процессе интегрирования сохранялись относительные входные уровни сигналов. Путем использования множества интеграторов в одной и той же интегральной схеме с согласованием интеграторов на коммутирующих емкостях, требуемая точность согласования легко обеспечивается.

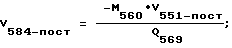

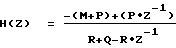

На фиг. 6 показано выполнение коммутируемой емкости для схемы сумматора. Сумматор имеет каскад с двумя входами. Выходные сигналы интеграторов 548 и 584 непосредственно подаются в конденсаторы, работающие в непрерывном режиме, 593 и 611, а также стробируются в коммутируемые конденсаторы 596 и 614 соответственно. Входные переключатели 587 и 605 стробируют выходные сигналы интеграторов в коммутируемые входные емкости, при этом переключатели 602 и 620 позволяют передавать заряд в суммирующий узел операционного усилителя 635. Переключатели 590, 599, 608 и 617 обеспечивают разряд коммутируемых входных емкостей. Выходной сигнал 638 накапливается на конденсаторе 632 и подается обратно посредством конденсаторов обратной связи 623 и 632 и переключателей 626 и 629. Функция Z-преобразования сумматора имеет вид:

где M - входная коммутирующая емкость,

P - входная непрерывная емкость,

R - интегрирующая емкость,

Q - коммутирующая емкость обратной связи.

Анализ приведенных выше уравнений показывает, что P/R = M/Q, когда полюс и нуль точно компенсируются, в результате формируется плоская частотная характеристика с коэффициентом передачи:

Коэффициент передачи = P/R = M/Q.

Другой вариант возможного выполнения настоящего изобретения, показанный на фиг. 7, иллюстрирует радиопередатчик. Низкочастотный сигнал данных 705 с частотным содержимым в диапазоне от 50 Гц до 100 Гц и вспомогательный входной сигнал 710 с частотным содержимым в диапазоне от 10 Гц до 10 кГц вводятся в сумматор-интегратор 725 с частотой полюса 1 Гц. Речевой сигнал 715 с частотным содержимым в диапазоне от 300 Гц до 3 кГц и сигнал системы ДТМЕ 720 с частотным содержимым в диапазоне от 600 Гц до 1600 Гц вводятся в сумматор/интегратор 730 с частотой полюса 15 Гц. Выходные сигналы интеграторов с полюсами на частотах 1 Гц и 15 Гц суммируются в сумматоре 735. Просуммированный выходной сигнал сумматора 735 вводится в фазовый модулятор 745. Фазовый модулятор 745 модулирует опорный сигнал 740 с использованием сумматорного выходного сигнала сумматора 735. Этот промодулированный сигнал затем подается на частотный синтезатор, содержащий фазовый детектор 750, низкочастотный фильтр 755, генератор, управляемый напряжением 760 и делитель 765. Обе группы входных сигналов также суммируются в сумматоре 775 и подаются на генератор, управляемый напряжением, для обеспечения непосредственной частотной модуляции выходного сигнала. Выходной сигнал частотного синтезатора затем поступает в передающий элемент 770, такой, как антенна.

Хотя данное изобретение было описано на примерах и проиллюстрировано чертежами, ясно, что приведенное выше описание приведено всего лишь для примера и специалистами в данной области техники могут быть внесены изменения и усовершенствования без изменения сущности изобретения. Различные группы входных сигналов могут быть обработаны с использованием различных конфигураций интеграторов с суммированным и с единичным входом. Данное изобретение целиком или частично может быть использовано в цифровых процессорах сигналов вместо схем аналоговой обработки сигналов.

Способ и устройство для объединения совокупности входных сигналов относятся к обработке сигнала, в частности к суммированию и объединению аналоговых сигналов и могут быть использованы в цифровых процессорах. Технической задачей является суммирование и объединение множества входных сигналов без использования развязывающего по постоянному току конденсатора больших размеров. Устройство для объединения совокупности входных сигналов содержит первый интегратор, имеющий первую частоту полюса, второй интегратор, имеющий вторую частоту полюса, сумматор, фазовый модулятор, соединенный с сумматором для приема объединенного проинтегрированного сигнала сумматора и выработки частотно-модулированного сигнала. Способ объединения совокупности входных сигналов основан на суммировании и интегрировании сигналов для выработки частотно-модулированного сигнала, при этом интегрируют совокупности входных сигналов, содержащих низкочастотные сигналы данных и речевые сигналы. 2 с. и 4 з.п. ф-лы, 7 ил.

| US 5057796 A, 15.10.91 | |||

| US 4640990 A, 03.02.87 | |||

| US 4511862 A, 16.04.85 | |||

| US 4546331 A, 08.10.85 | |||

| US 4870384 A, 26.09.89 | |||

| Частотно-модулированный кварцевый генератор Ю.Г.Никитенко | 1982 |

|

SU1084945A1 |

| Частотно-модулированный кварцевый генератор Ю.Г.Никитенко | 1985 |

|

SU1317643A2 |

Авторы

Даты

1999-08-20—Публикация

1994-10-17—Подача