Изобретение относится к синтезаторам частоты, а более конкретно к синтезаторам частоты с дробным значением коэффицента деления N, использующим множество накапливающих сумматоров в конфигурации с фиксаторами и последовательной рекомбинацией. Данная конфигурация накапливающих сумматоров с фиксаторами работает синхронно и позволяет системе работать на более высоких частотах, чем простая система, обладающая пульсацией, что позволяет снизить уровень паразитных сигналов.

Предшествующий уровень техники

Синтез частот с использованием системы фазовой автоматической подстройки частоты (АПЧ) является хорошо известным методом генерирования одного из многих связанных сигналов с помощью управляемого напряжения осциллятора (VCO). В отдельной системе АПЧ выходной сигнал от VCO подается на программируемый делитель частоты.

Этот программируемый делитель частоты обеспечивает деление на выбранное целое число, выдавая сигнал деленной частоты на фазовый детектор. Фазовый детектор сравнивает сигнал поделенной частоты с сигналом опорной частоты от другого осциллятора фиксированной частоты.

Любая разность фаз между сигналом деленной частоты и опорным сигналом выдается из фазового детектора через сетевой фильтр и прикладывается к VCO. Этот сигнал разности фаз заставляет выходной сигнал VCO изменять частоту таким образом, чтобы фазовая ошибка между частотой поделенного сигнала и частотой опорного сигнала была минимальной. Так как программируемый делитель частоты делит только в целое число раз, размер шага выходной частоты ограничен до значения, равного частоте опорного сигнала. При одинарной системе АПЧ необходимо достичь компромисса между противоречивыми требованиями времени синхронизации системы, размером шага, характеристиками шума и генерацией паразитных сигналов.

С целью преодоления указанных ограничений, свойственных одинарной схеме АПЧ, были разработаны программируемые делители частоты, способные осуществлять деление не на целые числа. Получены размеры шага выходной частоты, которые являются долями сигнала опорной частоты с сохранением высокой опорной частоты и широкой полосы пропускания этой цепи.

Анализ синтеза частоты с дробным значением коэффициента деления N можно найти в патенте США N 4 816 774. В решении по данному патенту применяются два накапливающихся сумматора для моделирования характеристик синтеза с дробным значением коэффициента деления частоты. Такое моделирование подразумевает переключение между различными целями делителей без сопутствующих паразитных сигналов, генерируемых в результате такого переключения.

Такой метод использования двух накапливающих сумматоров позволяет снизить нежелательные паразитные сигналы за счет их взаимного уничтожения и устранения сетевого фильтра.

Следовательно, частота опорного сигнала для синтезатора с дробным значением коэффициента деления частоты N определяется размером шага выходной частоты VCO, умноженным на знаменатель делителя этого программируемого делителя частоты.

Синтез частоты с дробным значением N позволяет использовать опорную частоту, которая значительно больше, чем реальное расстояние между каналами, и позволяет использовать в конструкциях более широкие полосы за счет уменьшения низкочастотных паразитных сигналов. Более широкие полосы позволяют иметь малое время синхронизации и возможность приложения широкополосной модуляции к входу опорного сигнала или к схеме дробного деления.

Однако указанная система не идеальна и генерирует некоторые паразитные сигналы на частоте, соответствующей расстоянию между каналами. Частота желаемого выходного сигнала выше, чем в системе с недробным коэффициентом деления, но еще не недостаточна для некоторых высококачественных систем.

С целью минимизации влияния паразитного выхода была разработана система синтеза с дробным значением N, состоящая из множества накапливающих сумматоров. Также системы переносят указанные паразитные сигналы на частоты, на которых фильтрация является недорогой и простой в реализации. За счет использования систем, имеющих более двух накапливающих сумматоров, это преимущество может быть в значительной степени увеличено.

Пример предложен в патенте US N 5070310. Патент US N 5070310 предлагает радиопередатчик, применяющий синтезатор с дробным значением коэффициента деления N, который принимает цифровой номер из множества бит от контроллера для выбора частоты рабочего сигнала. Синтезатор с дробным значением коэффициента деления N делит частоту рабочего сигнала с помощью делителя системы АПЧ. Делитель системы АПЧ имеет изменяемый делитель, управляемый управляющим входным сигналом для создания сигнала обратной связи с целью сравнения с опорным сигналом.

Некоторые из указанных систем с множеством накапливающих сумматоров требуют, чтобы накапливающие сумматоры осуществляли "пульсацию" данных.

В частности, при каждом импульсе синхронизации эти данные должны действовать на всю цифровую сеть. В результате, это приводит к относительно низкому верхнему частотному пределу работы для многосумматорных систем, определяемому задержками распространения в цифровых схемах, используемых для построения системы. Наконец, некоторые известные многосумматорные системы все еще сохраняют терм остаточных шумов, который может вызывать сигналы паразитного шума. Эти сигналы паразитного шума должны быть уменьшены для правильной работы многих систем.

Раскрытие изобретения

Настоящее изобретение относится к синтезатору изменяемой частоты, содержащему, по крайней мере, две сети накапливающих сумматоров в сочетании с фиксаторами, которые рекомбинируют последовательно. Эти сети накапливающих сумматоров в сочетании с фиксаторами принимают цифровое число, которое используется для формирования изменяемого делителя.

Частота колебаний осциллятора с изменяемой частотой управляется путем деления частоты выходного сигнала на переменный делитель в сети делителя частоты, формирующей промежуточный сигнал. Этот промежуточный сигнал сравнивается с опорным сигналом, генерирующим первый сигнал ошибки, индицирующий разность фаз между этими двумя сигналами. Этот первый сигнал ошибки подается на вход осциллятора переменной частоты как управляющий сигнал осциллятора переменной частоты.

Первая сеть накапливающих сумматоров генерирует проходящий через фиксатор выходной сигнал и выходной сигнал первого переноса, представляющий интеграл этого цифрового числа.

Вторая сеть накопленных сумматоров генерирует второй, проходящий через фиксаторы выходной сигнал и выходной сигнал второго переноса, представляющий интеграл от первого, прошедшего через фиксатор выходного сигнала.

Третья сеть накапливающих сумматоров в сочетании с фиксаторами генерирует третий, прошедший через фиксаторы выходной сигнал и выходной сигнал третьего переноса, который представляет интеграл от второго, прошедшего через фиксатор выходного сигнала.

Указанные три выходные сигнала переноса далее объединяются для формирования сигнала переменного двигателя. Третий выходной сигнал переноса дифференцируется и объединяется с выходным сигналом второго переноса, формируя пятый выходной сигнал. Этот пятый выходной сигнал далее дифференцируется и объединяется с выходным сигналом первого переноса, формируя сигнал переменного делителя. Сигнал переменного делителя подается на вход сети делителя частоты.

Краткое описание чертежей

В дальнейшем изобретение поясняется описанием примеров его выполнения со ссылками на чертежи, на которых:

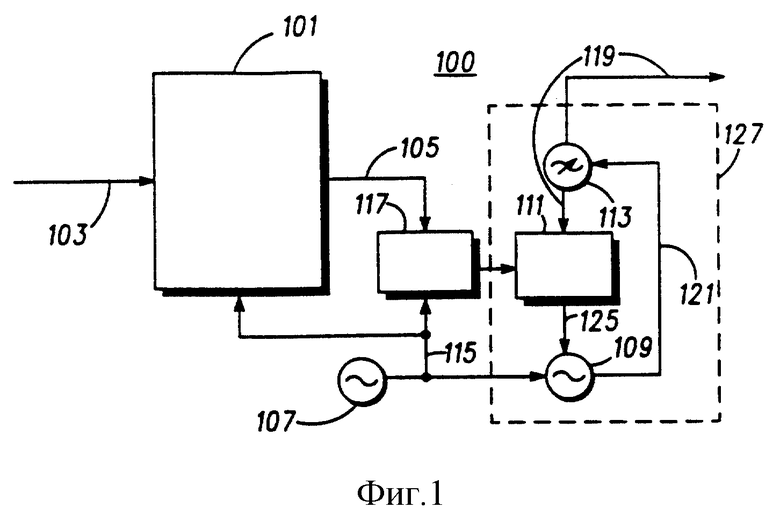

Фиг. 1 изображает блок-схему синтезатора переменной частоты.

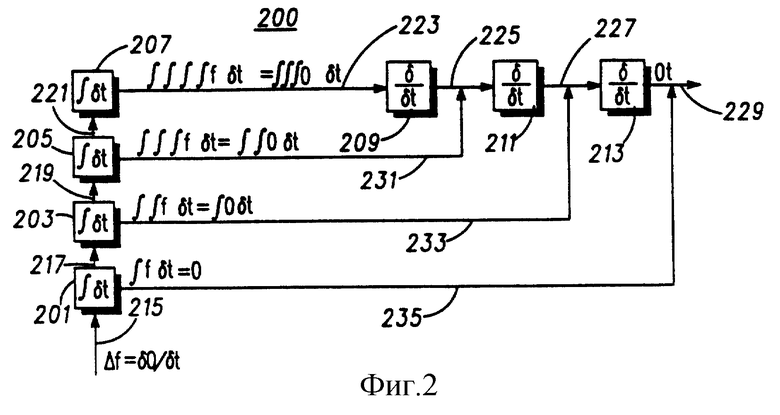

Фиг. 2 - общую блок-схему сети накапливающих сумматоров (с последовательной рекомбинацией) синтезатора с дробным значением N в соответствии с настоящим изобретением.

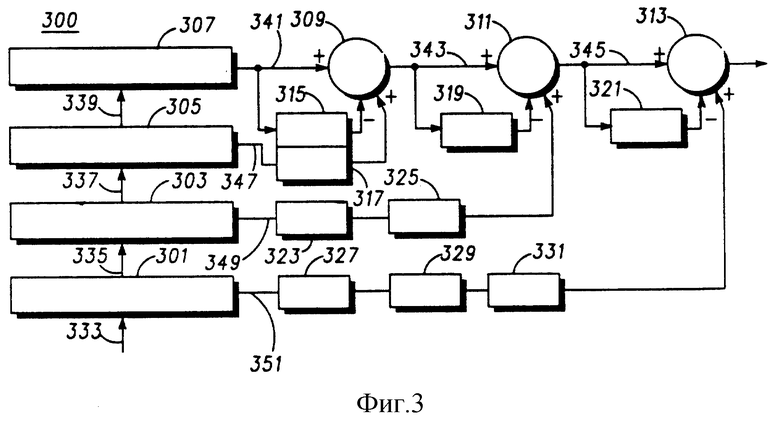

Фиг. 3 - сеть накапливающих сумматоров в сочетании с фиксаторами в соответствии с настоящим изобретением.

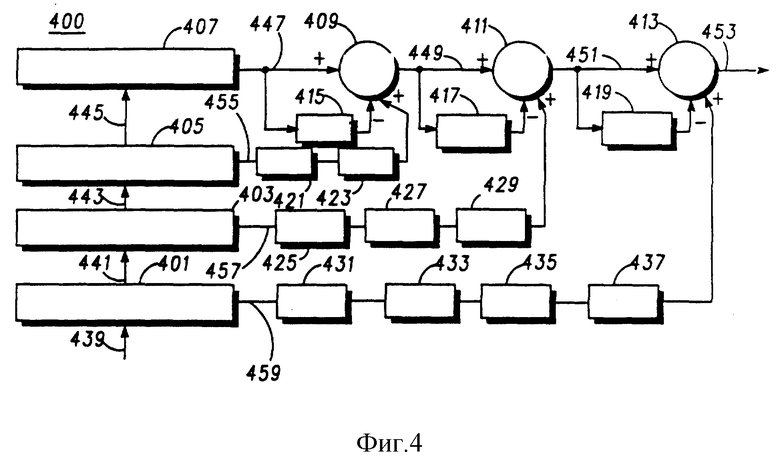

Фиг. 4 - сеть накапливающих сумматоров в сочетании с фиксаторами с двойной выдержкой в соответствии с настоящим изобретением.

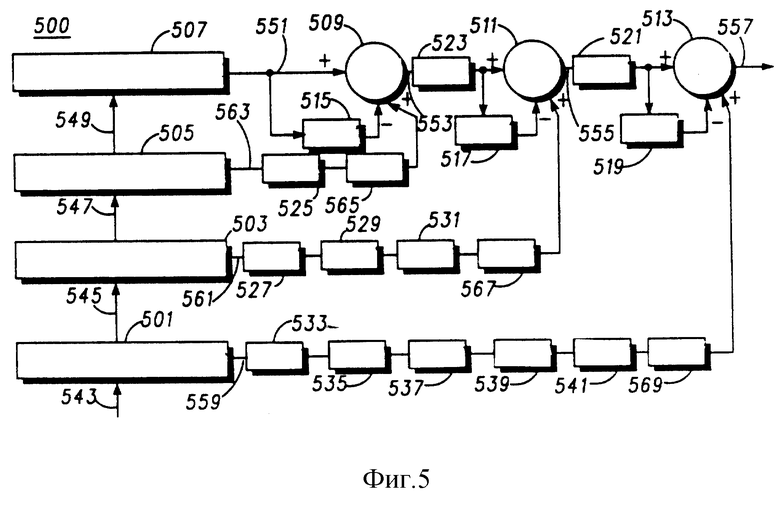

Фиг. 5 - сеть с фиксаторами с двойной задержкой в соответствии с настоящим изобретением.

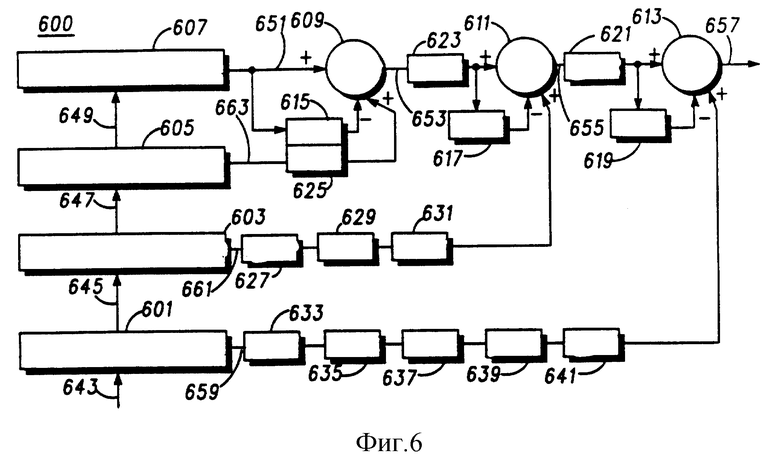

Фиг. 6 - сеть накапливающих сумматоров в сочетании с фиксаторами с одинарной задержкой в соответствии с настоящим изобретением.

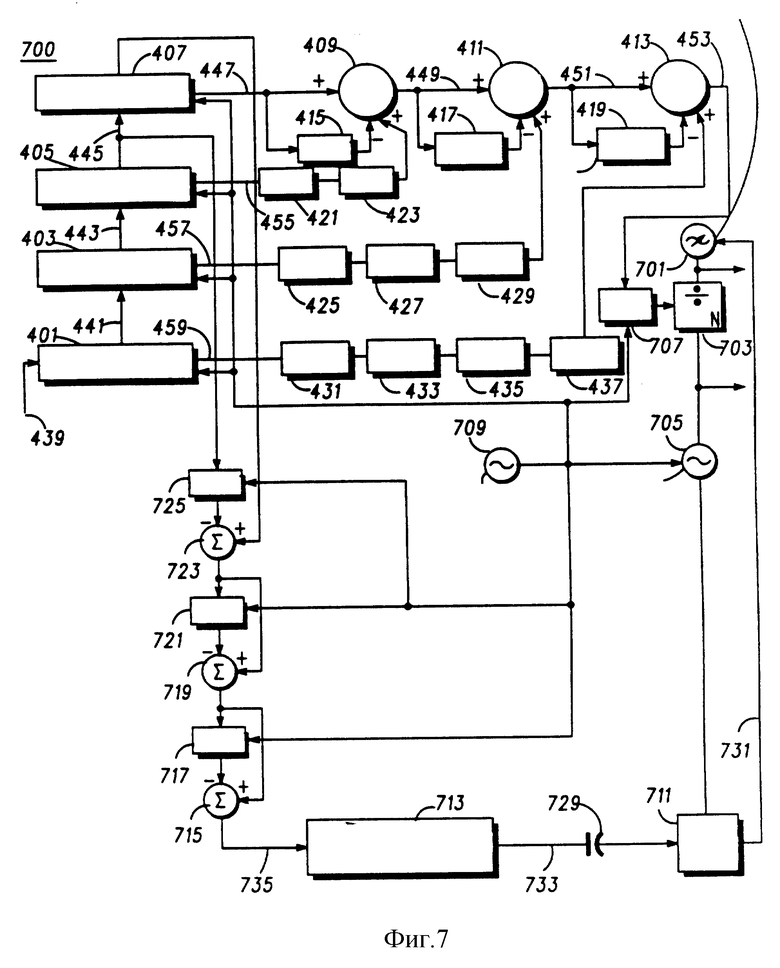

Фиг. 7 - сеть накапливающих сумматоров в сочетании с фиксаторами с двойной задержкой, с коррекцией остаточной ошибки в соответствии с настоящим изобретением.

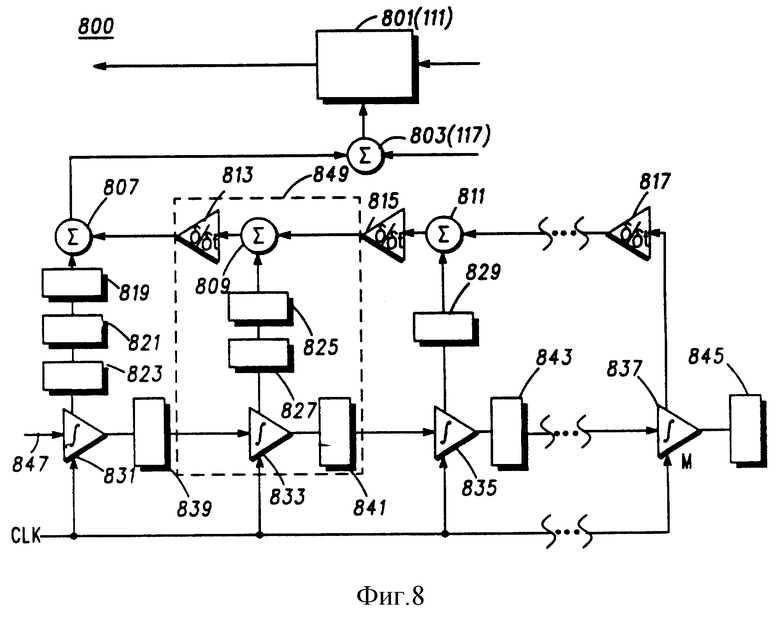

Фиг. 8 - сеть накапливающих аккумуляторов в сочетании с фиксаторами с одинарной задержкой в альтернативной форме в соответствии с настоящим изобретением.

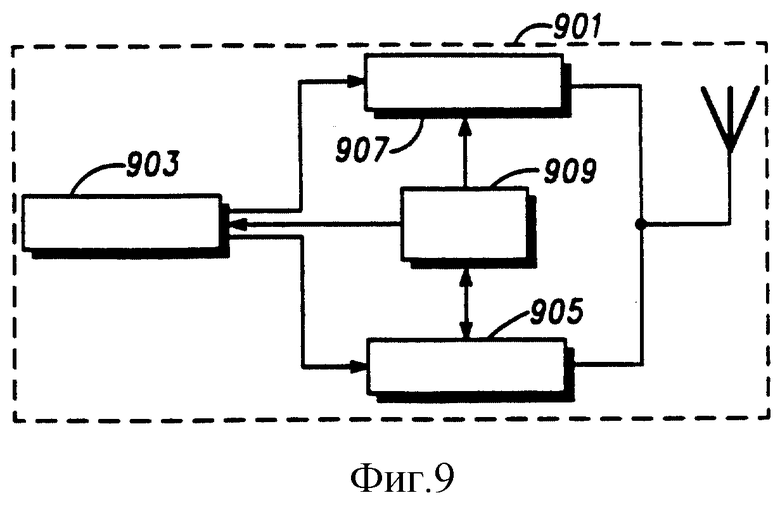

Фиг. 9 - блок-схему радиоприемопередатчика, в котором может применяться настоящее изобретение.

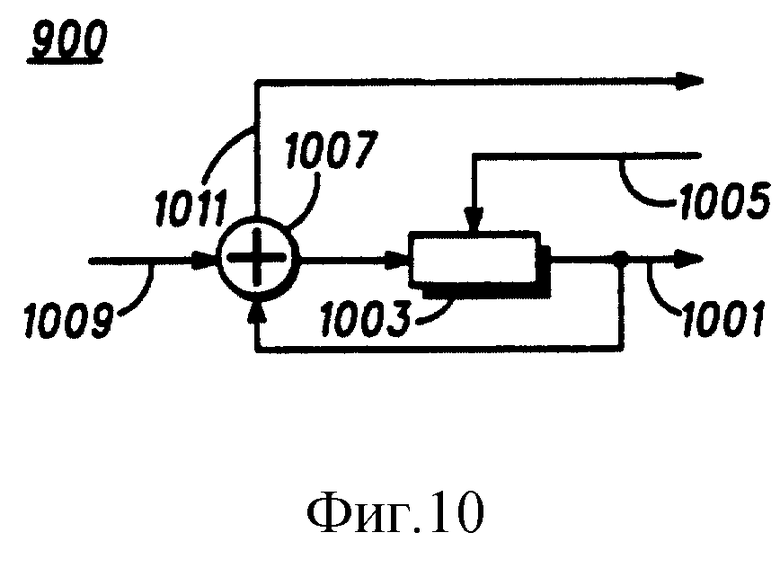

Фиг. 10 - схему типового накапливающего сумматора в сочетании с фиксатором в соответствии с настоящим изобретением.

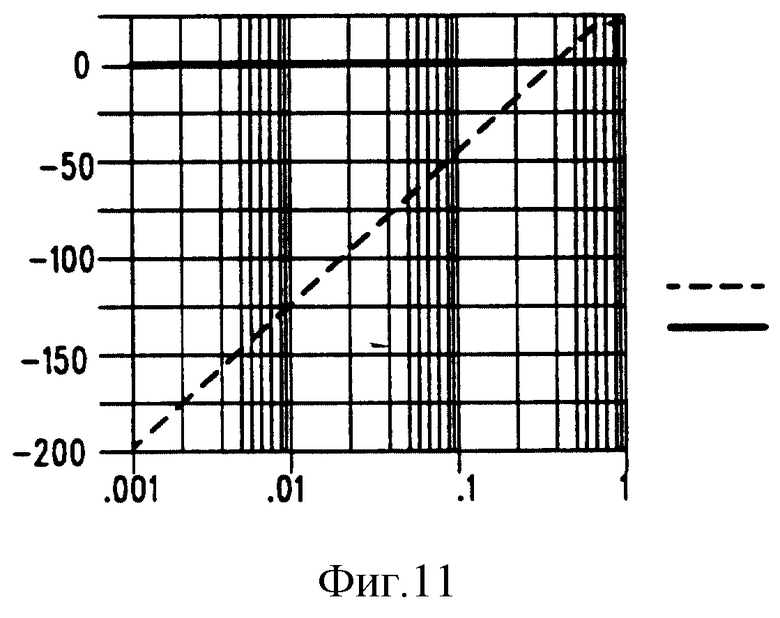

Фиг. 11 - график кривых, иллюстрирующий зависимость ослабления от частоты в каждом терме передаточной функции системы в соответствии с настоящим изобретением.

Лучший вариант осуществления изобретения

Предпочтительный вариант выполнения относится к использованию синтезатора в радиоприемопередатчике. Указанный синтезатор относится к типу синтезаторов с дробным значением N. В синтезаторе используются множественные накапливающие сумматоры в сочетании с фиксаторами в сети сумматоров для получения множественных интегралов от входного сигнала. Выходы накапливающих сумматоров объединены последовательно для формирования выходного сигнала данных, который используется как переменный делитель в синтезаторе.

Базовая блок-схема радиотелефона 901, содержащая радиоприемопередатчик, показана на фиг. 9. Предпочтительно, чтобы такой радиотелефон был цифровым радиотелефоном, используемым в радиотелефонной системе. Выходной сигнал синтезатора 903 используется приемником 905 и передатчиком 907 для создания локального осциллятора и передачи сигнала соответственно.

Функции управления приемопередатчиком 900, такие как передача сигнала рабочей частоты, осуществляются управляющей логикой схемой 909, которая подает его на вход первого накапливающего сумматора с дробным значением N, содержащегося в синтезаторе 903.

Фиг. 1 есть родовая блок-схема синтезатора изменяемой частоты с дробным значением N. Осциллятор с изменяемой частотой или VCO 113 обеспечивает сигнал 119 с желаемой входной частотой и подает его на вход схемы 111 делителя изменяемой цифровой частоты. Выходной сигнал 125 схемы делителя изменяемой цифровой частоты подается на вход компаратора 109 фаз.

Второй вход компаратора 109 фаз является сигналом 115 опорного осциллятора. Выходной сигнал 121 компаратора фаз подается на управляющий вход VCO 113 так, что вход VCO 113 будет регулировать сигнал 119 своей выходной частоты, деленной на цифровой коэффициент деления N схемы 111 делителя частоты, для выравнивания данной частоты с частотой опорного осциллятора 107.

В предварительном варианте выполнения коэффициент деления N схемы 111 деления частоты изменяется в периодической последовательности таким образом, что сигнал 119 выходной частоты VCO 113 может регулироваться с шагами частоты, равными доле частоты опорного генератора 107. Эта периодическая последовательность генерируется сетью 101 множества накапливающих сумматоров и управляется сигналами 103 входных данных.

В предпочтительном варианте выполнения конфигурации накапливающих сумматоров в сочетании с фиксаторами, как показано на фиг. 10, применяется во всех сетях накапливающих сумматоров. Другая, в равной степени достаточная конфигурация накапливающих сумматоров может быть применена любым специалистом в данной области техники.

Здесь, сигнал 1001 выходных данных каждого накапливающего сумматора представляет собой триггерный выход обычной триггерной схемы 1003. Каскадное соединение таких накапливающих сумматоров будет давать задержку одного сумматора при каждом цикле синхронизации синхронизирующего сигнала 1005.

Такая структура позволяет задерживать выходную последовательность переносов в каждом накапливающем сумматоре от сумматора 1007 на один цикл синхронизации по сравнению с выходной последовательностью накапливающего сумматора следующего более низкого порядка.

В других вариантах выполнения могут использоваться накапливающие сумматоры в сочетании с фиксаторами, которые фиксируют выходной сигнал 1011 переноса и выходной сигнал 1001 данных.

Фиг. 2 является иллюстрацией типа сети накапливающих сумматоров, примененных в настоящей системе. В этой сети используется множество накапливающих сумматоров с фиксаторами и последовательная рекомбинация, что обеспечивает простоту конструкции и возможность непосредственно добавлять смещения частоты постоянного тока к выходу 229 (D0) данных.

Выходной сигнал смещения частоты или вход данных 215 (D1) является входом от схемы селекции частоты, содержащейся в логике 909 управления на фиг. 9, и прикладывается к первому накапливающему сумматору 201 (фиг. 2). Указанный первый накапливающий сумматор генерирует входные сигналы 217, 235, которые представляют интеграл от сигнала 215 входных данных.

Выходной сигнал 217 данных подается на вход второго накапливающего сумматора 203. Выходной сигнал 235 переноса непосредственно суммируется с сигналом дифференциатора 213, давая в результате выходной сигнал 229 данных. Данный выходной сигнал 235 переноса позволяет непосредственно передавать смещения фаз постоянного тока к выходному сигналу 229 данных.

Выходной сигнал данных 219 второго накапливающего сумматора 203 подается на вход третьего накапливающего сумматора 205, подобным же образом выходной сигнал 221 данного третьего накапливающего сумматора 205 подается на вход четвертого накапливающего сумматора 207.

Выходной сигнал 223 переноса четвертого накапливающего сумматора 207 дифференцируется и объединяется с выходным сигналом 231 переноса от третьего накапливающего сумматора 205, создавая в результате сигнал 225. Сигнал 225 подается на вход второго дифференциатора 211, этот результирующий сигнал объединяется с выходным сигналом 233 второго переноса от второго накапливающего сумматора 203. Результирующий сигнал 227 подается на вход третьего дифференциатора 213.

Схема, представленная на фиг. 2, используется как родовое описание синтеза частоты с дробным значением N и с последовательной рекомбинацией. Формы выполнения этого общего метода проиллюстрированы на приведенных ниже чертежах на фиг. 3, 4, 5, 6, 7 и 8. Фиг. 2, даваемая без фиксированных выходных сигналов или цифровых задержек, имеет ограниченную практическую ценность.

Фиг. 3 является реализацией синтеза частоты с дробным значением N и с последовательной рекомбинацией, проиллюстрированного на фиг. 2. Эта реализация содержит задержки сигналов и накапливающие сумматоры в сочетании с фиксаторами. Важной особенностью этого изобретения является то, что данные представляются от одного накапливающего сумматора к следующему накапливающему сумматору только в течение одного цикла синхронизации.

Эти данные никогда не попадают от первого накапливающего сумматора к третьему накапливающему сумматора в течение одного цикла синхронизации, благодаря этому исключая проблему "пульсаций", проходящих через все накапливающие сумматоры в течение одного импульса синхронизации. Эти накапливающие сумматоры, включенные в сочетании с фиксаторами, обеспечивают синхронизацию сети 101.

Эффект "пульсации" представляет собой накопление задержек, свойственных схемам, используемым для осуществления конкретной конструкции. Пульсирующие накапливающие сумматоры ограничивают возможное число накапливающих сумматоров в заданной сети накапливающих сумматоров, создавая фиксированную частоту синхронизации и цифровые задержки схем.

В синхронизированной системе каждая функция имеет фиксированную задержку в один период синхронизации. Эта синхронизированная система фиксирует данные каждой функции, поэтому данные задерживаются на одну функцию во время каждого периода синхронизации. Таким образом, система из многих накапливающих сумматоров может функционировать так же быстро, как система, состоящая только из одного накапливающего сумматора.

В сети, проиллюстрированной на фиг. 3, общая задержка системы будет равна трем циклам синхронизации плюс кумулятивная задержка трех сумматоров 309, 311, 313 вследствие внутренних цифровых задержек. Указанная кумулятивная задержка трех сумматоров 309, 311, 313 отсутствует в вариантах выполнения по фиг. 5 по причине суммирования фиксированных задержек между этими сумматорами.

В предпочтительном варианте выполнения синхронизирующий сигнал генерируется из выходного сигнала 125 сети 111 делителя частоты, и наоборот, данный синхронизирующий сигнал может генерироваться из выходного сигнала опорного генератора 107.

В предпочтительном варианте выполнения используются сумматоры с фиксаторами, поскольку система является цифровой. Однако согласно настоящему изобретению может быть разработана аналоговая эквивалентная система, содержащая аналоговые интеграторы.

Первый накапливающий сумматор 301 выполняет цифровое интегрирование входного сигнала 333 данных. Выходной сигнал 335 фиксируется при первом появлении сигнала синхронизации. Второй накапливающий сумматор 303 выполняет цифровое интегрирование содержимого фиксируемого накапливающего сумматора 301, фактически создавая двойной интеграл входных данных 333.

При втором появлении указанного синхросигнала выход второго накапливающего сумматора 303 фиксируется. Третий накапливающий сумматор 305 выполняет цифровое интегрирование содержимого указанного фиксированного выхода второго накапливающего сумматора 303, фактически создавая тройной интеграл входа данных 333.

Четвертый фиксированный накапливающий сумматор 307 выполняет цифровое интегрирование содержимого выхода фиксированного третьего накапливающего сумматора 305, фактически создавая четвертый интеграл этого входа данных 333.

Выходной сигнал 351 переноса первого накапливающего сумматора 301 представляет тот факт, что выходная частота (PO) VCO 113 имеет приобретенные 360o фазовой ошибки относительно частоты выходного сигнала опорного осциллятора 107. С целью коррекции этого выходной сигнал 229 данных увеличивается на единицу в течение следующего интервала синхронизации, а внутреннее содержимое первого накапливающего сумматора 303 уменьшается на его собственную емкость.

Это действие эффективно устраняет один цикл из частоты входного сигнала 125 фазового компаратора, в результате осуществляя коррекцию фазы в 360 градусов в выходном сигнале (PO) 119 от VCO.

Производные 209, 211 и 213 на фиг. 2 представлены на фиг. 3 комбинацией из цифрового элемента задержки и сумматора, например 315 и 309. Производная реализуется цифровым способом за счет удержания предыдущей выборки сигнала и вычитания ее из настоящего значения этого сигнала. Сумматор 309 функционирует также, чтобы объединять выход переноса от третьего фиксированного накапливающего сумматора 347 с выходом производной от четвертого фиксированного накапливающего сумматора. Результирующий сигнал 343 передается через два последующих средства дифференцирования.

Указанные цифровые элементы задержки позволяют синхронизировать рекомбинантные выходные сигналы переноса с надлежащим циклом синхронизации. Выходной сигнал 351 переноса задерживается на три последовательных цикла задержки, прежде чем достигнуть сумматора 313. Выходной сигнал переноса от второго фиксированного накапливающего сумматора 349 задерживается на два цикла синхронизации, прежде чем достичь сумматора 311.

Выключая задержку на один цикл синхронизации, вносимую первым фиксированным накапливающим сумматором 301, данный выходной сигнал переноса достигнет сумматора 311 по третьему циклу синхронизации. Выход переноса от третьего фиксированного накапливающего сумматора 347 задерживается на один цикл синхронизации с момента его создания, прежде чем он будет просуммирован в сумматоре 309. Эта одна задержка имеет место после двух задержек от первого и второго фиксированных накапливающих сумматоров, тем самым достигая этого сумматора по третьему циклу синхронизации.

Поэтому сигнал изменяемого делителя 229 имеет три цикла задержки плюс влияние вследствие пульсации от выхода фиксированного накапливающего сумматора 307 и трех сумматоров 309, 311, 313. Эта синхронизированная система позволяет работать с намного более высокой скоростью синхронизации, с последующим намного более быстрым изменением периодической последовательности, использующей входной сигнал 333 данных.

Последовательная рекомбинация выходных сигналов этих накапливающих сумматоров снижает число необходимых дифференциаторов в сети накапливающих сумматоров.

Кроме задержек, которые показаны на фиг. 4, к системе могут быть добавлены дополнительные фиксированные задержки без каких-либо связанных проблем, однако эти дополнительные задержки не дают каких-либо эффективных преимуществ этой системе накапливающих сумматоров.

На фиг. 4 представлена блок-схема синтеза частот с дробным значением N с фиксированными накапливающими сумматорами и с последовательной рекомбинацией. Данная форма выполнения сети накапливающих сумматоров синтезатора подобна той, что представлена на фиг. 3, за исключением добавленных задержек 423, 429, 437, которые введены в цепь выходных сигналов 455, 457, 459 переноса первых трех фиксированных накапливающих сумматоров.

Эти элементы дополнительной задержки добавлены к накапливающим сумматорам более низкого порядка с целью получения всепропускающей характеристики для входных данных и с целью получения терма коррекции остаточного шума. Этот терм остаточного шума может быть легко реконструирован в цифровой форме для преобразования цифра (D) - аналог (A) и приложения к сетевому фильтру. Один пример схемы коррекции остаточного шума приведен на фиг. 7.

На фиг. 7 приведена блок-схема четырехсумматорной системы, такой как показана на фиг. 4, в которой информация, накопленная в фиксированном накапливающем сумматоре 407 высшего порядка и втором по величине порядка сумматоре 405, используется для вычитания терма остаточного шума в сетевом фильтре 711.

Это внутреннее содержимое фиксированного накапливающего сумматора 405 один раз задерживается на элементе 725 задержки и затем вычитается из внутреннего содержимого фиксированного накапливающего сумматора 407 высшего порядка в общепринятой функции 723 сложения. В результате получают терм, эквивалентный Z-1Q4 на выходе сумматора 723. Где Q4 есть терм шума квантования. Элементы 721 задержки и 719 сумматора формируют цепь цифровой производной. Выход сумматора 719 будет равен - Z-1(1 - Z-1)Q4. Элемент задержки 717 и сумматор 715 формируют цепь второй цифровой производной.

На выходе сумматора 715 будет выражение - Z-1(1 - Z-1)2Q4. Известный цифроаналоговый преобразователь 713 затем преобразовывает этот выходной сигнал 735 в аналоговую форму и определяет масштаб амплитуды.

Аналоговый выходной сигнал 733 через конденсатор 729 подается на вход сетевого фильтра. Конденсатор 729 используется как цепь для взятия аналоговой производной для преобразования выходного напряжения преобразователя 713 цифра-аналог в ток, удобный для приложения к сетевому фильтру 711, для которого привод от фазового компаратора является источником тока. (Ток через конденсатор является производной по времени от напряжения).

Терм 733 коррекции имеет дополнительную задержку по сравнению с выходным сигналом 453 данных. Эта задержка компенсируется добавлением задержки 707 к пути выхода данных делителя 703 переменной частоты. Следовательно, эта последовательность данных делителя 703 переменной частоты есть:

DO = Z-5D1 + Z-1(1 - Z-1)4Q4,

где

DO есть сигнал Data Out;

DI есть сигнал Data In;

Z-x представляет задержки периода x синхронизации в области Z-преобразования.

Так как фазовый детектор 705 сравнивает фазу, а не частоту, этот сигнал фактически интегрируется при прохождении через фазовый детектор 705. Следовательно, данный терм фаз выхода фазового детектора может быть представлен в области преобразования, как:

Фсогг = Kф{DIZ-5 / (1 - Z-1) + Q4Z-1(1 - Z-1)3}

где K0 есть усиление преобразования фазового конвертера.

Терм коррекции фазы, генерируемый преобразователем 713 цифра-аналог и конденсатором 729, может быть представлен в области Z преобразования, как:

Фсогг = A D/A CQ4Z-1(1-Z-1)3

где AD/A есть усиление преобразователя цифра (D)-аналог (A), а C есть емкость конденсатор 729.

Если значение конденсатора 729 выбрано равным усилению фазового детектора, деленному на усиление преобразования D/A, достигается взаимное уничтожение любых термов остаточного шума. Дополнительные элементы 423, 429, 437 прибавлены к выходным сигналам переноса первых трех накапливающих сумматоров 401, 403, 405 для того, чтобы терм последовательности шума выходных данных зависел только от четвертого накапливающего сумматора 407.

Это позволяет легко преобразовать последовательность шума для использования в преобразователе цифра-аналог, который обеспечивает коррекцию ошибки на входе осевого фильтра. Без этих элементов задержки терм выходного шума включал бы в себя множители от всех накапливающих сумматоров. И было бы трудно получить кривую коррекции для такого типа выхода.

Конденсатор 729 может быть заменен другой формой производной. Например, дополнительной цифровой задержкой и сумматором, помещенными перед указанным преобразователем цифра/аналог, аналогичными использованными на выходе последовательной рекомбинации, а именно цифровой задержкой 717 и сумматором 715. Для взаимного уничтожения усилений усиление преобразователя 713 цифра/аналог должно быть равно усилению фазового детектора 105.

Фиг. 5 является вариантом выполнения сети накапливающих сумматоров коррекции и синтеза, проиллюстрированной на фиг. 4. Здесь добавлены дополнительные задержки 523 и 521 на выходах сумматоров 509, 511 соответственно. Назначением этих дополнительных задержек является устранение эффекта "пульсации", вызываемой цифровыми задержками внутри цепочки этих сумматоров.

Как отмечалось выше, выходной сигнал четвертого фиксированного накапливающего сумматора 507 подается на вход сумматора 509 без указанных цифровых задержек 523 и 521 сигнал 557 изменяемого делителя имел бы эффект пульсации. Добавлением этих задержек устраняется эффект пульсации. В течение пятого цикла синхронизации данные будут переходить от сумматора 509 к сумматору 511. В течение шестого цикла синхронизации эти данные будут переходить из сумматора 511 в сумматор 513. Тем самым, только одна цифровая задержка будет иметь место в течение каждого цикла синхронизации. Эта модификация обеспечивает более быстрый цикл синхронизации.

На фиг. 6 представлена форма выполнения, содержащая дополнительные задержки между сумматорами, но только минимальные задержки на выходах первых трех фиксированных накапливающих сумматоров. Вариант выполнения, проиллюстрированный на фиг. 6 аналогичен варианту по фиг. 3, с добавлением синхронной последовательной рекомбинации.

В предпочтительном варианте выполнения информации модуляции прикладывается к многосумматорной цифровой сети 400 накапливающих сумматоров синтеза частоты с дробным значением N. Эта информация модуляции составляет 16 младших разрядов 24-разрядного числа, поданного на вход данных 439. Так как приемопередатчик, в котором применяется настоящее изобретение, может быть эффективно использован в цифровой радиотелефонной системе CSM Pan European Digital Radiotelephone Syctem, быстрые изменения частоты модуляции и низкоуровневые сигналы и шумы реализуются с помощью синтезатора частоты с дробным значением N.

Для модуляции указанный синтезатор с дробным значением N использует справочную таблицу, чтобы с ее помощью преобразовать поток данных, подлежащих передаче, в смешения частоты для этого синтезатора с дробным значением N. Цепь деления данного синтезатора регулируется в соответствии с входным потоком данных для отслеживаний мгновенных смещений частоты, которые требуются для моделированного сигнала CMSK. Данная операция может проводиться на частоте смещения или на основной частоте.

Синтезатор с дробным значением N и с использованием накапливающих сумматоров с фиксацией работает с большими накапливающими сумматорами для исключения паразитных сигналов, обеспечения коррекции преобразованных цифра/аналог, снижения уровня дискретных паразитных сигналов и обеспечения прямой цифровой модуляции в цепи PLL.

В системе CSM скорость данных составляет 270,8333 кбит с произведением BT, равным 0,3. Где T - период бита, равный 1/270,8333 кГц, а B - базовая ширина полосы Гауссовского фильтра, используемого для формирования данных базовой полосы. В результате получают базовую ширину полосы 81 кГц, которая должна быть пропущена с малыми искажениями через цепь PLL как частота модуляции.

Действительные компоненты смещения частоты сигнала CMSK изменяются в диапазоне значений от 10 Гц до приблизительно 70 кГц. Этот диапазон определяет разрядность накапливающих сумматоров, т.к. оказывается необходимым синтезировать шаги с меньшей шириной, чем 10 Гц в предпочтительном варианте выполнения системы CSM. Для опорной частоты в 26 МГц требуется накапливающий сумматор с шириной, по крайней мере, в 22 бита; в данном случае были выбраны 24 бита для простоты использования коммерчески доступных составных частей системы.

Очевидно, что желаемые мгновенные смещения частоты в том, что касается модуляции, должны быть гораздо ниже, чем частота отсечки данного сетевого фильтра. Следовательно, цепь синтезатора частоты не ослабляет частоты паразитных сигналов, соответствующих фундаментальным передаваемым частотам, являющимся результатом модуляции.

Однако при использовании многосумматорной системы эта проблема решается.

Общая передаточная функция системы ранее была определена, как следующая:

DO = Z-5D1 + Z-1(1 - Z-1)4Q4

Это выражение может быть преобразовано обратно в область частот путем замены eiπv = Z. В результате получаем следующее выражение для DO. Здесь использовано выражение амплитуды терм за термом.

D0 = D1+(2-2cosπv)2Q4

В предыдущем выражении V есть частота, нормализованная с частотой свертки. Эта частота свертки равна половине скорости, с которой работает синхронизация накапливающего сумматора.

Кривая зависимость ослабления от частоты проиллюстрирована на фиг. 11 и показывает каждый терм данного выражения. DI проходит без искажений относительно DO, и каждый из термов (Q) шумов квантования пропущен через фильтр высоких частот.

Является возможным и предпочтительным повышать степень дробности так, чтобы все паразитные выходы сместились к очень низким частотам. Объединенный эффект от использования многих накапливающих сумматоров при высокой скорости синхронизации дает в результате большое ослабление шумов квантования процесса дробления. Так, большой знаменатель эффективно снижает частоту паразитных сигналов, так что они оказываются значительно ниже, чем трехдецибелловый уровень верхней частоты полосового фильтра, сформированного многосумматорной структурой.

Использование многих накапливающих сумматоров повышает наклон кривой фильтрующего действия полосового фильтра, повышая скорость работы, передвигают верхнюю границу частоты фильтра вверх по шкале частот.

В целом, сеть 101 накапливающих сумматоров генерирует изменяющийся во времени коэффициент деления N. При заданном N-ом порядке системы с дробным значением N эти накапливающие сумматоры могут использоваться с фиксированием сигнала, что приводит к синхронной системе, в которой пульсации данных не проходят больше, чем через один накапливающий сумматор за один цикл синхронизации.

В системе с одной задержкой выход первого или накапливающего сумматора самого нижнего уровня к делителю переменной цепи задерживается на N - 1 единиц синхронизации, выход накапливающего сумматора следующего нижнего уровня или второго накапливающего сумматора задерживается на N - 2 единиц и так далее до тех пор, пока следующий последней накапливающий сумматор не будет задержан на одну единицу синхронизации, а самый последний или накапливающий сумматор самого высшего уровня не будет задерживаться вообще.

В системе с двумя задержками одна единица дополнительной задержки прибавляется к выходу всех накапливающих сумматоров за исключением последнего накапливающего сумматора или накапливающего сумматора самого высшего уровня.

Из-за синхронной природы данной системы она способна работать с более высокими частотами и благодаря этому позволяет иметь более широкую полосу PLL. Это обеспечивает скорейшие времена синхронизации и широкополосную цифровую модуляцию такого дробного делителя с одновременным сохранением превосходных и предсказуемых характеристик паразитных сигналов.

Цифровое представление оставшейся ошибки получается в форме, удобной для использования в схеме цифрового аналогового преобразования. Аналоговый выход этого преобразования прикладывается к выходу фазового детектора для взаимного уничтожения любых остаточных шумов.

Последовательная рекомбинация в схеме 101 накапливающих сумматоров с фиксированием сигнала обеспечивает возможность непосредственного прикладывать фазовые коррекции по постоянному току к выходному сигналу данных. Кроме этого, такая последовательная рекомбинация снижает число компонентов, необходимых для выполнения рекомбинации, по сравнению с системами треугольника Паскаля и ему подобными.

Фиг. 8 иллюстрирует реализацию сети накапливающих сумматоров с дробным значением N, как проиллюстрировано на фиг. 3. Такая схема расположения сети на иллюстрации использована для упрощения описания. Например, сеть 849 накапливающих сумматоров содержит накапливающий сумматор 833, фиксатор 841, цифровые задержки 825, 827, устройство для комбинирования сигналов 809 и дифференциатор 813. Все это может быть приведено в блок-схеме на фиг. 3.

Дополнительные сети накапливающих сумматоров могут быть добавлены в дополнение к сети 849 для создания сети накапливающих сумматоров N-го порядка. При количестве задержек в системе с минимальным числом задержек между первым накапливающим сумматором 831 и сумматором 807, равным N - 1, и первой сети накапливающих сумматоров, имеющей N - 1, второй сети накапливающих сумматоров, имеющей N - 2, и третьей сети, имеющей N - 3, и так далее до тех пор, пока не останется ни одной задержки, как проиллюстрировано на фиг. 8.

В системе с двойной задержкой сеть накапливающих сумматоров будет иметь одну дополнительную задержку за исключением последней сети или сети наивысшего порядка.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТЫ С ДЕЛЕНИЕМ НА ДРОБНОЕ ЧИСЛО И КОРРЕКЦИЕЙ ОСТАТОЧНОЙ ПОГРЕШНОСТИ И СПОСОБ СИНТЕЗА ЧАСТОТЫ | 1994 |

|

RU2134930C1 |

| СИНТЕЗАТОР ЧАСТОТЫ ДЛЯ СОЗДАНИЯ СИНТЕЗИРОВАННОЙ ВЫХОДНОЙ ЧАСТОТЫ | 1989 |

|

RU2085031C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ СИНТЕЗАТОРОМ ЧАСТОТЫ С СИСТЕМОЙ ФАЗОВОЙ АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ В ЗАВИСИМОСТИ ОТ РАССТАНОВКИ РАДИОЧАСТОТНЫХ КАНАЛОВ | 1994 |

|

RU2110151C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1989 |

|

SU1646053A1 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ, ОБЪЕДИНЕННЫЙ С КОНТРОЛЛЕРОМ АМПЛИТУДНОЙ МОДУЛЯЦИИ И КОНТРОЛЛЕРОМ ФАЗОВОЙ МОДУЛЯЦИИ | 1994 |

|

RU2121755C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2001 |

|

RU2214043C2 |

Изобретение относится к области синтеза частот и может использоваться в синтезаторах частоты с дробным значением коэффициента деления. Достигаемый технический результат - снижение уровня паразитных сигналов. Синтезатор с изменяемой частотой содержит множество накапливающих сумматоров с фиксацией состояния средства для дифференцирования и делитель частоты. В способе синтеза частоты сигнала для регулируемого синтезатора частот формируют множества интегрированных сигналов, сигналы переноса, дифференцируют сигналы переноса, объединяют дифференцированные сигналы и сигналы переноса для формирования сигнала изменяемого делителя, который подают на делитель частоты. Радиотелефон содержит радиоприемник для приема радиочастотных сигналов, радиопередатчик для передачи радиочастотных сигналов, контроллер, средство для генерирования сигнала локального осциллятора для радиоприемника и сигнала передачи для радиопередатчика, средство для генерирования синхронизирующего сигнала, осциллятор с изменяемой частотой для генерации выходного сигнала, делитель частоты, фазовый компаратор, сеть накапливающих сумматоров, интеграторы, элементы задержки, дифференциаторы. 3 с. и 4 з.п. ф-лы, 11 ил.

| US 5070310, 03.12.1991 | |||

| US 4609881, 02.09.1986 | |||

| US 4816774, 28.03.1989 | |||

| US 3696422, 03.10.1972 | |||

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| SU 16554969 A1, 07.06.1991 | |||

| US 4918403, 17.04.1990 | |||

| Электромеханический исполнительный орган системы ориентации искусственного спутника Земли | 2016 |

|

RU2649560C2 |

| КОМПОЗИЦИЯ ИНГРЕДИЕНТОВ ДЛЯ НАСТОЙКИ ГОРЬКОЙ "ИШИМСКАЯ ЛЮБИТЕЛЬСКАЯ" | 1993 |

|

RU2124047C1 |

Авторы

Даты

2000-07-20—Публикация

1992-12-23—Подача