Предлагаемые объекты изобретения объединены единым изобретательским замыслом, относятся к радиоизмерительной технике.

Известен способ измерения частоты аналогового сигнала, см. патент WO 91/04496, МКИ G 01 R 23/00, 4.04.1991. Способ заключается в получении спектральных компонент сигнала из его дискретных отсчетов путем преобразования, определении спектральной компоненты сигнала с наибольшим значением и присвоении частоты данной компоненты частоте оцениваемого сигнала.

Недостатком этого способа является низкие точность и помехоустойчивость оценивания частоты сигнала.

Наиболее близким по своей технической сущности к заявляемому является способ по патенту США, N 4904930, МКИ G 01 R 23/16, 27.02.1990. Способ-прототип заключается в предварительной дискретизации сигнала в пределах полосы частот поиска, вычислении компонент спектральной плотности мощности в дискретных точках методом преобразования Фурье, выделении частотной области ΔF функции спектральной плотности мощности с максимальной концентрацией мощности и вычислении несущей частоты в этой области.

Данный способ позволяет более точно определять несущую частоту сигнала за счет дополнительных вычислений, однако способ-прототип имеет низкую помехоустойчивость.

Известно устройство оценивания несущей частоты аналогового входного сигнала, см. патент WO 91/04496, МКИ G 01 R 23/00, 4.04.1991. Устройство включает последовательно соединенные блок дискретизации входного сигнала, преобразующее устройство для получения спектральных компонент из дискретизированного сигнала, блок определения спектральной компоненты, имеющей наибольшую спектральную величину мощности, и блок присвоения частоты данной компоненты частоте оцениваемого сигнала.

Основным недостатком устройства является его низкая помехоустойчивость.

Наиболее близким к заявленному по своей технической сущности является устройство оценивания несущей частоты, см. патент США, N 4904930, МКИ G 01 R 23/16, 27.05.1990, фиг. 1.

Устройство-прототип с учетом элементов синхронизации содержит последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, группы входов управления которых объединены между собой и выходами управления блока управления, группа адресных входов которого соединена с группами адресных входов первого и второго блока памяти.

Благодаря использованию блока определения частоты повышается точность оценивания.

Недостатком устройства-прототипа является низкая помехоустойчивость.

Целью заявляемых объектов изобретения является разработка способов (варианты) и устройств (варианты) оценивания несущей частоты сигнала, которые обеспечивают повышение помехоустойчивости оценивания несущей частоты.

Способ оценивания несущей частоты (первый вариант).

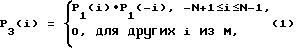

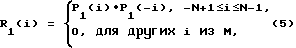

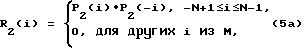

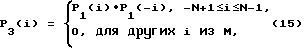

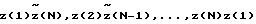

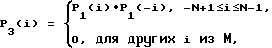

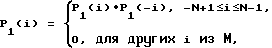

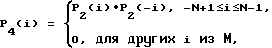

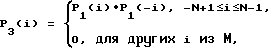

Поставленная цель в первом варианте заявляемого способа достигается тем, что в известном способе оценивания несущей частоты сигнала, заключающемся в предварительной дискретизации принятого сигнала в пределах полосы частот поиска в первую последовательность дискретных отсчетов P1, вычислении компонент спектральной плотности мощности в дискретных точках методом преобразования Фурье, выделении частотной области спектральной плотности мощности с максимальной концентрацией мощности сигнала и вычислении оценки несущей частоты в выделенной области, дополнительно принятый сигнал сдвигают по фазе на π/2 и дискретизируют его во вторую последовательность P2 дискретных отсчетов. Формируют третью последовательность дискретных отсчетов P3 объемом M ≥ 2N-1, где M - общее число дискретных отсчетов, путем перемножения дискретных отсчетов первой последовательности P1 по формуле:

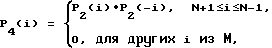

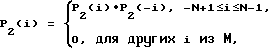

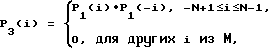

где N - число отсчетов, определяющее длину окна, i - номер дискретного отсчета. Формируют четвертую последовательность дискретных отсчетов P4 объемом M ≥ 2N-1 путем перемножения дискретных отсчетов второй последовательности P2 по формуле:

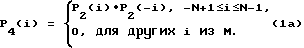

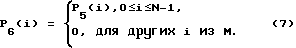

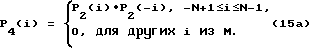

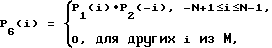

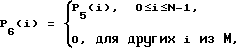

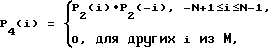

Формируют пятую последовательность дискретных отсчетов P5 путем поэлементного сложения дискретных отсчетов третьей P3 и четвертой P4 последовательностей. Формируют шестую последовательность дискретных отсчетов P6 объемом M ≥ 2N-1 путем перемножения дискретных отсчетов первой P1 и второй P2 последовательностей по формуле:

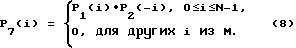

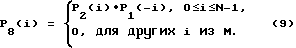

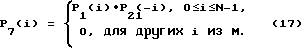

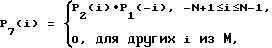

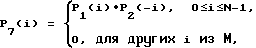

Формируют седьмую последовательность дискретных отсчетов P7 объемом M ≥ 2N-1 путем умножения дискретных отсчетов второй P2 и первой P1 последовательностей по формуле:

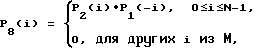

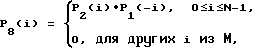

Формируют восьмую последовательность дискретных отсчетов P8 путем поэлементного вычитания дискретных отсчетов седьмой последовательности P7 из дискретных отсчетов шестой последовательности P6. Формируют девятую последовательность дискретных отсчетов P9 объемом M ≥ 2N-1 путем сложения дискретных отсчетов пятой P5 и восьмой P8 последовательностей по формуле:

P9(i) = P5(i) + jP8(i),

где j - мнимая единица. Преобразуют девятую последовательность P9 методом дискретного преобразования Фурье.

Способ оценивания несущей частоты (второй вариант).

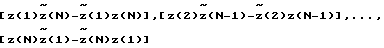

Поставленная цель во втором варианте заявляемого способа достигается тем, что в известном способе оценивания несущей частоты сигнала, заключающемся в предварительной дискретизации принятого сигнала в пределах полосы частот поиска в первую последовательность дискретных отсчетов P1, вычислении компонент спектральной плотности мощности в дискретных точках, выделении частотной области спектральной плотности мощности с максимальной концентрацией мощности сигнала и вычислении оценки несущей частоты в выделенной области, дополнительно принятый сигнал сдвигают по фазе на π/2 и дискретизируют его во вторую последовательность дискретных отсчетов P2. Формируют последовательность произведений R1(i) объемом M ≥ 2N-1, где M - общее число дискретных отсчетов, путем перемножения первой последовательности P1 по формуле:

где N - число отсчетов, определяющее длину окна, i - номер произведения и дискретного отсчета. Формируют последовательность произведений R2(i) объемом M ≥ 2N-1 путем перемножения дискретных отсчетов второй последовательности P2 по формуле:

Затем суммируют поэлементно произведения R1(i) и R2 и умножают результат суммирования на нормирующий множитель. Полученную последовательность дискретных отсчетов преобразуют методом дискретного косинусного преобразования.

Способ оценивания несущей частоты (третий вариант).

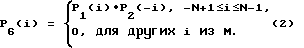

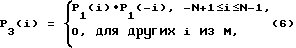

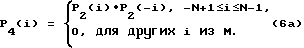

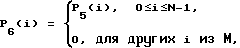

Поставленная цель в третьем варианте заявляемого способа достигается тем, что в известном способе оценивания несущей частоты сигнала, заключающемся в предварительной дискретизации в пределах полосы частот поиска принятого сигнала в первую последовательность дискретных отсчетов P1, вычислении компонент спектральной плотности мощности в дискретных точках, выделении частотной области спектральной плотности мощности с максимальной концентрацией мощности сигнала и вычислении оценки несущей частоты в выделенной области, дополнительно принятый сигнал сдвигают по фазе на π/2 и дискретизируют его во вторую последовательность дискретных отсчетов P2. Формируют третью последовательность дискретных отсчетов P3 объемом M ≥ 2N-1, где M - общее число дискретных отсчетов, путем перемножения дискретных отсчетов первой последовательности P1 по формуле:

где N - число отсчетов, определяющее длину окна, i - номер дискретного отсчета. Формируют четвертую последовательность дискретных отсчетов P4 объемом M ≥ 2N-1 путем перемножения дискретных отсчетов второй последовательности P2 по формуле:

Формируют пятую последовательность дискретных отсчетов P5 путем поэлементного сложения дискретных отсчетов третьей P3 и четвертой P4 последовательностей. Формируют шестую последовательность дискретных отсчетов P6 объемом M ≥ 2N-1 по формуле:

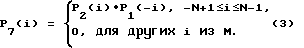

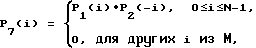

Формируют седьмую последовательность дискретных отсчетов P7 объемом M ≥ 2N-1 путем перемножения дискретных отсчетов первой P1 и второй P2 последовательностей по формуле:

Формируют восьмую последовательность дискретных отсчетов P8 объемом M ≥ 2N-1 путем перемножения дискретных отсчетов второй P2 и первой P1 последовательностей по формуле:

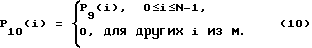

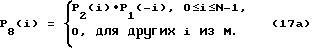

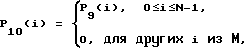

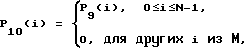

Формируют девятую последовательность дискретных отсчетов P9 путем поэлементного вычитания дискретных отсчетов восьмой последовательности P8 из дискретных отсчетов седьмой последовательности P7. Формируют десятую последовательность дискретных отсчетов P10 объемом M ≥ 2N-1 по формуле:

Формируют одиннадцатую последовательность дискретных отсчетов P11 путем сложения дискретных отсчетов шестой P6 и десятой P10 последовательностей по формуле:

P11(i) = P6(i) + j • P10(i), (11)

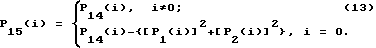

где j - мнимая единица. Формируют двенадцатую последовательность дискретных отсчетов P12 методом прямого быстрого преобразования Фурье над одиннадцатой последовательностью дискретных отсчетов P11. Формируют тринадцатую последовательность дискретных отсчетов P13 методом обратного быстрого преобразования Фурье над одиннадцатой последовательностью дискретных отсчетов P11. Формируют четырнадцатую последовательность дискретных отсчетов P14 объемом M ≥ 2N-1 путем поэлементного сложения дискретных отсчетов тринадцатой P13 и двенадцатой последовательностей дискретных отсчетов P12 по формуле:

P14(i) = {Rе P12(i) + Re P13(i)} + j{Im P12(i) + Im P13(i)}. (12)

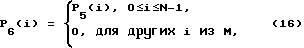

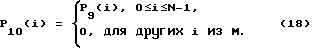

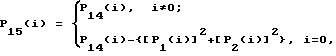

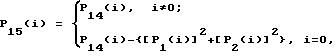

Формируют пятнадцатую последовательность дискретных отсчетов P15 объемом M ≥ 2N-1 по формуле:

Формируют шестнадцатую последовательность дискретных отсчетов P16 путем умножения пятнадцатой последовательности дискретных отсчетов P15 на нормирующий множитель. Из полученной последовательности вычисляют компоненты спектральной плотности мощности.

Способ оценивания несущей частоты (четвертый вариант).

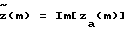

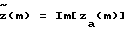

Поставленная цель в четвертом варианте заявляемого способа достигается тем, что в известном способе оценивания несущей частоты сигнала, заключающемся в предварительной дискретизации в пределах полосы частот поиска принятого сигнала в первую последовательность дискретных отсчетов P1, вычислении компонент спектральной плотности мощности в дискретных точках, выделении частотной области спектральной плотности мощности с максимальной концентрацией мощности сигнала и вычислении оценки несущей частоты в выделенной области, дополнительно после дискретизации сигнала в первую последовательность дискретных отсчетов P1 над ним выполняют прямое преобразование Фурье, обнуляют спектральные компоненты на частотах, меньших нуля, затем из полученных спектральных компонент формируют промежуточную последовательность дискретных отсчетов Pn методом обратного быстрого преобразования Фурье. Формируют вторую последовательность дискретных отсчетов P2 объемом М ≥ 2N-1, где М - общее число дискретных отсчетов, по формуле:

P2(i)=Im[Pn(i)].

Формируют третью последовательность дискретных отсчетов P3 объемом М ≥ 2N-1 путем перемножения дискретных отсчетов первой последовательности P1 по формуле:

где N - число отсчетов, определяющее длину окна, i - номер дискретного отсчета. Формируют четвертую последовательность дискретных отсчетов P4 объемом М ≥ 2N-1 путем перемножения дискретных отсчетов второй последовательности P2 по формуле:

Формируют пятую последовательность дискретных отсчетов P5 путем поэлементного сложения дискретных отсчетов третьей P3 и четвертой P4 последовательностей. Формируют шестую последовательность дискретных отсчетов P6 объемом М ≥ 2N-1 по формуле:

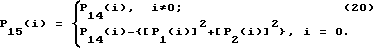

Формируют седьмую последовательность дискретных отсчетов P7 объемом М ≥ 2N-1 путем перемножения дискретных отсчетов первой P1 и второй P2 последовательностей по формуле:

Формируют восьмую последовательность дискретных отсчетов P8 объемом М ≥ 2N-1 путем перемножения дискретных отсчетов второй P2 и первой P1 последовательностей по формуле:

Формируют девятую последовательность дискретных отсчетов P9 путем поэлементного вычитания дискретных отсчетов восьмой последовательности P8 из дискретных отсчетов седьмой последовательности P7. Формируют десятую последовательность дискретных отсчетов P10 объемом М ≥ 2N-1 по формуле:

Формируют одиннадцатую последовательность дискретных отсчетов P11 путем сложения дискретных отсчетов шестой P6 и десятой P10 последовательностей по формуле:

P11(i) = P6(i) + j•P10(i), (18а)

где j - мнимая единица. Формируют двенадцатую последовательность дискретных отсчетов P12 методом прямого быстрого преобразования Фурье над одиннадцатой последовательностью дискретных отсчетов P11. Формируют тринадцатую последовательность дискретных отсчетов P12 методом обратного быстрого преобразования Фурье над одиннадцатой последовательностью дискретных отсчетов P11. Формируют четырнадцатую последовательность дискретных отсчетов P14 объемом М ≥ 2N-1 путем поэлементного сложения дискретных отсчетов тринадцатой P13 и двенадцатой последовательностей дискретных отсчетов P12 по формуле:

P14(i) = {Re P12(i) + Re P13(i)} + j{ImP12(i) + Im P13(i)}. (19)

Формируют пятнадцатую последовательность дискретных отсчетов P15 объемом М ≥ 2N-1 по формуле:

Формируют шестнадцатую последовательность дискретных отсчетов P16 путем умножения пятнадцатой последовательности дискретных отсчетов P15 на нормирующий множитель. Из полученной последовательности вычисляют компоненты спектральной плотности мощности.

Указанная новая совокупность существенных признаков позволяет осуществлять измерение частоты в более жестких условиях приема, чем и достигается требуемая помехоустойчивость оценивания несущей частоты.

Устройство оценивания несущей частоты (первый вариант).

Поставленная цель в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются информационными выходами устройства оценивания несущей частоты, блок управления, группа адресных выходов которого соединена с группами адресных входов первого и второго блоков памяти, а первая группа управляющих выходов соединена с группами управляющих входов первого и второго блоков памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров и блока определения частоты, дополнительно введены фазовращатель, линия задержки, первый и второй аналого-цифровые преобразователи, первый и второй блоки преобразования сигнала и коммутатор. Информационные входы фазовращателя и линии задержки объединены и соединены с информационным входом устройства оценивания несущей частоты. Информационный вход первого аналого-цифрового преобразователя соединен с выходом линии задержки. Тактовый вход первого аналого-цифрового преобразователя объединен с тактовым входом второго аналого-цифрового преобразователя и соединен с тактовым входом устройства оценивания несущей частоты. Вход разрешения первого аналого-цифрового преобразователя объединен с входом разрешения второго аналого-цифрового преобразователя и выходом разрешения блока управления. Выход готовности первого аналого-цифрового преобразователя соединен с первым входом готовности блока управления. Второй вход готовности блока управления соединен с выходом готовности второго аналого-цифрового преобразователя. Информационный вход второго аналого-цифрового преобразователя соединен с выходом фазовращателя. Информационные выходы второго аналого-цифрового преобразователя соединены с вторыми группами информационных входов первого и второго блоков преобразования сигналов, первые группы информационных входов которых соединены с информационными выходами первого аналого-цифрового преобразователя. N групп информационных выходов каждого блока преобразования сигнала соединены соответственно с первой по N и с N+1 по 2N группами информационных входов коммутатора. Информационные выходы коммутатора соединены с информационными входами первого блока памяти. Адресные входы коммутатора соединены с адресными выходами блока управления. Второй управляющий выход блока управления соединен с входами управления первого и второго блоков преобразования сигнала.

Первый блок преобразования сигнала выполнен содержащим два идентичных тракта обработки и N сумматоров. Первая и вторая группы информационных входов первого блока преобразования сигнала соединены с информационными входами соответственно первого и второго трактов обработал, управляющие входы которых объединены и соединены с управляющим входом первого блока преобразования сигнала. N групп выходов первого тракта обработки соединены соответственно с первыми группами входов N сумматоров, вторые группы входов которых соединены с соответствующими N группами выходов второго тракта обработки. Группы выходов N сумматоров являются N группами информационных выходов первого блока преобразования сигнала. Каждый тракт обработки выполнен содержащим первую группу из N последовательно соединенных регистров, N умножителей и вторую группу из N последовательно соединенных регистров. Информационные входы первого регистра первой группы объединены с информационными входами N-го регистра второй группы и соединены с группой информационных входов соответствующего тракта обработки. Выходы регистров первой группы RG1i соединены с первыми группами входов соответствующих умножителей X1j, i= j, i=1, 2, ..., N. Выходы регистров второй группы RG2i соединены со вторыми группами входов умножителей X2j в обратном порядке, когда j=N-i+1. Выходы умножителей являются соответствующей группой выходов тракта обработки. Управляющий вход тракта обработки соединен с управляющими входами всех регистров первой и второй групп.

Второй блок преобразования сигнала выполнен содержащим два идентичных тракта обработки и N блоков вычитания. Первые группы информационных входов первого и второго трактов обработки объединены и соединены с первой группой информационных входов второго блока преобразования сигнала. Вторые группы информационных входов первого и второго трактов объединены и соединены c второй группой информационных входов второго блока преобразования сигнала. Управляющие входы первого и второго трактов обработки объединены и соединены с входом управления второго блока преобразования сигнала. N групп выходов первого тракта обработки соединены с входами уменьшаемого соответствующих N блоков вычитания, группы входов вычитаемого которых соединены с соответствующими выходами второго тракта обработки. Группы выходов N блоков вычитания являются N группами информационных выходов второго блока преобразования сигнала. Каждый тракт обработки выполнен содержащим первую группу из N последовательно соединенных регистров, N умножителей и вторую группу из N последовательно соединенных регистров. Информационные входы первого регистра первой группы объединены с первой группой информационных входов тракта обработки. Информационные входы N-го регистра второй группы объединены с второй группой информационных входов тракта обработки. Выходы регистров первой группы RG1i соединены с первыми группами входов соответствующих умножителей X1j, i= j, i=1, 2, ..., N. Выходы регистров второй группы RG2i соединены со вторыми группами входов соответствующих умножителей X2j, i=j, i=1, 2, ..., N. Выходы умножителей являются соответствующими группами выходов тракта обработки. Управляющий вход тракта обработки соединен с управляющими входами всех регистров первой и второй групп.

Устройство оценивания несущей частоты (второй вариант).

Поставленная цель во втором варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются информационными выходами устройства оценивания несущей частоты, блок управления, группа адресных выходов которого соединена с группами адресных входов первого и второго блоков памяти, а первая группа управляющих выходов соединена с группами управляющих входов первого блока памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров, второго блока памяти и блока определения частоты, дополнительно введены аналого-цифровой преобразователь, линия задержки, блок преобразования по Гильберту, первый и второй блоки преобразования сигнала и коммутатор. Информационный вход аналого-цифрового преобразователя соединен с информационным входом устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя соединен c тактовым входом устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя соединен со входом готовности блока управления. Выход разрешения блока управления соединен со входом разрешения аналого-цифрового преобразователя. Выходы аналого-цифрового преобразователя соединены с информационными входами блока преобразования по Гильберту и информационными входами линии задержки. Выходы линии задержки соединены с первыми группами информационных входов первого и второго блоков преобразования сигнала. Вторые группы информационных входов первого и второго блоков преобразования сигнала соединены с выходами блока преобразования по Гильберту. N групп выходов первого блока преобразования сигнала соединены с первой совокупностью из N групп соответствующих информационных входов коммутатора. Вторая совокупность из N групп информационных входов коммутатора соединена с N соответствующих групп выходов второго блока преобразования сигнала. Управляющий вход второго блока преобразования сигнала объединен с управляющим входом первого блока преобразования сигнала и вторым управляющим выходом блока управления. Третий управляющий выход блока управления соединен с управляющими входами линии задержки и блока преобразования по Гильберту. Адресные выходы блока управления соединены с адресными входами коммутатора. Выходы коммутатора соединены с информационными входами первого блока памяти.

Первый и второй блоки преобразования сигнала выполнены аналогично рассмотренным в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Устройство оценивания несущей частоты (третий вариант).

Поставленная цель в третьем варианте заявленного устройства, реализующего второй вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем блок управления и первый блок памяти, последовательно соединенные блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются информационными выходами устройства оценивания несущей частоты, управляющие входы которого объединены с управляющими входами первого блока памяти, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена с адресными входами первого и второго блоков памяти, дополнительно введены фазовращатель, линия задержки, первый и второй аналого-цифровые преобразователи, блок преобразования сигнала, коммутатор и блок дискретного косинусного преобразования и определения спектральной плотности мощности. Вход фазовращателя объединен с входом линии задержки и соединен с информационным входом устройства оценивания несущей частоты. Выход фазовращателя соединен с информационным входом второго аналого-цифрового преобразователя. Тактовый вход второго аналого-цифрового преобразователя объединен с тактовым входом первого аналого-цифрового преобразователя и соединен с тактовым входом устройства оценивания несущей частоты. Выход готовности второго аналого-цифрового преобразователя соединен с вторым входом готовности блока управления. Первый вход готовности блока управления соединен с выходом готовности первого аналого-цифрового преобразователя. Вход разрешения первого аналого-цифрового преобразователя объединен с входом разрешения второго аналого-цифрового преобразователя и выходом разрешения блока управления. Информационные выходы первого аналого-цифрового преобразователя соединены с первой группой информационных входов блока преобразования сигнала. Вторая группа информационных входов блока преобразования сигнала соединена с информационными выходами второго аналого-цифрового преобразователя. Управляющий вход блока преобразования сигнала соединен со вторым управляющим выходом блока управления. N групп выходов блока преобразования сигнала соединены с соответствующими N группами входов коммутатора. Адресные входы коммутатора объединены с адресными входами первого блока памяти. Информационные выходы коммутатора соединены с информационными входами первого блока памяти. Выходы первого блока памяти соединены с информационными входами блока дискретного косинусного преобразования и определения спектральной плотности мощности. Управляющие входы блока дискретного косинусного преобразования и определения спектральной плотности мощности соединены с первой группой управляющих выходов блока управления, а выходы соединены с информационными входами блока фильтров.

Блок преобразования сигнала выполнен аналогично первому блоку преобразования сигнала, рассмотренному в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

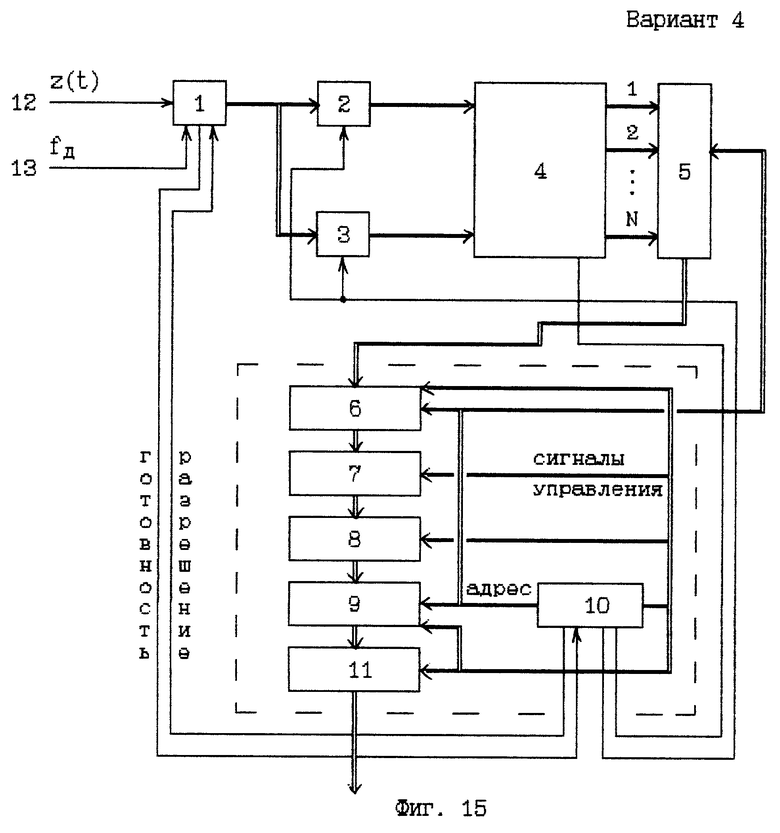

Устройство оценивания несущей частоты (четвертый вариант).

Поставленная цель в четвертом варианте заявленного устройства, реализующего второй вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем первый блок памяти, блок управления, последовательно соединенные блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются выходами устройства оценивания несущей частоты, а управляющие входы объединены с управляющими входами первого блока памяти, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена с адресными входами первого и второго блоков памяти, дополнительно введены аналого-цифровой преобразователь, линия задержки, блок преобразования по Гильберту, блок преобразования сигнала, коммутатор и блок дискретного косинусного преобразования и определения спектральной плотности мощности. Информационный вход аналого-цифрового преобразователя является информационным входом устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя соединен с тактовым входом устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя соединен с входом готовности блока управления. Разрешающий выход блока управления соединен со входом разрешения аналого-цифрового преобразователя. Информационные выходы аналого-цифрового преобразователя соединены с информационными входами блока преобразования по Гильберту и информационными входами линии задержки. Выходы линии задержки соединены с первой группой информационных входов блока преобразования сигнала. Вторая группа информационных входов блока преобразования сигнала соединена с выходами блока преобразования по Гильберту. N групп информационных выходов блока преобразования сигнала соединены с соответствующими N группами информационных входов коммутатора. Адресные входы коммутатора объединены с адресными входами первого блока памяти. Информационные выходы коммутатора объединены с информационными входами первого блока памяти. Выходы первого блока памяти соединены с информационными входами блока дискретного косинусного преобразования и определения спектральной плотности мощности. Информационные выходы блока дискретного косинусного преобразования и определения спектральной плотности мощности соединены с информационными входами блока фильтров. Входы управления блока дискретного косинусного преобразования и определения спектральной плотности мощности соединены с первой группой управляющих выходов блока управления. Второй выход управления блока управления соединен с входами управления линии задержки и блока преобразования по Гильберту. Третий выход управления блока управления соединен c входом управления блока преобразования сигнала.

Блок преобразования сигнала выполнен аналогично первому блоку преобразования сигнала, рассмотренному в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

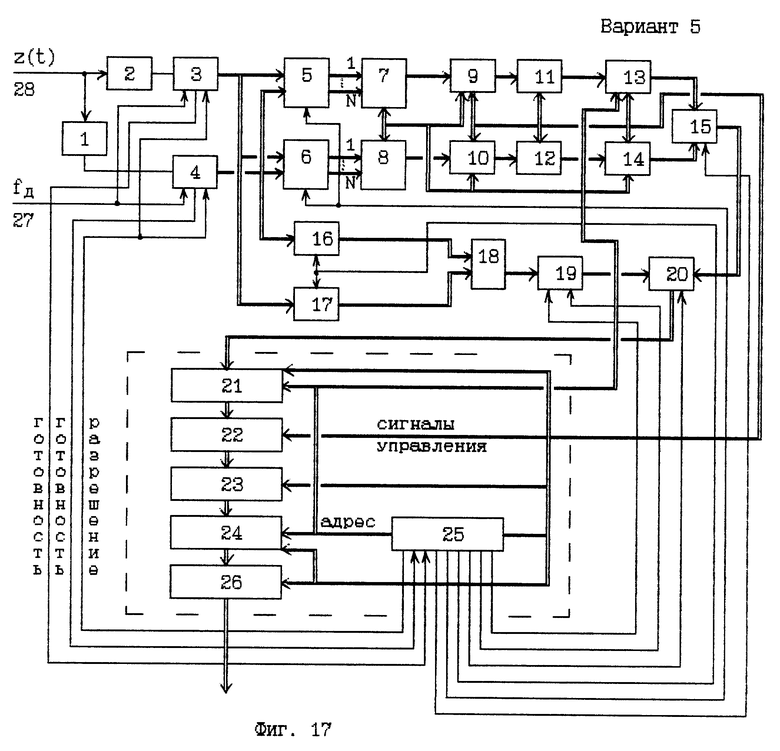

Устройство оценивания несущей частоты (пятый вариант).

Поставленная цель в пятом варианте заявленного устройства, реализующего третий вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем блок управления и последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются выходами устройства оценивания несущей частоты, а управляющие входы объединены с управляющими входами первого блока памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена с адресными входами первого и второго блоков памяти, дополнительно введены фазовращатель, линия задержки, первый и второй аналого-цифровые преобразователи, первый и второй коммутаторы, блок быстрого преобразования Фурье, блок обратного быстрого преобразования Фурье, третий, четвертый, пятый и шестой блоки памяти, сумматор, блок вычитания, первый, второй и третий регистры и блок вычисления квадрата модуля аналитического сигнала. Вход линии задержки объединен с входом фазовращателя и информационным входом устройства оценивания несущей частоты. Выход линии задержки соединен с информационным входом первого аналого-цифрового преобразователя. Тактовый вход первого аналого-цифрового преобразователя объединен с тактовым входом второго аналого-цифрового преобразователя и тактовым входом устройства оценивания несущей частоты. Вход разрешения первого аналого-цифрового преобразователя объединен с входом разрешения второго аналого-цифрового преобразователя и выходом разрешения блока управления. Первый вход готовности блока управления соединен с выходом готовности первого аналого-цифрового преобразователя. Второй вход готовности блока управления соединен с выходом готовности второго аналого-цифрового преобразователя. Информационный вход второго аналого-цифрового преобразователя соединен с выходом фазовращателя. Выходы второго аналого-цифрового преобразователя соединены c информационными входами первого регистра и вторыми группами информационных входов первого и второго блоков преобразования сигнала, первые группы информационных входов которых соединены с выходами первого аналого-цифрового преобразователя и информационными входами второго регистра. Выходы второго регистра соединены с второй группой информационных входов блока вычисления квадрата модуля аналитического сигнала. Первая группа информационных входов блока вычисления квадрата модуля аналитического сигнала соединена с выходами первого регистра. Управляющий вход первого регистра объединен с управляющим входом второго регистра и вторым управляющим выходом блока управления. Третий управляющий выход блока управления соединен с входом управления первого блока преобразования сигнала и входом управления второго блока преобразования сигнала. N групп выходов второго блока преобразования сигнала соединены с соответствующими N группами информационных входов второго коммутатора. Адресные входы коммутатора объединены с адресными входами первого, третьего, четвертого, пятого и шестого блоков памяти и адресными входами первого коммутатора. N групп информационных входов коммутатора соединены с соответствующими N группами выходов первого блока преобразования сигнала. Выходы коммутатора соединены с информационными входами третьего блока памяти. Выходы третьего блока памяти соединены с информационными входами блока быстрого преобразования Фурье. Выходы блока быстрого преобразования Фурье соединены с информационными входами пятого блока памяти. Выходы пятого блока памяти соединены с первой группой информационных входов сумматора. Управляющие входы пятого блока памяти объединены с управляющими входами третьего блока памяти, блока быстрого преобразования Фурье, блока обратного быстрого преобразования Фурье, шестого бока памяти, первой группой управляющих выходов блока управления и управляющими входами четвертого блока памяти. Информационные входы четвертого блока памяти соединены с выходами второго коммутатора. Выходы четвертого блока памяти соединены с информационными входами блока обратного быстрого преобразования Фурье. Выходы блока обратного быстрого преобразования Фурье соединены с информационными входами шестого блока памяти. Выходы шестого блока памяти соединены с второй группой информационных входов сумматора. Управляющий вход сумматора соединен с четвертым управляющим выходом блока управления. Выходы сумматора соединены с группой входов уменьшаемого блока вычитания, группа входов вычитаемого которого соединена с выходами третьего регистра. Информационные входы третьего регистра соединены с выходами блока вычисления квадрата модуля аналитического сигнала. Вход записи третьего регистра с выходом записи блока управления. Вход считывания третьего регистра соединен с выходом считывания блока управления. Пятый управляющий выход блока управления соединен со входом управления блока вычитания. Выходы блока вычитания соединены с информационными входами первого блока памяти.

Первый и второй блоки преобразования сигнала выполнены аналогично рассмотренным в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Устройство оценивания несущей частоты (шестой вариант).

Поставленная цель в шестом варианте заявленного устройства, реализующего третий вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем блок управления и последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются выходами устройства оценивания несущей частоты, а входы управления объединены со входами управления первого блока памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена c адресными входами первого и второго блоков памяти, дополнительно введены аналого-цифровой преобразователь, линия задержки, блок преобразования по Гильберту, третий, четвертый, пятый и шестой блоки памяти, первый и второй коммутаторы, первый и второй блоки преобразования сигнала, блок быстрого преобразования Фурье, блок обратного быстрого преобразования Фурье, сумматор, первый, второй и третий регистры, блок вычисления квадрата модуля аналитического сигнала и блок вычитания. Информационный вход аналого-цифрового преобразователя соединен с информационным входом устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя соединен с тактовым входом устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя соединен с входом готовности блока управления. Выход разрешения блока управления соединен с входом разрешения аналого-цифрового преобразователя. Выходы аналого-цифрового преобразователя соединены с информационными входами блока преобразования по Гильберту и информационными входами линии задержки. Выходы линии задержки соединены с информационными входами второго регистра, первой группой информационных входов первого блока преобразования сигнала и первой группой информационных входов второго блока преобразования сигнала. Вторая группа информационных входов второго блока преобразования сигнала объединена с информационными входами первого регистра, выходами блока преобразования по Гильберту и второй группой информационных входов первого блока преобразования сигнала. N групп выходов первого блока преобразования сигнала соединены с соответствующими N группами информационных входов первого коммутатора. Выходы первого коммутатора соединены с информационными входами третьего блока памяти. Адресные входы первого коммутатора объединены с адресными входами третьего, четвертого, пятого и шестого блоков памяти, группой адресных выходов блока управления и адресными входами второго коммутатора. N групп информационных входов второго коммутатора соединены с соответствующими N группами выходов второго блока преобразования сигнала. Выходы второго коммутатора соединены с информационными входами четвертого блока памяти. Входы управления четвертого блока памяти объединены с входами управления блока быстрого преобразования Фурье, блока обратного быстрого преобразования Фурье, входами управления пятого и шестого блоков памяти, первой группой управляющих выходов блока управления и управляющими входами третьего блока памяти. Выходы третьего блока памяти соединены с информационными входами блока быстрого преобразования Фурье. Выходы блока быстрого преобразования Фурье соединены с информационными входами пятого блока памяти. Выходы пятого блока памяти соединены с первой группой информационных входов сумматора. Вторая группа информационных входов сумматора соединена с выходами шестого блока памяти. Информационные входы шестого блока памяти соединены с выходами блока обратного быстрого преобразования Фурье. Информационные входы блока обратного быстрого преобразования Фурье соединены с выходами четвертого блока памяти. Выходы сумматора соединены с входами уменьшаемого блока вычитания. Входы вычитаемого блока вычитания соединены с выходами третьего регистра. Информационные входы третьего регистра соединены с выходами блока вычисления квадрата модуля аналитического сигнала. Первая группа информационных входов блока вычисления квадрата модуля аналитического сигнала соединена с выходами первого регистра. Вторая группа информационных входов блока вычисления квадрата модуля аналитического сигнала соединена с выходами второго регистра. Управляющий вход второго регистра объединен с управляющим входом первого регистра и вторым управляющим выходом блока управления. Выход записи блока управления соединен с входом записи третьего регистра. Вход считывания третьего регистра соединен c выходом считывания блока управления. Третий управляющий выход блока управления соединен c управляющим входом блока вычитания. Выходы блока управления соединены с информационными входами первого блока памяти. Управляющий вход линии задержки объединен с входами управления блока преобразования по Гильберту и четвертым управляющим выходом блока управления. Пятый управляющий выход блока управления соединен с управляющими входами первого и второго блоков преобразования сигнала. Шестой управляющий выход блока управления соединен с управляющим входом сумматора.

Первый и второй блоки преобразования сигнала выполнены аналогично рассмотренным в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Устройство оценивания несущей частоты (седьмой вариант).

Поставленная цель в седьмом варианте заявленного устройства, реализующего четвертый вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем блок управления и последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются выходами устройства оценивания несущей частоты, а входы управления объединены с входами управления первого блока памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена с адресными входами первого и второго блоков памяти, дополнительно введены аналого-цифровой преобразователь, первый и второй блоки быстрого преобразования Фурье, первый и второй блоки обратного быстрого преобразования Фурье, третий, четвертый, пятый, шестой, седьмой и восьмой блоки памяти, первый и второй блоки преобразования сигнала, первый и второй коммутаторы, первый, второй и третий регистры, блок вычисления квадрата модуля аналитического сигнала, блок вычитания и сумматор. Информационный вход аналого-цифрового преобразователя соединен с информационным входом устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя соединен с тактовым входом устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя соединен со входом готовности блока управления. Вход разрешения аналого-цифрового преобразователя соединен с выходом разрешения блока управления. Выходы аналого-цифрового преобразователя соединены с информационными входами первого блока быстрого преобразования Фурье. Выходы первого блока быстрого преобразования Фурье соединены с информационными входами первого блока обратного быстрого преобразования Фурье. Выходы первого блока обратного быстрого преобразования Фурье соединены с информационными входами третьего блока памяти и информационными входами четвертого блока памяти. Выходы четвертого блока памяти соединены с информационными входами первого регистра и вторыми группами входов первого и второго блоков преобразования сигнала, первые группы информационных входов которых соединены с выходами третьего блока памяти и информационными входами второго регистра. Выходы второго регистра соединены с второй группой информационных входов блока вычисления квадрата модуля аналитического сигнала. Первая группа информационных входов блока вычисления квадрата модуля аналитического сигнала соединена с выходами первого регистра. Управляющий вход первого регистра объединен с управляющим входом второго регистра и вторым управляющим выходом блока управления. Третий управляющий выход блока управления соединен с управляющим входом второго блока преобразования сигнала и управляющим входом первого блока преобразования сигнала. N групп выходов первого блока преобразования сигнала соединены с соответствующими N группами информационных входов первого коммутатора. Входы первого коммутатора соединены с информационными входами пятого блока памяти. Выходы пятого блока памяти соединены с информационными входами второго блока быстрого преобразования Фурье. Выходы второго блока быстрого преобразования Фурье соединены с информационными входами седьмого блока памяти. Выходы (седьмого блока памяти соединены с первой группой информационных входов сумматора. Вторая группа информационных входов сумматора соединена с выходами восьмого блока памяти. Информационные входы восьмого блока памяти соединены с выходами второго блока обратного быстрого преобразования Фурье. Информационные входы второго блока обратного быстрого преобразования Фурье соединены с выходами шестого блока памяти. Информационные входы шестого блока памяти соединены с выходами второго коммутатора. N групп информационных входов второго коммутатора соединены с соответствующими N группами выходов второго блока преобразования сигнала. Адресные входы второго бока преобразования сигнала объединены с адресными входами третьего, четвертого, пятого, шестого, седьмого и восьмого блоков памяти, адресными входами первого коммутатора и группой адресных выходов блока управления. Четвертый управляющий выход блока управления соединен с управляющим входом сумматора. Выходы сумматора соединены с группой входов уменьшаемого блока вычитания, группа входов вычитаемого которого соединена с выходами третьего регистра. Информационные входы третьего регистра соединены с выходами блока вычисления квадрата модуля аналитического сигнала. Вход записи третьего регистра соединен с выходом записи блока управления. Вход считывания третьего регистра соединен с выходом считывания блока управления. Первая группа управляющих выходов блока управления соединена с входами управления первого и второго блоков быстрого преобразования Фурье, первого и второго блоков обратного быстрого преобразования Фурье, входами управления третьего, четвертого, пятого, шестого, седьмого и восьмого блоков памяти. Пятый управляющий выход блока управления соединен со входом управления блока вычитания. Выходы блока вычитания соединены с информационными входами первого блока памяти.

Первый и второй блоки преобразования сигнала выполнены аналогично рассмотренным в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Устройство оценивания несущей частоты (восьмой вариант).

Поставленная цель в восьмом варианте заявленного устройства, реализующего четвертый вариант способа оценивания несущей частоты сигнала, достигается тем, что в известном устройстве оценивания несущей частоты, содержащем блок управления и последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, выходы которого являются выходами устройства оценивания несущей частоты, а управляющие входы объединены с управляющими входами первого блока памяти, блока преобразования Фурье и определения спектральной плотности мощности, блока фильтров, второго блока памяти и первой группой управляющих выходов блока управления, группа адресных выходов которого соединена с адресными входами первого и второго блоков памяти, дополнительно введены аналого-цифровой преобразователь, первый и второй блоки быстрого преобразования Фурье, первый и второй блоки обратного быстрого преобразования Фурье, третий, четвертый, пятый, шестой, седьмой и восьмой блоки памяти, первый и второй блоки преобразования сигнала, первый и второй коммутаторы, первый, второй и третий регистры, блок вычисления квадрата модуля аналитического сигнала, блок вычитания и сумматор. Информационный вход аналого-цифрового преобразователя соединен с информационным входом устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя соединен с тактовым входом устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя соединен с входом готовности блока управления. Вход разрешения аналого-цифрового преобразователя соединен с выходом разрешения блока управления. Выходы аналого-цифрового преобразователя соединены с информационными входами третьего блока памяти и информационными входами первого блока быстрого преобразования Фурье. Выходы первого блока быстрого преобразования Фурье соединены с информационными входами первого блока обратного быстрого преобразования Фурье. Выходы первого блока обратного быстрого преобразования Фурье соединены с информационными входами четвертого блока памяти. Выходы четвертого блока памяти соединены с информационными входами первого регистра, вторыми группами информационных входов первого и второго блоков преобразования сигнала, первые группы информационных входов которых соединены с выходами третьего блока памяти и информационными входами второго регистра. Выходы второго регистра соединены с второй группой информационных входов блока вычисления квадрата модуля аналитического сигнала. Первая группа информационных входов блока вычисления квадрата модуля аналитического сигнала соединена с выходами первого регистра. Управляющий вход первого регистра соединен с управляющим входом второго регистра и вторым управляющим выходом блока управления. Третий управляющий выход блока управления соединен с управляющим входом первого блока преобразования сигнала и управляющим входом второго блока преобразования сигнала. N групп выходов второго блока преобразования сигнала соединены с соответствующими N группами информационных входов второго коммутатора. Выходы второго коммутатора соединены с. информационными входами шестого блока памяти. Выходы шестого блока памяти соединены с информационными входами второго блока обратного быстрого преобразования Фурье. Выходы второго блока обратного быстрого преобразования Фурье соединены с информационными входами восьмого блока памяти. Выходы восьмого блока памяти соединены со второй группой информационных входов сумматора. Первая группа информационных входов сумматора соединена с выходами седьмого блока памяти. Информационные входы седьмого блока памяти соединены с выходами второго блока быстрого преобразования Фурье. Информационные входы второго быстрого преобразования Фурье соединены с выходами пятого блока памяти. Информационные входы пятого блока памяти с выходами первого коммутатора. N групп информационных входов первого коммутатора соединены с соответствующими N группами выходов первого

блока преобразования сигнала. Адресные входы первого коммутатора объединены с адресными входами третьего, четвертого, пятого, шестого, седьмого и восьмого блоков памяти, адресными входами второго коммутатора и группой адресных выходов блока управления. Первая группа управляющих выходов блока управления соединена с управляющими входами первого и второго блока быстрого преобразования Фурье, первого и второго блоков обратного быстрого преобразования Фурье, входами управления третьего, четвертого, пятого, шестого, седьмого и восьмого блоков памяти. Четвертый управляющий выход блока управления соединен с управляющим входом сумматора. Выходы сумматора соединены со входами уменьшаемого блока вычитания, группа входов вычитаемого которого соединена с выходами третьего регистра. Информационные входы третьего регистра соединены с выходами блока вычисления квадрата модуля аналитического сигнала. Вход записи третьего регистра соединен с выходом записи блока управления. Вход считывания третьего регистра соединен с выходом считывания блока управления. Пятый управляющий выход блока управления соединен с управляющим входом блока вычитания. Выходы блока вычитания соединены с информационными входами первого блока памяти.

Первый и второй блоки преобразования сигнала выполнены аналогично рассмотренным в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Перечисленная новая совокупность существенных признаков заявленных устройств (варианты) обеспечивает высокую помехоустойчивость оценивания несущей частоты сигнала. Это достигается тем, что предлагаемые устройства обеспечивают более рельефное представление спектра сигнала за счет адаптивности устройств к изменению параметров сигнала в любой момент времени.

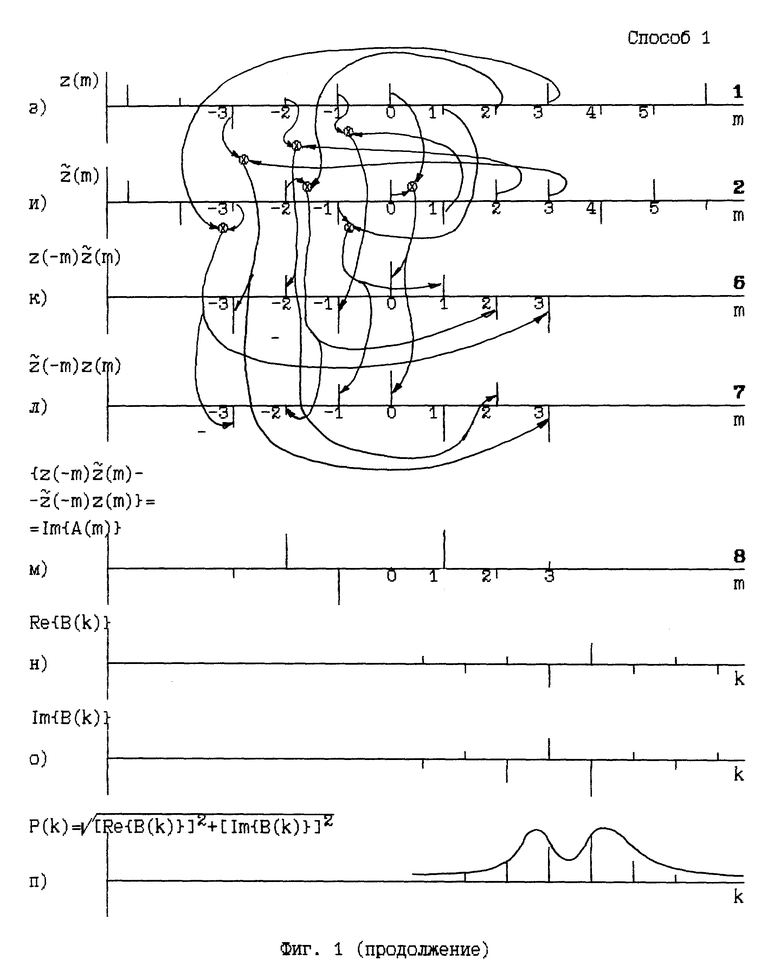

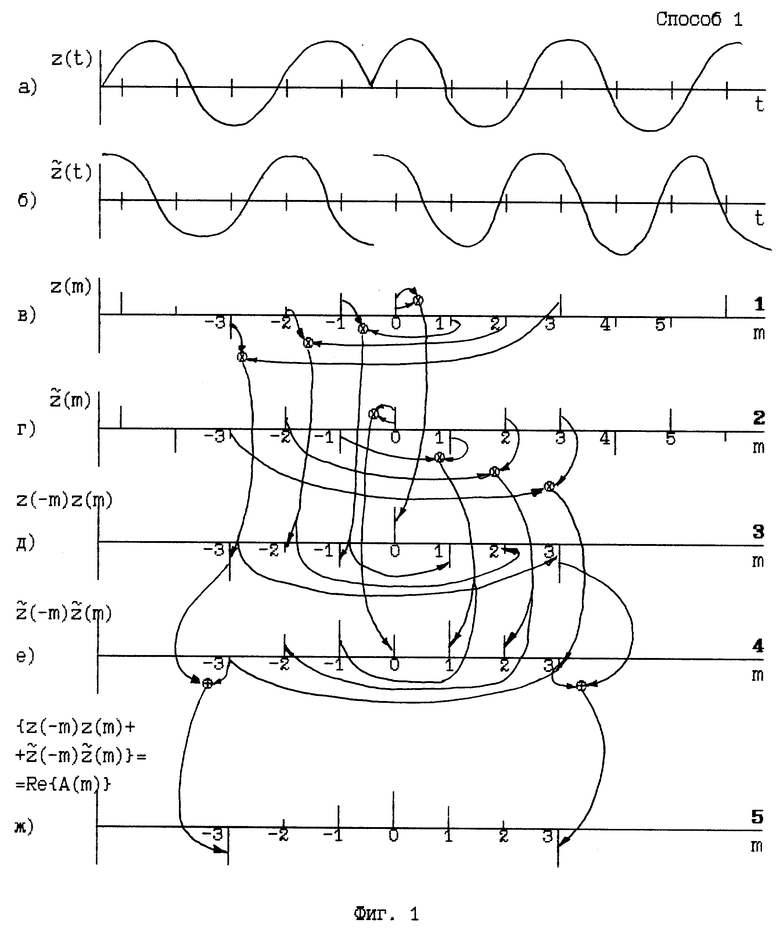

На фиг. 1 на 2-х листах приведены рисунки, поясняющие сущность заявленного первого варианта способа оценивания несущей частоты сигнала;

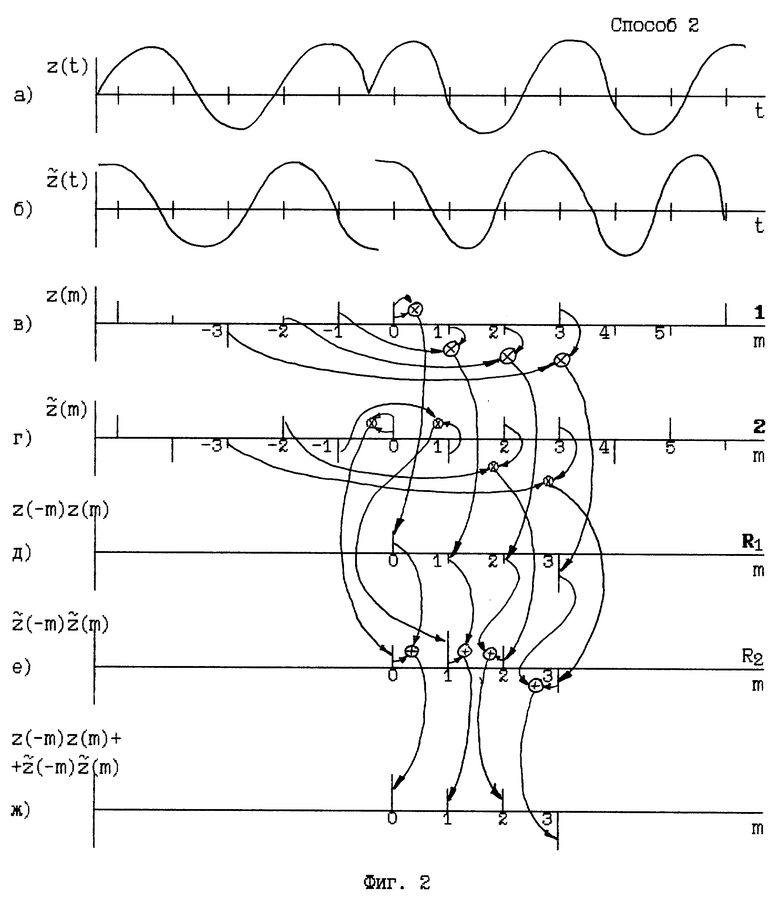

на фиг. 2 на 2-х листах приведены рисунки, поясняющие сущность заявленного второго варианта способа оценивания несущей частоты сигнала;

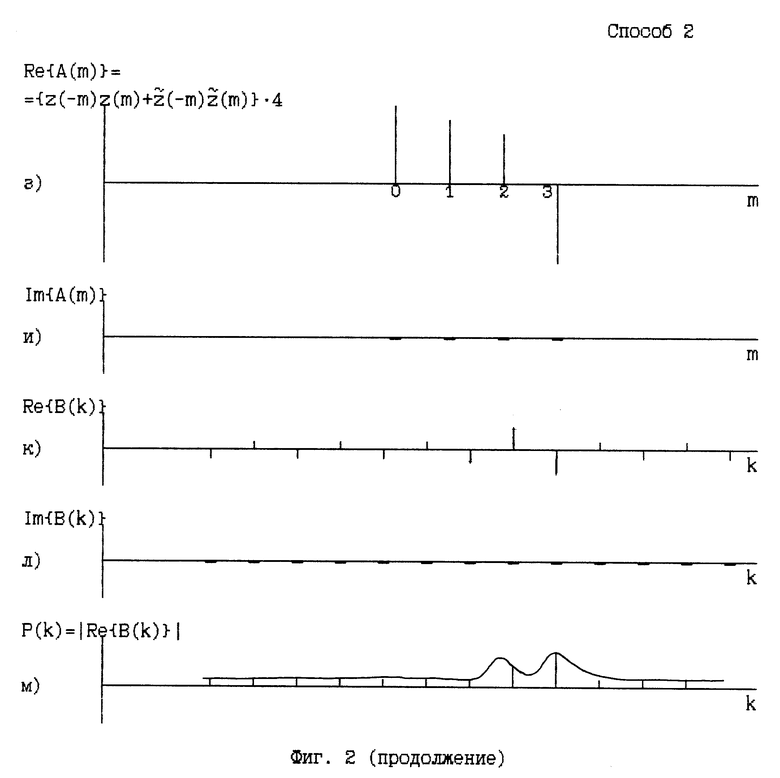

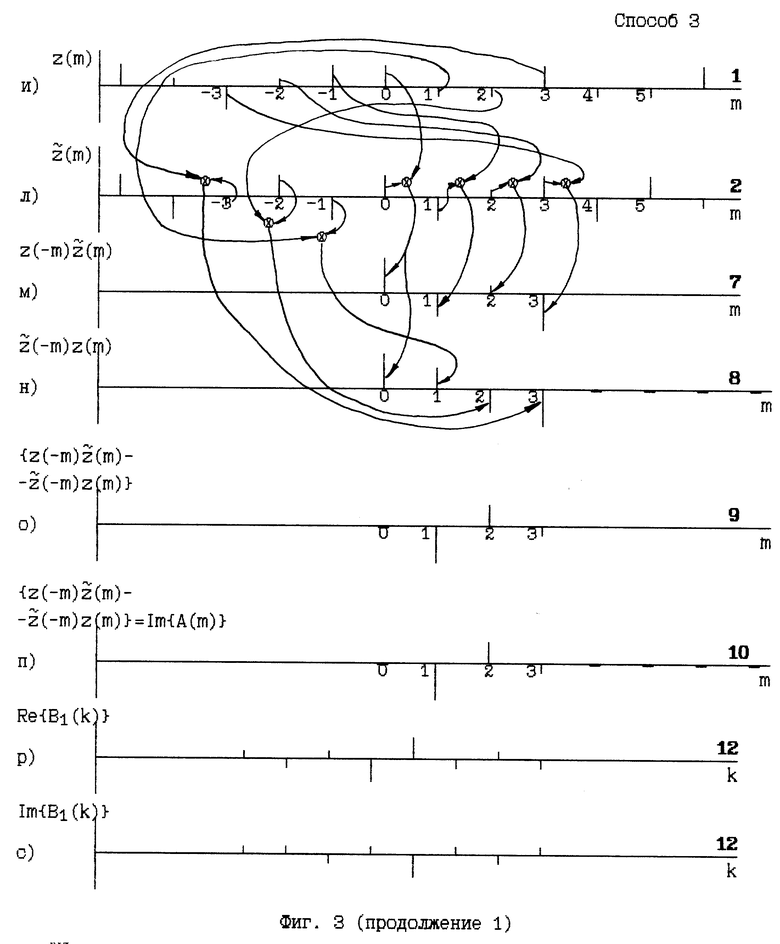

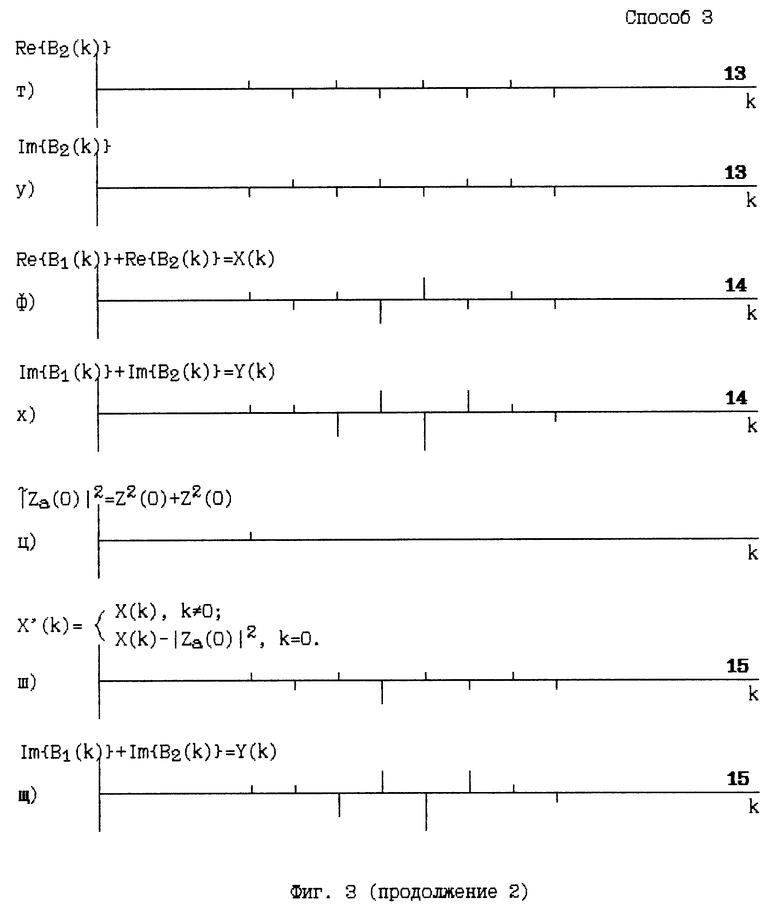

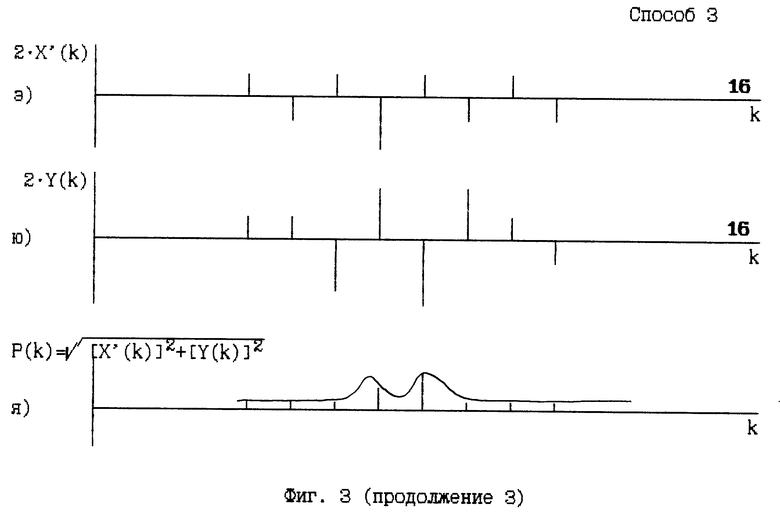

на фиг. 3 на 4-х листах приведены рисунки, поясняющие сущность заявленного третьего варианта способа оценивания несущей частоты сигнала;

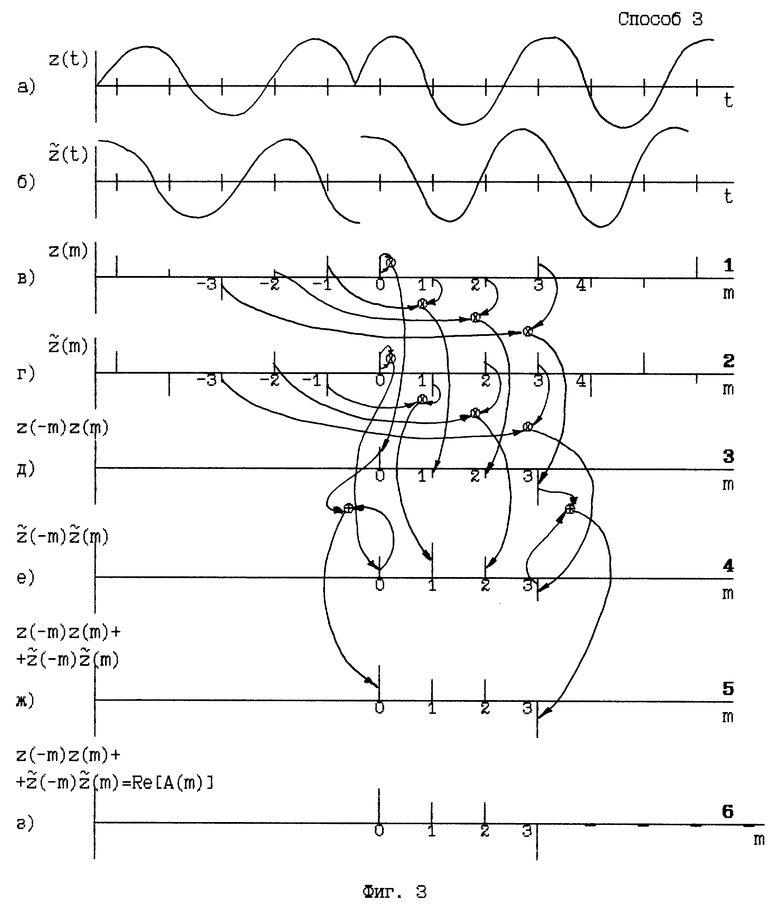

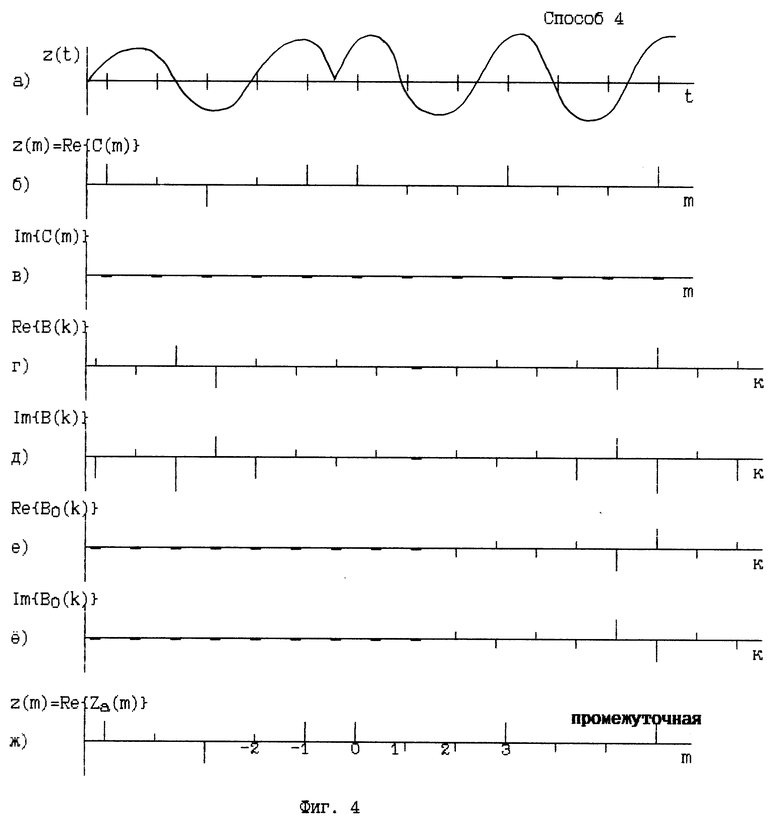

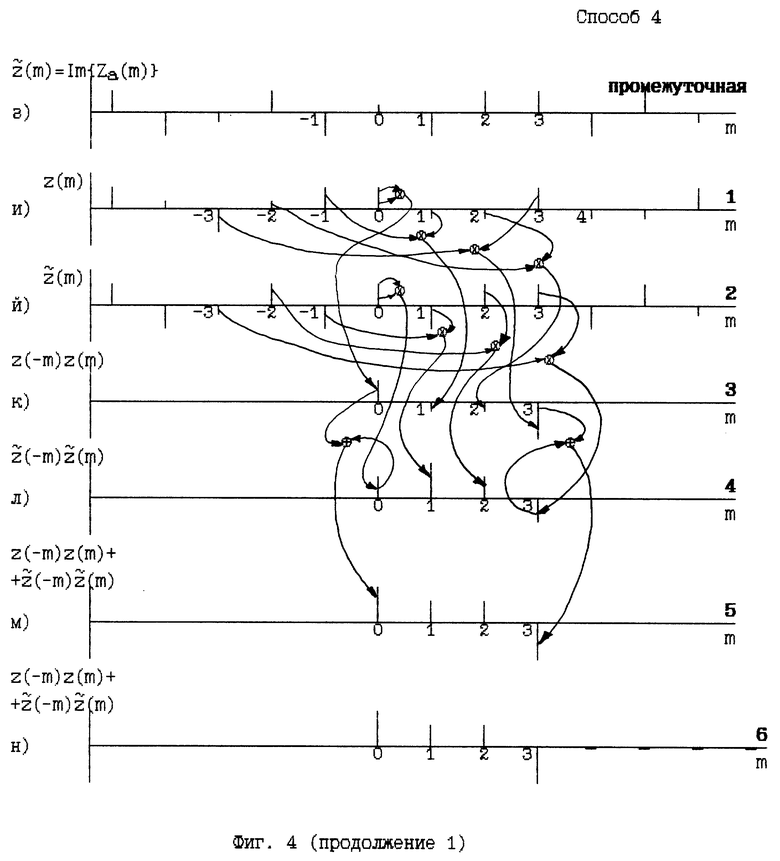

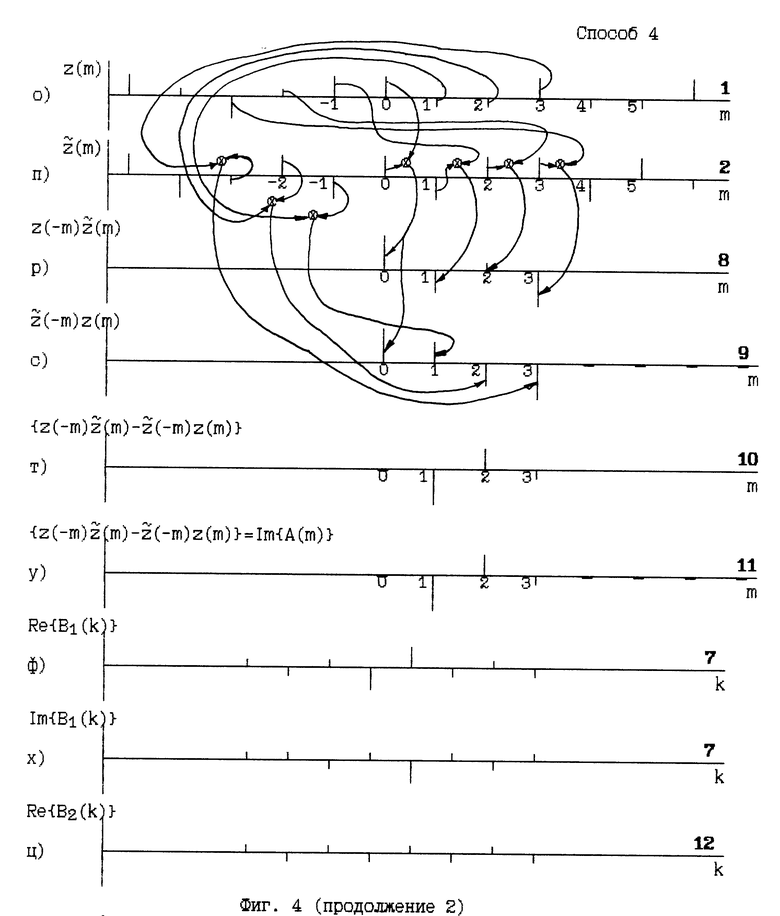

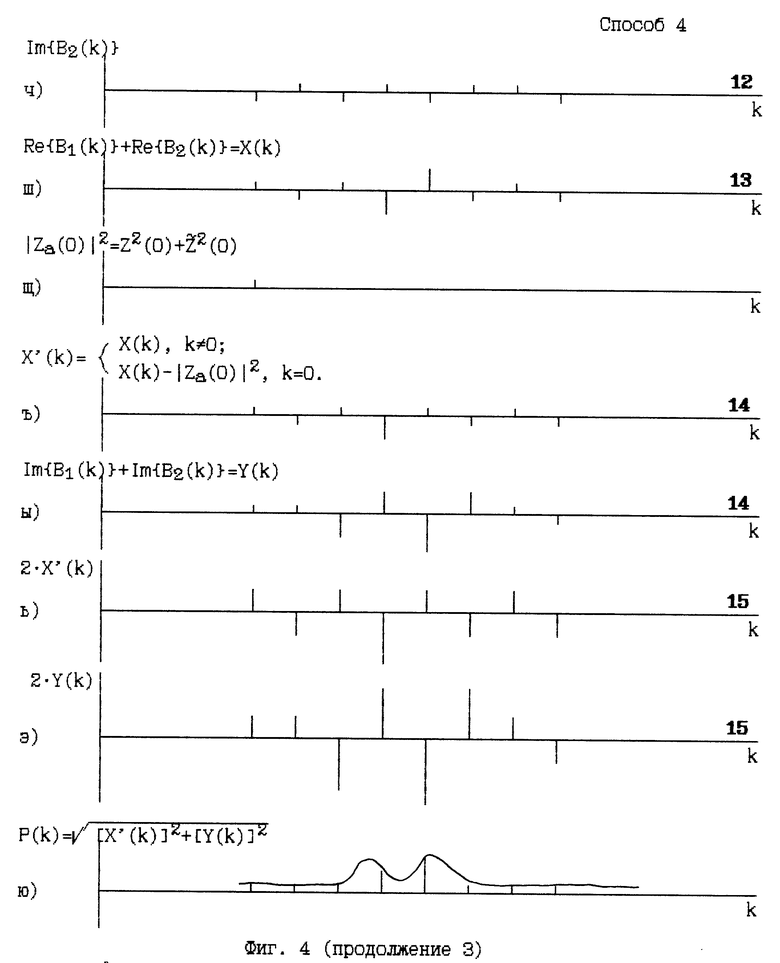

на фиг. 4 на 4-х листах приведены рисунки, поясняющие сущность заявленного четвертого варианта способа оценивания несущей частоты сигнала;

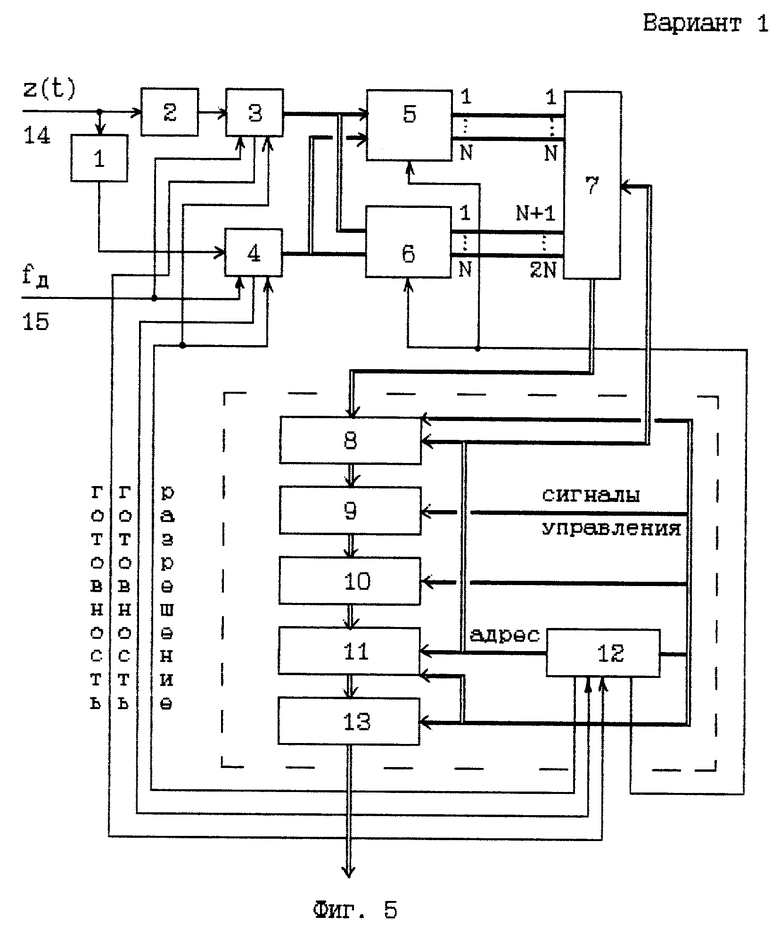

на фиг. 5 приведена общая структурная схема заявленного первого варианта устройства оценивания несущей частоты, реализующего первый вариант способа оценивания несущей частоты сигнала;

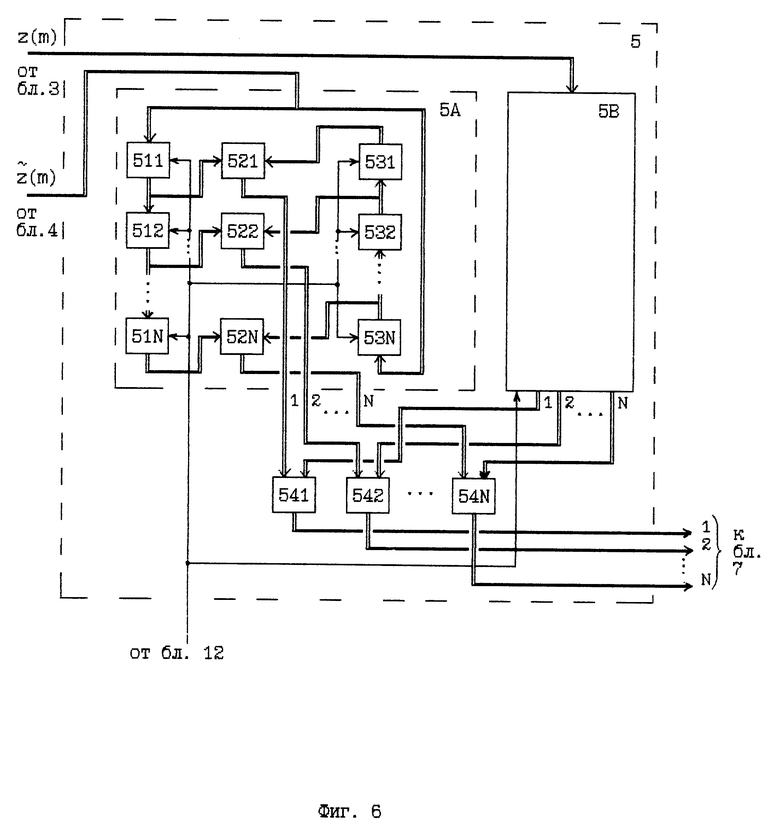

на фиг. 6 приведена схема реализации первого блока преобразования сигнала;

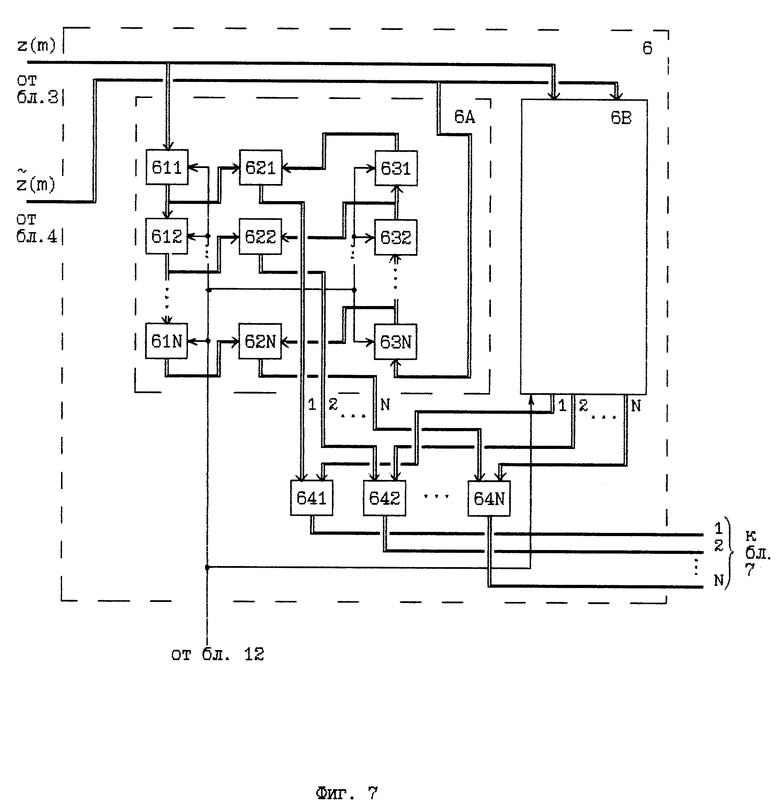

на фиг. 7 приведена схема реализации второго блока преобразования сигнала;

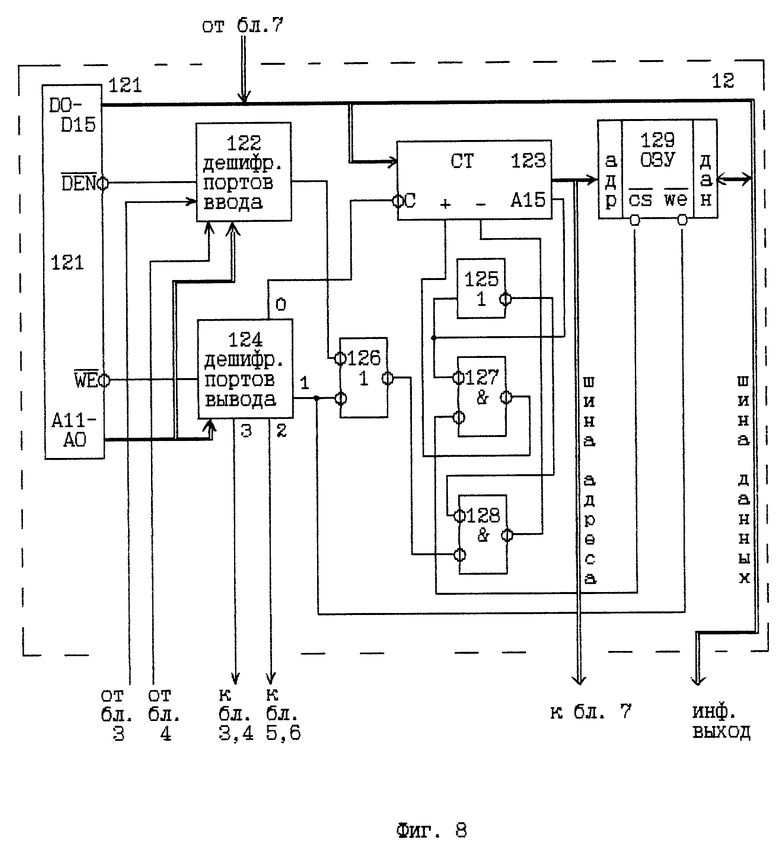

на фиг. 8 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 5 пунктирной линией;

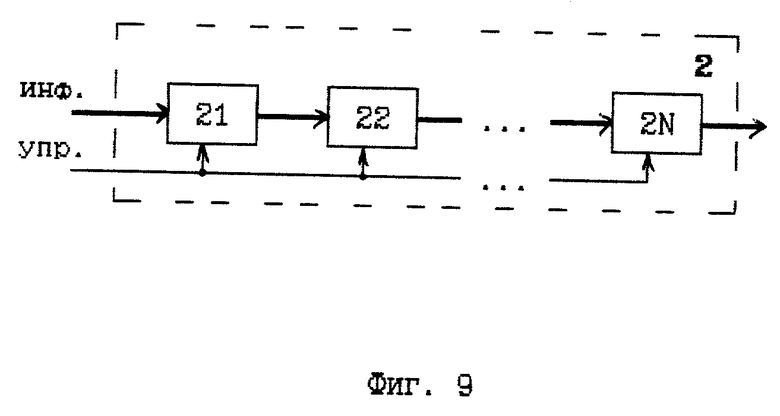

на фиг. 9 приведена структурная схема линии задержки;

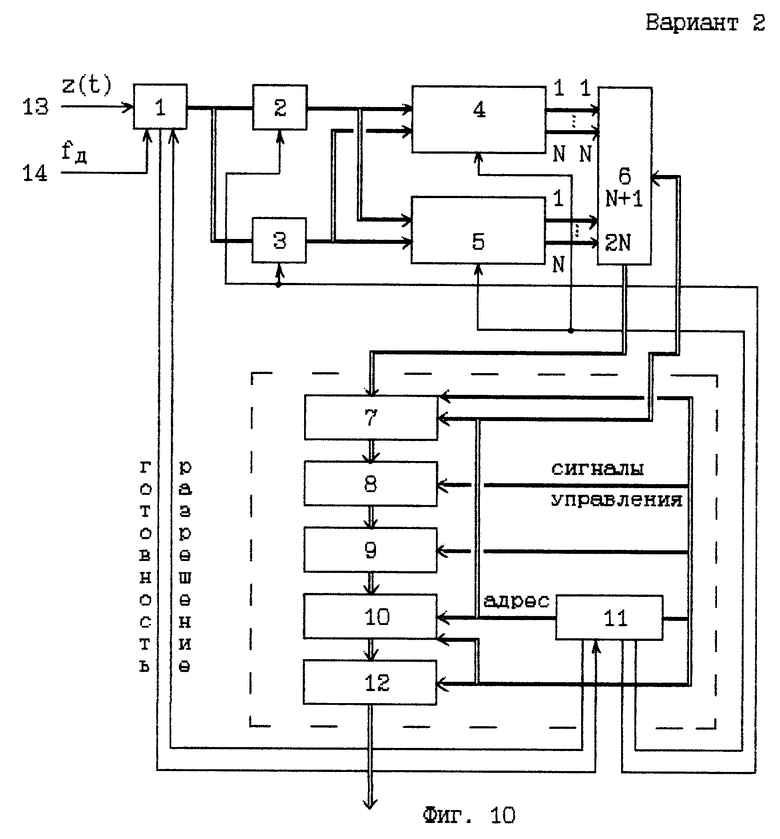

на фиг. 10 приведена общая структурная схема заявленного второго варианта устройства оценивания несущей частоты, реализующего первый вариант способа оценивания несущей частоты сигнала;

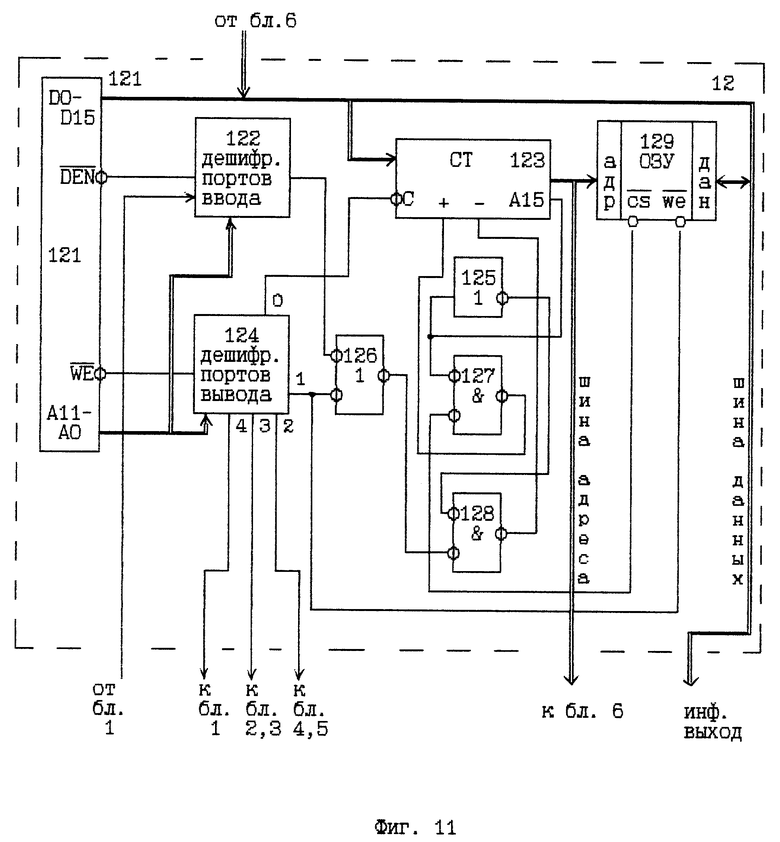

на фиг. 11 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 10 пунктирной линией;

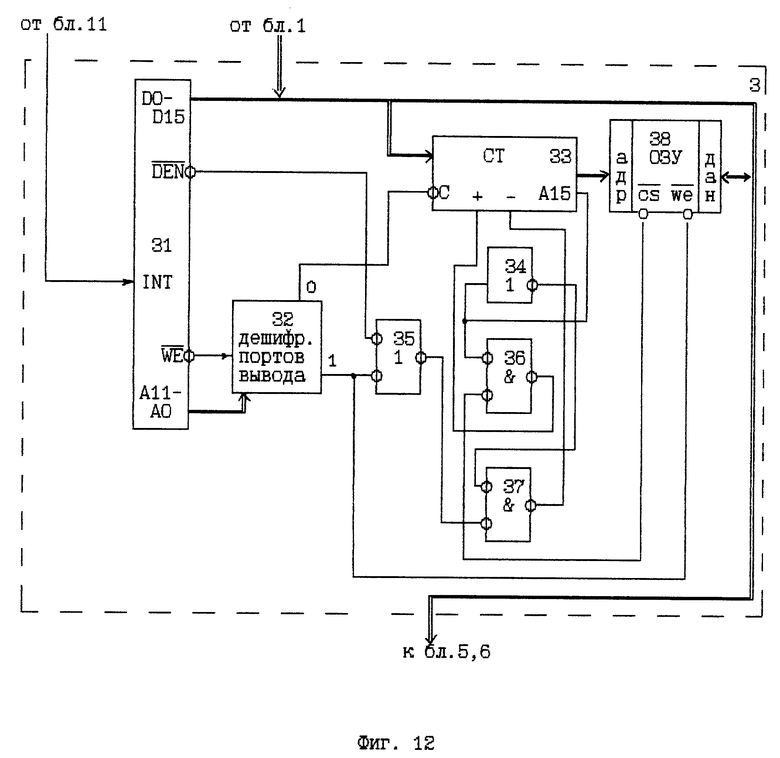

на фиг. 12 приведена структурная схема блока преобразования по Гильберту;

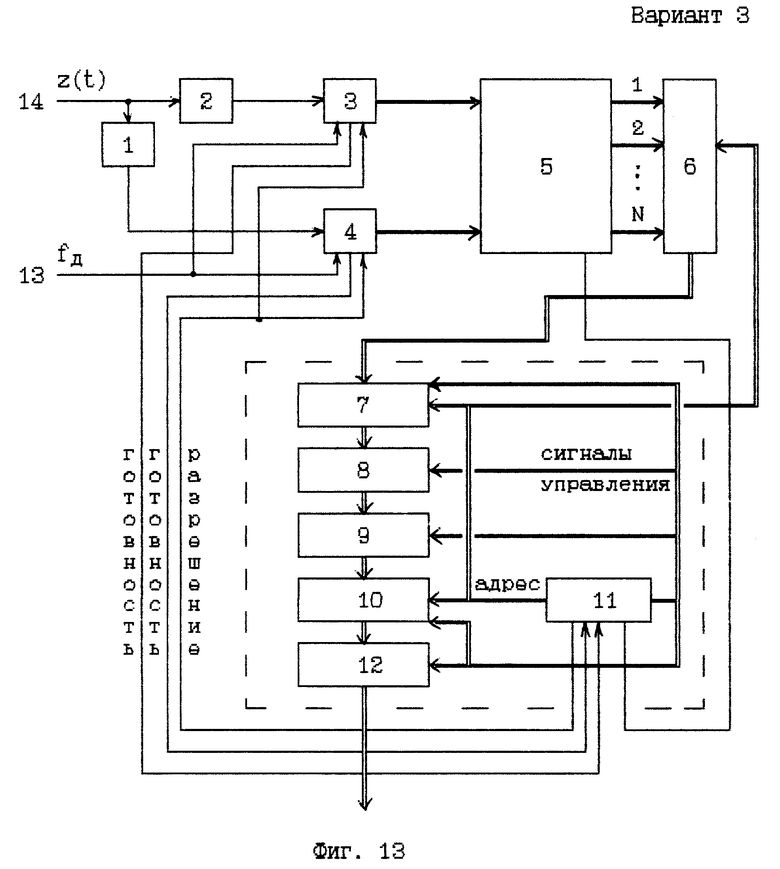

на фиг. 13 приведена общая структурная схема заявленного третьего варианта устройства оценивания несущей частоты, реализующего второй вариант способа оценивания несущей частоты сигнала;

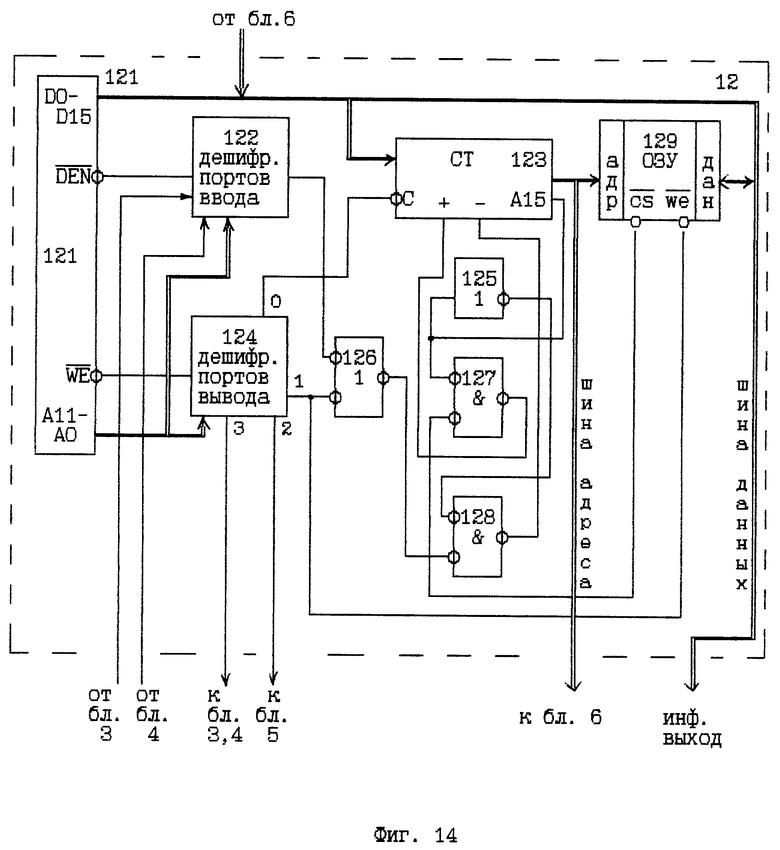

на фиг. 14 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 13 пунктирной линией;

на фиг. 15 приведена общая структурная схема заявленного четвертого варианта устройства оценивания несущей частоты, реализующего второй вариант способа оценивания несущей частоты сигнала;

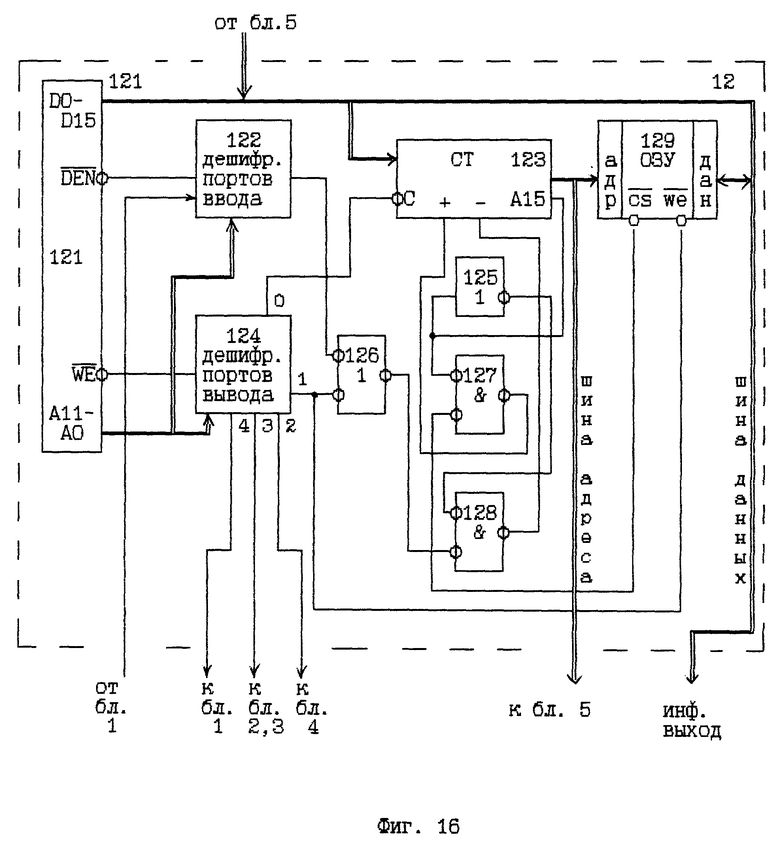

на фиг. 16 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 15 пунктирной линией;

на фиг. 17 приведена общая структурная схема заявленного пятого варианта устройства оценивания несущей частоты, реализующего третий вариант способа оценивания несущей частоты сигнала;

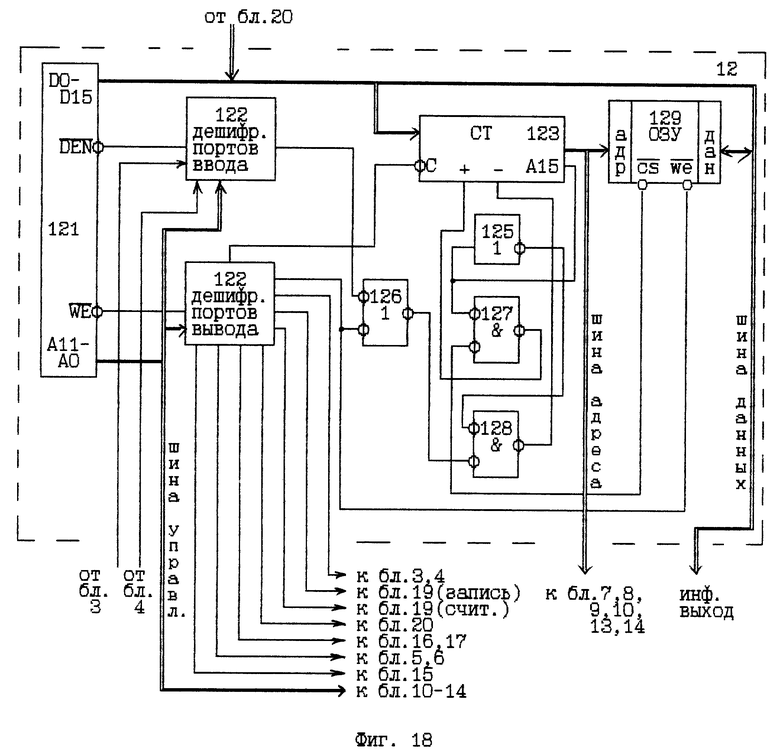

на фиг. 18 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 17 пунктирной линией;

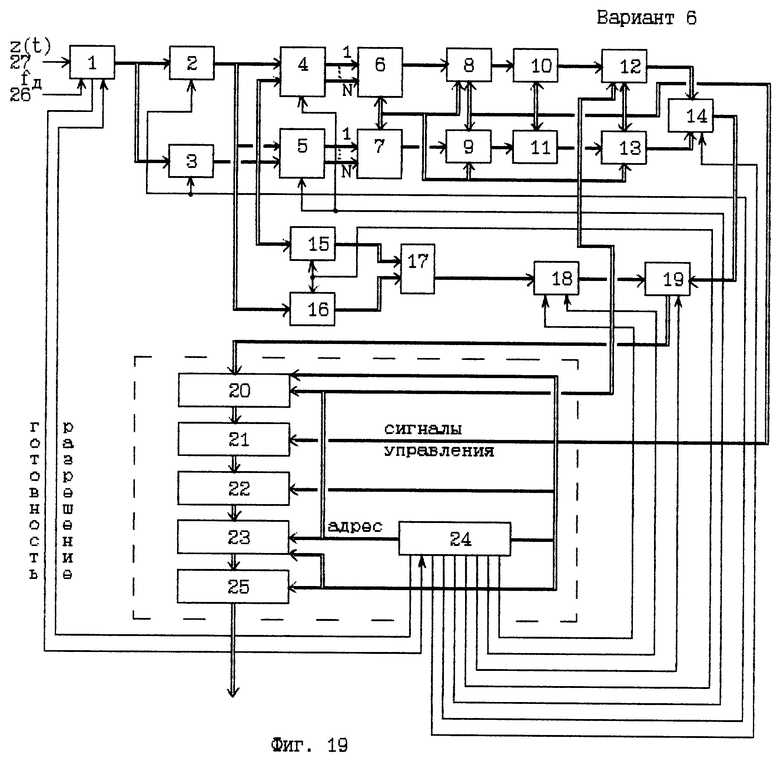

на фиг. 19 приведена общая структурная схема заявленного шестого варианта устройства оценивания несущей частоты, реализующего третий вариант способа оценивания несущей частоты сигнала;

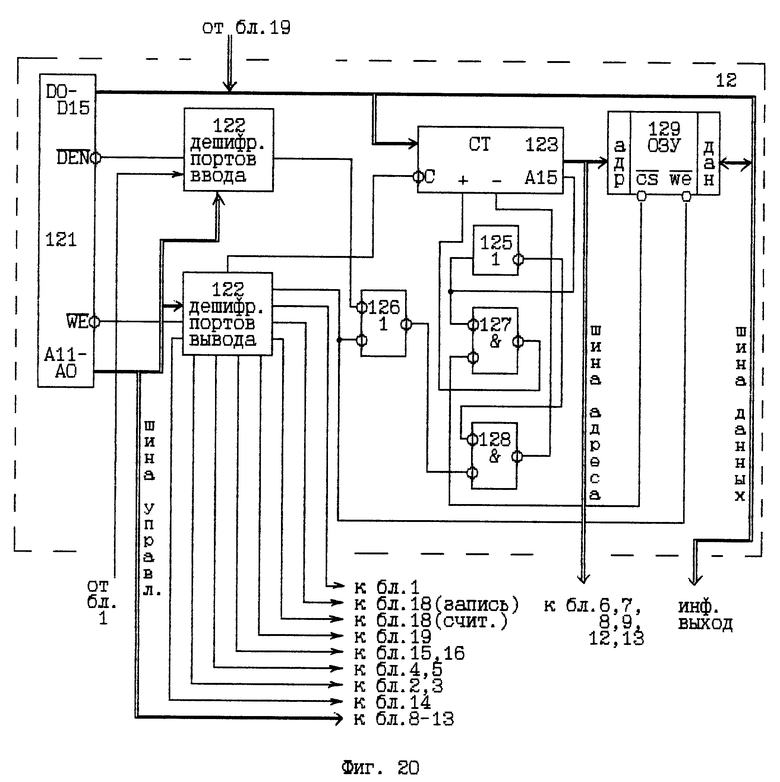

на фиг. 20 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 19 пунктирной линией;

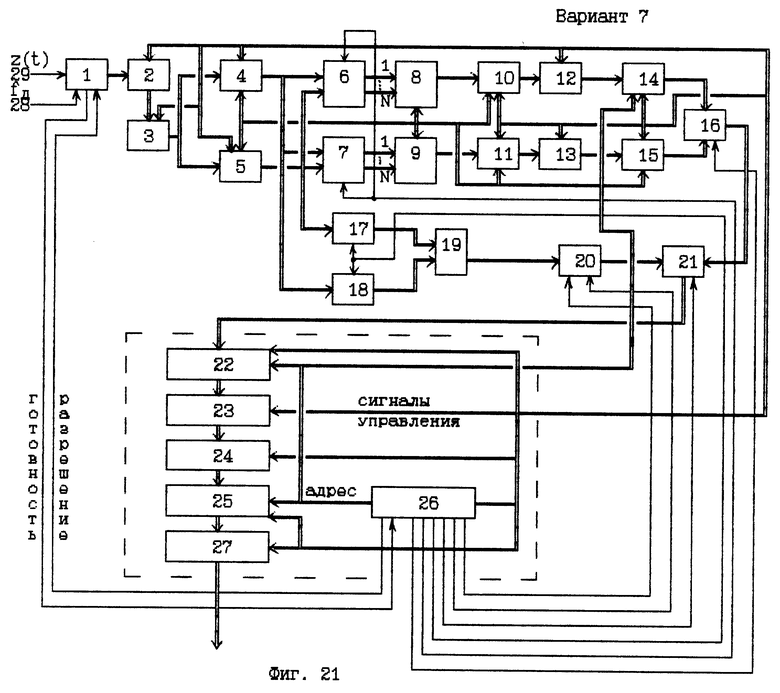

на фиг. 21 приведена общая структурная схема заявленного седьмого варианта устройства оценивания несущей частоты, реализующего четвертый вариант способа оценивания несущей частоты сигнала;

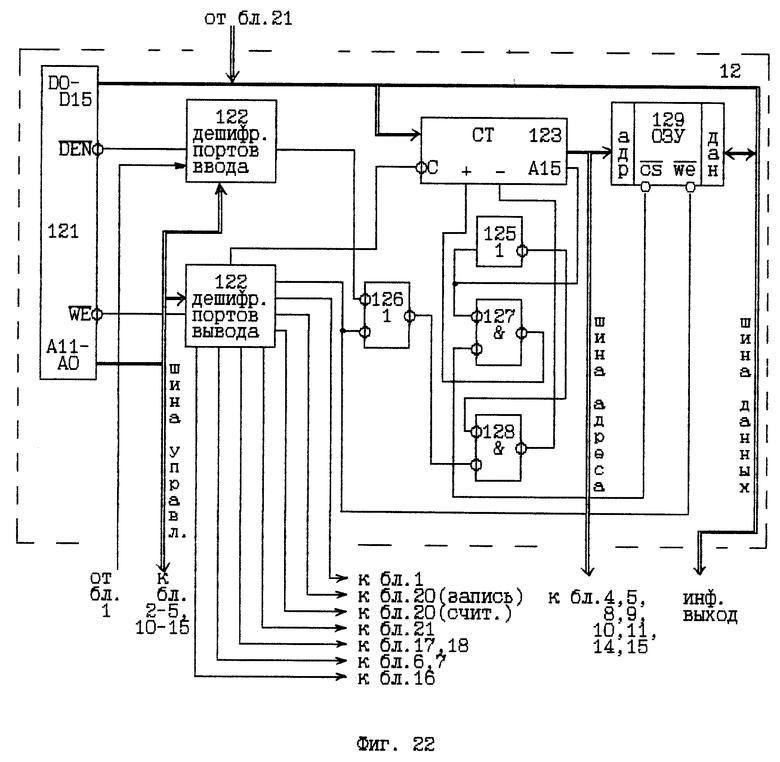

на фиг. 22 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 21 пунктирной линией;

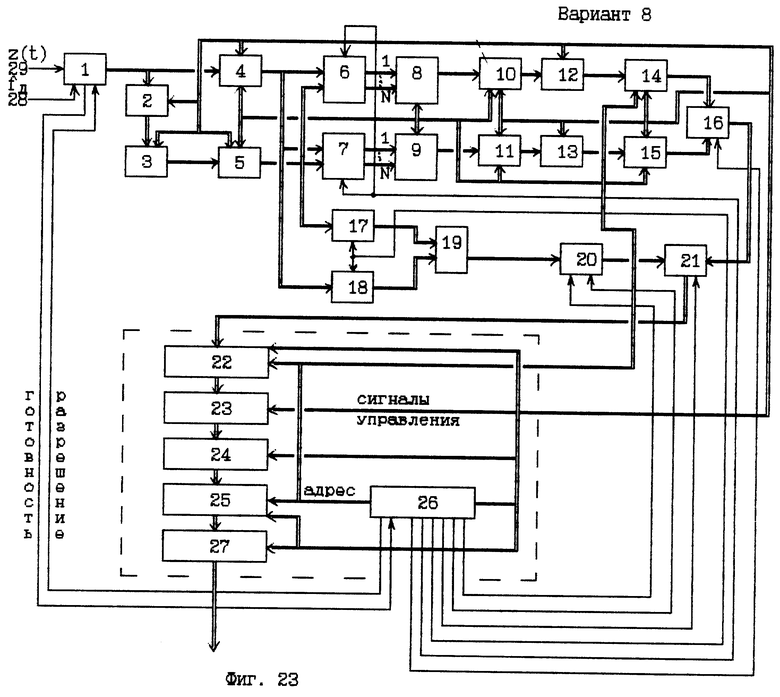

на фиг. 23 приведена общая структурная схема заявленного восьмого варианта устройства оценивания несущей частоты, реализующего четвертый вариант способа оценивания несущей частоты сигнала;

на фиг. 24 приведена структурная схема устройства, реализующего блоки, выделенные на фиг. 23 пунктирной линией;

Реализация заявленного способа (варианты) оценивания несущей частоты сигнала объясняется следующим образом (соответственно фиг. 1, 2, 3, 4).

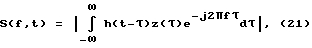

Известны измерители частоты сигналов, базирующиеся на использовании преобразования Фурье вида

где h((t- τ ) - весовая функция, которая часто представляется либо прямоугольным импульсом заданной длительности Т или гауссовой функцией длительностью Т на уровне 0,606, f - частота, t - время.

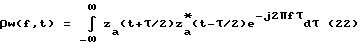

Главный недостаток измерителей частоты, основанных на (21), заключается в том, что длительность весовой функции должна быть соизмеримой с периодом возможных изменений спектральной структуры оцениваемого процесса. Следовательно, в зависимости от класса обрабатываемых процессов необходима оперативная подстройка измерителя под соответствующий процесс, что наталкивается на серьезные технологические проблемы изменения элементов соответствующей фильтровой системы. С этой точки зрения переход на методы цифровой обработки сигналов (ЦОС) позволяет проще адаптироваться к условиям сигнальной обстановки, что и сделано в прототипе. Однако при увеличении скорости измерения спектральной структуры сигналов уменьшение периода измерений (что наблюдается в прототипе) приводит к естественному ухудшению разрешающей способности по частоте. Для преодоления указанного недостатка предлагается отказаться от фильтровых методов и перейти к интерференционным. Для этих целей воспользуемся известным распределением Вигнера [Коэн Л. Время-частотные преобразования: Обзор //ТИИЭР, 1989, т.77, N 10, -с. 72-120]

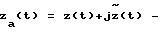

где  аналитический сигнал,

аналитический сигнал,  сигнал, преобразованный по Гильберту, Z

сигнал, преобразованный по Гильберту, Z

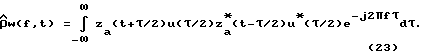

Как видно, в основе выражения (22), также как и в выражении (21), находится преобразование Фурье. Главный недостаток здесь заключается в том, что выражение (22) неприспособлено для обработки непрерывных излучений. Поэтому воспользуемся псевдораспределением Вигнера, записанным в форме [Claaser T.A. C. M. , Mecklenbrauker W.F.G. The Wigner distrihition - a tool for time-frequency signal analisis. Part 1, 2, 3. //Philips J.Res., 1980, Vol. 35, N 3, 4/5, 6- p. 217-250, 276-300, 372-389]

где u(τ/2) - весовая функция анализа.

Псевдораспределение Вигнера вида (23) будет давать лучшие результаты при оценивании несущей частоты, в том числе в случаях, когда сигналы формируются из фрагментов отрезков синусоид (к ним относятся сигналы с фазовой манипуляцией несущей частоты). Действительно, сопоставительный анализ выражений (21) и (23) позволяет рассматривать их как свертку сигнала z(t) с некоторыми функциями. В первом случае эти функции являются откликами фильтров с заданными параметрами средней частоты и полосы пропускания, форма АЧХ и ФЧХ которых не меняется в процессе обработки. Во втором (предлагаемом) случае отклики "условных" фильтров определяются отрабатываемой реализацией сигнала (в выражении (23) осуществляется свертка сигнала с его копией, претерпевающей соответствующие частотные и фазовые сдвиги), т.е. реализуется процедура согласованного приема в каждый момент времени на частоте реализации сигнала. Параметры "условных" фильтров адаптивны к входящему процессу таким образом, что условия согласованного приема для принимаемой реализации сигнала выполняются для соответствующего значения ее мгновенной частоты. Очевидно, что энергетика спектра Вигнера в этом случае будет лучше, чем простого преобразования Фурье. Этот спектр более рельефен, что позволяет более точно оценивать несущую частоту сигнала при более низких отношениях сигнал/шум. Об этом свидетельствуют, в частности, исследования, приведенные в:

[Алексеев А. А. , Чеченов С.Ю., Кириллов А.Б. Анализ сигналов на основе функций распределений мощности в условиях многосигнального воздействия // Радиотехника. - 1993. - N 10-12. - С. 32-37];

[Алексеев А.А., Аладинский В.А., Чеченев С.Ю. Функции распределения мощности сигналов и обобщение понятий теории цепей и радиотехники // Радиотехника. - 1991. - N 11. - С. 62-63];

[Алексеев А.А., Аладинский В.А. Алгоритм фильтрации параметров сигналов на основе частотно-временных распределений мощности // Радиоэлектроника (Изв. высш. учебн. заведений). - 1989. -Т. 32. - N 3.- С. 3-6].

Поясним суть предлагаемого способа.

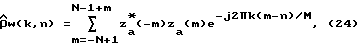

Для этого представим выражение (23) в дискретной форме из предположения прямоугольной функции окна длиной N:

где M≥2N-1.

Остановимся на реализации первого варианта способа.

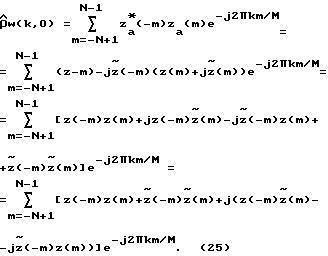

При n=0:

Реализация выражения (25) поясняется фиг. 1.

Сигнал, изображенный на фиг. 1а, и сдвинутый по Гильберту [Л. Рабинер, Б. Гоулд. Теория и применение цифровой обработки сигналов. -М.: Мир, 1978, -с. 81-88.], приведенный на фиг. 1б, дискретизируют соответственно в первую (фиг. 1в) и вторую (фиг. 1г) последовательности (номера последовательностей справа). Затем формируют третью и четвертую последовательности путем выполнения умножений в первой и второй последовательностях (фиг. 1д, е).

Затем полученные произведения складывают поэлементно, так что (-3)-й элемент третьей последовательности складывают с (-3)-им элементом четвертой последовательности, (-2)-й элемент третьей последовательности складывают с (-2)-ым элементом четвертой последовательности и т.д. Так формируется пятая последовательность, приведенная на фиг. 1ж.

Одновременно элементы первой последовательности (фиг. 18) умножаются на элементы второй последовательности (фиг. 1и), образуя шестую последовательность, приведенную на фиг. 1к, а элементы второй последовательности умножаются на элементы первой последовательности, образуя седьмую последовательность (фиг. 1л).

Затем из дискретных отсчетов шестой последовательности поэлементно вычитаются дискретные отсчеты седьмой последовательности так, что из значения (-3)-го дискретного отсчета шестой последовательности вычитают значение (-3)-го дискретного отсчета седьмой последовательности, а значения (-2)-го дискретного отсчета шестой последовательности вычитают значения (-2)-го дискретного отсчета седьмой последовательности и т.д. При этом формируется (-3)-й, (-2)-й, ... дискретный отсчет восьмой последовательности, показанный на фиг. 1м.

Дискретные отсчеты пятой и восьмой последовательностей образуют единую комплексную последовательность A (m), над которой производят дискретное преобразование Фурье [Л. Рабинер, Б. Гоулд. Теория и применение цифровой обработки сигналов. -М.: Мир, 1978, -с. 62-72.]. Результатом этого преобразования является комплексная последовательность B(k) (фиг. 1н, о), из которой определяют спектр мощности (фиг. 1н). Далее рассчитывают несущую частоту так же, как и в прототипе.

Поясним особенности второго варианта способа оценивания несущей частоты.

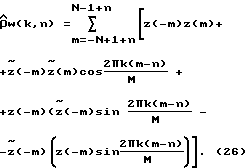

По определению распределение Вигнера - действительная функция [Claaser T. A.C.M., Mecklenbrauker W.F.G. The Wigner distrihition - a tool for time-frequency signal analisis. Part 1, 2, 3. //Philips J.Res., 1980, Vol. 35, N 3, 4/5, 6 - p. 217-250, 276-300, 372-389]. Поэтому его можно преобразовать, если взять реальную часть от выражения (24), к виду

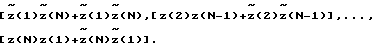

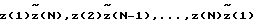

Воспользовавшись известными свойствами преобразования Гильберта [Трахман А. М. Введение в обобщенную спектральную теорию сигналов. -М.: Советское радио, 1972] , а также свойствами симметрии относительно m=0 функций z (-m)z(m) и  можно получить выражение

можно получить выражение

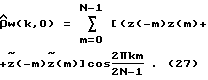

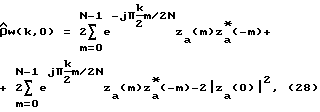

а при n=0 (27)

(27)

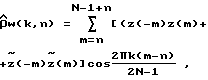

Следовательно, для вычисления псевдораспределения Вигнера необходимо вычислить дискретное косинусное преобразование Фурье [Методы передачи изображений. Сокращение избыточности /Под ред. У. К. Претта. -М.: Радио и связь, 1983, - 264 с; Киволовиц П. Сжатие изображений по стандарту JPEG //Мир ПК. , 1992, N 4, - с. 46-51; Ахмед Н., Рао И.Р. Ортогональные преобразования при обработке цифровых сигналов. - М.: Связь, 1980, - 248 с.] последовательности данных, полученных из исходного сигнала в соответствии с выражением в квадратных скобках формулы (27).

Последовательность действий демонстрируется на фиг. 2. Здесь из первой и второй последовательностей (фиг. 2в, г) формируют произведения R1 и R2 (фиг. 2д, е). При этом 0-й элемент R1 есть результат умножения 0-го дискретного отсчета первой последовательности на 0-й элемент этой же последовательности первый элемент R1 является результатом умножения 1-го и (-1)-го дискретного отсчетов первой последовательности и т. д. 0-й элемент R2 есть результат зультат умножения самого на себя 0-го элемента второй последовательности, 1-й элемент R2 является результатом умножения 1-го и (-1)-го элемента второй последовательности и т.д.

Затем R1 и R2 поэлементно суммируют (фиг. 2ж) и умножают на 4 (фиг. 2з). Над полученной комплексной последовательностью A (m) выполняют дискретное косинусное преобразование, получая последовательность B(k), приведенную на фиг. 2к, л, а из последней получают спектр мощности путем определения модуля реальной части B(k).

Рассмотрим особенности третьего варианта оценивания несущей частоты.

Преобразуем выражение (24) следующим образом:

где M=2N.

Формирование пятой и девятой последовательностей (фиг. 3ж, п) происходит подобным образом, как и пятой и восьмой последовательностей первого варианта (фиг. 1ж, м). Особенность в том, что, так как предел изменения m лежит от нуля до N-1, то количество дискретных отсчетов в пятой и девятой последовательностях меньше для данного варианта. Поэтому для формирования последовательности A(m), приведенной на фиг. 3з, п, пятую и девятую последовательности дополняют нулями. Затем над одиннадцатой последовательностью A(m)= P6(i)+j•P10(i) выполняют прямое быстрое преобразование Фурье, получая соответственно двенадцатую B1(k) и тринадцатую B2(k) последовательности дискретных отсчетов (фиг. 3р, с, т, у). После этого реальные части последовательностей дискретных отсчетов B1(k) и B2(k) поэлементно складывают и мнимые части этих последовательностей поэлементно складывают. Результатом является четырнадцатая последовательность дискретных отсчетов, приведенная на фиг. 3ф, х. После вычитания из реальной части четырнадцатой последовательности в точке k=0 величины  получаем пятнадцатую последовательность дискретных отсчетов (фиг. 3ш, щ). Последнюю последовательность умножают на нормирующий множитель для получения шестнадцатой последовательности, а затем вычисляют спектр мощности.

получаем пятнадцатую последовательность дискретных отсчетов (фиг. 3ш, щ). Последнюю последовательность умножают на нормирующий множитель для получения шестнадцатой последовательности, а затем вычисляют спектр мощности.

Рассмотрим особенности четвертого варианта оценивания несущей частоты.

Отличие от третьего варианта оценивания несущей частоты заключается в том, что здесь не используется преобразование Гильберта. Сдвинутый по Гильберту [Improved Time-Freqency Representation of Multicomponent Signals Using Exponential Kernels. HYUNG-iee CHOi and Wielian J. Wieliaun IEE Transactions on cecoustics speechand signal processing, 1989, Vol. 37, N 6,-p. 868] сигнал получают из несдвинутого. Для этого исходный сигнал дискретизируют, затем выполняют на ним быстрое преобразование Фурье (фиг. 4г, д). Затем значение спектральных составляющих на частотах меньших нуля обнуляют (фиг. 4е, е), получая последовательность B0(k) и над ней выполняют быстрое преобразование Фурье. Получают промежуточную последовательность (фиг. 4ж, з), реальная часть которой есть дискретный сигнал (первая последовательность), а мнимая часть - сдвинутая по Гильберту последовательность дискретных отсчетов (вторая последовательность). Дальнейшая последовательность действий аналогична изложенной в третьем варианте оценивания несущей частоты.

Устройство оценивания несущей частоты (первый вариант).

Первый вариант устройства оценивания несущей частоты, реализующего первый вариант способа оценивания несущей частоты сигнала, показанный на фиг. 5, состоит из фазовращателя 1, линии задержки 2, первого 3 и второго 4 аналого-цифровых преобразователей, первого 5 и второго 6 блоков преобразования сигнала, коммутатора 7, первого 8 и второго 11 блоков памяти, блока преобразования Фурье и определения спектральной плотности мощности 9, блока фильтров 10, блока управления 12 и блока определения частоты 13. Выходы блока определения частоты 13 являются информационными выходами устройства оценивания несущей частоты. Группа адресных выходов блока управления 12 соединена с группами адресных входов первого 8 и второго 11 блоков памяти. Первая группа управляющих выходов блока управления 12 соединена с группами управляющих входов первого 8 и второго 11 блоков памяти, блока преобразования Фурье и определения спектральной плотности мощности 9, блока фильтров 10 и блока определения частоты 13. Информационные входы фазовращателя 1 и линии задержки 2 объединены и соединены с информационным входом 14 устройства оценивания несущей частоты. Информационный вход первого аналого-цифрового преобразователя 3 соединен с выходом линии задержки 2. Тактовый вход первого аналого-цифрового преобразователя 3 объединен с тактовым входом второго аналого-цифрового преобразователя 4 и соединен с тактовым входом 15 устройства оценивания несущей частоты. Вход разрешения первого аналого-цифрового преобразователя 3 объединен с входом разрешения второго аналого-цифрового преобразователя 4 и выходом разрешения блока управления 12. Выход готовности первого аналого-цифрового преобразователя 3 соединен с первым входом готовности блока управления 12. Второй вход готовности блока управления 12 соединен с выходом готовности второго аналого-цифрового преобразователя 4. Информационный вход второго аналого-цифрового преобразователя 4 соединен с выходами фазовращателя 1. Информационные выходы второго аналого-цифрового преобразователя 4 соединены со вторыми группами информационных входов первого 5 и второго 6 блоков преобразования сигналов. Первые группы информационных входов первого 5 и второго 6 блоков преобразования сигналов соединены с информационными выходами первого аналого-цифрового преобразователя 3. N групп информационных выходов каждого блока преобразования сигнала соединены соответственно с первой по N и с N+1 по 2N группами информационных входов коммутатора 7. Информационные выходы коммутатора 7 соединены с информационными входами первого блока памяти 8. Адресные входы коммутатора 7 соединены с адресными выходами блока управления 12. Второй управляющий выход блока управления 12 соединен с входами управления первого 5 и второго 6 блоков преобразования сигнала.

Первый блок преобразования сигнала 5, показанный на фиг. 6, состоит из двух 5A и 5B идентичных трактов обработки, N сумматоров 541, 542, ..., 54N, двух групп из N регистров 511, 512, ..., 51N, 531, 532, ..., 53N и N умножителей 521, 522, ..., 52N. Первая и вторая группы информационных входов первого блока преобразования сигнала 5 соединены с информационными входами соответственно первого 5A и второго 5B трактов обработки, управляющие входы которых объединены и соединены с управляющим входом первого блока преобразования сигнала 5. N групп выходов первого тракта 5A обработки соединены соответственно с первыми группами входов N сумматоров 541, 542, ..., 54N, вторые группы входов которых соединены с соответствующими N группами выходов второго тракта обработки 5В. Группы выходов N сумматоров 541, 542, ..., 54N являются N группами информационных выходов первого блока преобразования сигнала 5. Информационные входы первого регистра 511 первой группы регистров объединены с информационными входами N-го регистра 53N второй группы регистров и соединены с группой информационных входов соответствующего тракта обработки. Выходы регистров первой группы 511, 512, ..., 51N соединены с первыми группами входов соответствующих умножителей 521, 522, ..., 52N. Выходы регистров второй группы 531, 532, ..., 53N соединены со вторыми группами входов умножителей 521, 522, ..., 52N в обратном порядке. Выходы умножителей 521, 522, . . ., 52N являются соответствующей группой выходов тракта обработки. Управляющий вход тракта обработки соединен с управляющими входами всех регистров первой 511, 512, ...,51N и второй 531, 532, ..., 53N групп регистров.

Второй блок преобразования сигнала 6, показанный на фиг. 7, состоит из двух 6A и 6B идентичных трактов обработки, N блоков вычитания 641, 642, ..., 64N, двух групп из N регистров 611, 612, ..., 61N, 631, 632, ..., 63N и N умножителей 621, 622, ..., 62N. Первые группы информационных входов первого 6A и второго 6B трактов обработки объединены и соединены с первой группой информационных входов второго блока преобразования сигнала 6. Вторые группы информационных входов первого 6A и второго 6B трактов объединены и соединены со второй группой информационных входов второго блока преобразования сигнала 6. Управляющие входы первого 6A и второго 6B трактов обработки объединены и соединены с входом управления второго блока преобразования сигнала 6. N групп выходов первого тракта обработки 6A соединены со входами уменьшаемого соответствующих N блоков вычитания 641, 642, . . ., 64N, группы входов вычитаемого которых соединены с соответствующими выходами второго тракта обработки 6В. Группы выходов N блоков вычитания 641, 642, ..., 64N являются N группами информационных выходов второго блока преобразования сигнала 6. Информационные входы первого регистра 611 первой группы регистров объединены с первой группой информационных входов тракта обработки. Информационные входы N-го регистра 63N второй группы регистров объединены со второй группой информационных входов тракта обработки. Выходы регистров первой группы 611, 612, . . . , 61N соединены с первыми группами входов соответствующих умножителей 621, 622, ..... 62N. Выходы регистров второй группы 631, 632, ..., 63N соединены с вторыми группами входов соответствующих умножителей 621, 622, ..., 62N. Выходы умножителей 621, 622, ..., 62N являются соответствующими группами выходов тракта обработки. Управляющий вход тракта обработки соединен с управляющими входами всех регистров первой 611, 612, ..., 61N и второй 631, 632, ..., 63N групп регистров.

Устройство оценивания несущей частоты (второй вариант).

Второй вариант устройства оценивания несущей частоты, реализующего первый вариант способа оценивания несущей частоты сигнала, показанный на фиг. 10, состоит из аналого-цифровой преобразователя 1, линии задержки 2, блока преобразования по Гильберту 3, первого 4 и второго 5 блоков преобразования сигнала, коммутатора 6. первого 7 и второго 10 блоков памяти, блока преобразования Фурье и определения спектральной плотности мощности 8, блока фильтров 9, блока управления 11 и блока определения частоты 12. Выходы блока определения частоты 12 являются информационными выходами устройства оценивания несущей частоты. Группа адресных выходов блока управления 11 соединена с группами адресных входов первого 7 и второго 10 блоков памяти. Первая группа управляющих выходов блока управления соединена с группами управляющих входов первого блока памяти 7, блока преобразования Фурье и определения спектральной плотности мощности 8, блока фильтров 9, второго блока памяти 10 и блока определения частоты 12. Информационный вход аналого-цифрового преобразователя 1 соединен с информационным входом 13 устройства оценивания несущей частоты. Тактовый вход аналого-цифрового преобразователя 1 соединен с тактовым входом 14 устройства оценивания несущей частоты. Выход готовности аналого-цифрового преобразователя 1 соединен со входом готовности блока управления 11. Выход разрешения блока управления 11 соединен с входом разрешения аналого-цифрового преобразователя 1. Выходы аналого-цифрового преобразователя 1 соединены с информационными входами блока преобразования по Гильберту 3 и информационными входами линии задержки 2. Выходы линии задержки 2 соединены с первыми группами информационных входов первого 4 и второго 5 блоков преобразования сигнала. Вторые группы информационных входов первого 4 и второго 5 блоков преобразования сигнала соединены с выходами блока преобразования по Гильберту 3. N групп выходов первого блока преобразования сигнала 4 соединены с первой совокупностью из N групп соответствующих информационных входов коммутатора 6. Вторая совокупность из N групп информационных входов коммутатора 6 соединена с N соответствующими группами выходов второго блока преобразования сигнала 5. Управляющий вход второго блока преобразования сигнала 5 объединен с управляющим входом первого блока преобразования сигнала 4 и вторым управляющим выходом блока управления 11. Третий управляющий выход блока управления 11 соединен с управляющими входами линии задержки 2 и блока преобразования по Гильберту 3. Адресные выходы блока управления 11 соединены с адресными входами коммутатора 6. Выходы коммутатора 6 соединены с информационными входами первого блока памяти 7.

Первый 4 и второй 5 блоки преобразования сигнала (фиг. 8) по своему составу выполнены аналогично рассмотренным в первом заявленном устройстве, соответственно, первому 5 (фиг. 6) и второму 6 (фиг. 7) блокам преобразования сигнала.

Устройство оценивания несущей частоты (третий вариант).

Третий вариант устройства оценивания несущей частоты, реализующего второй вариант способа оценивания несущей частоты сигнала, показанный на фиг. 13, состоит из фазовращателя 1, линия задержки 2, первого 3 и второго 4 аналого-цифровых преобразователей, блока преобразования сигнала 5, коммутатора 6, блока дискретного косинусного преобразования и определения спектральной плотности мощности 8, блока фильтров 9, первого 7 и второго 10 блоков памяти, блока управления 11 и блока определения частоты 12. Выходы блока определения частоты 12 являются информационными выходами устройства оценивания несущей частоты. Управляющие входы устройства оценивания несущей частоты объединены с управляющими входами первого блока памяти 7, блока фильтров 9, второго блока памяти 10 и первой группой управляющих выходов блока управления 11. Группа адресных выходов блока управления 11 соединена с адресными входами первого 7 и второго 10 блоков памяти. Вход фазовращателя 1 объединен со входом линии задержки 2 и соединен с информационным входом 14 устройства оценивания несущей частоты. Выход фазовращателя 1 соединен с информационным входом второго аналого-цифрового преобразователя 4. Тактовый вход второго аналого-цифрового преобразователя 4 объединен с тактовым входом первого аналого-цифрового преобразователя 3 и соединен с тактовым входом 13 устройства оценивания несущей частоты. Выход готовности второго аналого-цифрового преобразователя 4 соединен со вторым входом готовности блока управления 11. Первый вход готовности блока управления 11 соединен с выходом готовности первого аналого-цифрового преобразователя 3. Вход разрешения первого аналого-цифрового преобразователя 3 объединен с входом разрешения второго аналого-цифрового преобразователя 4 и выходом разрешения блока управления 11. Информационные выходы первого аналого-цифрового преобразователя 3 соединены с первой группой информационных входов блока преобразования сигнала 5. Вторая группа информационных входов блока преобразования сигнала 5 соединена с информационными выходами второго аналого-цифрового преобразователя 4. Управляющий вход блока преобразования сигнала 5 соединен с вторым управляющим выходом блока управления 11. N групп выходов блока преобразования сигнала 5 соединены с соответствующими N группами входов коммутатора 6. Адресные входы коммутатора 6 объединены с адресными входами первого блока памяти 7. Информационные выходы коммутатора 6 соединены с информационными входами первого блока памяти 7. Выходы первого блока памяти 7 соединены с информационными входами блока дискретного косинусного преобразования и определения спектральной плотности мощности 8. Управляющие входы блока дискретного косинусного преобразования и определения спектральной плотности мощности 8 соединены с первой группой управляющих выходов блока управления 11, а выходы соединены с информационными входами блока фильтров 9.

Блок преобразования сигнала 5 (фиг. 9) выполнен аналогично первому блоку преобразования сигнала 5 (фиг. 6), рассмотренному в первом варианте заявленного устройства, реализующего первый вариант способа оценивания несущей частоты сигнала.

Устройство оценивания несущей частоты (четвертый вариант).