Данное изобретение относится к выполнению инструкции по обработке данных.

Некоторые процессоры данных содержат центральный процессор (CPU), который способен во время контроля за текущей выполняемой инструкцией по обработке данных обращаться к данным, хранимым в оперативной памяти (RAM), через промежуточное устройство организации памяти. Ранее предложенным примером такого процессора данных является ARM6 процессор, описанный в списке данных ARM6 изданного Advanced Risc Machines Limited, 1993. Во время обращения к памяти, устройство организации памяти может генерировать сигнал прерывания, указывающий, что текущий доступ к памяти не может быть завершен. Прерывающие сигналы могут генерироваться по нескольким причинам. В одном примере прерванный доступ к памяти может возникнуть в системе обработки данных, использующей виртуальную память, в которой данные перекачиваются между RAM и более медленным дисковым носителем, создавая иллюзию, что адресное пространство памяти больше, чем предусмотрено в RAM. В такой системе, если данные, соответствующие требуемому виртуальному адресу, в данный момент находятся на диске, а не в оперативной памяти, произойдет задержка пока эти данные не будут доступны, во время этой задержки данные должны быть перенесены с дискового носителя в RAM. В этом случае текущее обращение к памяти прерывается и попытка обращения к этим данным делается позже.

Прерывающий сигнал, подаваемый с устройства организации памяти, генерируется до тех пор, пока не приостановится исполнение инструкции, которая вызвала несостоятельное обращение к памяти, но может, вместо этого, быть использована для отмены выполнения последующей инструкции по обработке данных, т.е. инструкции по обработке данных, стоящей за инструкцией, которая привела к несостоятельному обращению к памяти. Это применимо благодаря тому, что последующие инструкции могут быть успешно переданы в память.

Использование прерывающего сигнала для отмены выполнения инструкции, следующего сразу же за инструкцией, которая инициализировала несостоятельный доступ к памяти, устанавливает последовательные требования на таймерование сигнала прерывания. В противном случае должен быть предусмотрен сложный механизм для возврата результатов выполнения последующей инструкции после того как эта инструкция завершена.

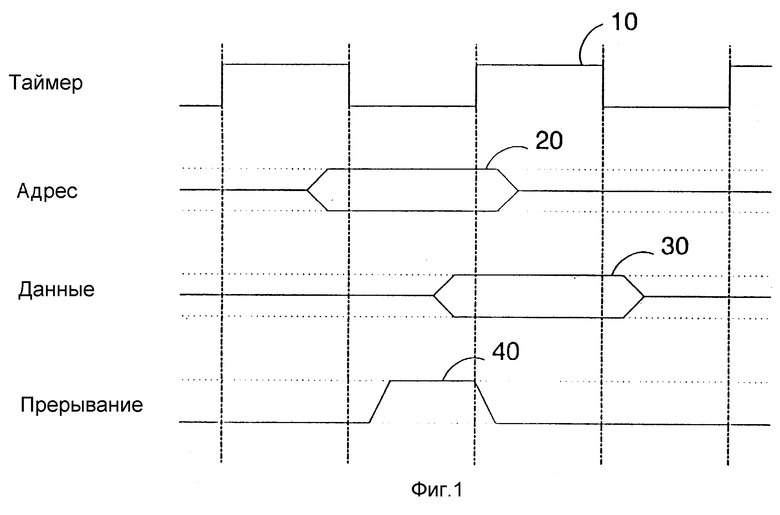

Фиг. 1 сопроводительных рисунков является схематичной диаграммой организации таймера для прерывающего сигнала во время операции записи данных (в которой данные записываются в RAM) с помощью ранее предложенного процессора, на который делалась ссылка.

Как показано на фиг. 1, сигнал таймера 10 контролирует выполнение инструкций обработки данных с помощью процессора. Когда инициализируется операция записи данных, адрес памяти 20 подается процессором на устройство организации памяти и через половину цикла сигнала таймера данные 30, которые должны быть записаны по этому адресу, выводятся процессором.

Если устройство организации памяти определяет, что адрес памяти 20 недействительный (например, из-за того что данные, соответствующие этому адресу, в настоящий момент удерживаются за диском в системе виртуальной памяти), то устройством организации памяти генерируется прерывающий сигнал 40 и подается на процессор.

Следующая инструкция после инструкции записи данных выполняется сразу же, поэтому нет необходимости (при нормальных обстоятельствах) ждать сигнала из устройства организации памяти после того как данные, которые должны быть записаны, помещены на шину данных. В соответствии с этим, чтобы прерывающий сигнал поступал вовремя для отмены выполнения последующей инструкции, предложенный процессор данных обладает требованием, чтобы прерывающий сигнал действовал половину цикла сигнала таймера до того как данные, которые должны быть записаны, поступают на выход процессора данных.

На практике такую организацию таймирования трудно достигнуть и она, в частности, требует быстрой работы устройства организации памяти (с соответствующим высоким энергопотреблением этим устройством).

Вышеуказанный процессор данных, на который делалась ссылка, также предусматривает выполнение своего внутреннего набора инструкций. Это достигается путем сравнения текущего состояния четырех действующих флагов с соответствующими состояниями, определенными с помощью условного кода, включенного в каждую инструкцию. Это сравнение происходит одновременно с выполнением инструкции. Поэтому полное исполнение инструкции прерывается если состояние действующих флагов не соответствует заданному условному коду.

Другим документом, описывающим этот тип процессора данных, является статья "ARM6: A. High Performance Low Power Consumption Macrocell", M. Muller, COMPCON Spring 93, стр. 80-87. Эта статья описывает признаки прерывания памяти и выполнении условных инструкций упомянутого выше процессора ARM6.

Описание изобретения.

Данное изобретение предлагает устройство обработки данных, в котором успешно выполняются инструкции по обработке данных конвейерным способом, данное устройство содержит: устройство доступа к памяти для доступа к памяти с данными в ответ на выполнение одной или более инструкций, устройство доступа к памяти содержит средство для детектирования возможности каждого доступа к памяти; и средство проверки условия в ответ на рабочее состояние устройства обработки данных, создаваемого посредством предыдущих выполненных инструкций и оперирующего в процессе выполнения каждой инструкции для детектирования насколько эта инструкция может быть выполнена; отличающееся тем, что содержит устройство контроля условий, воспринимающее состояние устройства доступа к памяти и устройства проверки условия, для предотвращения полного выполнения текущей инструкции, если либо средство доступа к памяти указывает, что доступ к памяти инициализированный с помощью предшествующей инструкции является недействительным, либо средство проверки условия указывает на то, что текущая инструкция не может быть выполнена.

В обрабатывающем данные устройстве, в соответствии с изобретением, установлен полный набор инструкций условия и также применяется механизм, предотвращающий полное выполнение каждой инструкции в зависимости от условия, для управления прерываниями памяти. Таким образом, сигналы прерывания памяти, инициализируемые действующей инструкцией, могут быть получены одновременно во время выполнения каждой инструкции в качестве детектирования с помощью устройства проверки условия насколько данная инструкция может быть выполнена. Это может позволить прерываниям памяти работать для каждой инструкции в более поздний момент времени, чем это позволялось ранее предложенным процессором данных.

В предпочтительном варианте устройство обработки данных содержит один или более действующих флагов для хранения данных, чувствительных к текущему рабочему состоянию обрабатывающего данные устройства, каждая инструкция содержит код условия, определяющий состояние действующих флагов, который требуется для выполнения этой инструкции, и средство проверки условия оперирует для сравнения требуемого состояния действующих флагов, заданного кодом условия в каждой инструкции с нужным состоянием действующих флагов. Коды условия могут определять, что конкретные действующие флаги должны быть установлены в конкретное логическое состояние или, что состояние данного действующего флага не влияет на выполнение текущей инструкции. В экстремальном случае возможный код условия может определить, что конкретная инструкция должна быть выполнена несмотря на состояние любого из действующих флагов.

Действующие флаги могут определять различные признаки рабочего состояния устройства обработки данных. В предпочтительном варианте оно содержит четыре действующих флага, соответственно определяющих;

(i) генерировала ли предыдущая операция обработки данных отрицательный результат;

(ii) генерировала ли предыдущая операция обработки данных нулевой результат;

(iii) был ли установлен бит переноса предыдущей операцией устройства обработки данных; и

(iv) появилась ли арифметическая перегрузка во время предыдущей операции устройства обработки данных.

Предпочтительно, чтобы средство доступа к памяти содержало: средство для передачи адреса памяти в память данных; и средство для дальнейшей передачи данных в память данных или получения данных из памяти данных.

Чтобы устройство контроля условия было удобно совместимо как с устройством доступа к памяти, так и с устройством проверки условия, предпочтительно чтобы: устройство доступа к памяти было способно генерировать прерывающий контрольный сигнал, чтобы указать что доступ к памяти невозможен; устройство проверки условия было способно генерировать сигнал условия неудачного контроля, чтобы указать, что текущая инструкция, не может быть выполнена; и заявленное устройство содержало устройство для комбинирования сигнала прерывания контроля и сигнала условия прерывания неудачного контроля, чтобы генерировать комбинированный контрольный сигнал для подачи на устройство контроля условия.

В преимущественном простом варианте устройство для комбинирования содержит логический элемент OR (или).

В удобном варианте операции устройства обработки данных контролируется с помощью сигнала таймера.

Вторым объектом изобретения является интегральная схема, содержащая устройство обработки данных.

Третьим объектом изобретения является способ обработки данных, в котором последовательные инструкции по обработке данных выполняются конвейерным методом, который содержит стадии: доступ к памяти данных в ответ на одну или более инструкций; детектирование насколько возможен каждый доступ; и детектирование, во время выполнения каждой инструкции, возможно ли выполнение этой инструкции в зависимости от рабочего состояния устройства обработки данных, заданного предыдущим выполнением инструкций; и отличается стадией, предотвращающей полное выполнение текущей инструкции, если определено, что либо этот доступ к памяти, инициализированный действующей инструкцией, невозможен, либо, что текущая инструкция не может быть выполнена.

Изобретение будет описано со ссылкой на сопровождающие чертежи, в которых:

фиг. 1 - диаграмма схематичного таймирования, иллюстрирующая требования на время для сигнала прерывания во время операции записи данных с помощью предложенного ранее процессора данных,

фиг. 2 - схематическая блок-схема аппаратуры для обработки данных, в соответствии с вариантом изобретения,

фиг. 3 - схематическая блок-схема части центрального процессора, и

фиг. 4 - схематическая диаграмма таймирования, иллюстрирующая требования на время для сигнала прерывания во время операции записи данных с помощью обрабатывающей данные аппаратуры на фиг. 2.

На фиг. 2 проиллюстрирована схематическая блок-схема устройства обработки данных в соответствии с вариантом изобретения. Оно содержит центральный процессор (CPU) 100, устройство организации памяти (MMU) 110 и оперативную память (RAM) 120. CP 100 и MMU 110 связаны адресной шиной 130 для обмена адресами памяти и шиной данных 140 для обмена данными. Из MM 110 к CPU 100 также предусмотрена линия контрольного прерывания, чтобы переносить прерывающий сигнал, чувствительный к некорректному или невозможному доступу к памяти.

Сигнал таймера (импульс синхронизации) подается на CPU 100 и на MMU 110 для контроля за операциями обоих этих устройств. Каждая инструкция по обработке данных выполняется с помощью CPU 100 за конкретное число циклов сигнала таймера (в зависимости от природы этой инструкции) и обращение к памяти с помощью MMU 110 осуществляется синхронно с сигналом таймера.

MMU 110 оперирует под контролем CPU 100 и сигнала таймера, чтобы иметь доступ к данным, хранимым в RAM 120. В соответствии с этим MMU связано с RAM посредством множества адресных линий и линий данных 160.

Фиг. 3 является блок-схемой части центрального процессора 100. CPU 100 применяет конвейерную инструкцию, чтобы позволить практически постоянно осуществлять обработку и операции памяти. Обычно, пока одна инструкция завершается, ее преемник декодируется, а третья инструкция вызывается из памяти. Такая организация носит название конвейера трехстадийного исполнения.

В части CPU 100, проиллюстрированной на фиг. 3, инструкции по обработке данных, которые уже был извлечены из памяти и декодированы, поступают для исполнения. Инструкция по обработке данных содержат 32-битные слова, в которых биты с 28 по 31 формируют 4-битное поле условия. Оставшиеся биты (биты с 0 по 27) задают операцию, которая должна быть осуществлена в ответ на эту инструкцию, и, в некоторых случаях, операнд, по которому должна быть осуществлена операция.

Поле условия (биты 28-31) поступает на тестер условия 200, который сравнивает биты поля условия с 16 ранее заданными кодами условия. 16 кодов условия определяют состояние одного или более из четырех флагов процессора 210, обозначенных как N, Z, C и V флаги. Эти флаги отражают рабочее состояние CPU 100, заданное предыдущим исполнением инструкций.

Флаг N указывает на отрицательный результат в результате предыдущего арифметического действия CPU 100; Z флаг указывает на нулевой (равный) результат от предыдущего действия CPU; флаг C указывает был ли установлен бит переноса во время предыдущей операции CPU; и флаг V указывает на арифметическое переполнение, возникнувшее во время предыдущей операции CPU. Соотношение между четырьмя битами поля условия и условиями, присвоенными для N, Z, C и V.

Флагами показаны в списке ниже:

0000 = EQ - Z установлен (равен)

0001 = NE - Z сброшен (не равен)

0010 = CS - C установлен (неопределенно высокий или такой же)

0011 = CC - C сброшен (неопределенно низкий)

0100 = MI - N установлен (отрицательный)

0101 = PL - N сброшен (положительный или ноль)

0110 = VS - V установлен (перегрузка)

0111 = VC - V сброшен (перегрузки нет)

1000 = HI - C установлен и Z сброшен (неопределенно высокий)

1001 = LS - C сброшен или Z установлен (неопределенно низкий или тот же)

1010 = ∈E-N установлен и V установлен, или N сброшен и V сброшен (больше или равно)

1011 = LT - N установлен и V сброшен, или N сброшен и V установлен (меньше чем)

1100 = ∈T-Z сброшен и либо N установлен и V установлен, либо N сброшен и V сброшен (больше чем)

1101 = LE - Z установлен, либо N установлен и V сброшен, либо N сброшен и V установлен (меньше чем или равно)

1110 = AL - всегда

1111 = NV - никогда.

Тестер условия 200 проверяет состояние перечисленных выше флагов в зависимости от того, какой бит установлен в поле условия текущей инструкции. Это сравнение осуществляется во время выполнения текущей инструкции. Выполнение текущей инструкции позволяют завершить только если соответствующие флаги установлены в состояния, отведенные под поле условия. Если определено состояние "всегда" (AL), то инструкция будет выполнена независимо от флагов. Код условия "никогда" (NV) прекращает выполнение инструкции независимо от состояния флагов 210.

Тестер условия 200 генерирует выходящий сигнал 220, указывающий может ли быть полностью выполнена текущая инструкция. Выходящий сигнал 220 объединяется с прерывающим сигналом, подаваемым на линию контрольного прерывания 150 из MMU 110 на CPU 100, посредством элемента "ИЛИ" 230. Поэтому выходной сигнал элемента "ИЛИ" 230 выставлен если либо тестер условия 200 указывает, что текущая инструкция не может быть полностью выполнена, либо сигнал прерывания установил MMU 110.

Устройство выполнения инструкции 240 получает биты с 0 по 27 каждой инструкции, определяя операцию, которая будет осуществлена и, в некоторых случаях, операнд по которому будет производиться операция. Во время выполнения текущей инструкции (т.е. после прохождения и рабочих задержек тестера условия 200 и элемента "ИЛИ" 230) устройство выполнения инструкции 240 получает выходной сигнал с элементами "ИЛИ", указывающий может ли быть полностью выполнена текущая инструкция. Если выходной сигнал с элемента "ИЛИ" 230 указывает, что текущая инструкция не может быть полностью выполнена, то инструкция отменяется без изменения состояния каких-либо регистров или распределения памяти, связанного с аппаратурой.

Тестер условия 200 и устройство выполнения инструкции 240 могут быть выполнены в том же виде, что и ранее предложенный процессор ARM6, на который делалась ссылка. Результат использования аппаратуры фиг. 3 заключается в том, что строгое таймирование сигнала прерывания значительно ослабляется, так что сигнал прерывания, относящийся к доступу к памяти и инициализированный предыдущей инструкцией, может быть установлен на более поздней стадии во время исполнения каждой инструкции.

Если сигнал прерывания получен в результате несостоявшейся операции при выполнении инструкции, тогда эта инструкция просто отбрасывается на позднюю стадию упомянутого выше конвейера инструкций.

Операции по чтению данных следуют за внутренним циклом процессора без доступа к памяти, чтобы предоставить время для перезагрузки данных, которые считываются из памяти, в соответствующий резистор процессора. В соответствии с этим, если прерывающий сигнал получен в результате несостоявшейся операции прочтения данных, то внутренний цикл, следующий за операцией чтения, предоставит время для того чтобы любые данные, поданные из памяти с помощью MMU 110 (те данные, которые могут быть ошибочными), были игнорированы и не сохранены в намеченном месте (например, в регистре процессора).

Соотношение времени при выполнении инструкции и применение сигнала прерывания для операции по записи данных показаны на фиг. 4, на котором сигнал таймера 300, который контролирует выполнение инструкции с помощью CPU 100, иллюстрируется с состояниями адресной шины 130 и шины данных 140. Чтобы инициализировать операцию записи данных адрес 310 помещается на адресную шину с помощью CPU 100. Через половину цикла сигнала таймера 300 данные 320 помещаются посредством CPU 100 на шину данных 140. Как только это сделано, CPU 100 способен выполнить следующую инструкцию во время следующего цикла сигнала таймера 300.

В то же время, когда данные 320 помещены на шину данных, если получен сигнал прерывания (обозначенный на фиг. 4 как 330) или если тестер условия 200 определяет, что последующая инструкция не может быть выполнена (что определяется с помощью тестера условия 200 во время половины цикла, после того как данные были помещены на шину данных и обозначено как 340), от выполнения последующей инструкции отзываются.

Хотя иллюстративные варианты изобретения описаны детально со ссылкой на сопроводительные чертежи, необходимо понимать, что изобретение не ограничивается этими определенными вариантами, и различные изменения и модификации могут быть выполнены специалистом в этой области техники, не выходящие из сферы изобретения, которая определена в приложенных пунктах формулы изобретения.

Изобретение относится к устройству обработки данных и способу выполнения инструкции по обработке данных. Техническим результатом является возможность получения сигналов прерывания памяти, инициализируемых предшествующей инструкцией, одновременно во время выполнения каждой инструкции. Устройство обработки данных содержит устройство доступа к памяти с данными в ответ на выполнение одной или более инструкций, содержащее средство для определения возможности каждого доступа к памяти, средство проверки условия для определения возможности выполнения этой инструкции, средство контроля условия для предотвращения полного исполнения текущей инструкции в случае, когда либо доступ к памяти является недействительным, либо текущая инструкция не может быть выполнена. 2 с. и 7 з.п.ф-лы, 4 ил.

(i) генерировала ли предыдущая операция обработки данных упомянутым устройством обработки данных отрицательный результат (N),

(ii) генерировала ли предыдущая операция обработки данных устройством обработки данных нулевой результат (Z),

(iii) был ли установлен бит переноса предыдущей операцией устройства обработки данных (С), и

(iv) появилась ли арифметическая перегрузка во время предыдущей операции устройства обработки данных (V).

| M.MULLER "APMG a High Performance Low Power Consumption Macrocell", SAN FRANCISCO, CA, US, COMPSON SPRING'93, February 1993, стр | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

| Устройство управления выборкой команд | 1985 |

|

SU1259260A1 |

| US 3766527 А, 16.10.73 | |||

| US 4864496 А, 24.05.83. | |||

Авторы

Даты

1999-09-10—Публикация

1994-08-16—Подача