ключены соответственно к первому и второму синхровходам устройства, вход базового адреса устройства подключен к входу базового адреса блока формирования адреса, вход разрешения загрузки базового адреса которого подключен к входу разрешения загрузки базового адреса устройства выходы блоки памяти с первого по . четвертый подключены соответственно к информационным входам блока формирования адреса с первого по четвертый, вход признака адреса последнего байта, выход признака адреса последнего байта входной информации и выход, признака адреса последнего байта которого подключены соответственно к выходу второго элемента ИЛИ блока прерывания, первому входу первого элемента И блока прерывания и к первому входу первого элемента И бло ка управления, выходы с первого по четвертый второго входного регистра подключены к информационным входам соответственно с четвертог.о по седьмой первого, второго и четвертого мультиплексоров, восьмой информационный вход которых подключен к четвертому выходу первого входного регистра, управляющие входы мультиплексоров с первого по четвертый подключены к информационным выходам блока формирования адреса соответственно с первого по четвертый, выходы разрядов с первого по третий третьего информационного выхода блока формирования адреса подключены к входам второго элемента И блока прерываний выход которого подключен к первому входу второго элемента ИЛИ блока прерываний, второй вход которого под ключен к выходу триггера блока прерываний, входы установки в 1 и установки в О которого подключены соответственно к входу начальной установки устройства и к первому синхровходу устройства,, первый вход второго элемента И. блока прерываний подключен к второму входу первого элемента И блока прерываний, выход которого подключен к второму входу первого элемента ИЛИ блока прерывания-, трети й вход которого подключен к выходу второго элемента И блока прерываний, вход начальной установки выходного регистра подключен к входу начальной установки устройства, входы начальной установки выходов с первого по четвертый выходног6 регистра подключены к выходам блока памяти соответственно с пятого по восьмой, синхровход выходного per гистра подключен к первому выходу признака фор1мирования кода команды устройства и к выходу первого элбмента ИЛИ блока управления, первый и второй входы которого.подключены соответственно к второму синхровходу устройства и к- выходу первого элемента И блока управления, второй вход которого подключен к первому синхровходу устройства, выход первого элемента И блока управления подключен к первому входу второго элемента И блока управления и к входу запуска одновибратора, вход разрешения запуска и выход которого подключены соответственно к девятому выходу блока памяти и к синхровходу регистра базы, информационный вход и вход установки в О которого подключены соответственно к выходу четвертого мультиплексора и к входу начальной установки устройства, первый и второй входы установки в О счетчика смещения подключены соответственно к входу начальной установки устройства и к выходу одновибратора, девя-. тый выход блока памяти подключен к инверсному входу второго элемента И блока управления, выход которого: подключен к счетному входу счетчика смещения, выход одновибратора подключен к второму вьпсоду признака формирования кода команды устройства, выход регистра базы и выход счетчика смещения подключены к первым информационным входам коммутатора, вторые информационные входы которого подключены к.первому и второму адресным входам устройства, управляющий вход . и выход коммутатора подключены соответственно к входу разрешения загрузки микропрограмм устройства и к адресному входу блока памяти, информационный вход и вход записи-считывания которого подключены соответственно к входу микрокоманд устройства и к управляющему входу коммутатора. 2. Устройство по п. 1, о т л и чающееся тем, что блок формирования адреса содержит четьфе полусумматора, три триггера, три коммутатора, три элемента И, элемент задержки и элемент ИСКЛЮЧАНЩЕЕ ИЛИ , причем первые информационные входы полусумматоров с первого по четвертый подключены к информационным входам блока соответственно с первого по четвертый, входы разрядов с первого по третий вторых информационных входов первого, второго,.третьего и четвертого полусумматоров,подключены к выходам триггеров соответственно с первого по третий, информационные входы которых подключены к выходам коммутаторов соответственно с первого по третий, вход установки в 1 первого триггера подключен к выходу первого элемента И, первый вход которого подключен к первому синхровходу блока и к первому входу второго элемента И, второй и третий входы которого подключены соответственно к выходу признака адреса последнего байта блока и к входу разрешения загрузки базового адреса блока и вькод третьего элемента И подключен к синхровходам .триггеров с первого по третий, входы установки в О которых подключены к выходу второго элемента И второй вход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход и выход которого подключены соответственно к входу

разрешения загрузки базового адреса блока и к первому входу третьего элемента И, второй вход которого подключен к второму синкровходу блока, вход признака адреса последнего байта блока через .элемент задержки подключен к вторьм входам первого и второго элементов И, вход.загрузки базового адреса подключен к первым информационным входам коммутаторов с первого по третий, выходы разрядов с первого по третий четвертого полусумматора подключены к вторым информационным входам коммутаторов соответственно с первого по третий, вторые входы которых подключены к входам разрядов соответственно с первого по третий базового адреса

блока, выход первого триггера блока подключен к выходу признака адреса последнего байта входной информации блока, выходы полусумматоров с первого по третий подключены соответственно к информационным выходам блока с первого по третий, вьпсоды разрядов с первого по третий четвертого информационного выхода блока подключены к выходам триггеров блока со.ответственно с первого по третий.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

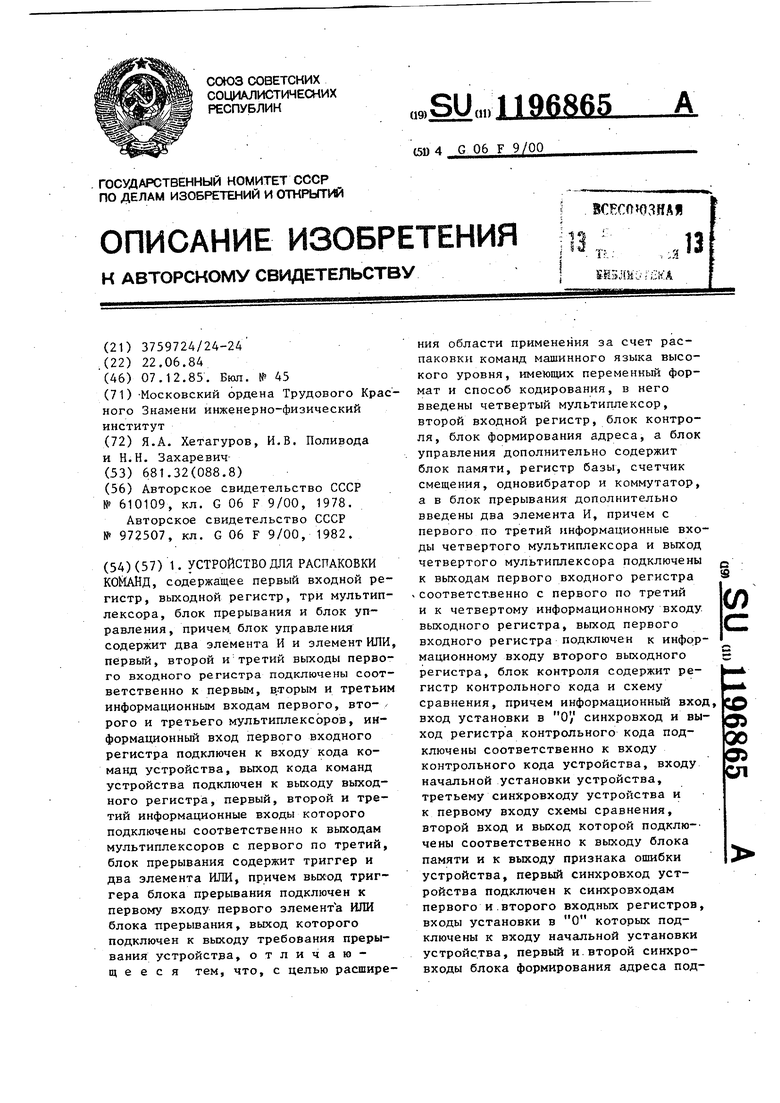

1. УСТРОЙСТВО ДЛЯ РАСПАКОВКИ КОЙАНД, содержащее первый входной регистр, выходной регистр, три мультиплексора, блок прерывания и блок уп равления, причем, блок управления содержит два элемента И и элемент ИЛИ, первый, второй и третий выходы первого входного регистра подключены соответственно к первьм, вторым и третьим информационным входам первого, вто- / рого и третьего мультиплексоров, информационный вход первого входного регистра подключен к входу кода команд устройства, выход кода команд устройства подключен к выходу выходного регистра, первый, второй и третий информационные входы которого подключены соответственно к выходам мультиплексоров с первого по третий, блок прерывания содержит триггер и два элемента ИЛИ, причем выход триггера блока прерывания подключен к первому входу первого элементна ИЛИ блока прерывания, выход которого подключен к выходу требования прерывания устройства, отличающееся тем, что, с целью расширения области применения за счет распаковки команд машинного языка высокого уровня, имейщих переменный формат и способ кодирования, в него введены четвертый мультиплексор, второй входной регистр, блок контроля, блок формирования адреса, а блок управления дополнительно содержит блок памяти, регистр базы, счетчик смещения, одновибратор и коммутатор, а в блок прерывания дополнительно введены два элемента И, причем с первого по третий информационные входы четвертого мультиплексора и выход четвертого мультиплексора подключены i к выходам первого входного регистра .соответственно с первого по третий (Л и к четвертому информационному входу выходного регистра, выход первого входного регистра подключен к информационному входу второго выходного регистра, блок контроля содержит регистр контрольного кода и схему сравнения, причем информационный вход, со 0) вход установки в О/ синхровход и выход регистра контрольного кода под00 Од ключены соответственно к входу контрольного кода устройства, входу ел начальной установки устройства, третьему синхровходу устройства и к первому входу схемы сравнения, второй вход и выход которой подключены соответственно к выходу блока памяти и к выходу признака ошибки устройства, первый синхровход устройства подключен к синхровходам первого и.второго входных регистров, входы установки в О которых подключены к входу начальной установки устройства, первый и.второй синхровходы блока формирования адреса под

1

Изобретение относится к вычислительной технике и может найти применение в ЭВМ, структура команд которых однозначно соответствует струк- . туре инструкций языков высокого уровня (ЯВУ), т.е. в ЭВМ с машинными ЯВУ.

Цель изобретения - расширение области применения устройства за счет введения в его состав средств, позволяющих распаковывать команды, машинного ЯВУ, обеспечивакяцих адаптацию устройства к изменению способов кодирования команд без изменения его структуры и повышакщих надежность устройств..

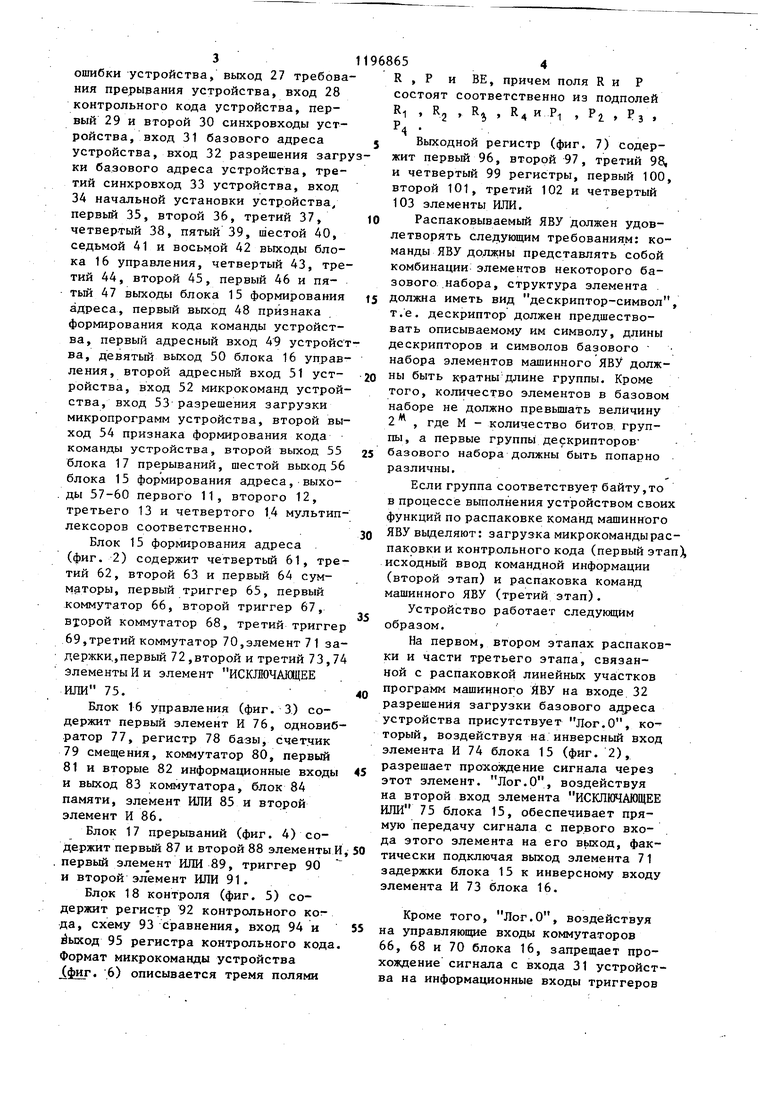

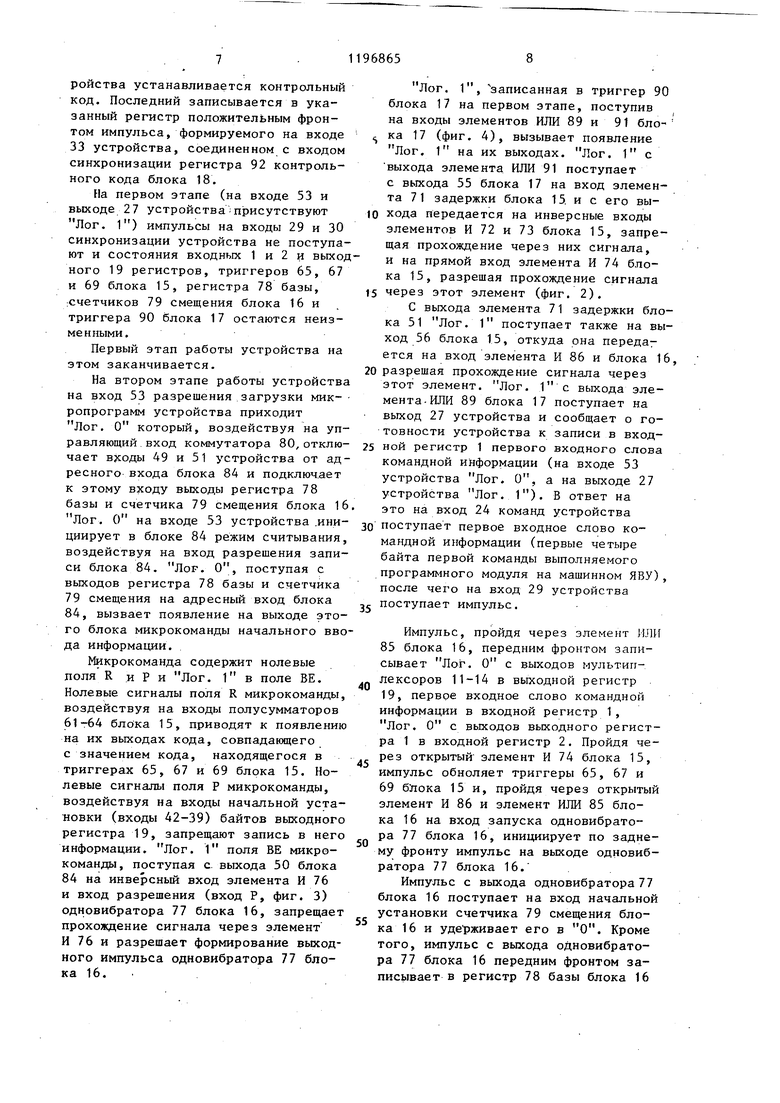

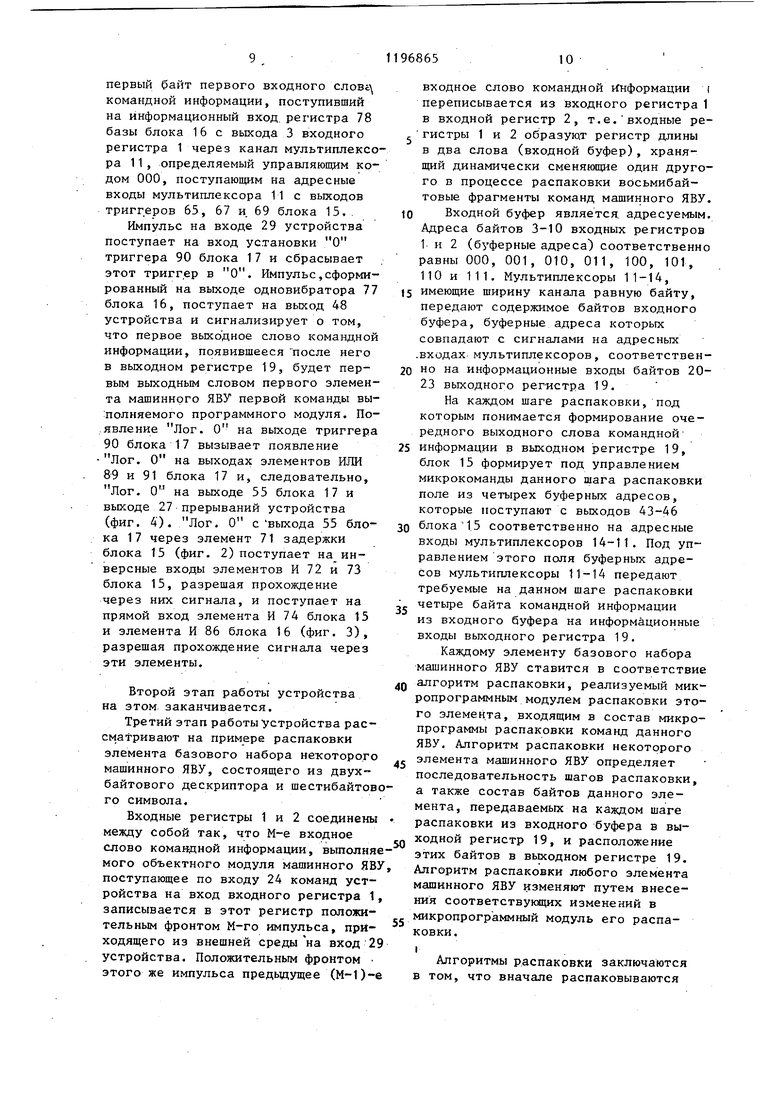

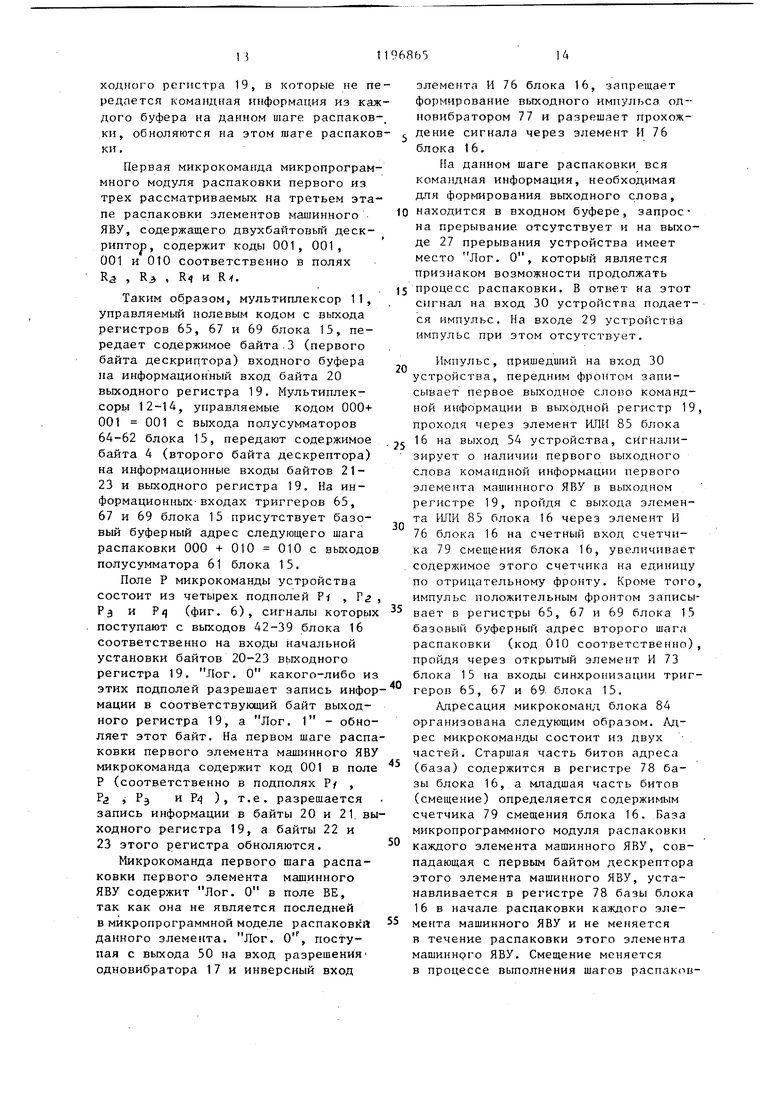

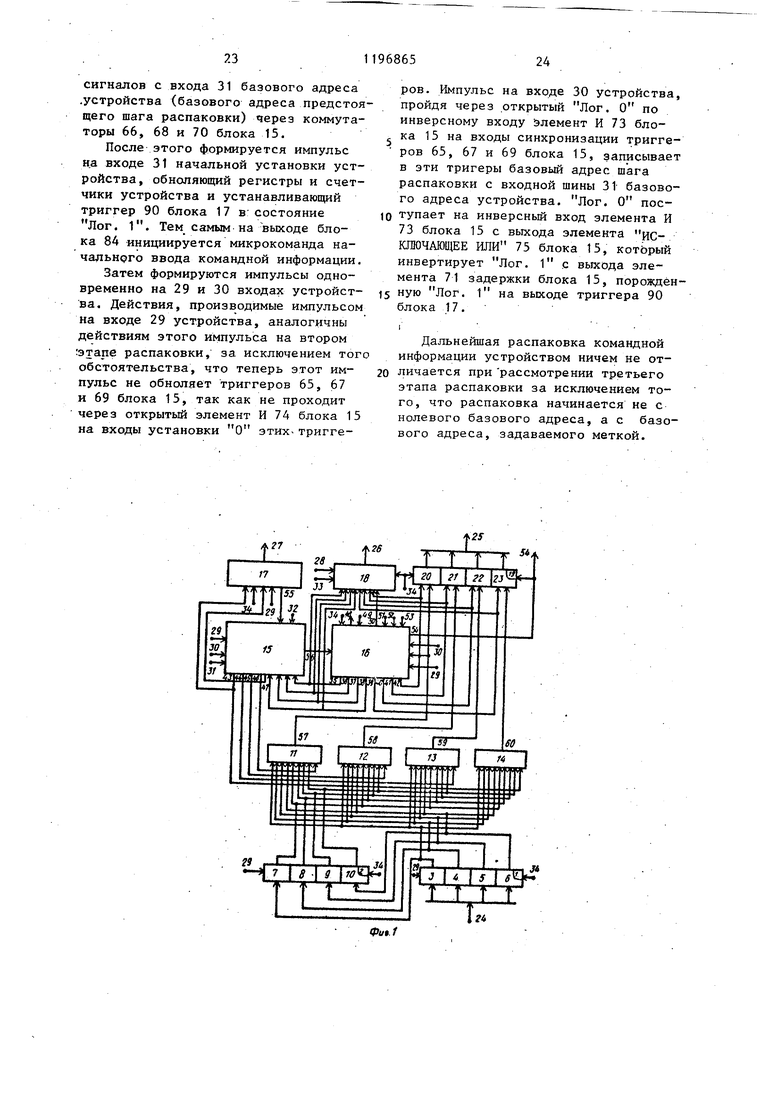

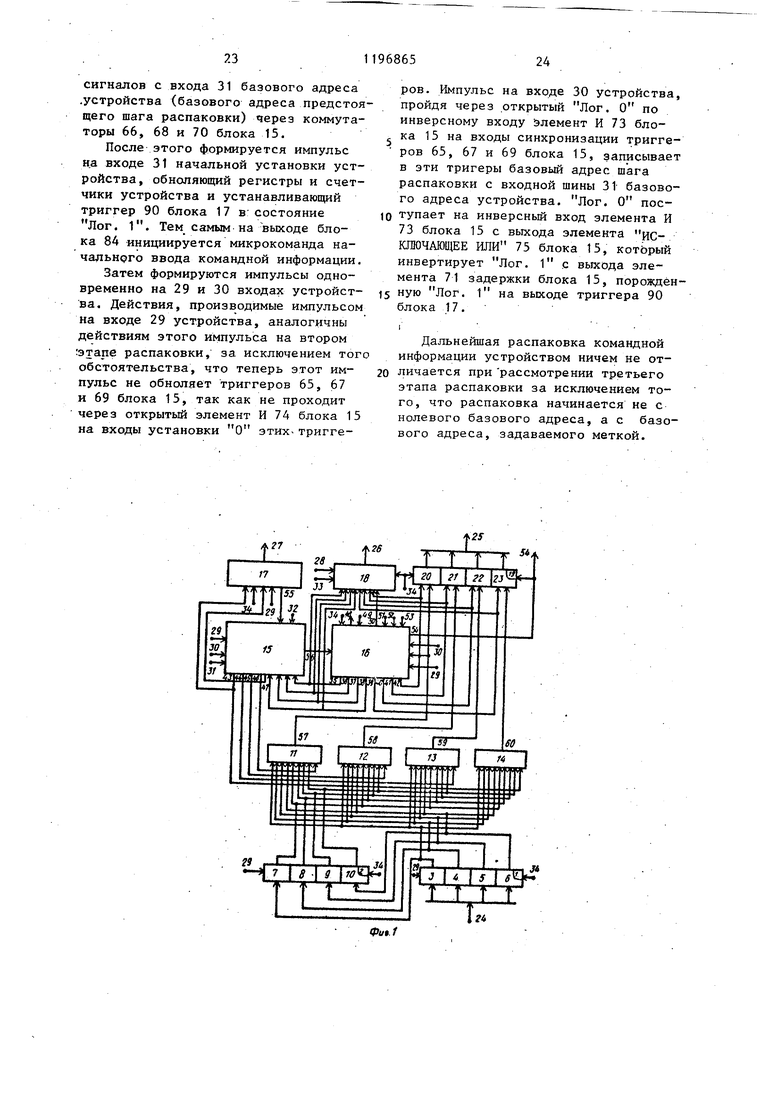

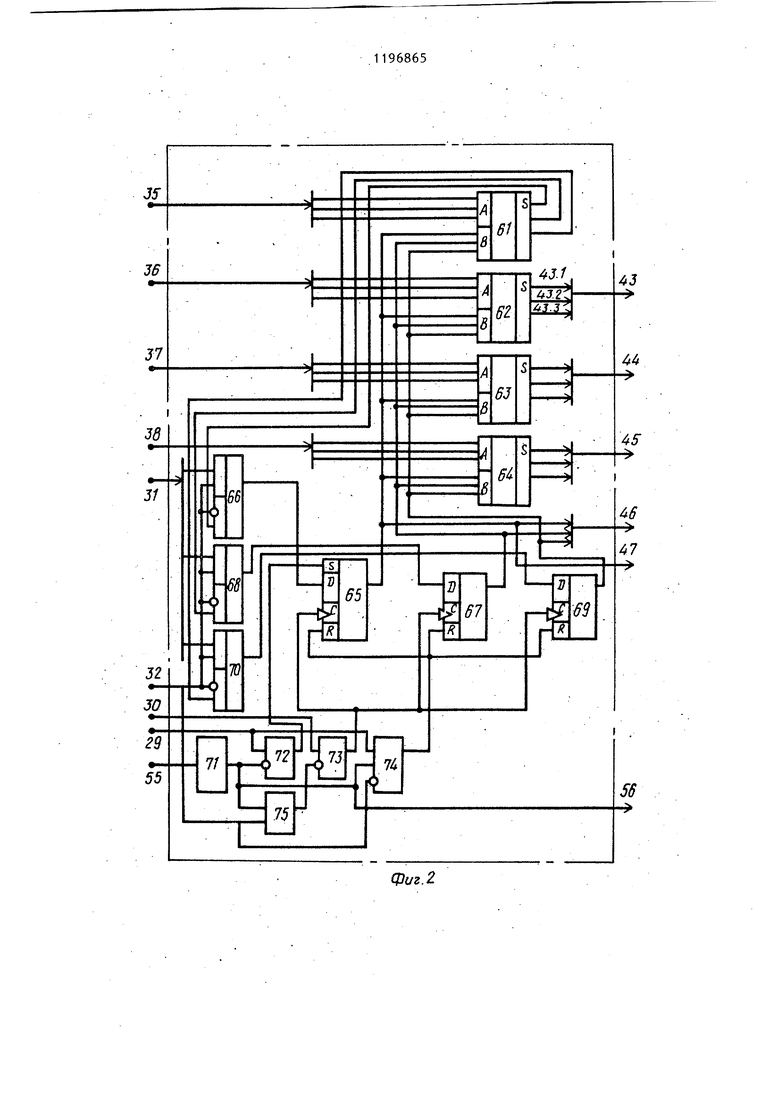

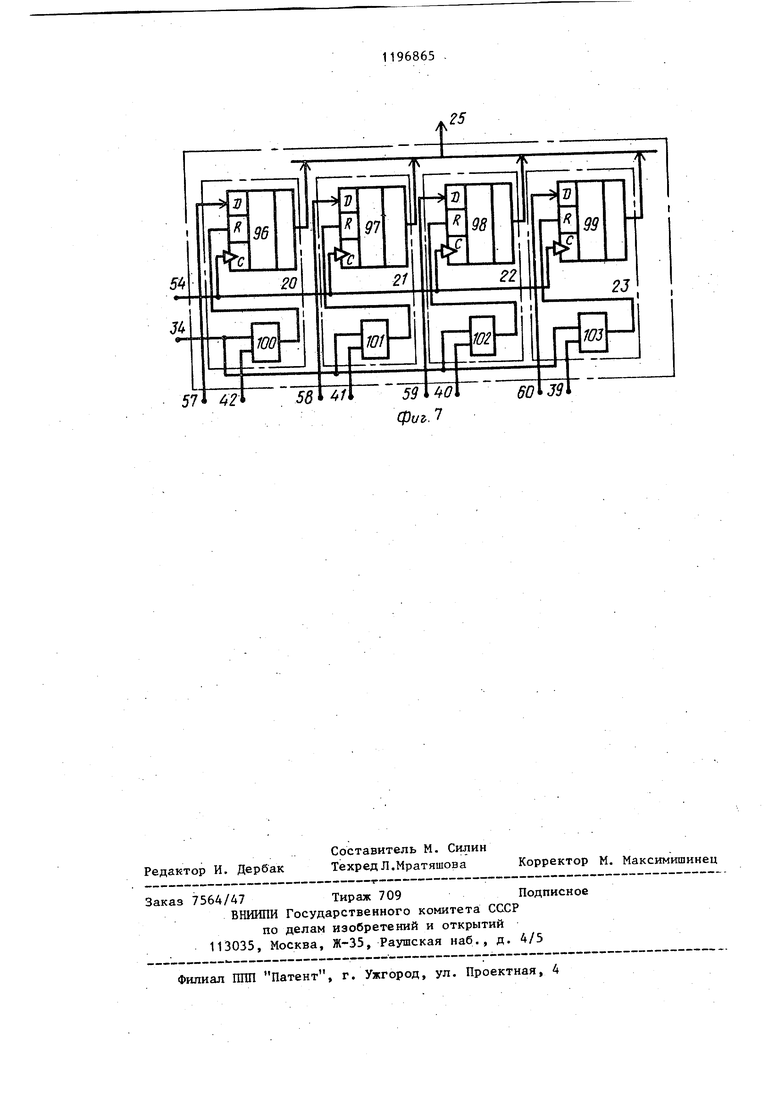

На фиг. 1 представлена структурная схема устройства распаковки команд; на фиг. 2 - функциональная схема блока формирования адреса; на фиг. 3 - функциональная схема блока управления;на фиг. 4 - функциональная схема блока прерываний; на фиг. 5 - функциональная схема блока контроля; на фиг. 6 - формат микрокоманд устройства; на фиг. 7 - функциональная схема выходного регистра.

Устройство (фиг. 1) содержит первый 1 и второй 2 входные регистры, первый 3, второй 4, третий 5 и четвертый 6 выходы (байты) первого входного регистра 1, первый 7, второй 8, третий 9 и четвертый 10 выходы (байты) второго входного регистра 2, первый 11, второй 12, третий 13 и четвертый 14 мультиплексоры, блок 15

формирования адреса, блок 16 управления, блок 17 прерываний, блок 18 контроля, выходной регистр 19, первый 20, второй 21, третий 22 и четвертый 23 выходы (байты) выходного

регистр-а 19, вход 24 и выход 25 команд устройства, выход 26 признака ошибки устройства, выход 27 требова ния прерывания устройства, вход 28 контрольного кода устройства, первый 29 и второй 30 синхровходы устройства, вход 31 базового адреса устройства, вход 32 разрешения загр ки базового адреса устройства, третий синхровход 33 устройства, вход 34 начальной установки устройства/ первый 35, второй 36, третий 37, четвертый 38, пятый 39, шестой 40, седьмой 41 и восьмой 42 выходы блока 16 управления, четвертый 43, тре тий 44, второй 45, первый 46 и пятый 47 выходы блока 15 формирования адреса, первый выход 48 признака формирования кода команды устройства, первый адресный вход 49 устройс ва, девятый выход 30 блока 16 управ ления, второй адресный вход 51 устройства, вход 52 микрокоманд устрой ства, вход 53 разрешения загрузки микропрограмм устройства, второй вы ход 54 признака формирования кода команды устройства, второй выход 55 блока 17 прерываний, шестой выход 56 блока 15 формирования адреса, выходы 57-60 первого 11, второго 12, третьего 13 и четвертого 1,4 мультип лексоров соответственно. Блок 15 формирования адреса . (фиг. 2) содержит четвертый 61, тре тий 62, второй 63 и первый 64 сумматоры, первый триггер 65, первый коммутатор 66, второй триггер 67, В1орой коммутатор 68, третий тригге 69,третий коммутатор 70,злемент71 за держки,, пер вый 72,второй и третий 73,7 элементы И и элемент ИСКЛЮЧАКЩЕЕ ИЛИ 75. Блок 16 управления (фиг. 3) содержит первый элемент И 76, одновиб ратор 77, регистр 78 базы, счетчик 79 смещения, коммутатор 80, первый 81 и вторые 82 информационные входы и выход 83 коммутатора, блок 84 памяти, элемент ИЛИ 85 и второй элемент И 86. Блок 17 прерываний (фиг. 4) содержит первый 87 и второй 88 элементы первый элемент ИЛИ 89, триггер 90 и второй элемент ИЛИ 91. Блок 18 контроля (фиг. 5) содержит регистр 92 контрольного когда, схему 93 сравнения, вход 94 и йыход 95 регистра контрольного кода Формат микрокоманды устройства фиг. 6) описывается тремя полями R , Р и BE, причем поля R и Р состоят соответственно из подполей RI . Rg 4 1 Pi , РЗ . Выходной регистр (фиг. 7) содержит первый 96, второй 97, третий 98, и четвертый 99 регистры, первый 100, второй 101, третий 102 и четвертый 103 элементы РИГИ.. Распаковываемый ЯВУ должен удовлетворять следующим требованиям: команды ЯВУ должны представлять собой комбинации элементов некоторого базового .набора, структура элемента . должна иметь вид дескриптор-символ, т.е. дескриптор должен предшествовать описываемому им символу, длины дескрипторов и символов базового набора элементов машинного ЯВУ должны быть кратны длине группы. Кроме того, количество элементов в базовом наборе не должно превьш1ать величину 2 , где М - количество битов группы, а первые группы дескрипторов базового набора должны быть попарно различны. Если группа соответствует байту,то в процессе выполнения устройством своих функций по распаковке команд машинного ЯВУ выделяют: загрузка микрокомандыраспакрвки и контрольного кода (первый этапХ исходный ввод командной информации (второй этап) и распаковка команд машинного ЯВУ (третий этап). Устройство работает следующим образом. На первом, втором этапах распаковки и части третьего этапа, связанной с распаковкой линейных участков программ машинного ЯВУ на входе 32 разрешения загрузки базового адреса устройства присутствует Лог.О, который. Воздействуя на. инверсный вход элемента И 74 блока 15 (фиг. 2), разрешает прохождение сигнала через этот элемент. Лог.О, воздействуя на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 75 блока 15, обеспечивает прямую передачу сигнала с первого входа этого элемента на его вькод, фактически подключая выход элемента 71 задержки блока 15 к инверсному входу элемента И 73 блока 16. Кроме того, Лог.О, воздействуя на управляющие входы коммутаторов 66, 68 и 70 блока 16, запрещает прохождение сигнала с входа 31 устройства на информационные входы триггеров

65, 67 и 69 блока 15 и, в свою очередь, разрешает прохождение сигналов с первого, второго и третьего вьпсодов полусумматора 6Г блока 15 через коммутаторы 66, 68 и 70 блока 15 на информационные входы триггеров 65, 67 и 69 блока 15 соответственноНа первом этапе в исходном состоянии входные 1 и 2 и выходной 19 ре- ю гистры устройства (фиг. 1), регистр 78 и счетчик 79 смещения блока 16 (фиг. 3), регистр 92 контрольного кода блока 18 (фиг. 5) устанавливаются в ноль импульсом, формируемым is на входе 34 начальной установки устройства. Этим же импульсом триггер 90 блока 17 (фиг. 4) устанавливается в состояние Лог.1. После этого подается сигнал Лог.1 на вход 53 20 разрешения загрузки микропрограмм устройства. Этот сигнал воздействует на вход разрешения записи (фиг. 3) блока 84, инициируя в последнем режим записи информации, и подключает 25 к адресному входу блока 84 сигналы с входов 49 и 51 устройства.

После .этого начинается запись в блок 84 микропрограммы распаковки зо команд конкретного машинного ЯВУ из множества используемых совместно с устройством машинных ЯВУ. Микрокоманды этой микропрограммы поступают

на вход 52 микрокоманд устройства, с нега на информационный вход блока 84 и записываются по адресам, поступающим по входам 49 и 51 устройства через коммутатор 80 на адресньй вход блока 84. Микропрограмма распаковки .. хранится в блоке 84 в течение всего времени, пока устройство рсуществляет распаковку команд данного конкретного машинного ЯВУ. При переходе на другой машинный ЯВУ в блок 84 записы- . вается микропрограмма распаковки, соответствующая новому машинному ЯВУ. Каждому из используемых совместно, с устройством машинных ЯВУ соответствует своя микропрограмма распаковки, ко-торая управляет процессом распаковки машинного ЯВУ и состоит из микропрограмм.

Формат микрокоманд (фиг. 6) преду матривает три поля R , Р и BE. Поле R микрокоманды управл9еткак4ор- f мированием блоком 15 поля адресов байтов информации входных 1 и 2 регистров, подлежащих передаче в выходной

регистр .19, так и динамической сменой этого поля в процессе распаковки команд мащинного ЯВУ. Поле Р микрокоманды управляет записью этих байтов информации в выходной регистр 13. Поле BE микрокоманды содержит информацию является ли данная микрокоманда последней при распаковке некоторого элемента машинного ЯВУ или нет.

Структурно микропрограмма распаковки состоит из микрокоманды начального ввода информации и микропрограммных модулей расп-аковки элементов машинного ЯВУ. Микрокоманда начального ввода информации является первой в микрокоманде распаковки и обеспечивает ввод первого входного слова командой информации для некоторого программного модуля данного машинного ЯВУ во входной регистр 1. Эта микрокоманда размещается в ячейке блока 84 с нолевым адресом.

Микропрограммные модули распаковки элементов машинного ЯВУ содержат микрокоманды, управляющие распаковкой этих элементов, причем между элементами базового набора машинного ЯВУ и соответствующими ему микропрограммными модулями распаковки, имеет место взаимно однозначное соответствие. Микрокоманды модулей распаковки размещаются в последовательных ячейках ЗУ 84 микропрограмм блока 16, причем первые микрокоманды размещаются в ячейках, старшие разряды адресов которых совпадают с первыми байтами дескрипторов элементов базового набора, соответствукщих данным модулям распаковки. Последние микрокоманды модулей распаковки содержат указание на окончание распаковки соответствующих элементов машинного ЯВУ - Лог. 1 в поле BE микрокоманды. Причем микрокоманды, не являющиеся последними в модулях распаковки, содержат Лог. О в поле BE.

Ячейки блока 84, не занятые ни микрокомандой начального ввода, ни микропрограммными модулями распаковки элементов машинного ЯВУ,.загружаются Контрольным кодом, не совпадающим ни с одной из использованных в микропрограмме микрокоманд,

Наряду с вводом в блок 84 микропрограммы распаковки на вход 28 устройства устанавливается контрольный код. Последний записывается в указанный регистр положительным фронтом импульса, формируемого на входе 33 устройства, соединенном с входом синхронизации регистра 92 контрольного кода блока 18.

Fla первом этапе (на входе 53 и выходе 2 7 устройства присутствуют Лог. 1) импульсы на входы 29 и 30 синхронизации устройства не поступают и состояния входных 1 и 2 и выходного 19 регистров, триггеров 65, 67 и 69 блока 15, регистра 78 базы, :Счетчиков 79 смещения блока 16 и триггера 90 блока 17 остаются неизменными.

Первый этап работы устройства на этом заканчивается.

На втором этапе работы устройства на вход 53 разрешения загрузки микропрограмм устройства приходит Лог. О который, воздействуя на управляющий вход коммутатора 80,отключает входы 49 и 51 устройства от адресного входа блока 84 и подключает к этому входу выходы регистра 78 базы и счетчика 79 смещения блока 16 Лог. О на входе 53 устройства .инициирует в блоке 84 режим считывания, воздействуя на вход разрешения записи блока 84. Лог. О, поступая с выходов регистра 78 базы и счетчика 79 смещения на адресный вход блока 84, вызвает появление на выходе этого блока микрокоманды начального ввода информации.

Микрокоманда содержит нолевые поля R и Р и Лог. 1 в поле BE. Нолевые сигналы поля R микрокоманды, воздействуя на входы полусумматоров 61-64 блока 15, приводят к появлению на их выходах кода, совпадающего с значением кода, находящегося в триггерах 65, 67 и 69 блока 15. Нолевые сигналы поля Р микрокоманды, воздействуя на входы начальной установки (входы 42-39) байтов выходного регистра 19, запрещают запись в него информации. Лог. 1 поля BE микрокоманды, поступая с. выхода 50 блока 84 на инверсный вход элемента И 76 и вход разрешения (вход Р, фиг. 3) одновибратора 77 блока 16, запрещает прохождение сигнала через элемент И 76 и разрешает формирование выходного импульса одновибратора 77 блока 16.

Лог. 1, записанная в триггер 90 блока 17 на первом этапе, поступив на входы элементов ИЛИ 89 и 91 блока 17 (фиг. 4), вызывает появление Лог. 1 на их выходах. Лог. Г с выхода элемента ИЛИ 91 поступает с выхода 55 блока 17 на вход элемента 71 задержки блока 15 и с его выхода передается на инверсные входы элементов И 72 и 73 блока 15, запрещая прохождение через них сигнала, и на прямой вход элемента И 74 блока 15, разрешая прохождение сигнала

5 через этот элемент (фиг. 2).

С выхода элемента 71 задержки блока 51 Лог. 1 поступает также на выход 56 блока 15, откуда она передаг ется на вход элемента И 86 и блока 16,

0 разрешая прохождение сигнала через этот элемент. Лог. 1 с выхода элемента-ИЛИ 89 блока 17 поступает на выход 27 устройства и сообщает о готовности устройства к записи в входной регистр 1 первого входного слова командной информации (на входе 53 устройства Лог. О, а на выходе 27 устройства Лог. 1). В ответ на это на вход 24 команд устройства

0 поступает первое входное слово командной информации (первые четыре байта первой команды выполняемого программного модуля на машинном ЯВУ), после чего на вход 29 устройства

поступает импульс.

Импульс, пройдя через элемент ИЛИ 85 блока 16, передним фронтом записывает Лог. О с выходов мультиплексоров 11-14 в вьпсодной регистр 19, первое входное слово командной информации в входной регистр 1, Лог. О с выходов выходного регистра 1 в входной регистр 2. Пройдя через открытый элемент И 74 блока 15, импульс обноляет триггеры 65, 67 и 69 блока 15 и, пройдя через открытый элемент И 86 и элемент ИЛИ 85 блока 16 на вход запуска одновибратора 77 блока 16, инициирует по заднему фронту импульс на выходе одновибратора 77 блока 16.

Импульс с выхода одновибратора 77 блока 16 поступает на вход начальной установки счетчика 79 смещения блока 16 и удерживает его в О. Кроме того, импульс с выхода оДновибратора 77 блока 16 передним фронтом записывает в регистр 78 базы блока 16 первый байт первого входного словс командной информации, поступивший на информационный вход, регистра 78 базы блока 16 с выхода 3 входного регистра 1 через канал мультиплексо ра 1 1 , определяемый управляющим кодом 000, поступающим на адресные входы мультиплексора 11 с выходов тригг.еров 65, 67 и. 69 блока 15. . Импульс на входе 29 устройства поступает на вход установки О триггера 90 блока 17 и сбрасывает этот триггер в О. Импульс,сформированный на выходе одновибратора 77 блока 16, поступает на выход 48 устройства и сигнализирует о том, что первое выходное слово командной информации, появившееся после него в выходном регистре 19, будет первым выходным словом первого элемента машинного ЯВУ первой команды вы:полняемого программного модуля. Появление Лог. О на выходе триггера 90 блока 17 вызывает появление . О на выходах элементов ИЛИ 89 и 91 блока 17 и, следовательно, Лог. О на выходе 55 блока 17 и выходе 27 прерываний устройства (фиг. 4). Лог. О с выхода 55 блока 17 через элемент 71 задержки блока 15 (фиг. 2) поступает на инверсные входы элементов И 72 и 73 блока 15, разрешая прохождение через них сигнала, и поступает на прямой вход элемента И 74 блока 15 и элемента И 86 блока 16 (фиг. 3), разрешая прохождение сигнала через эти элементы. Второй этап работы устройства на этом заканчивается. Третий этап работы устройства рассматривают на примере распаковки элемента базового набора некоторого машинного ЯВУ, состоящего из двухбайтового дескриптора и шестибайтов го символа. Входные регистры 1 и 2 соединены между собой так, что М-е входное слово командной информации, выполня мого объектного модуля машинного ЯВ поступающее по входу 24 команд устройства на вход входного регистра записывается в этот регистр положительным фронтом М-го импульса, приходящего из внешней среды на вход 2 устройства. Положительным фронтом этого же импульса предьщущее (М-1)входное слово командной нГнформации i переписывается из входного регистра 1 в входной регистр 2, т.е.входные регистры 1 и 2 образуют регистр длины в два слова (входной буфер), хранящий динамически сменяющие один другого в процессе распаковки восьмибайтовые фрагменты команд машинного ЯВУ. Входной буфер является, адресуемым. Адреса байтов 3-10 входных регистров 1 и 2 (буферные адреса) соответственно равны 000, 001, 010, 011, 100, 101, 110 и 111. Мультиплексоры 11-14, имеющие ширину канала равную байту, передают содержимое байтов входного буфера, буферные адреса которьгх совпадают с сигналами на адресных входах- мультиплексоров, соответственно на информационные входы байтов 2023 вькодного регистра 19. На каждом шаге распаковки, под которым понимается формирование очередного выходного слова командной информации в выходном регистре 19, блок 15 формирует под управлением микрокоманды данного шага распаковки поле из четырех буферных адресов, которые поступают с выходов 43-46 блока Ч 5 соответственно на адресные входы мультиплексоров 14-11. Под управлением этого поля буферных адресов мультиплексоры 11-14 передают требуемые на данном шаге распаковки четыре байта командной информации из входного буфера на информационные входы выходного регистра 19, Каждому элементу базового набора машинного ЯВУ ставится в соответствие алгоритм распаковки, реализуемый микропрограммным модулем распаковки этого элемента, входящим в состав микропрограммы распаковки команд данного ЯВУ. Алгоритм распаковки некоторого элемента машинного ЯВУ определяет последовательность шагов распаковки, а также состав байтов данного элемента, передаваемых на каждом шаге распаковки из входного буфера в выходной регистр 19, и расположение этих байтов в вькодном регистре 19. Алгоритм распаковки любого элемента машинного ЯВУ изменяют путем внесения соответствующих изменений в микропрограммный модуль его распаковки. Алгоритмы распаковки заключаются в том, что вначале распаковываются

дескрипторы, так что их байты, начи ная с первого, размещаются группами по четыре соответственно в байтах 20-23 выходного регистра 19 на каждом шаге распаковки дескриптора. Если на последнем шаге распаковки дескриптора количество его оставшихся байтов меньше четырех, то эти байты размещаются в выходном регистре 19 последовательно начиная с байта 20, причем оставшиеся свободными правые байты этого регистра устанавливаются в О. После распаковки дескриптора аналогичным образом распаковывается символ.

Первьй байт первого входного слова командной информации, записанный на втором этапе распаковки в регистр 78 базы блока 16 (фиг. 3),является первым байтом дескриптора первого элемента вьтолняемого программного модуля машинного ЯВУ. Этот байт совместно с нолевым содержимым счетчика 79 смещения блока 16 определяет адрес в ЗУ 84 микропрограмм блока 16 первой микрокоманды микропрограммного модуля распаковки данного элемента машинного .ЯВУ. Сигналы с выходов регистра 78 базы и счетчика 79 смещения блока 16 поступают через коммутатор 80 на адресный вход блока 84, вызывая появление на выходе этого ЗУ указанной микрокоманды, под управлением которой осуществляется первый шаг распаковки данного элемента.

Сигналы поля R этой микрокоманды, воздействуя на блок 15, управляют формированием буферных адресов байтов, передаваемых на первом шаге распаковки данного элемента машинного ЯВУ в выходной регистр 19. После R микрокоманды устройства состоит из четьфех подполей R , Ra , R и R 4 (фиг. 6), сигналы которых поступают соответственно с выходов 35, 38, 37 и 36 ЗУ 84 микрокоманд блока 16(фиг. 3) на входы полусумматоров 61, 64, 63 и 62 блока 15 (фиг. 2).

Сущность используемой в предлагаемом устройстве системы адресации байтов входного буфера заключается в следукяцем.

Буферный адрес байта,, помещаемого на данном шаге распаковки в байт 20 выходного регистра 19 (базовый буферный адрес), содержится в триггерах 65, 67 и 69 блока 15 (фиг. 2) и поступает с выхода 46 блока 15 на адресный вход мультиплексора 11. Буферные адреса байтов, поступающих на каждом-шаге распаковки с выходов мультиплексоров 12-14 соответственно на информационные входы байтов 21-23

выходного регистра 19, формируются соответственно полусумматорами 64-62 путем сложения базового буферного адреса соответственно с содержимыми подполей Ег , Ra , и R 4„микрокоманды данного шага распаковки (относительные буферные адреса).

Базовый буферный адрес следующего шага распаковки, формируемый полусуматором 61 блока. 15 путем сложения

базового буферного адреса данного ага распаковки с содержимым подполя R/ микрокоманды данного шага распаковки, поступает с выхода полусумматора 61 блока 15 на информационные

входы (фиг. 2) триггеров 65, 67 и 69 блока 15. Если на данном шаге распаковки командная информация из входного буфера поступает во все четые байта 20-23 выходного регистра 19,

то содержимые подполей R , R , Rj и R4 микрокоманды данного шага расаковки соответственно равны 100, 01, 010. и 011.

Если на данном шаге распаковки командная информация помещается в три байта 20-22 выходного регистра 19, то содержимые подполей R , R , RJ и R 4;} данного шага распавки со-, ответственно равны 011, 001, 010 и 010. Если на данном шаге распаковки командная информация помещается в два байта 20 и 21 выходного регистра 19 j то содержимые подп.олей RI ,Ra , R3 и R 4 микрокоманды данного шага расцаковки соответственно равны 010, 001, 001 и 001. Если же на данном шаге распаковки командная информация помещается только в байт 20 выходного регистра 19, то содержимые подполей Rf , Ri , R,3 и R 4 микрокоманды данного шага распаковки соответственно равны 001, 000, 000 и 000.

Таким образо.м, на выходе полусумматора 62 блока 15 ,на каждом шаге распаковки присутствует буферный адрес байта, помещаемого в байт выходного регистра 19 с самым большим номером (нумерация на фиг.1). Байты выХОДНОГО регистра 19, в которые не п редается командная информация из ка дого буфера на данном шаге распаков ки, обноляются на этом шаге распако ки. Первая микрокоманда микропрограм много модуля распаковки первого из трех рассматриваемых на третьем эта пе распаковки элементов машинного ЯВУ, содержащего двухбайтовьй дескриптор, содержит коды 001, 001, 001 и 010 соответственно в полях Ra , Кэ , Rl и R. Таким образом, мультиплексор 11, управляемый нолевым кодом с выхода регистров 65, 67 и 69 блока 15, передает содержимое байта 3 (первого байта дескриптора) входного буфера на информационный вход байта 20 выходного регистра 19, Мультиплексоры 12-14, управляемые кодом 000+ 001 001 с выхода полусумматоров 64-62 блока 15, передают содержимое байта 4 (второго байта дескрептора) на информационные входы байтов 2123 и выходного регистра 19, На информационных- входах триггеров 65, 67 и 69 блока 15 присутствует базовый буферный адрес следующего шага распаковки 000 + 010 010 с выходо полусумматора 61 блока 15, Поле Р микрокоманды устройства состоит из четырех подполей Pf , Рг РЗ и Р/) (фиг. 6), сигналы которых поступают с выходов 42-39 блока 16 соответственно на входы начальной установки байтов 20-23 вьпсодного регистра 19. Лог. О какого-либо и этих подполей разрешает запись инфор мации в соответствукхций байт выходного регистра 19, а Лог, 1 - обно ляет этот байт. На первом шаге расп ковки первого элемента машинного ЯВУ микрокоманда содержит код 001 в поле Р (соответственно в подполях Р/ , Рг j РЗ и Р/) ), т.е. разрешается запись информации в байты 20 и 21. вы ходного регистра 19, а байты 22 и 23 этого регистра обноляются. Микрокоманда первого шага распаковки первого элемента машинного ЯВУ содержит Лог. О в поле BE, так как она не является последней в микропрограммной моделе распаковки данного элемента. Лог. О, поступая с выхода 50 на вход разрешения одновибратора 17 и инверсный вход элемента И 76 блока 16, запрещает формирование выходного импульса одновибратором 77 и разрешает прохождение сигнала через элемент И 76 блока 16. На данном шаге распаковки вся командная информацияj необходимая для формирования выходного слова, находится в входном буфере, запросна прерывание, отсутствует и на выходе 27 прерывания устройства имеет место Лог. О, который является признаком возможности продолжать процесс распаковки. В ответ на этот сигнал на вход 30 устройства подается импульс. На входе 29 устройства импульс при этом отсутствует. Импульс, пришедший на вход 30 устройства, передним фронтом записывает первое выходное слово командной информации в выходной регистр 19, проходя через элемент И.Т1И 85 блока 16 на выход 54 устройства, сигнализирует о наличии первого выходного слова командной информации первого элемента машинного ЯВУ в выходном регистре 19, пройдя с выхода элемента ИЛИ 85 блока 16 через элемент И 76 блока 16 на счетный вход счетчи.ка 79 смещения блока 16, увеличивает содержимое этого счетчика на единицу по отрицательному фронту. Кроме того, импульс положительным фронтом записывает в регистры 65, 67 и 69 блока 15 базовый буферный адрес второго шага распаковки (код 010 соответственно), пройдя через открытый элемент И 73 блока 15 на входы синхронизации триггеров 65, 67 и 69. блока 15, Адресация микрокоманд блока 84 организована следующим образом. Адрес микрокоманды состоит из двух частей. Старшая часть битов адреса (база) содержится в регистре 78 базы блока 16, а младшая часть битов (смещение) определяется содержимым счетчика 79 смещения блока 16, База микропрограммного модуля распаковки каждого элемента машинного ЯВУ, совпадающая с первым байтом дескрептора этого элемента машинного ЯВУ, устанавливается в регистре 78 базы блока 16 в начале распаковки каждого элемента машинного ЯВУ и не меняется в течение распаковки этого элемента машиннрго ЯВУ. Смещение меняется в процессе выполнения шагов распаковки данного элемента машинного ЯВУ от О (первая микрокоманда микропрограммного модуля распаковки данного элемента) до величины К, - 1 (последняя микрокоманда микропрограммного модуля), где К - количество микрокоманд микропрограммного модуля распаковки М - го элемента базового набора машинного ЯВУ и 1 .гС. М , Н, где Н - количество элементов базового набора данного машинного ЯВУ.

После выполнения первого шага распаковки первого элемента машинного ЯВУ счетчик 79 смещения блока 16 содержит код, соответствующий десятичной единице, и на выходе блока 84 прису.тствует микрокоманда второго шага распаковки. Эта микрокоманда содержит коды 100, 001, 010 и 011 соответственно в полях R , Кз ,Кз и R-I Лог. О в подполях Р , Pi , РЗ и Р и Лог. О в поле БЕ, Данная микрокоманда согласно алгоритму распаковки определяет передачу следующих за байтами дескриптора четырех байтов символа распаковываемог элемента машинного ЯВУ в выходной регистр 19 устройства из входного буфера. После выполнения первого шага распаковки, в результате которого используют первые два байта элемента (байты дескриптора из бай.тон 3 и 4 входного регистра 1), в входном буфере остается только два байта символа данного элемента машинного ЯВУ (байты 5 и 6 входного регистра 1), т.е. командной информации содержащейся в входном буфере, недостаточно для продолжения процесса распаковки.

Для отработки подобных ситуаций в предлагаемом устройстве предусмотрено прерывание распаковки по недостатку информации.

Сигнал прерывания по недостатку информации вырабатывается блоком 17 (фиг. 4) на основании анализа поля буферных адресов, формируемых блоком 15 на каждом шаге распаковки. Устройство работает таким образом, что на каждом шаге распаковки в выходной регистр 19 передается некоторое количество (меньшее или равное четырем) последовательно размещенных байтов командной информации, образующих выходное слово командной информации, причем первый байт передается в байт 20 выходного регистра 19,

второй, если он есть на данном .шаге распаковки - в байт 21 выходного регистра 19, третий, если он есть, в б.айт 22 выходного регистра 19, четвертый, если он есть, - в байт 23 выходного регистра 19.

Входной буфер организован так, что последовательность его байтов 7-10 и 3-6, соответствующая последовательности буферных.адресов 100, 101, 110, 111, 000, 001, 010 и 011, Соответствует, некоторым восьми последовательно расположенным байтам командной информации, т.е. поле буферных адресов К байтов (К 4), помещаемых на данном шаге распаковки в выходной регистр 19, начиная с буферного адреса первого байта данного выходного слова командной информации кончая буферным адресом К-го байта этого слова, должно представлять собой непрерывный К - адресный фрагмент описанной последовательности буферных адресов в случае, когда вся командная информация, требуемая для формирования данн-ого выходного слова, находится в вх.одном буфере.

В случае, когдав входном буфере находится лишь часть требуемых на данном шаге распаковки байтов командной информации (X байтов в входном регистре 1, X N), буферные адреса оставшихся (N - Т)-байтов формируются блоком 15 в входном регистре 2, т.е. правильная последовательность буферных адресов нарушается. Для буферных адресов входного регистра .1 старший (левьш) разряд равен Лог.О а для буферных адресов входного регистра 2 - Лог. 1.

Блок 15 анализирует старшие разряды базового буферного адреса (буферный адрес первого байта выходного слова командной информации данного шага) и буферного адреса байта передаваемого в байт 23 выходного регистра 19 (буферный адрес последнего байта выходного слова командной информации данного шага) и в случае, когда старший разряд первого равен Лог. О, а старший разряд второго . 1, формирует сигнал прерывания по недостатку информации на данном шаге распаковки.

Поскольку на втором шаге распаковки первого элемента машинного ЯВУ триггеры 65, 67 и 69 блока 15 содержат соответственно код 010, то на выходах-полусумматоров 64, 63, 62 и 61 блока 15 имеют место соответствен но коды 011, 100, 101 и 110, т.е. буферные адреса первого (010) и последнего (101) байтов данного выходно го слова командной информации содер жат соответственно Лог. О и Лог.1 в старших разрядах. Сигналы этих разрядов, поступая соответственно с выходов 47 и A3 блока 15 на инверсный и прямой входы элемента И 88 блока 17, вызывают поя ление Лог. 1 на выходе этого логического элемента, которая(Поступая на вход элемента ИЛИ 89 блока 17, вы зывает появление Лог. 1 на выходе элемента ИЛИ 89 блока 17 и соответст венно на выходе 27 прерывания устрой ства. На выходе 55 блока 17 при этом присутствует Лог. О. Сигнал прерывания по недостатку информации (Лог. 1 на-выходе 27 прерывания устройства и Лог. О на выходе 55 блока 17) сигнализирует о недостатке в .входном буфере команд ной информации для продолжения процесса распаковки и является запросом на .ввод следующего входного слова командной информации в входной буфер устройства. В ответ на формирование очередного импульса на входе 30 устройства формирует.ся следующее слово командной информации на входе 24 командной информации устройства и фо мируется импульс на входе 29 устройства. Передним фронтом этого же импульса предыдущее входное слово командной информации переписывается из вхо ного регистра 1 в входной регистр 2. Этот же импульс, пройдя через открытый Лог. О на инверсном входе элемент И 72 блока 15, поступает на вход установки Лог. 1 триггера 65 блока 15 и .устанавливает его в соетояние Лог. 1. Тем самым базовый буферный адрес данного шага распаковки получает приращение + 4 (т.е. становится равным 110), что соответствует новому положению первого байта данного выходного слова командной информации, до этого находившегося в байте 5 входного регистра 1, в бай те 9 входного регистра 2. Буферные адреса данного шага распаковки, формируемые полусумматорами 64, 63, 62 и 61 блока 15, теперь соответственно равны 111, 000, 001 и 010. Эти адреса обеспечивают передачу байтов 9 и 10 входного регистра 2 и байтов 3 и 4 входного регистра 1 соответственно в байты 20-23 выходного регистра, как того и требует алгоритм распаковки на втором шаге распаковки первого элемента. Таким образом, в результате коррекции поля буферных адресов буферные адреса первого (110) и последнего (001) байтов данного выходного слова командной информации содержат в старших разрядах соответственно Лог. 1 и Лог. О, которые поступая соответственно на инверсный прямой входы логического элемента И 88 блока 17, вызывают появление Лог.О на выходах элементов И 88 и ИЛИ 89 блока 17. Этот Лог. О, поступая с выхода 27 прерывания устройства,сигнализирует о наличии в входном буфере устройства всей информации, необходимой для продолжения процесса распаковки, и о возможности продолжать этот процесс. В ответ на это запрещается формирование импульсов на входе 29 устройства и снимается запрет ,на формирование импульсов на входе 30 устройства. Синхроимпульс на входе 30 устройства выполняет действия, аналогичные такому же синхроимпульсу предыдущего шага распаковки: записывает второе выходное слово командной информации первого элемента машинного ЯВУ в выходной регистр 19 устройства, сообщает о наличии этого слова в выходном регистре 19, записывает в триггеры 65, 67 и 69 блока 15 базовый адрес третьего щага распаковки первого элемента машинного ЯВУ (код 010) и увеличивает содержимое счетчика 79 смещения блока 16 на +1 (его содержимое теперь соответствует десятичному числу 2), вызывая появление на вькоде блока 84 микропрограммы третьего шага распаковки первого элемента машинного ЯВУ. Микрокоманда третьего шага распаковки содержит коды 010, 001, 001 и 001 соответственно в подполях Rf , Ra , ЕЗ и , Лог. О в подполях Р/ и РТ: , Лог. 1 - в подполях РЗ и Pfl и Лог. 1 - в поле БЕ. Микрокоманда согласно алгоритму распаковки определяет передачу последних двух байтов первого элемента машинного ЯВУ, находящихся в байтах 5 и 6, входного регистра 1 соответственно в байты 20 и 21 выходного регистра 19 устройства и обозначение байтов 22 и 23 выходного регистра 19 Поскольку в данном случае последний байт выходного слова командной информации (байт 6 входного регистра 1) является последним из введенных в входной буфер из оперативной .памяти ЭВМ байтов командной информации (имеет буферньй адрес 011), первьй байт следующего выходного слова командной информации отсутствует в входном буфере, буферный адрес этого байта на данном шаге распаковки не определен и базовый адрес следующего шага распаковки сформирован обычными для предлагаемого устройства средствами, (суммированием базового адреса данного шага распаковки с содержимым подполя R микрокоманды быть не может) . Для обработки подобных ситуаций в предлагаемом устройстве предусмотрено прерывание процесса распаковки по критической длине выходного слова Сигнал прерывания по. критической длине выходного слова вырабатывается блоком 17 на основании анализа буфер ного адреса последнего байта выходно го слова командной информации на каж дом этапе распаковки. Буферный адрес формируемый полусумматором 62 блока 15, поступает с выхода 43 блока 15 на входы элемента И 87 блока 17. Если буферный адрес последнего байта выходного слова командной информации равен 011 (соответственно на выходах .43.1, 43.2 и 43.3 полусумматора 62 блока 15), что соответствует нахожде нию последнего байта в байте 6 выход ного регистра 1, то на выходе элемен та И 87 блока 1 7 имеет местоЛог. 1 кото рая воздействует на входы элементов ИЛИ 91 и 89 блока 17 и вызывает появ ление Лог. 1 на выходах этих элементов, и, соответственно, Лог. 1 на выходе 55 блока 17 и выходе 27 прерывания устройства - сигнал прерывания по критической длине выходного слова. Поскольку на третьем шаге распаковки первого элемента машинного ЯВУ буферный адрес последнего байта выходного слова командной информации равен 011, блок 17 вырабатывает сигнал прерывания по критической длине выходного слова. Лог. 1 с выхода 55 блока 17, поступая на вход элемента 71 задержки блока 15, вызывает появление Лог. 1 на выходе этого элемента, которая, воздействуя на инверсные входы элементов И 72 и 73 блока 15, запрещает прохождение сигналов через эти элементы и, воздействуя на прямые входы элемента И 74 блока 15 и элемента И 86 блока 16, разрешает прохождение сигналов через эти элементы. Поскольку микрокоманда третьего шага распаковки первого элемента машинного ЯВУ является последней в микропрограммном модуле распаковки данного элемента,она содержит Лог. 1 в поле BE. Лог. 1 поступая с выхода.50 ЗУ 84 микропрограмм блока 16 на инверсный вход элемента И 76.и вход разрешения одновибратора 77 -блока 16, запрещает прохождение сигнала чере.з элемент И 76 и разрешает формирование импульса одновибратором 77 блока 16. Импульс, пришедший на вход 29 устройства, пройдя через открытьй элемент И 86 блока 16 и элемент ИЛИ 85 блока 16 на выход 54 устройства, передним фронтом записывает выходное слово командной информации третьего шага распаковки первого элемента машинного ЯВУ в выходной регистр 19 и сигнализирует о наличии этого слова в выходном регистре 19. Этот же импульс передним фронтом записывает следующее входное слово командной информации, сформированное На входе 24 командной информации устройства, в входной регистр 1 устройства и переписывает содержимое его в входной регистр 2. Этот же импульс, ПРОЙДЯчерез открытьй элемент И 74 блока 15 на входы установки О триггеров 65, 67 и 69 блока 15 обноляёт эти триггеры. Этот же импульс, поступая с выхода элемента ИЛИ 85 на вход формирования одновибратора 77 блока 16, вызывает по заднему фронту появление импульса на выход одновибратора 77 блока 16. Импульс с вькода этого одновибратора поступает на вход установки О счетчика 79 смещения блока 16, обноляя этот счетчик, и положительным фронтом записывает в регистр 78 базы блока 16 содержимое байта 3 входного регистра 1, поступившее к- этому времени на информационный вход регистра 78 базы блока 16 через мультиплексор 1 1 , управляемь1й нолевым кодом с выхоцов триггеров 65, 67 и 69 блока 15, Байт 3 входного регистра 1 в данном случае содержит первый байт деск риптора второго элемента машинного ЯВУ. Вместе с нолевым содержимым счетчика 79 смещения блока 16 этот байт, поступая на адресный вход блока 84, вызывает появление на выходе, этого блока микрокоманды первого шага распаковки второго элемента машин ного ЯВУ. Кроме того, импульс с выхода одновибратора 77 блока 16, поступая с вькода 48 устройства, сигна лизирует о том, что следующее выходное слово командной информации будет первым выходным словом командной информации следующего элемента машинного ЯВУ. При переходе на другой програм.мный модуль того же ЯВУ на первом этапе производится только лишь замена контрольного кода. Блок 18 осуществляет контроль за работой устрой ства. Контрольный код, записываемый в регистр 92 контрольного кода блока 18 на первом этапе распаковки каждого программного модуля машинного ЯВУ и поступающий с выхода этого регистра на вход А схемы 93 сравнения в те чение всего процесса распаковки данного программного модуля, сравнивает ся схемой 93 сравнен.ия с кодом микро команды каждого шага распаковки данного программного модуля машинного ЯВУ, содержится также во всех ячейках блока 84, не; содержащих микрокоманд микропрограммы распаковки дан ного программного модуля. Любые сбои предлагаемого устройст ва приводят в конечном счете либо к появлению в регистре 78 базы блока 16 кода, отлично от кода первого байта дескрептора элемента распаковываемого на данном шаге, либо к пре вышению содержимым счетчика 79 смеще ния блока 16 при распаковке К-го элемента величины (М 1) где М количество микрокоманд микропрограммного модуля распаковки К-го элемента. В обоих случаях (в первом с вероятностью того, что ошибочное содер жимое регистра 78 базы блока 16 не совпадает с кодом первого байта ни одного из элементов базового набора данного машинного ЯВУ, а во втором - с вероятностью, равной единице) формируется обращение к ячейке блока 84, не принадлежащей ни одному из программных модулей распаковки элементов базового набора машинного ЯВУ. Таким образом, в .отсутствие сбоя схема 93 сравнения сравнивает микрокоманды микропрограммы распаковки с контрольным кодом, ие совпадающим ни с одной из них, и на выходе 26 устройства имеет место Лог. О. В случае же, когда приналичии сбоя имеет место обращение к ячейке блока 84, не содержащей микрокоманды распаковки, схема 93 сравнения блока 18, сравнивая содержимое этой ячейки (совпадающее с контрольным кодом) и контрольный код, формирует Лог. 1 на выходе 26 устройства. Лог. О на выходе 26 устройства свидетельствует об отсутствии, а Лог. Г - о наличии сбоя при распаковке команд машинного ЯВУ. Все это относится к распаковке устройством последовательности команд машинного ЯВУ, соответствующей линейному участку программы. При появлении в последовательности команд машинного ЯВУ, распаковываемых устройством, команды, нарушающей линейность выполнения программы формируется метка команды машинного ЯВУ, которойпередается управление. На вход 31 поступает базовый адрес первого шага распаковки. Командная информация, адрес которой указан в метке, поступает на вход 24 команд устройства. Наряду с этим формируется Лог.Г на входе 32 разрешения загрузки базового адреса устройства, которая, воздействуя на инверсный вход элемента И 74 блока 15, запрещает прохождение сигнала через этот элемент, а воздействуя на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 75 блока 15, переводит этот элемент в режим инвертора, и, воздействуя на управляющие входы коммутаторов 66, 68 и 70 блока 15, запрещает прохождение через эти элементы сигналов с выхода полусумматора 61 блока 15 на входы триггеров 65, 67.и 69 блока 15, разрешая поступление на входы этих триггеров

сигналов с входа 31 базового адреса .устройства (базового адреса предстоящего шага распаковки) через коммутаторы 66, 68 и 70 блока 15.

После этого формируется импульс на входе 31 начальной установки устройства, обноляющий регистры и счетчики устройства и устанавливающий триггер 90 блока 17 в: состояние Лог. 1. Тем самым на выходе блока 84 инициируется микрокоманда начальнрго ввода командной информации.

Затем формируются импульсы одновременно на 29 и 30 входах устройства. Действия, производимые импульсом на входе 29 устройства, аналогичны действиям этого импульса на втором этапе распаковки, за исключением тог обстоятельства, что теперь этот импульс не обноляет триггеров 65, 67 и 69 блока 15, так как не проходит через открытый элемент И 74 блока 15 на входы установки О этих-триггеров. Импульс на входе 30 устройства, пройдя через открытый Лог. О по инверсному входу элемент И 73 блока 15 на входы синхронизации триггеров 65, 67 и 69 блока 15, записывает в эти тригеры базовый адрес шага распаковки с входной шины 31 базового адреса устройства, Лог. О поступает на инверсный вход элемента И 73 блока 15 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 75 блока 15, который инвертирует Лог. 1 с выхода элемента 71 задержки блока 15, порождённую Лог. 1 на выходе триггера 90 блока 17.

I .

Дальнейшая распаковка командной информации устройством ничем не отличается при рассмотрении третьего этапа распаковки за исключением того, что распаковка начинается не с нолевого базового адреса, а с базового адреса, задаваемого меткой.

Фиг.2

51 5 52

305629

фиг.З

(Риг.б

25

фиг,. 7

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-22—Подача