«1259260

Изобретение относится к цифровой

вычислительной технике и может быть использовано в качестве блока предварительной выборки команд ЦВМ, к которым предъявляются высокие требования по быстродействию и ограничения на аппаратурные затраты (энергопотребление) .

Целью изобретения является упрощение устройства.

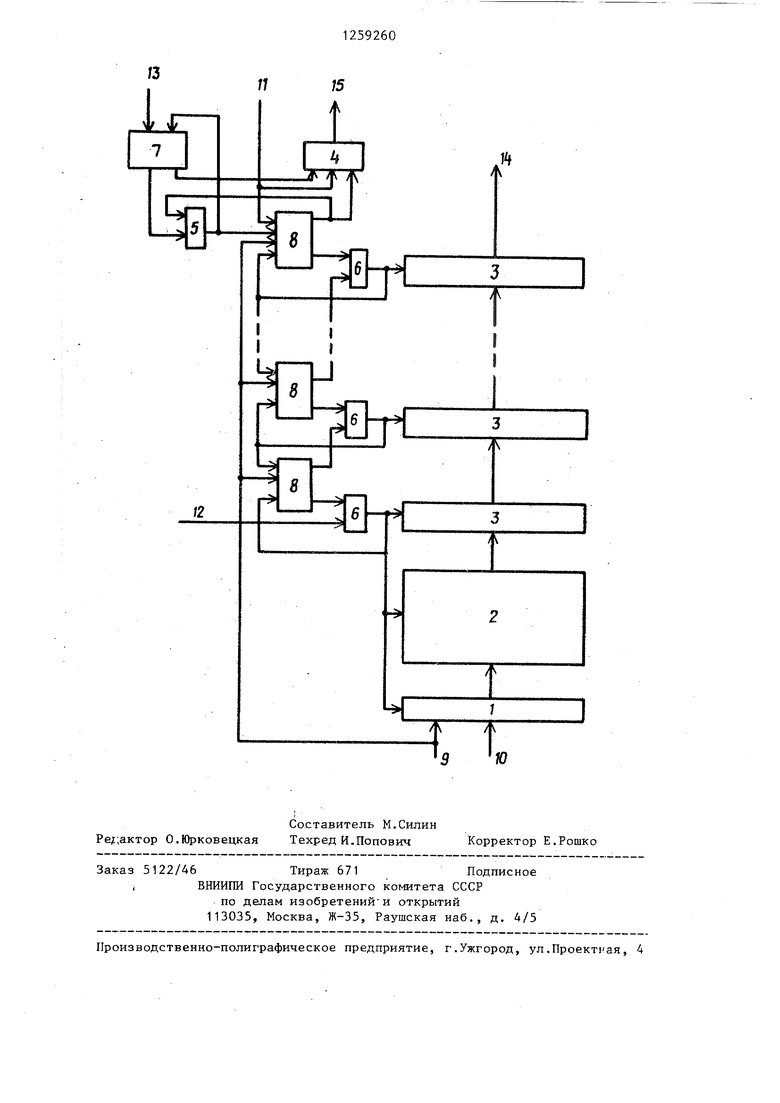

На чертеже представлена функцио- нальная схема предлагаемого устройства .

Устройство содержит счетчик 1 адреса, блок 2 памяти, группу регистров ,3, элементы И 4 и 5, группу элементов И 6, триггер 7 пропуска команды, группу триггеров 8 флага, входы 9 записи адреса команды, 10 адреса команды, 11 запроса выдачи очередной команды, 12 тактовых импульсов, 13 признака пропуска очередной команды устройства, -выходы 14 кода команды и 15 признака выдачи кода команды устройства.

Регистры 3 группы образуют буфер команд.

Счетчик 1 адреса предназначен для формирования адреса очередной команды.

Триггер 7 предназначен для хранения запроса на пропуск очередной команды (цепи начального сброса триггера 7 не показаны).

Триггеры 8 предназначень для хранения сигналов Свободен-занят одноименных регистров 3.

Вход 10 устройства предназначен для занесения адреса команды в счетчик 1 команд по синхронизирующему сигналу входа 9 в начале работы и при выполнении команд переходов, сигнал с входа 9, кроме того, приводит- в исходное состояние (Свободен) триггеры 8.

На вход 11 устройства поступают сигналы запроса очередной команды, на вход 12 поступает последовательность импульсов от генератора, периг од которьЕх равен циклу обращения к памяти, на вход 13 поступает из процессора сигнал пропуска очередной команды..

Выход 14 устройства предназначен для вьщачи очередной команды, сопровождаемой синхронизируюпщм импульсом на выходе 15.

Устройства работает следующим образом.

В блоке 2 памяти находятся команды, подлежащие выполнению. Устройство приходит в исходное состояние при подаче на вход 10 адреса начальной команды, сопровождаемого синхронизирующим сигналом с входа 9, в результате чего сбрасываются (устанавливаются в состояние Свободен) триггеры 8. Импульс с входа 12 через открытый элемент И 6 считывает команду с блока 2 памяти по начальному адресу, выставленному на информационных выходах счетчика 1, записывает эту команду в первый регистр 3, переводит одноименный триггер 8 в состояние Занят и прибавляет единицу к содержимому счетчика 1. Сигнал с

прямого выхода первого триггера 8 через открытый второй элемент И 6 переписывает информацию из первого регистра 3 во второй регистр 3-, сбрасывает первый триггер 8 и -устанавливает в состояние Занят второй триггер 8. В результате первый элемент И 6 вновь открывается, а второй элемент И 6 закрывается и т.д. Таким образом, информация, считанная с блока 2 памяти в первый регистр 3, последовательно переписывается из регистра в регистр, освобождая первый регистр 3 для записи очередной команды и последовательно заполняя

регистры.

Сигнал запроса с входа 11 устройства через открытый элемент И 4

(предполагается что сигнал Пропуск команды на вход 13 не поступал) поступает на выход 15 устройства, сопровождая информационный код на выходах 14 устройства. Этот же сигнал сбрасывает п-й триггер 8, в результате чего открывается одноименный

элемент И 6, что свидетельствует о готовности п-го регистра 3 записать информацию из (п-1)-го регистра 3 и т.д. Таким образом, при поступлении каждого сигнала запроса на вход

11 устройства и непустом буфере команд происходит считывание очередной команды из п-го регистра 3 группы, о чем свидетельствует появление сигнала на выходе 15 устройства.

В ЭВМ для организации программных переходов часто используются команды следующего типа Если выполнено условие, то пропустить следующую команJ1

ду. Для обеспечения такого режима в предложенном устройстве введены триггер 7 и элемент И 5.

Если в какой-либо момент поступает сигнал Пропуск команды на вход 13 устройства, то триггер 7 переводится этим сигналом в единичное состояние, элемент И 4 закрывается, в результате очередной запросный сигнал на входе 11 не вызывает появле-; ние сигнала на выходе 15, т.е. очередная команда на информационных выходах 14 устройства пропущена. Одновременно сигнал с прямого выхода п-го триггера 8 через открытый элемент И 5 поступает на вход сброса этого же триггера, в результате чего открывается одноименный элемент И 6, т.е. в п-й регистр 3 записывается следующая за пропущенной команда. Этот же сигнал сбрасывает триггер 7, т.е. элемент И 4 открывается, а элемент И 5 закрывается.

Формула изобретения 25

Устройство управления выборкой команд, содержащее блок памяти, группу регистров, два элемента И, счетчик адреса и триггер пропуска команды, причём информационный вход, вход записи и выход счетчика адреса подключены соответственно к входу адреса команды устройства, к входу записи адреса команды устройства и к информационному входу блока памяти, выход которого подключен к информационному входу первого регистра группы выход п-го регистра группы подключен к выходу кода ко- i манды устройства, где п - количество буферизируемых команд, выход первого элемента И подключен к выходу признака выдачи кода команды устройства, прямой выход триггера пропуска ко- I манды подключен к первому входу второго элемента И, о т.л и ч а ю- щ е е с я тем, что, с целью упроще10

15

20

25

592604

ния, оно содержит группу элементов И и группу триггеров флага, причем вход записи адреса команды устройства подключен к первым входам уста- 5 новки в О триггеров флага группы, вход тактовых импульсов устройства подключен к первому входу первого элемента И группы, вых,од которого подключен к синхровходу первого регистра группы, входу прибавления единицы счетчика адреса, входу записи-считывания блока памяти и к входу установки в 1 первого триггера группы, выход К-го регистра группы подключен к информационному входу (К + 1)-го регистра группы (К 1, п-1), выход Р-го элемента И группы подключен к синхровходу Р-го регистра группы (Р - 2, п), к входу установки в 1 Р-го триггера флага группы и к второму входу установки в О (Р-1)-го триггера флага группы, прямой и инвер сный выходы К-го триггера флага группы подключены соответственно к первому входу (Ky-l)-ro и к второму входу К-го элементов И группы, инверсный выход п-го триггера флага группы подключен к второму входу п-го элемента И группы, прямой выход п-го триггера флага группы подключен к первому входу первого элемента И и к второму входу второго элемента И, выход которого подключен к второму входу установки в О п-го триг- гера флага группы и к входу установки в О триггера пропуска команды, вход установки в 1 и инверсный выход которого подключены соответственно к входу признака пропуска очередной команды устройства и к второму входу первого элемента И, вход запроса вндачи очередной команды устройства подключен к третьему входу первого элемента И и к третьему входу установки в О h-го триггера флага группы .

0

5

0

5

/3

11

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для преобразования формата данных в доменной памяти | 1985 |

|

SU1368919A1 |

Устройство для выборки команд относится к области цифровой вычислительной техники и может быть использовано в качестве блока памяти команд с предварительной выборкой для ЦВМ, к которым предъявляются по- вьшенные требования по быстродействию и энергопотреблению. Целью изобретения является упрощение устройства. Устройство содержит счетчик адреса, блок памяти, группу регистров, группу элементов И, группу триггеров флага пропуска команды и два элемента И. Устройство обеспечивает выполнение следующих функций: прием начального адреса команды; запись информации из оперативной памяти в первый регистр буфера команд; выдачу по запросу очередной команды из пос- ( леднего регистра буфера команд; пропуск очередной команды по соответствующему сигналу. 1 ил. (Л ю сд ю а:

| Королев Л.Н | |||

| Структуры ЭВМ и их математическое обеспечение | |||

| - М.: Наука, 1978 | |||

| Устройство для выборки команд | 1984 |

|

SU1149257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-02-20—Подача