Изобретение относится к импульсной технике и может быть использовано при построении синтезаторов частоты.

Известно устройство, содержащее управляющий делитель частоты с двумя коэффициентами деления, программирующий счетчик, блок введения единичных приращений, делитель частоты с переменным коэффициентом деления (ДПКД), управляемый преобразователь параллельного кода в последовательный, входную и выходную шины [1]

Целые коэффициенты деления реализуются делителями с двумя коэффициентами деления и с переменным коэффициентом деления и программирующим счетчиком с дискретностью, равной единице по командам с блока управления.

Дробные коэффициенты деления реализуются управляемым преобразователем параллельного кода в последовательный и блоком введения единичных приращений путем изменения в отдельных циклах деления на единицу общего коэффициента деления.

Введение дробных коэффициентов деления приводит к появлению в спектре выходного сигнала нежелательных дискретных составляющих, кратных минимальной дискретности дробного коэффициента деления. Их амплитуда ослаблена в N (N коэффициент деления всего делителя) раз по отношению к уровню основного сигнала. Наличие дискретных составляющих (при малых значениях N, соизмеримых с уровнем основного сигнала) недостаток данного устройства и всех делителей частоты с дробным переменным коэффициентом деления (ДДПКД).

Наиболее близким по технической сущности к предлагаемому устройству является выбранный в качестве прототипа делитель частоты с дробным переменным коэффициентом деления, состоящий из делителя частоты с переменным коэффициентом деления, блока изменения кода на ±1, сумматора и двух накопителей кода. Выбор коэффициентов деления (частоты синтезатора) производится по шинам управления n1 (целые) и n2 (дробные) [2]

ДПКД реализует целые коэффициенты деления в соответствии с кодом, поступающим по шине n1. При коде, соответствующем числу ноль на шине n2, по выходу переноса первого накопителя кода сигнала не будет, а на выходах суммы код с равной вероятностью может соответствовать любому числу в пределах емкости накопителя кода. Если код суммы не соответствует числу ноль, то второй накопитель кода будет формировать сигнал переноса, а блок изменения кода на ±1 через сумматор будет изменять код на ±1. В результате будет формироваться последовательность коэффициентов деления N-1, N, N+1, причем количество циклов деления с коэффициентами N-1 и N+1 равно между собой и циклы деления следуют друг за другом, а с коэффициентом деления N может быть любое количество циклов деления. В этом случае средний коэффициент деления будет равен N.

При включении дробных коэффициентов деления по шине n2 код суммы первого накопителя кода будет меняться с каждым тактовым импульсом, а это значит, что частота сигнала переноса второго накопителя кода будет иметь переменный "набегающий" характер, а импульсы переноса первого накопителя кода будут суммироваться с кодом, соответствующим любому коэффициенту деления. Тогда ДПКД будет делить на N-1, N, N+1, N+2. Происходит как бы "маскировка" сигнала переноса с первого накопителя. В результате, в спектре выходного сигнала уровень дискретных составляющих (дробных помех), возникающих за счет дробного деления, будет уменьшен в N2 раз, хотя и появляются другие частотные составляющие, но их уровень будет значительно меньше дробной помехи.

Так как накопитель кода содержит регистр, то после включения источника питания при выключенных дробных коэффициентах деления код суммы первого накопителя кода может с равной вероятностью соответствовать любому коэффициенту деления, в том числе и единице младшего дробного разряда. Этот же код может оставаться и при выключении дробных разрядов. В этом случае при реализации целых коэффициентов деления в спектре выходного сигнала будет дискретная составляющая, стабильная по частоте и уровнем, равным уровню дробной помехи, как если бы работал первый накопитель кода.

Возможность формирования дробной помехи при реализации целых коэффициентов деления это недостаток данного ДДПКД. Этим же недостатком обладают и ДДПКД, которые построены по такому же принципу и в которых заложен этот метод уменьшения дробной помехи, в синтезаторах частоты [3] [4]

Задача настоящего изобретения повышение чистоты спектра выходного сигнала ДДПКД при делении на целые коэффициенты.

Использование предлагаемого устройства позволит получить чистый спектр выходного сигнала ДДПКД при делении на целые коэффициенты.

Решение задачи достигается тем, что в делитель частоты с дробным переменным коэффициентом деления, который состоит из делителя частоты с переменным коэффициентом деления, сумматора, двух накопителей кода и блока изменения кода на ± 1, введен блок анализа, который следит за включением дробных разрядов и управляет работой второго накопителя кода.

Включение блока анализа может иметь несколько вариантов:

1) вход блока анализа подключен к шине управления дробными разрядами. В этом случае блок анализа может быть реализован на n-входовой схеме совпадения или n-входовой схеме контроля четности;

2) вход блока анализа подключен к выходу переноса первого накопителя кода. В этом случае могут быть применены RC-цепь, постоянная времени которой на 20-30% больше периода частоты следования импульсов переноса при единице младшего дробного разряда, если счетчик с емкостью хотя бы на единицу больше емкости первого накопителя кода.

Во всех вариантах выход блока анализа подключен к запрещающему входу второго накопителя кода и блокируют его при нулевом коде на шине управления дробными коэффициентами деления.

При появлении кода управления, отличного от нуля, или первого импульса переноса блокировка снимается и второй накопитель кода начинает работать.

Сопоставительный анализ показывает, что предложенное техническое решение отличается от прототипа тем, что введенный блок анализа следит за периодом следования импульсов переноса или кодом управления и при отключении дробных разрядов блокирует второй накопитель кода, что позволяет исключить формирование нежелательных дискретных составляющих в спектре выходного сигнала ДДПКД при делении на целые коэффициенты.

Поэтому данное техническое решение отвечает критерию "новизна".

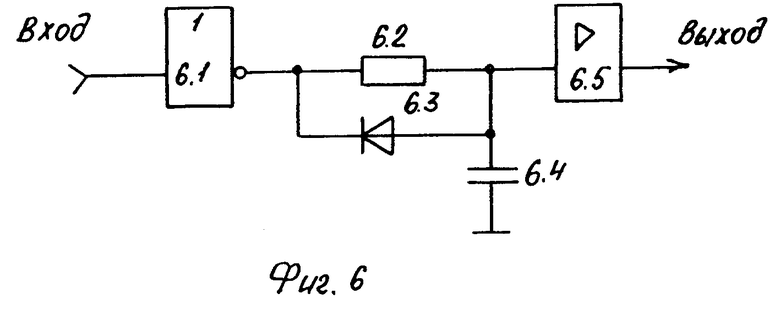

На фиг. 1 представлена структурная схема делителя частоты с дробным переменным коэффициентом деления, содержащая делитель 1 с переменным коэффициентом деления, сумматор 2, первый 3 и второй 4 накопители кода, блок 5 изменения кода на ± 1, блок 6 анализа, шины входную 7 и выходную 8, шину 9 тактовой частоты, первую n1 и вторую n2 кодовые шины.

Вход ДПКД 1 подключен к входной шине 7, выход к выходной шине 8, а группа информационных входов соединена с группой информационных выходов 2, группа информационных входов которого подключена к первой кодовой шине n1 шине управления целыми коэффициентами деления. Вход переноса сумматора 2 подключен к входу блока анализа 6 и выходу переноса первого накопителя 3 кода, группа информационных входов которого соединена со второй кодовой шиной n2 шиной управления дробными коэффициентами деления, а группа информационных выходов его подключена к группе информационных входов второго накопителя 4 кода. Выход переноса второго накопителя 4 кода соединен с первым входом блока 5 изменения кода на ±1, два выхода которого подключены ко входам сумматора 2, кроме того шина 9 тактовой частоты подключена к тактовым входам накопителей кода 3 и 4 и ко второму входу блока 5 изменения кода на ±1, а выход блока 6 анализа соединен с запрещающим входом накопителя 4 кода.

На фиг. 1 приведена схема устройства, в котором в качестве блока 6 анализа применена TC-цепь.

Рассмотрим работу устройства. На входную шину 7 подадим сигнал частотой F, а на шину 9 тактовой частоты подадим сигнал частотой F/N (при описании работы устройства в качестве тактовой частоты можно использовать выходной сигнал ДПКД 1). На шину n1 подадим код, соответствующий коэффициенту деления N, а на шину n2 нулевой код. В этом случае по выходу переноса накопителя 3 кода будет постоянный уровень, на выходе блока 6 анализа будет также постоянный уровень, который запрещает работать накопителю 4 кода, хотя код на его информационных входах может быть любой, на входах сумматора 2 будут постоянные уровни, так как импульсы переноса с накопителя 4 кода отсутствуют. Код шины n1 будет поступать на ДПКД 1 без изменений, а это значит, что ДПКД 1 будет делить на коэффициент деления N. При включении дробных разрядов первый импульс переноса изменит выходной уровень блока 6 анализа и снимет запрет с накопителя 4 кода, в результате чего ДПКД 1 будет работать, как сказано выше при описании ДДПКД в прототипе.

При отключении дробных разрядов импульсы переноса исчезнут и выходной уровень блока 6 анализа изменится и заблокирует накопитель 4 кода.

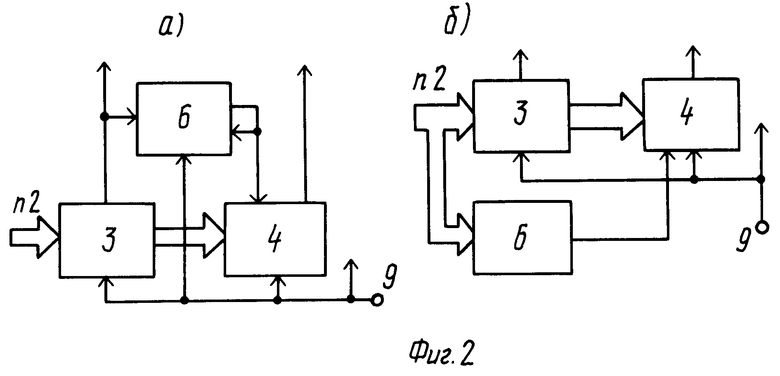

На фиг. 2, а приведена схема включения блока 6 анализа, выполненного на счетчике. В этом случае тактовый вход блока 6 анализа подключен к шине 9 тактовой частоты, выход переноса накопителя 3 соединен с запрещающим входом блока 6 анализа, выход которого подключен к собственному входу установки и к запрещающему входу накопителя 4 кода.

В исходном состоянии счетчик в блоке 6 анализа находится в заполненном состоянии, а выходной уровень удерживает его в этом состоянии. При появлении первого импульса переноса с накопителя 3 кода счетчик установится в ноль, выходной уровень изменения и накопитель 4 кода начнет работать. Каждый очередной импульс переноса устанавливает счетчик в ноль, таким образом счетчик все время остается незаполненным, поскольку, как указано выше, емкость счетчика больше емкости накопителей кода. Когда импульсы переноса прекратятся, то через некоторое время счетчик заполнится и его выходной уровень заблокирует накопитель 4 кода и этот же уровень будет удерживать счетчик в заполненном состоянии.

На фиг. 2,б приведена схема блока 6 анализа, который выполнен на схеме совпадения, например по нулям, или схеме контроля четности. Вход блока 6 анализа подключен к шине управления дробными разрядами, а выход к запрещающему входу накопителя 4 кода.

Если дробные разряды отключены, то выходной уровень блока 6 анализа блокирует накопитель 4 кода, а при включении дробных разрядов блокировка снимается.

Таким образом, применение предлагаемого изобретения позволит получить спектр выходного сигнала ДДПКД при делении на целые коэффициенты чистым.

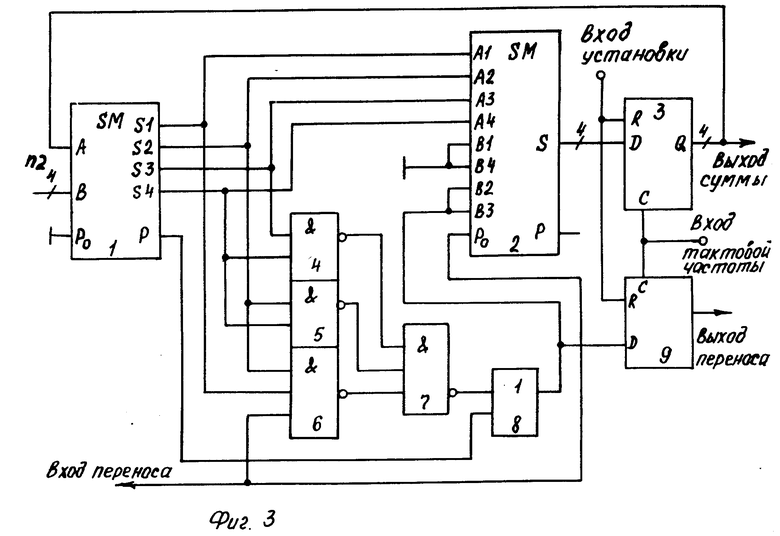

На фиг. 3 приведена схема, по которой разработана и серийно выпускается микросхема К04ИМ002 КПМ3.543.012ТУ формирователь команд дробности (четырехразрядный двоично-десятичный накопитель кода).

Схема состоит из двух четырехразрядных двоичных сумматоров 1 и 2, четырехразрядного регистра 3, логических элементов 4.8 и D-триггера 9. Сумматор 2 и логические элементы 4.8 предназначены для коррекции, чтобы из двоичного накопителя получить двоично-десятичный. Логические элементы формируют сигнал тогда, когда код суммы сумматора 1 будет соответствовать числу 10 или более, а сумматор 2 добавляет к этому код числа 6 по входам с весовыми коэффициентами 2 и 4.

Рассмотрим пример, когда по шине n2 поступает код числа 3. На шину переноса, на вход Ро сумматора 1 и на вход установки подадим логический ноль. Код числа 3 через сумматоры 1 и 2 поступает на входы регистра 3. Первый тактовый импульс запишет этот код в регистр 3, который подается на входы А сумматора 1, и на его выходах суммы будет код числа 6, который через сумматор 2 поступает на регистр 3. Второй тактовый импульс запишет этот код и на выходах сумматора 1 будет код числа 9, который через сумматор 2 поступит на регистр 3. Третий тактовый импульс запишет этот код в регистр 3 и на выходах сумматора 1 будет код числа 12. Логические элементы сформируют сигнал коррекции, который добавит в сумматор 2 число 6. На выходах суммы сумматора 2 будет код числа 2 (12 + + 616 + 2). Четвертый тактовый импульс запишет в регистр 3 код числа 2 и сигнал коррекции в D-триггер 9, который будет импульсом переноса. Следующие импульсы переноса будут сформированы седьмым и десятым тактовыми импульсами.

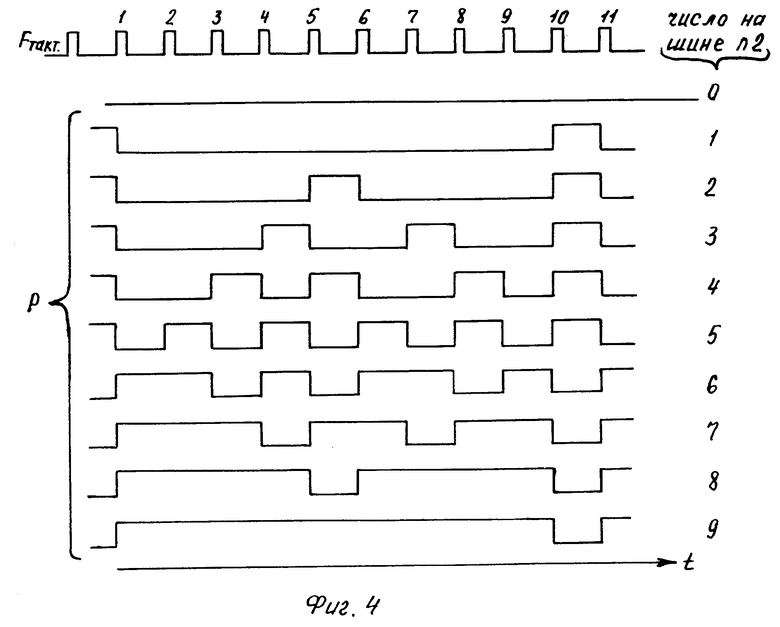

На фиг. 4 приведены формы импульсов переноса при различных кодах (числах) на кодовой шине n2.

По этой же схеме разработана и серийно выпускается микросхема 1528ХМ2-0062 АЕЯР 431260.045ТУ формирователь команд дробности (два двоично-десятичных накопителя кода).

Цифровой двоично-десятичный накопитель по упрощенной схеме (коррекция реализована на одном сумматоре 2) защищен а. с. N 783999, кл. Н 03 К 23/00.

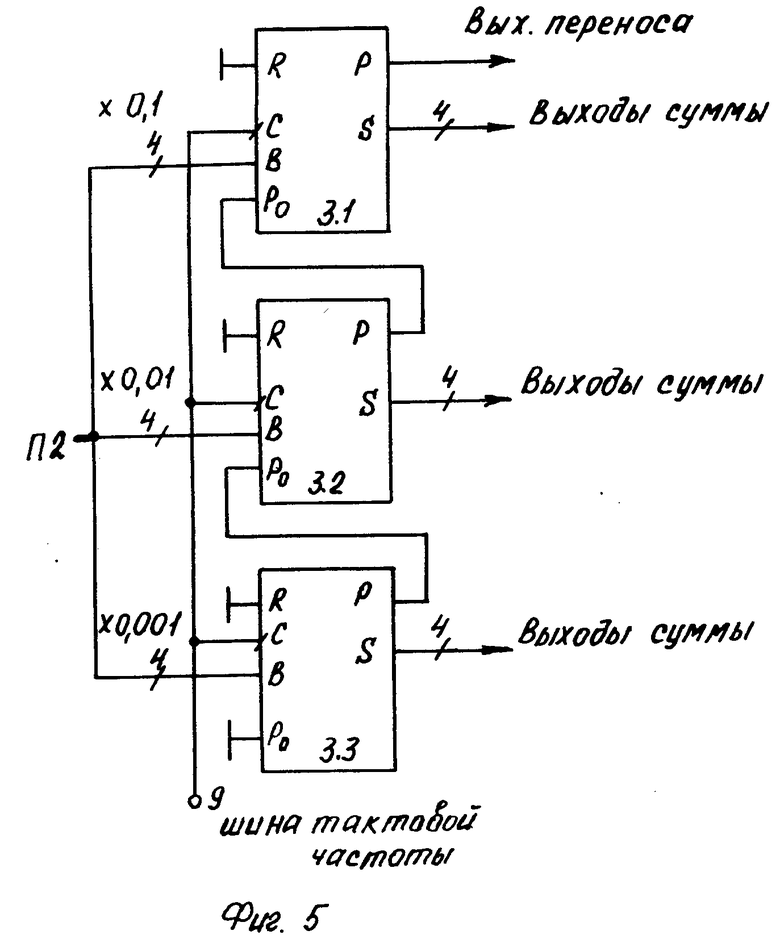

На фиг. 5 приведена структурная схема для получения трех дробных разрядов в коэффициенте деления ДДПКД. По этой схеме могут быть реализованы накопители кода 3 и 4 предложенного устройства. Входы установки R могут быть использованы в качестве запрещающего входа (входа блокировки) в накопителе 4 кода.

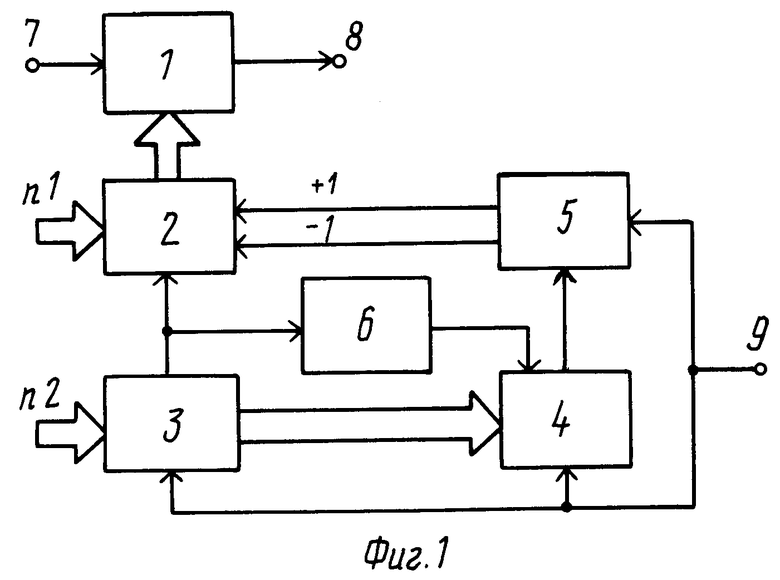

На фиг. 6 приведена схема блока 6 анализа, в котором применена RC-цепь.

Все приведенные схемы пригодны для реализации накопителей на микросхемах КМОП-технологии. Если будут применены микросхемы ТТЛ-технологии, то при описании работы накопителя на фиг. 3 на вход установки необходимо подать уровень логической единицы, как и на вход R на фиг. 5, на фиг. 6 вместо усилителя 6.5 необходимо применить инвертор.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2108659C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2001 |

|

RU2214043C2 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| ВОЗБУДИТЕЛЬ РАДИОПРИЕМНИКА | 1990 |

|

RU2119250C1 |

Изобретение относится к импульсной технике и может быть использовано при построении синтезаторов частоты. Сущность изобретения: устройство содержит: делитель с переменным коэффициентом деления 1, сумматор 2, первый и второй накопители кода 3,4, блок изменения кода на ± 1 5, блок анализа 6, входную шину 7, выходную шину 8, шину тактовой частоты 9, первую и вторую кодовые шины n 1, n 2 с соответствующими связями. 6 ил.

ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий делитель частоты с переменным коэффициентом деления ДПКД, первый и второй накопители кодов, блок изменения кода, первую и вторую кодовые шины, шину тактовой частоты, выходную шину и сумматор кодов, группа информационных выходов которого подключена к группе информационных входов делителя с переменным коэффициентом деления ДПКД, группа информационных входов к первой кодовой шине, а первый вход к выходу переноса первого накопителя кодов, группа информационных выходов которого подключена к группе информационных входов второго накопителя кодов, выход переноса которого подключен к первому входу блока изменения кода, первый и второй выходы которого подключены к второму и третьему входам сумматора соответственно, причем вторая кодовая шина подключена к группе информационных входов первого накопителя кодов, тактовый вход которого подключен к тактовому входу второго накопителя кодов, второму входу блока изменения кода и шине тактовой частоты, отличающийся тем, что в него введены входная шина, блок анализа, вход которого подключен к выходу переноса первого накопителя кодов, а выход к запрещающему входу второго накопителя кодов, а вход и выход делителя с переменным коэффициентом деления ДПКД подключены к входной и выходной шинам соответственно.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ ИЗДЕЛИЙ | 1978 |

|

RU2026268C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-08-09—Публикация

1992-03-25—Подача