(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1998 |

|

RU2153698C2 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частот с высокой линейностью закона изменения частоты | 2016 |

|

RU2635278C1 |

| Синтезатор частот | 1987 |

|

SU1467738A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2012 |

|

RU2490789C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| Цифровой синтезатор сигналов | 1984 |

|

SU1224949A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

Изобретение относится к радиотехнике и может быть использовано в технике связи, в радиолокационных и измерительных системах для формирования частот. Цель изобретения - расширение диапазона синтезируемых частот. Синтезатор содержит генератор 1 тактовых импульсов, делитель 2 частоты, блок 3 формирования кода частоты, формирователь 4 управляющего кода, накопителя 5 и 6 фазы, умножитель 7 кодов, блок 8 суммирования, распределитель 9 импульсов, регистры 10,12 и 14 памяти, блок постоянной памяти (БПП) 11, коммутатор 13, ЦАП 15 и (ФНЧ) 16. СИНТЕЗ ОТСЧЕТОВ ФАЗЫ ПРОИЗВОДИТСЯ В ПОСЛЕДОВАТЕЛЬНО СОЕДИНЕННЫХ НАКОПИТЕЛЯХ 5 И 6 ФАЗЫ, РАБОТАЮЩИХ С ТАКТОВОЙ ЧАСТОТОЙ, В N РАЗ МЕНЬШЕ ЧАСТОТЫ ГЕНЕРАТОРА 1. ВЫХОДНОЙ СИГНАЛ НАКОПИТЕЛЯ 5 ФАЗЫ - КОД ТЕКУЩЕЙ ФАЗЫ А СИНТЕЗИРУЕМОГО КОЛЕБАНИЯ, ДИСКРЕТНО МЕНЯЮЩЕЙСЯ С ШАГОМ ΔА=M .N. Умножитель 7 кодов формирует коды 2M, 3M,...(N-1)M, а в блоке 8 суммирования происходит сложение кода текущей фазы А с выходными кодами умножителя 7 кодов. БПП 11 состоит из N блоков памяти, выходы которых через коммутатор 13 подаются на вход ЦАП 15. РЕГИСТРЫ 10 И 12 СЛУЖАТ ДЛЯ ВЫРАВНИВАНИЯ ЗАДЕРЖЕК. КОММУТАТОР 13 УПРАВЛЯЕТСЯ ВЫХОДНЫМ КОДОМ РАСПРЕДЕЛИТЕЛЯ 9 ИМПУЛЬСОВ. БЫСТРОДЕЙСТВИЕ ОПРЕДЕЛЯЕТСЯ ЦАП 15, регистром 14 и коммутатором 13. 1 ил.

СП

00

;о со 35

О5

тели 5 и 6 фазы, умножитель 7 кодов, блок 8 суммирования, распределитель 9 импульсов, регистры 10, 12 и 14 па- мяти, блок постоянной памяти (БПП) 11, коммутатор 13, ЦЛП 15 и фильтр нижних частот (ФНЧ) 16. Синтез отсчетов фазы производится в последовательно .соединенных накопителях 5 и 6 фазы, работающих с тактовой частотой, в п раз меньше частоты генератора 1. Выходной сигнал накопителя 5 фазы - ;код текущей фазы-А синтезируемого ко- ; лебания,. дискретно, меняющейся с шагом

Изобретение относится к радиотехнике и может быть использовано в технике связи, в радиолокационных и измерительных системах для формировг.ни.; частот.

Цель изобретения - расширение диапазона синтезируемых частот.

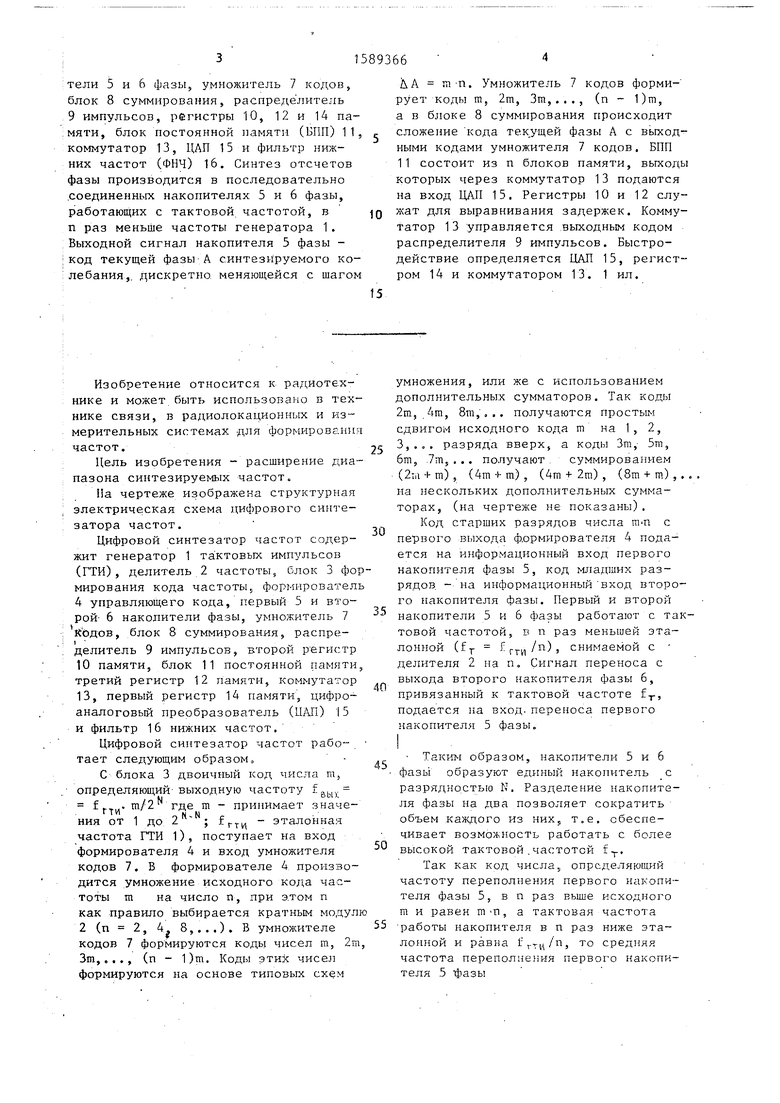

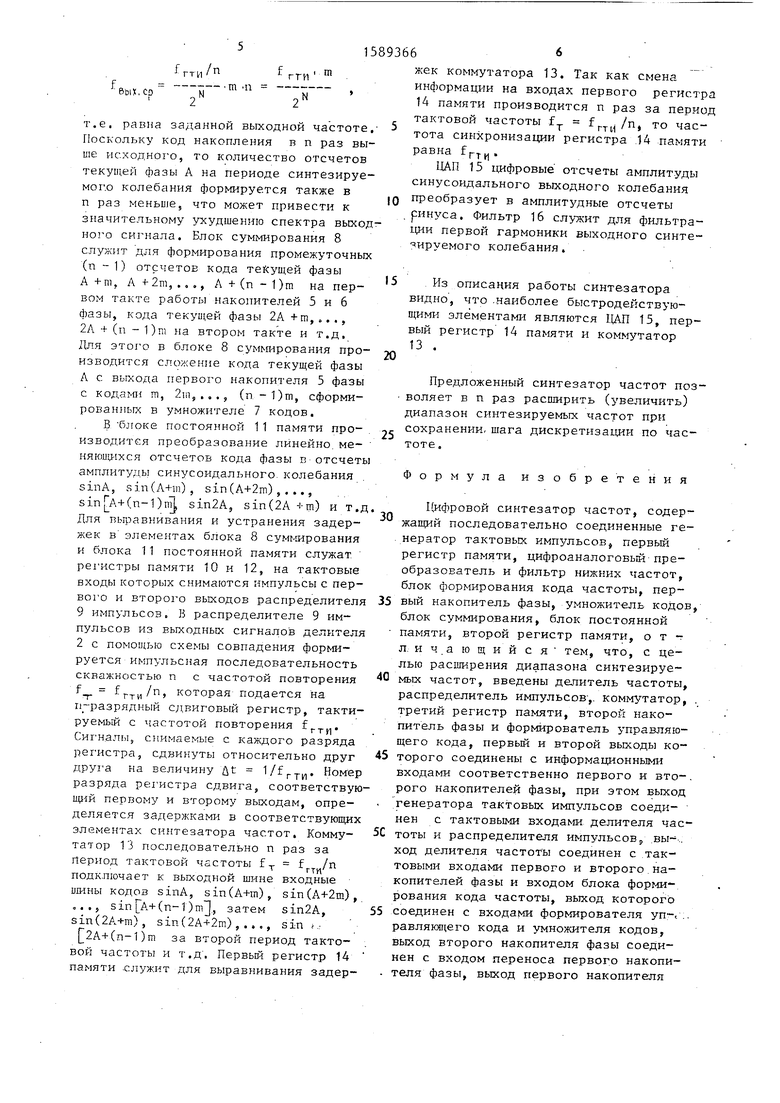

Па чертеже изображена структурная электрическая схема цифрового синтезатора частот.

Цифровой синтезатор частот содер жит генератор 1 та ктовых. импульсов (ГТИ), делитель 2 частоты, блок 3 формирования кода частоты, формирователь 4 управляющего кода, первый 5 и вто

рой 6 наколители фазы, умножитель 7 КЪдов, блок 8 суммирования, распределитель 9 импульсов, второй регистр 10 памяти, блок 11 постоянной памяти, третий регистр 12 памяти, коммутатор 13, первый регистр 14 памяти, цифро- аналоговый преобразователь (ЦАП) 15 и фильтр 16 нижних частот.

Цифровой синтезатор частот работает следующим образом,

С блока 3 двоичный код числа т, определяющий-выходную частоту fj,,yy f ,,,. m/2 где m - принимает значегти

.N-N

35

40

45

ВИЯ от 1 до 2 ; frrn эталонная частота ГТИ 1), поступает на вход формирователя 4 и вход умножителя кодов 7. В формирователе 4 производится умножение исходного кода частоты ш на число п, при э.том п как правило выбирается кратньм модулю

2 (п 2, 4. 8,...). В умножителе кодов 7 формируются коды чисел т, 2т, 3т,,.., (п - 1)т, Коды этих чисел формируются на основе типовых

hPi m-n. Умножитель 7 кодов формирует коды т. 2т, 3т,..., (п - 1)т, а в блоке 8 суммирования происходит сложение кода текущей фазы А с выходными кодами умножителя 7 кодов. БПП 11 состоит из п блоков памяти, выходы которых через коммутатор 13 подаются на вход ЦАП 15. Регистры 10 и 12 служат для выравнивания задержек. Коммутатор 1 3 управляется .выходным кодом распределителя 9 импульсов. Быстродействие определяется ДАЛ 15, регистром 14 и коммутатором 13. 1 ил.

5

0

5

0

5

5

умножения, или же с использованием дополнительных сумматоров. Так коды 2т,.4т, 8т,,.. получаются простым сдвигом исходного кода m на 1, 2, 3,.,. разряда вверх, а коды Зш, 5т, 6т, .7т,... получают. суммированием (2ш + т) , (4т + т), (4т + 2т) , (8т + т.) ,.. на нескольких дополнительных сумматорах, (на чертеже не показаны).

Код старших разрядов числа Ш П с первого выхода ф.ормирователя 4 подается на информационный вход первого накопителя фазы 5, код младших раз- ря.дов. - на информационный вход второго накопителя фазы. Первый и второй накопители 5 и 6 фазы работают с тактовой частотой, в п раз меньшей эталонной (f-p f () , снимаемой с делителя 2 на п. Сигнал переноса с выхода второго накопителя фазы 6, привязанный к тактовой частоте , подается на вход.переноса первого накопителя 5 фазы.

Такрп-1 образом, накопители 5 и 6 фазь образуют единый накопитель с разрядностью N. Разделение накопителя фазы на два позволяет сократить объем каждого из них, т.е. обеспечивает возможность работать с более высокой тактовой .частотой f.

Так как код числа, определяющий частоту переполнения первого накопителя фазы 5, в п раз выше исходного m и равен m-n, а тактовая частота работы накопителя в п раз ниже эталонной и равна fr-r./п, то средняя частота переполнения первого накопителя 5 фазы

f

/n

f

m

ГТИ ГТП

---- ---Гт.е. paBiia заданной выходной частоте Поскольку код накопления в n раз выше исходного, то количество отсчетов текущей фазы А на периоде синтезируемого колебания формируется также в п раз меньше, что может привести к значительному ухудшению спектра выхоного сигнала. Блок суммирования 8 служит для формирования промежуточны (п -1) отсчетов кода текущей фазы А +ш, А -г2т, ., ., А + (п - От на первом такте работы накопителей 5 и 6 фазы, кода текущей фазы 2А+т,..., 2А + (п - Dm на втором такте и т.д. Для этого в блоке 8 суммирования производится сложение кода текущей фазы А с выхода первого накопителя 5 фазы с т, 2in, . . . , (n-l)ni, сформированных в умножителе 7 кодов.

В -блоке постоянной 11 памяти производится преобразование линейно, ме- няшиц-геся отсчетов кода фазы в отсчеты амплитуды синусоидального, колебания sinA, sin(AH-in), sin(A+2m), . .., (n-1)nij, sin2A, sin(2A -i-m) и т.д Для выравнивания и устранения задержек в элементах блока 8 сумг-ирования и блока 11 постоянной памяти служат регистры памяти 10 и 12, на тактовые входы которых снимаются импульсы с первого и второго выходов распределителя 9 импульсов. В распределителе 9 импульсов из выходных сигналов делителя 2 с помощью схемы совпадения формируется импульсная последовательность скважностью п с частотой повторения -1- гти/ которая подается на п-разрядный сд,виговый регистр, тактируемый с частотой повторения f Сигналы, снимаемые с каждого разряда регистра, сдвинуты относительно друг друга на величину t 1/f п-,. Номер разряда регистра сдвига, соответствую- первому и второму выходам, определяется задержками в соответствующих элементах синтезатора частот. Коммутатор 13 последовательно п раз за Период тактовой частоты подключает к

ошны кодов sinA, sin(A+m), sin(A+2m), ,.., (n-r)m3, затем sin2A SLn(2A+m), sin(2A+2m),..., sin..:

2А+Сп-1)т за второй период тактовой частоты и т.д. Первый регистр 14 памяти .служит для выравнивания задер„ т f,,«/n выходной шине входные

93666

жек коммутатора 13. Так как смена информации на входах первого регистра 14 памяти производится п раз за период 5 тактовой частоты f fгти/п, то частота синхронизации регистра 14 памяти равна fp.

ЦАП 15 цифровые отсчеты амплит.уды синусоидального выходного колебания 10 преобразует в амплитудные отсчеты .ринуса. Фильтр 16 служит для фильтрации первой гармоники выходного синтезируемого колебания. .

15

20

25

Из описания работы синтезатора видно , что .наиболее быстродействующими элементами являются ЦАП 15, первый регистр 14 памяти и коммутатор

Предложенный синтезатор частот поз- воляет в п раз расширить (увеличить) диапазон синтезируемых частот при сохранении, шага дискретизации по частоте.

Формула изобретения

30

35

40

Цифровой синтезатор частот, содер- последовательно соединенные ге- .нератор тактовых импульсов первый регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, блок формирования кода частоты, первый накопитель фазы, умножитель коДов, блок суммирования, блок постоянной памяти, второй регистр памяти, о т т л. и ч .а ю щ и и с я тем, что, с целью расширения диапазона синтезируемых частот, введены делитель частоты, распределитель импульсов-,, коммутатор, третий регистр памяти, второй накопитель фазы и формирователь управляющего кода, первый и второй выходы которого соединены с информационными входами соответственно первого и вто-, рого накопителей фазы, при этом выход .генератора тактовых импульсов соеди- - нен с тактовыми входами делителя частоты и распределителя импульсов,, .вы-... ход делителя частоты соединен с .тактовыми входами первого и второго накопителей фазы и входом блока формирования кода частоты, выход которого 5 соединен с входами формирователя уп- :. равляклцего кода и умножителя кодов, выход второго накопителя фазы соединен с входом переноса первого накопи- теля фазы, выход первого накопителя

5

С

фазы и выходы умножителя кодов соединены с соответствукхцими входами блока суммирования, выходы блока суммирования соединены с соответствующими вхо- дами второго регистра памяти, выходы которого соединены с соответствующими входами блока постоянной памяти, выходы которого соединены с соответствую- прми входами третьего регистра памяти, тактовые входы второго и третьего регистров памяти соединены соответственно с первым и вторым выходами распределителя импульсов, выход которого соединен,с входом управления коммутатора, выход которого соединен с вхо -; дом первого регистра памяти, разрядный выход делителя частоты соединен с входом распределителя импульсов, выходы третьего регистра памяти соединены с соответствующими входами коммута- .тора.

| Цифровой синтезатор сигналов | 1984 |

|

SU1224949A1 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-04—Подача