Изобретение относится к цифровым вычислительным системам и, в частности, к шинному интерфейсу (мосту) между двумя шинами.

Описание известного уровня техники.

В компьютерных системах электронные микросхемы и другие компоненты соединены друг с другом с помощью шин. С шиной могут быть соединены разные компоненты, при этом шина обеспечивает обмен информацией между всеми устройствами, подсоединенными к шине. Широкое распространение получила шина ISA (промышленной стандартной архитектуры). Шина ISA имеет двадцать четыре (24) адресных проводника шины, которые обеспечивают поддержку до шестнадцати (16) мегабайт памяти. Широкое распространение шин стандарта ISA привело к тому, что значительная доля устройств проектируется на использование с шиной ISA. Однако высокоскоростные устройства ввода/вывода, обычно используемые в современных компьютерных системах, нуждаются в более скоростных шинах.

Решение общей проблемы передачи и приема данных от процессора в любое высокоскоростное входное устройство связано с использованием локальной шины. В отличие от шины ISA, которая функционирует относительно медленно и имеет ограниченную ширину полосы пропускания, локальная шина осуществляет обмен данными с системной скоростью блоками по 32 бит. Устройства локальной шины с интерфейсами, которые требуют высокого быстродействия, например, при работе с памятью, дисплеем и дисководами, вынесены из основной системной шины. Одной из таких локальных шин, которая получила широкое распространение в промышленности, является шина PCI (межсоединения периферийных компонент). Шина PCI может представлять собой 32- или 64-разрядную магистраль для высокоскоростной передачи данных. По существу, шина PCI является параллельным трактом, дополняющим шину ISA. К примеру, системный процессор и память могут быть подсоединены к шине PCI непосредственно. К шине PCI могут быть также подсоединены и другие устройства, такие как адаптеры графического дисплея, контроллеры дисководов, звуковые платы и т.п., либо непосредственно, либо косвенным образом (например, через главный мост).

Микросхема моста (именуемая далее "мостом") подключается между шиной PCI и шиной ISA, для того чтобы обеспечить обмен между устройствами на этих двух шинах. Мост по существу преобразует циклы шины ISA в циклы шины PCI и наоборот.

Многие из устройств, подключенных к шине PCI и шине ISA, являются основными (задающими) устройствами, способными производить обработку информации независимо от шины или других устройств. Некоторые устройства, подключенные к шинам, рассматриваются как подчиненные ("ведомые") устройства или устройства - "адресаты", которые воспринимают команды и реагируют на запросы основного устройства. Многие устройства в определенных обстоятельствах способны выполнять роль как основных, так и подчиненных устройств.

Желательно создать мост между PCI шиной и ISA шиной, обладающий некоторыми функциональными возможностями, такими как распределение /сбор данных; взаимодействие с дисководом, имеющим встроенный контроллер, (IDE); арбитраж PCI и т.д. По меньшей мере для некоторых из этих целей в мосте предусмотрены подчиненные устройства. Эти подчиненные устройства должны взаимодействовать с шиной PCI согласно протоколу шины PCI, изложенному в Спецификации на PCI. Однако обеспечение требуемых функциональных возможностей в мосте в течение определенного времени отклика, требуемого шиной PCl, становится весьма проблематичным, если мост выполнен с использованием относительно недорогих средств с невысоким быстродействием, например, 0.8-микронной КМОП-технологии. Возникает проблема, связанная с необходимостью фиксации состояния сигналов, принимаемых от шины PCI в качестве входных сигналов в мосте, а также сигналов, передаваемых в шину PCI из моста, для обеспечения использования этих сигналов подчиненными устройствами, выполненными по технологии с невысоким быстродействием. Эта двухтактная задержка, обусловленная фиксацией состояния, несовместима с протоколом шины PCI.

В патенте США N 4864496 описан модуль шинного адаптера для шин межсоединения в многошинной компьютерной системе, в которой сигналы управления в шине межсоединения формируются указанным модулем и синхронизируются синхронизатором, управляемым высокоскоростным тактовым сигналом шины.

Сущность изобретения.

Имеется потребность в компьютерной системе, использующей мост, который обеспечивает требуемые функциональные возможности и может быть реализован по технологии с относительно невысоким быстродействием, но при этом способен поддерживать протокол шины PCI.

Соответственно в данном изобретении предлагается компьютерная система, содержащая первую шину, вторую шину для передачи сигналов управления от ведущего устройства к подчиненному устройству, и имеющая специальный шинный протокол, по меньшей мере одно ведущее устройство, подключенное ко второй шине, и мост, включенный между первой и второй шинами, причем мост включает третью шину с внутренней фиксацией состояния для передачи сигналов управления от ведущего устройства к подчиненному устройству с фиксацией их состояния, по меньшей мере одно подчиненное устройство, средство фиксации состояния, включенное между второй и третьей шинами, для фиксации состояния сигналов управления от ведущего устройства к подчиненному устройству, получаемых из второй шины, и сигналов управления от ведущего устройства к подчиненному устройству с зафиксированным состоянием, получаемых из третьей шины, и логическое устройство, включенное между второй и третьей шинами, причем логическое устройство выполнено с возможностью контроля состояния сигналов управления на второй шине и возбуждения по меньшей мере одного из сигналов управления на второй шине в соответствии с протоколом шины в ответ на некоторые заданные состояния контролируемых сигналов управления.

В предпочтительном варианте воплощения изобретения вторая шина является шиной стандарта PCI (межсоединение периферийных компонент), а протокол шины является протоколом шины PCI.

Настоящее изобретение обеспечивает преимущества, с точки зрения экономичности, моста, который может быть реализован, например, с использованием 0.8-микронной КМОП-технологии, поскольку для подчиненных устройств стандарта PCI обеспечивается фиксация состояний сигналов управления, передаваемых в шину PCI и принимаемых от шины PCI. Однако в то же время протокол шины PCI поддерживается с помощью логического устройства, контролирующего незафиксированные сигналы управления и реагирующего на заранее заданные состояния сигналов управления в соответствии с протоколом шины PCI. Это освобождает подчиненные устройства стандарта PCI от необходимости реагирования при определенных обстоятельствах на сигналы управления в шине PCI внутри интервалов времени, определяемых протоколом шины PCI.

Краткое описание чертежей.

Теперь на примере со ссылками на прилагаемые чертежи будет описан вариант воплощения данного изобретения, где:

фиг. 1 - перспективное изображение компьютерной системы, в которой может быть воплощено настоящее изобретение;

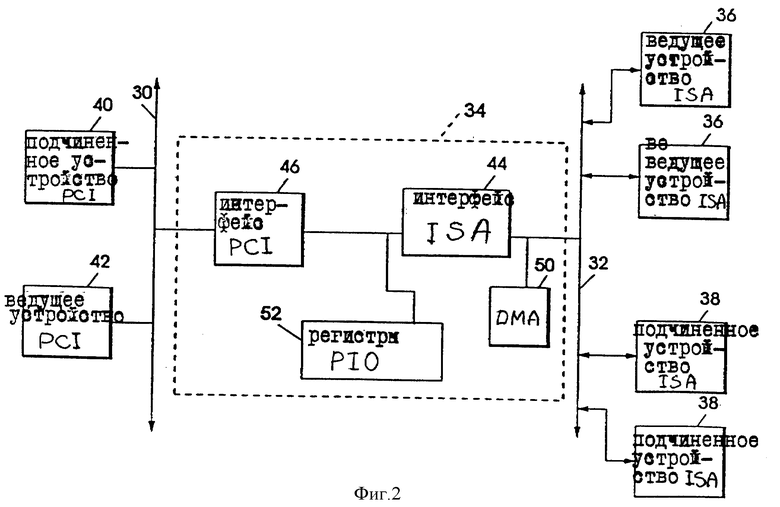

фиг. 2 - блок-схема варианта воплощения изобретения, входящего в состав компьютерной системы по фиг. 1;

фиг. 3 - блок-схема микросхемы моста в варианте воплощения настоящего изобретения;

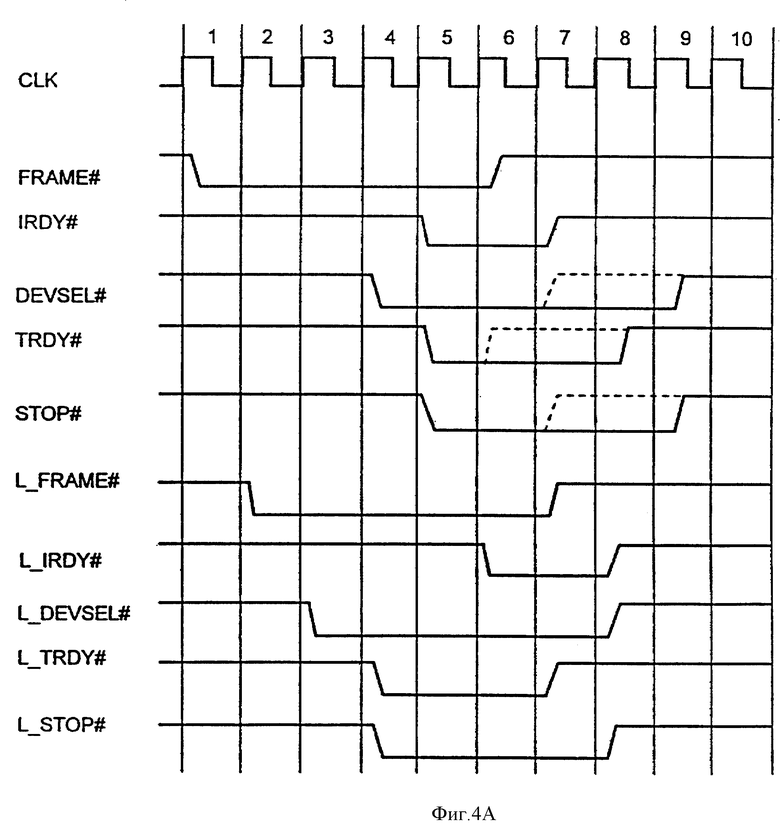

фиг. 4A - F - временные диаграммы передач сигналов между шиной PCI и микросхемой моста согласно настоящему изобретению для различных ситуаций.

Описание иллюстративных варианта(ов) воплощения изобретения.

На фиг. 1 представлен обычный компьютер, или PC (персональный компьютер) 10, с которым может быть использовано настоящее изобретение. Компьютер 10, который предпочтительно, но не обязательно, может относиться к классу персональных компьютеров IBM или подобным системам, содержит системный блок (корпус) 12, в котором размещаются схемные платы, содержащие необходимые схемы, в том числе плата микропроцессора и микросхемы BIOS (базовая система ввода-вывода), контроллеры, оперативное запоминающее устройство и другие аппаратные средства. Компьютер также содержит видеотерминал 14 и клавиатуру 16, соединенную с корпусом 12 посредством кабеля 18. Внешние запоминающие устройства включают накопитель на жестких дисках, который находится внутри корпуса и недоступен пользователю, и накопители на гибких дисках, доступные пользователю, а также, как вариант, дисководы CD ROM (ПЗУ на компакт-дисках) 20 и 22.

На фиг. 2 представлена блок-схема компьютерной системы, построенной согласно варианту воплощения настоящего изобретения. Система содержит шину PCI 30 и шину ISA 32 вместе с множеством ведущих устройств ISA 36 и подчиненных устройств ISA 38. Множество подчиненных устройств памяти PCI 40 (в протоколе PCI определены как "устройства-адресаты", далее называются "подчиненными устройствами") и ведущих устройств PCI 42 подключены к шине PCI 30.

Мост 34 содержит схему интерфейса ISA 44, подключенную между шиной ISA 32 и внутренней системной шиной 46. Между шиной PCI 30 и системной шиной 46 предусмотрена схема интерфейса PCI 48. Мост 34 имеет также контроллер DMA (прямого доступа к памяти) 50 и программируемые регистры ввода/вывода (PIO) 52. В числе других функций микросхема моста 34 обеспечивает интерфейс между шиной PCI 30 и шиной ISA 32. Интерфейс ISA 44 преобразует циклы шины ISA в циклы системной шины для микросхемы моста 34. Контроллер DMA 50 обеспечивает управление доступом к памяти в системе.

На фиг. 3 представлена блок-схема элементов интерфейса PCI 48, который позволяет выполнить мост по технологии с невысоким быстродействием и при этом тем не менее соответствовать протоколу PCI. Специалистам должно быть ясно, что интерфейс PCI 48 содержит и другие элементы для осуществления преобразования циклов PCI в циклы внутренней системной шины. Эти элементы здесь не показаны, чтобы не затруднять понимание сущности данного варианта воплощения изобретения.

PCI интерфейс 48 соединен со множеством подчиненных устройств PCI 64, 66, 68, размещенных в мосте 34. Эти подчиненные устройства PCI 64 - 66 выполняют различные необходимые функции, которые могут быть реализованы на мосту 34, такие как распределение/сбор данных, взаимодействие с дисководом с встроенным контроллером, арбитраж PCI и т.п.

Поскольку мост 34 реализован по технологии с невысоким быстродействием, для получения приемлемой стоимости микросхемы, подчиненные устройства PCI 30 64 - 68 также выполнены по технологии с невысоким быстродействием и не могут обнаруживать и реагировать на сигналы управления в шине PCI 30, состояния которых не зафиксированы. Таким образом для подчиненных устройств PCI 64 - 68 в месте 34 необходимо обеспечить фиксирование состояния сигналов управления, передаваемых в шину PCI 30 и поступающих от нее.

Фиксация состояния сигналов посредством PCI интерфейса 48, передаваемых к шине PCI 30 и поступающих от нее, обеспечивается обычными средствами фиксации (ключевыми схемами с фиксацией состояния 60). Ключевая схема с фиксацией состояния 60 подключена к шине PCI 30 для приема сигнала кадра (FRAME# ) и сигнала готовности инициатора (IRDY#) и посылки сигнала готовности адресата (TRDY#), сигнала останова (STOP#) и сигнала выбора устройства (DEVSEL#). Ключевая схема с фиксацией состояния 60 подсоединена также к шине PCI 62 с внутренней фиксацией состояния и обеспечивает копии фиксированных состояний вышеупомянутых сигналов в шине PCI 62. Сигналы с фиксацией состояний обозначены как L_FRAME#, L_IRDY#, L_TRDY#, L_DEVSEL# и L_STOP#.

Фиксация состояний сигналов в обоих направлениях добавляет задержку на два такта в циклы обмена между ведущим устройством PCI 42 и подчиненными устройствами PCI 64 - 68. Шина PCI 30 не рассчитана на то, чтобы при двухтактной задержке поддерживать данный протокол.

Для того, чтобы решить эту проблему задержки, вызванную необходимостью фиксировать состояние сигналов в обоих направлениях, согласно настоящему изобретению предусмотрена ключевая схема с фиксацией состояний PCI 48 вместе с логическим устройством интерфейса PCI 70, которое подключено к шине PCI 30. Как будет более подробно описано далее, логическое устройство интерфейса PCI 70 контролирует внешние PCI сигналы управления и сигналы управления подчиненных устройств и возбуждает сигналы управления в шине PCI 30 в соответствии с протоколом шины PCI.

Конфигурация логического устройства 70 определяется конкретной шиной, с которой используется логическое устройство 70, например шиной PCI 30 в рассматриваемом иллюстративном варианте. Для каждого из сигналов STOP#, DE7SEL# и TRDY# предусмотрен конечный автомат для поддержания протокола шины PCI. Конфигурация конечных автоматов для выполнения функций контроля и возбуждения сигналов управления в соответствии с протоколом шины PCI может быть осуществлена специалистами в данной области техники без особых затруднений.

Вследствие взаимодействия подчиненных устройств 64 - 68 с PCI шиной 62 с фиксацией состояний, могут возникнуть следующие проблемы:

(1) останов подчиненного устройства при попытке передачи пакетов при установлении сигнала TRDY# подчиненного устройства при неустановленном внешнем сигнале FRAME#;

(2) непакетные передачи и

(3) останов подчиненного устройства при попытке передачи пакетов, когда сигнал TRD появился прежде, чем сброшен внешний сигнал FRAME#, и т.п.

Хотя сигналы и протокол шины PCI хорошо известны специалистам, кратко опишем сущность взаимосвязи сигналов, которые показаны на временных диаграммах на фигурах 4A - F.

Сигнал FRAME# устанавливается ведущим устройством (или "инициатором"), указывая подчиненным устройствам, что ведущее устройство начинает транзакцию.

Сигнал IRDY# (готовность инициатора) устанавливается ведущим устройством, указывая, что ведущее устройство готово посылать и принимать данные.

Сигнал DEVSEL# (выбор устройства) устанавливается подчиненным устройством для уведомления ведущего устройства, что подчиненное устройство осведомлено о том, что именно оно выбрано для выполнения транзакции с ведущим устройством.

Сигнал TRDY# (готовность адресата) устанавливается подчиненным устройством, указывая, что подчиненное устройство (или "адресат") готово для посылки и приема данных.

Сигнал STOP# устанавливается подчиненным устройством, указывая ведущему устройству, что нет возможности обработки транзакции.

В примере воплощения настоящего изобретения логическое устройство 70 берет на себя управление сигналами DEVSEL#, STOP# и TRDY# (эти сигналы посылаются из подчиненного устройства) в шести различных ситуациях. Первая из них - когда ведущее устройство 42 пытается передавать данные пакетами на подчиненное устройство, у которого нет пакетного режима (например, подчиненное устройство PCI 64), с помощью последнего сигнала IRDY#. Временная диаграмма для этой ситуации представлена на фиг. 4A. (На всех временных диаграммах префикс "L_" означает сигналы с фиксацией состояния, являющиеся внутренними сигналами для моста 34, в то время как отсутствие префикса указывает на сигналы без фиксации состояния, являющиеся внешними для моста 34. Также пунктирная линия показывает сигнал, который был сформирован логическим устройством 70). Поскольку подчиненному устройству PCI 64 не известно, является ли передача пакетной, либо непакетной, подчиненное устройство PCI 64 устанавливает L_ STOP# на четвертом такте цикла. Сигнал STOP# посылается от микросхемы в шину PCI 30 на пятом такте цикла. Для того, чтобы переслать данные, ведущее устройство 42 активизирует сигнал IRDY#. Ведущее устройство 42 отслеживает также установленный сигнал STOP# на шестом такте и делает таким образом неактивным сигнал FRAME# для завершения цикла. Сигнал TRDY# должен устанавливаться только на один такт, поскольку подчиненное устройство PCI 64 не поддерживает пакетную транзакцию. Следовательно, логическое устройство интерфейса PCI 70 снимает сигнал TRDY# на шестом такте. После снятия сигнала TRDY# протокол PCI требует, чтобы были сняты сигналы DEVSEL#, TRDY# и STOP# (все сигналы подчиненных устройств). Следовательно, протокол PCI требует, чтобы сигналы STOP# и DEVSEL# были сняты через такт после снятия сигнала FRAME#, то есть, на седьмом такте. Без логического устройства интерфейса PCI 70 настоящего изобретения эти сигналы нельзя было бы установить в неактивное состояние, пока не наступит девятый такт, поскольку сигнал с фиксацией состояния L_ FRAME не воспринимается подчиненным устройством 64, пока не наступит седьмой такт, воспринимается на восьмом такте и посылается из микросхемы на девятом такте. Подчиненное устройство PCI 64 таким образом не знает, что цикл должен быть завершен за достаточное время в соответствии с протоколом шины PCI.

Логическое устройство интерфейса PCI 70, которое непрерывно контролирует внешние сигналы управления, т.е. сигналы управления без фиксации состояния, распознает неактивный сигнал FRAME# как ситуацию, требующую завершения цикла. Соответственно логическое устройство PCI 70 на седьмом такте устанавливает сигналы STOP#, DEVSEL# и TRDY# в неактивное состояние, поддерживая таким образом протокол шины PCI.

Из вышеприведенного описания и остальных временных диаграмм должно стать очевидным, как функционирует логическое устройство интерфейса PCI 70. Например, ситуация на фиг. 4B появляется, когда ведущее устройство 42 пытается передавать данные пакетами на подчиненное устройство 84, у которого нет пакетного режима, с помощью последнего сигнала TRDY#, и цикл должен быть завершен вместе с прекращением работы с адресатом. Прекращение работы с адресатом определяется подчиненным устройством, снимающим сигнал L_DEVSEL# и устанавливающим сигнал L_STOP#. После приема сигнала STOP# на пятом такте сигнал FRAME# устанавливается ведущим устройством в неактивное состояние. Сигнал STOP# должен устанавливаться в неактивное состояние логическим устройством интерфейса PCI 70 на следующем такте (сигналы DEVSEL# и TRDY# уже в неактивном состоянии) для поддержки протокола шины.

Третий случай (фиг. 4C) появляется, когда ведущее устройство 42 осуществляет пакетную передачу с непосредственным сигналом IRDY#, а подчиненное устройство PCI 84 прекращает работу с адресатом, переводя в неактивное состояние сигнал L_DEVSEL# и в активное состояние сигнал L_STOP#. В этом случае протокол шины PCI требует, чтобы сигнал FRAME# был установлен в активное состояние (что выполняется ведущим устройством 42), а сигнал STOP# был установлен в неактивное состояние (логическим устройством интерфейса PCI 70) через один такт после того, как сигнал FRAME# становится неактивным после прекращения работы с адресатом. Логическое устройство интерфейса PCI 70, которое контролировало сигналы без фиксации состояний, должно установить в неактивное состояние только сигнал STOP#, поскольку сигналы DEVSEL# и TRDY# уже неактивны.

Четвертый случай (фиг. 4D) появляется, когда ведущее устройство 42 выполняет непакетную передачу с последующим сигналом IRDY4# и прекратилась работа с адресатом. В этом случае сигнал FRAME# устанавливается в неактивное состояние ведущим устройством 42 после того, как ведущее устройство 42 обнаруживает активным сигнал STOP#. Сигнал STOP# снова устанавливается в неактивное состояние логическим устройством интерфейса PCI 70 через такт после того, как снимается сигнал FRAME# для того, чтобы поддерживать протокол шины PCI. В противном случае, сигнал L_STOP# не был бы неактивным на шине PCI 30 в течение других двух циклов, что нарушило бы протокол шины PCI.

Пятый случай (фиг. 4E) возникает, когда ведущее устройство 42 выполняет непакетную передачу и работа с адресатом не прекращена. В этом случае подчиненное устройство PCI 64 устанавливает L_STOP# на четвертом такте, воспринимаемый ведущим устройством 42 в виде сигнала STOP# на пятом такте. Ведущее устройство 42 реагирует на это, сбрасывая сигнал FRAME# на шестом такте. Сигналы STOP# , TRDY# и DEVSEL# должны все быть сброшены на седьмом такте, поскольку сигнал FRAME# был снят на шестом такте. Поскольку подчиненное устройство PCI 64 не может достаточно быстро установить эти сигналы в неактивное состояние вследствие фиксации состояния сигналов, логическое устройство интерфейса PCI 70 устанавливает сигналы в неактивное состояние для поддержания протокола шины PCI.

Шестой случай (фиг. 4F) возникает, когда ведущее устройство выполняет пакетную передачу на подчиненное устройство 64, не имеющее пакетного режима, с непосредственным сигналом IRDY# . Сигнал L_STOP# устанавливается подчиненным устройством PCI 64 на четвертом такте, воспринимается ведущим устройством 42 на пятом такте, что заставляет ведущее устройство сбросить сигнал FRAME# . После того, как сигнал FRAME# сброшен, сигналы DEVSEL# и STOP# должны быть установлены в неактивное состояние на шестом такте для поддержания протокола шины PCI, причем сигнал TRDY# в этом случае уже является неактивным.

Как можно понять из вышерассмотренных примеров, настоящий вариант воплощения изобретения предусматривает наличие логического устройства интерфейса PCI 70, которое контролирует внешние сигналы управления без фиксации состояний и в некоторых случаях берет на себя задачу возбуждения внешних сигналов подчиненных устройств в шине PCI 30 в соответствии с протоколом шины PCI. Это дает возможность реализовать мост 34, содержащий подчиненные устройства 64 - 68, по технологии с невысоким быстродействием, не требующей высоких затрат за счет использования сигналов с фиксацией состояний для поддержки протокола шины PCI.

Изобретение относится к цифровым вычислительным системам, в частности к шинному интерфейсу (мосту) между двумя шинами. Техническим результатом является создание моста между двумя шинами, реализованного по технологии с относительно невысоким быстродействием, но при этом способного поддерживать протокол шины РСI. Компьютерная система содержит первую, вторую и третью шины, мост, ведущее устройство, подчиненное устройство и ключевую схему с фиксацией состояний. 2 с. и 11 з.п. ф-лы, 4 ил.

| US 4864496 А, 05.09.89 | |||

| US 5341495 А, 23.08.94 | |||

| US 5664124 А, 02.11.97 | |||

| US 5455915 А, 03.10.95 | |||

| US 5533204 А, 02.07.96 | |||

| US 5535341 А, 09.07.96 | |||

| US 5548730 А, 20.08.96 | |||

| US 5519872 А, 21.05.96 | |||

| Артвик Б.А | |||

| Сопряжение микроЭВМ с внешними устройствами | |||

| - М.: Машиностроение, 1983, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Басиладзе С.Г | |||

| Интерфейсы магистрально-модульных многопроцессорных систем | |||

| - М.: ЭНЕРГОАТОМИЗДАТ, 1992, с | |||

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

Авторы

Даты

1999-10-27—Публикация

1995-11-23—Подача