ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к системам обработки данных, в частности к интерфейсу между динамическими или синхронизируемыми интегральными схемами в системе обработки данных.

ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

В современных системах обработки данных требуется производить перенос данных между динамическими или синхронизируемыми схемами, реализованными в системе в виде большого числа микросхем. Так, например, перенос данных между центральными процессорами (ЦП) в мультипроцессорной системе или между ЦП и системой памяти, которая может включать контроллер памяти и внекристальный кэш. Передача данных производится синхронно, и данные должны поступать в микросхему на предварительно заданном такте работы системы. По мере роста быстродействия ЦП скорость работы интерфейса между микросхемами (длительность такта шины) стала ограничивающим фактором, так как время ожидания в интерфейсе превосходит период тактовой частоты системы. С целью поддержания синхронизации системы, при ее разработке приходится ограничивать быстродействие шины, чтобы не происходило смешивания тактов прихода данных.

Для пояснения на фиг.1А показана структурная схема известного интерфейса связи между двумя интегральными схемами, микросхемой 102 и микросхемой 104 в системе обработки данных. Каждая из микросхем 102 и 104 получает опорный тактовый сигнал 106, связанный с системой 108 фазовой автоподстройки частоты (ФАПЧ). ФАПЧ 108 генерирует локальный тактовый сигнал, тактовый сигнал 110 в микросхеме 102, и тактовый сигнал 111 в микросхеме 104, которые синхронизируются по опорному тактовому сигналу 106. Опорный тактовый сигнал 106 обеспечивает "начало отсчета времени", и может прослеживаться для многих периодов локальных тактовых сигналов 110 и 111, в зависимости от степени умножения ФАПЧ 108. Тактовый сигнал 113 шины получается из опорного тактового сигнала 106 посредством деления делителем 112 локального тактового сигнала 110 на предварительно заданное целое число N. Данные, направляемые из микросхемы 102 в микросхему 104, фиксируются по предварительно заданному фронту деленного локального тактового сигнала 111, и направляются в линию 116 передачи данных с помощью драйвера 118. Данные принимаются приемником 120 и фиксируются целевой схемой-защелкой 122 по предварительно заданному фронту деленного локального тактового сигнала 110 микросхемы 104. В связи с физическим разделением микросхем 102 и 104, данные поступают на вход 124 целевой схемы-защелки 122 с задержкой. (Вклад, вносимый в задержку приемником 120, обычно является небольшим по сравнению с задержкой, вызываемой передачей данных). Время задержки, также называемое временем ожидания, будет рассматриваться далее с использованием фиг.1Б.

Аналогичным образом микросхема 104 направляет данные микросхеме 102 по линии 126 передачи данных. Данные, направляемые из микросхемы 104, фиксируются схемой-защелкой 128 по предварительно заданному фронту выходного сигнала делителя 130, который делит локальный тактовый сигнал 111 на N. Данные направляются в линию 126 передачи данных драйвером 132, и через приемник 136 захватываются целевой схемой-защелкой 134. Поступающие в микросхему 102 данные захватываются схемой-защелкой 134 по предварительно заданному фронту выходного сигнала делителя 130, который также делит на N локальный тактовый сигнал 110.

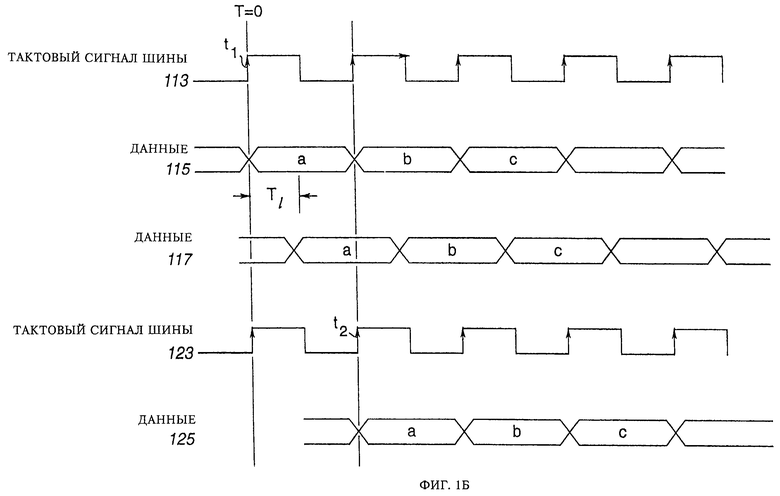

На фиг.1Б приведен пример временной диаграммы для известного интерфейса 100, показанного на фиг.1А. Фиксация данных 115, направляемых из микросхемы 102 в микросхему 104, производится схемой-защелкой 114 по нарастающему фронту t1 тактового сигнала 113 шины. Тактовый сигнал 113 шины генерируется посредством деления на N локального тактового сигнала 110 делителями 112 и 130 микросхемы 102. После задержки, вызываемой временем ожидания T1, данные 117 поступают на вход схемы-защелки 122, и фиксируются по нарастающему фронту t2 тактового сигнала 123 шины. Тактовый сигнал 123 шины генерируется посредством деления на N локального тактового сигнала 111 делителями 112 и 130 микросхемы 104. Таким образом, в известном интерфейсе, показанном на фиг. 1Б, данные 125 поступают в микросхему 104 через один такт работы шины после их направления из микросхемы 102. На фиг.1Б имеется нулевой сдвиг по фазе между тактовыми сигналами 113 шины и тактовыми сигналами 123 шины.

Если для интерфейса 100, показанного на фиг.1А, будет увеличена тактовая частота шины, время ожидания может превысить один такт работы шины. При этом может возникнуть ситуация, временная диаграмма для которой показана на фиг. 1В. Как и ранее, данные 115 фиксируются по фронту t1 тактовых сигналов 113 шины. Данные 117 поступают на вход 124 схемы-защелки 122 через время ожидания T1, превышающее период тактовых сигналов 113 шины и тактовых сигналов 123 шины. В микросхеме 104 данные 117 фиксируются по фронту t3 тактовых сигналов 123 шины, чтобы получить в микросхеме 104 данные 125. Если интерфейс 100 между микросхемами 102 и 104 является интерфейсом, имеющим максимальное время ожидания среди множества интерфейсов, имеющихся между микросхемой 102 и множеством других микросхем системы обработки данных, тогда время ожидания продолжительностью два такта, показанное на фиг.1В, соответствует "целевому" такту передачи и приема данных между микросхемами, например, между микросхемой 102 и микросхемой 104. Целевой такт представляет собой предварительно заданный такт, в который микросхемой ожидается получение данных. В ранее известных вариантах для обеспечения синхронной работы используется заполнение для интерфейсов с меньшим временем ожидания. За счет заполнения для более быстрых путей интерфейса 100 время ожидания оказывается больше одного такта шины и меньше двух тактов шины, что позволяет поддерживать синхронизацию данных.

Для пояснения ниже рассмотрена фиг.1Г, на которой показано множество 101 микросхем, в которое входят микросхемы 102, 103 и 104. Микросхемы 102 и 104 соединены "медленным" путем 152 с большим временем ожидания Ts. Микросхема 103 соединена с микросхемой 102 "быстрым" путем 154 с малым временем ожидания TF. "Номинальный" путь, соединяющий множество 101 микросхем 102-105 имеет время ожидания ТМ, совпадающее со временем ожидания для пути 156 между микросхемой 102 и микросхемой 105.

Дополнительные подробности показаны на временной диаграмме на фиг.1Д. На фиг. 1Д показана временная диаграмма, аналогичная диаграмме на фиг.1В, на которой целевой такт захвата данных в принимающей микросхеме равен двум тактам шины. На фиг.1Д показано номинальное время ожидания ТМ, равное 1,5 тактам шины, время ожидания TF для быстрого пути, превышающее один такт шины, и время ожидания Ts для медленного пути, меньше двух тактов шины. В этом случае каждая из множества микросхем 101, показанных на фиг.1Г, будет получать данные на целевом такте через два такта шины после отправки данных.

Если, однако, быстрый путь будет еще короче, то будет потеряна синхронизация данных для времени ожидания, соответствующего короткому пути. В этом случае данные будут поступать в микросхему 103 до момента перехода t2 тактового сигнала 103 шины микросхемы, что показано пунктирным изображением части данных 117 для микросхемы 103, и фиксация этих данных для микросхемы 103 будет происходить через один такт шины. Это показано пунктирным изображением части данных 125 для микросхемы 103. С целью восстановления синхронизации потребуется использовать заполнение для быстрого пути 154 между микросхемами 102 и 103, чтобы увеличить время ожидания для быстрого пути до значения TF. В результате этого процессы синхронизации в таком известном интерфейсе настраиваются для конкретного диапазона работы и определенной длины интерфейса, и они действительны только для технологии, для которой была разработана и проанализирована конструкция.

Аналогичным образом к потере синхронизации приведет увеличение тактовой частоты микросхем, показанных на фиг.1Г. Для лучшего понимания приводится конкретный пример, для которого период локального тактового сигнала сначала будет равен 1 наносекунде (нc). Тактовый сигнал шины будет иметь период, равный периоду локального тактового сигнала, умноженному на фиксированный множитель, равный в данном случае двум. Предположим, что номинальное время ожидания ТМ для интерфейса будет составлять 3 нc с вариацией +/-0,99 нc, т. е. для наилучшего случая быстрого пути значение TF будет равно 2 нc, а для наихудшего случая медленного пути значение Ts будет равно 4 нc. Данные будут поступать после двух наносекунд и до четырех наносекунд. В связи с этим интерфейс будет действовать во всех условиях, т.е. гарантируется поступление данных после первого такта шины и до второго такта шины. Однако, если быстродействие микросхем будет увеличено и период тактового сигнала будет составлять 0,9 нc, то период тактового сигнала шины изменится до 1,8 нc. С целью обеспечения наличия достаточного времени для распространения данных по интерфейсу в условиях наихудшего случая, данные не должны захватываться до истечения 2,5 тактов шины или 4,5 нc, так как длительность двух тактов шины будет меньше времени ожидания Ts для медленного пути, или 4 нc. Кроме того, чтобы обеспечить возможность работы при периоде такта шины 1,8 нc, самые быстрые данные могут прибывать через 1,5•1,8= 2,7 нc (на один такт шины раньше), что позволит обеспечить для всех условий прибытие данных на одном и том же такте. Однако для вышеприведенных значений времени ожидания самым ранним будет момент прибытия данных по быстрому пути со значением TF, равным 3 нc - 0,99 нc=2,01 нc. Таким образом, работа с периодом такта шины 1,8 нc не может поддерживаться традиционной системой синхронизации. С целью обеспечения синхронной работы соотношение тактовых периодов шины и процессора должно быть уменьшено, по крайней мере, до 3:1, и функционирование должно вестись при длительности тактового периода 2,7 нc (2,7 нc•1,5 такта=4,05 нc, и 2,7 нc•0,5 такта=1,35 нc), что делает нецелесообразным повышение частоты локального тактового сигнала.

Таким образом, существует потребность в создании устройств и способов, обеспечивающих передачу данных между микросхемами системы обработки данных с увеличенной тактовой частотой. В частности, существует потребность в наличии способов и устройств, обеспечивающих синхронизацию данных между микросхемами системы обработки данных, в которой время ожидания для различных путей отличается более чем на один такт работы шины, и в которых устранена необходимость введения дополнительной аппаратной задержки, предназначаемой для конкретной конструкции.

Задачей настоящего изобретения является создание технических решений, позволяющих устранить вышеописанные недостатки.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

На основании настоящего изобретения предлагается устройство интерфейса, имеющее первое запоминающее устройство для хранения первого набора значений данных, второе запоминающее устройство для хранения второго набора значений данных, соединенную с первым и вторым запоминающими устройствами схему, используемую для последовательного вывода под управлением хотя бы одного управляющего сигнала первого значения данных из первого запоминающего устройства и второго значения данных из второго запоминающего устройства, в котором первое и второе запоминающие устройства хранят значения данных в течение предварительно заданного числа периодов первого тактового сигнала, а первая и вторая схемы выбора имеют каждая по выходу, соединенному с соответствующими входами первого и второго запоминающих устройств, первая и вторая схемы выбора имеют каждая первый вход, используемый для приема потока данных, и второй вход, соединенный с соответствующим выходом первого и второго запоминающих устройств, в котором первая и вторая схемы выбора используются для выбора и вывода сигнала одного из первых или вторых входов на основании первого и второго управляющих сигналов.

Кроме того, на основании настоящего изобретения предлагается способ обеспечения взаимодействия интегральных схем, заключающийся в том, что сохраняют первый набор значений данных в первом запоминающем устройстве, в котором каждое значение данных из первого набора хранится в течение предварительно заданного числа периодов первого тактового сигнала; сохраняют второй набор значений данных во втором запоминающем устройстве, в котором каждое значение данных из второго набора хранится в течение предварительно заданного числа периодов первого тактового сигнала; последовательно выводят первое значение данных из первого запоминающего устройства и второе значение данных из второго запоминающего устройства посредством соединения схемы с первым и вторым запоминающими устройствами и направлением в эту схему управляющего сигнала, период которого является предварительно заданным кратным периода первого тактового сигнала; принимают поток данных на первом входе первой и второй схемы выбора; направляют выходные сигналы первого и второго запоминающих устройств на второй вход первой и второй схем выбора, соответственно; направляют каждое из значений данных первого набора данных из первой цепи выбора в первое запоминающее устройство на основании первого сигнала выбора; и направляют каждое из значений данных второго набора данных из второй цепи выбора во второе запоминающее устройство на основании второго сигнала выбора.

Выше было дано довольно общее описание особенностей и технических преимуществ настоящего изобретения, чтобы было более понятным приводимое ниже его подробное описание. Далее также будут описаны дополнительные особенности и преимущества изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

С целью более полного понимания сущности настоящего изобретения и его преимуществ, дальнейшее описание будет вестись с использованием прилагаемых чертежей, на которых показано:

на фиг.1А - известный интерфейс микросхем,

на фиг. 1Б - временная диаграмма для известного интерфейса микросхем, показанного на фиг.1А,

на фиг.1В - временная диаграмма для другого варианта осуществления известного интерфейса микросхем, показанного на фиг.1,

на фиг.1Г - множество соединенных микросхем в системе обработки данных,

на фиг.1Д - временная диаграмма для множества соединенных микросхем, показанных на фиг.Г,

на фиг.2 - структурная схема аппаратной среды использования изобретения,

на фиг.3 - структурная схема интерфейса микросхем в соответствии с вариантом осуществления изобретения,

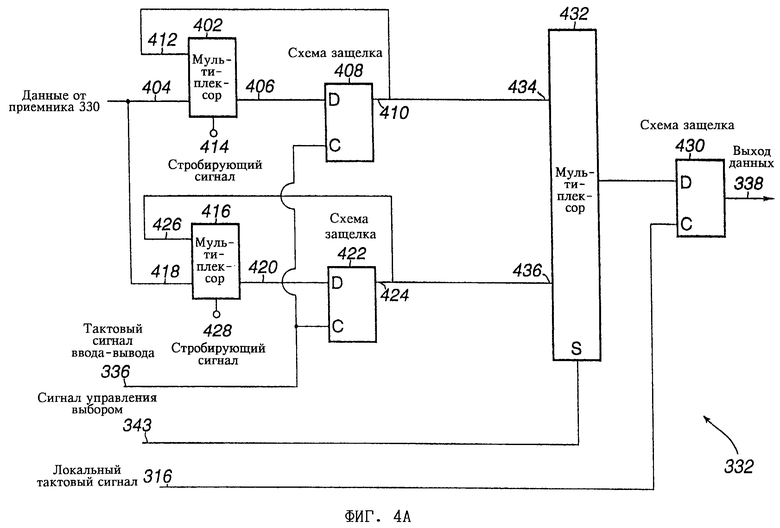

на фиг. 4А - структурная схема гибкого интерфейса в соответствии с вариантом осуществления изобретения,

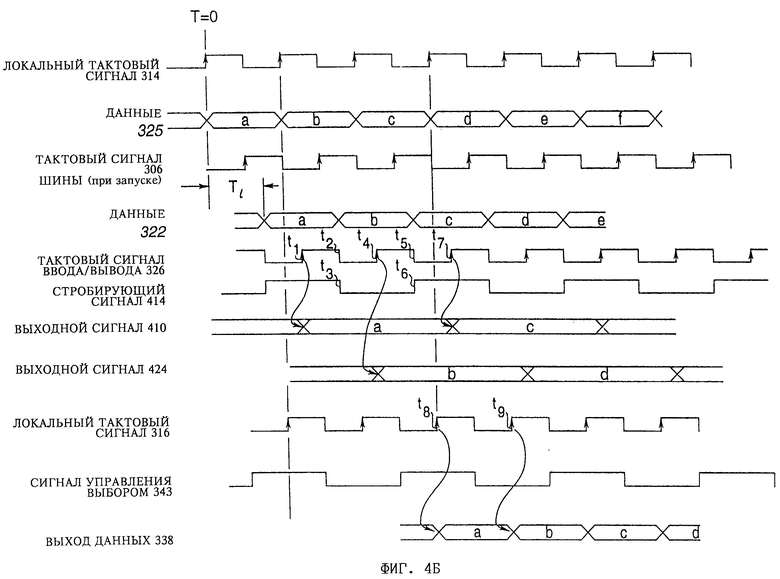

на фиг.4Б - временная диаграмма варианта осуществления изобретения, показанного на фиг.3А,

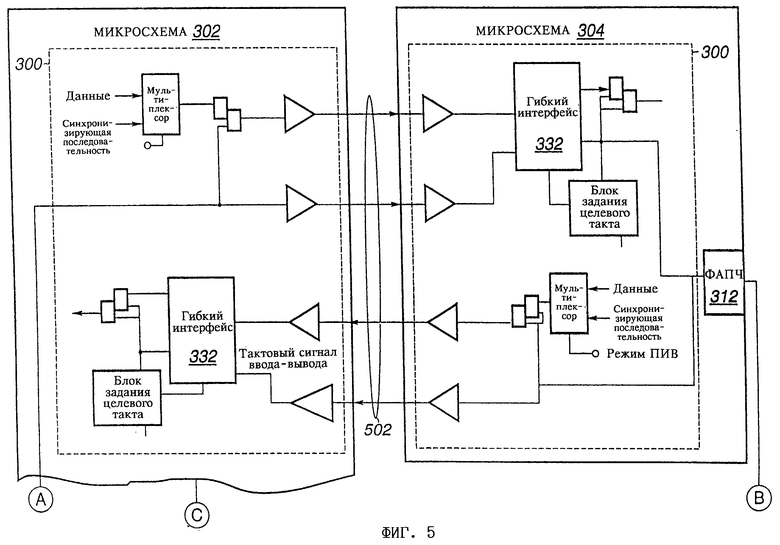

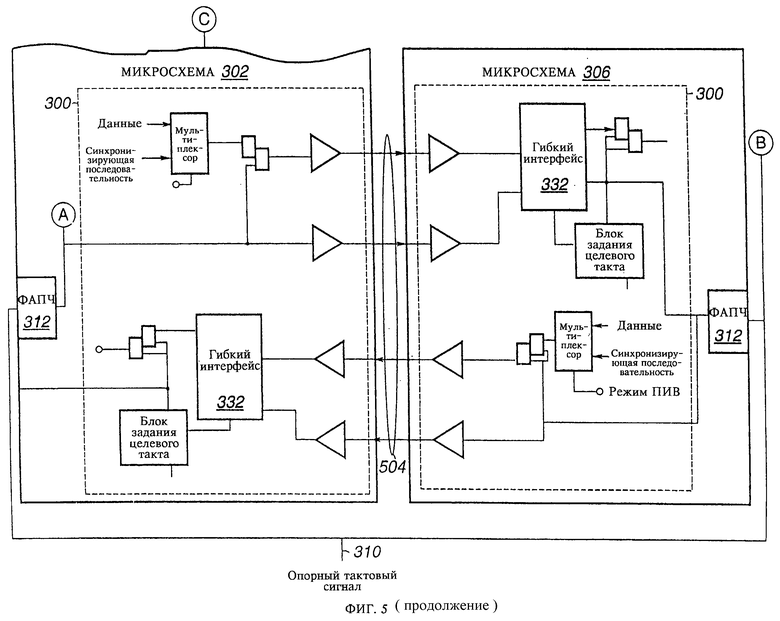

на фиг.5 - альтернативный вариант интерфейса микросхем в соответствии с изобретением,

на фиг. 6А - другой альтернативный вариант гибкого интерфейса в соответствии с изобретением,

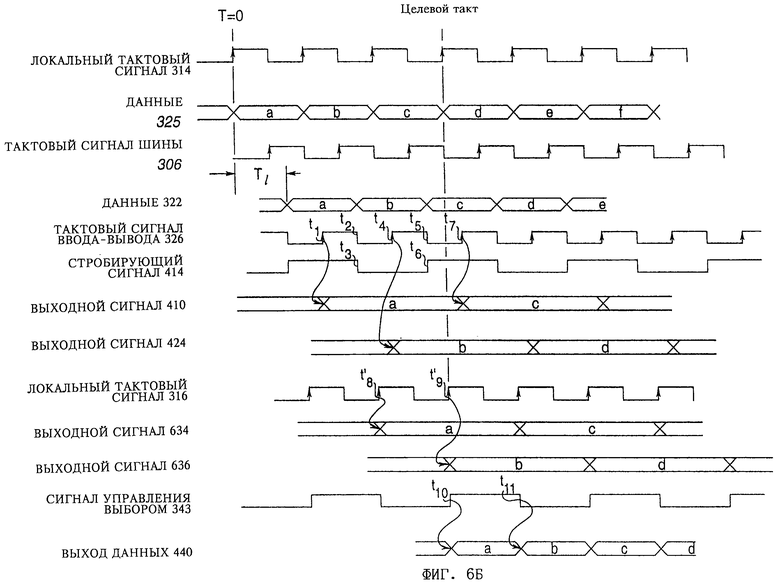

на фиг. 6Б - временная диаграмма для гибкого интерфейса, показанного на фиг.5А,

на фиг. 7А - другой альтернативный вариант гибкого интерфейса в соответствии с изобретением,

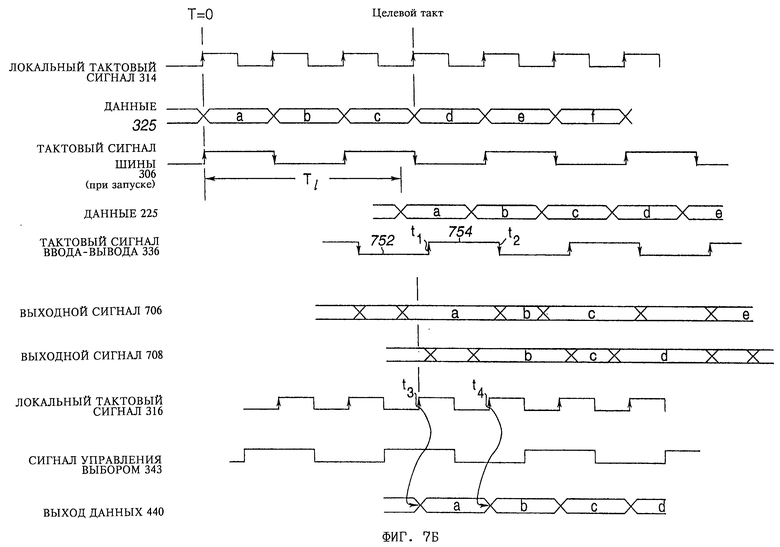

на фиг. 7Б - временная диаграмма для гибкого интерфейса, показанного на фиг.7А,

на фиг.8А - структурная схема еще одного альтернативного варианта выполнения гибкого интерфейса по изобретении и

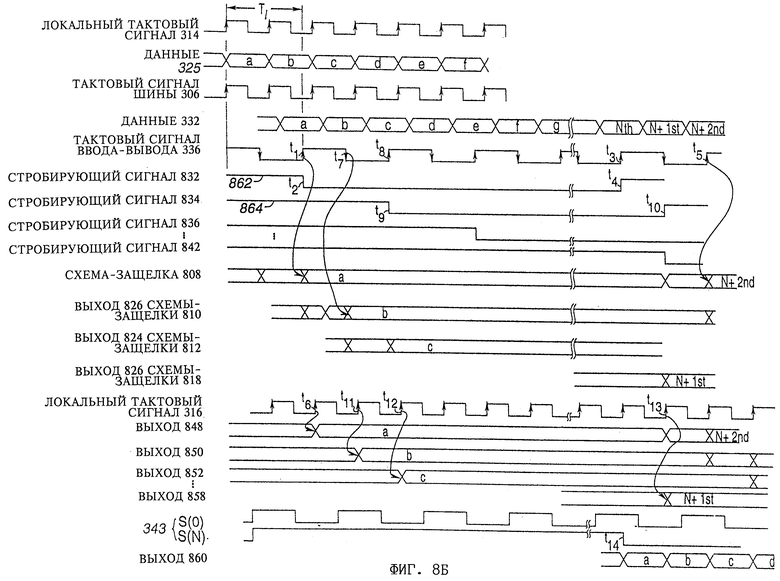

на фиг.8Б - временная диаграмма для варианта, показанного на фиг.8А.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

В изобретении предлагается гибкий интерфейсный механизм, обеспечивающий синхронизацию данных между множеством микросхем обработки данных в системе обработки данных. Синхронизация данных достигается без использования заполнения, которое приводит к усложнению физического соединения компонентов и усложняет конструкцию оборудования. "Гибкость" интерфейса компенсирует физическое различие путей, связывающих микросхемы обработки данных в системе. Посредством захвата принятых данных во множестве запоминающих элементов и избирательного управления зафиксированных данных обеспечивается синхронизация данных в системе обработки данных, в которой значения времени ожидания различаются более чем на один такт шинного обмена. Синхронизация может устанавливаться динамически за счет выполнения процедуры инициализационного выравнивания при включении питания системы или после ее сброса. Таким образом, в соответствии с изобретением синхронизация данных может достигаться без необходимости проведения временного анализа конфигурации платы и заполнения быстрых путей.

В последующем описании для наглядного пояснения настоящего изобретения приводится большое количество конкретных данных, например тактовые частоты шины и периоды синхронизации, фронты тактовых сигналов и т.д. Однако для специалистов в данной области представляется очевидным, что объем изобретения не ограничен указанием подобных конкретных данных. В некоторых случаях хорошо известные схемы представлены в описании и на чертежах в виде структурных схем, что позволяет упростить описание изобретения.

Ниже изобретение рассмотрено со ссылкой на фиг.2-9, изображенные на которых элементы не всегда воспроизведены с точным соблюдением масштаба и на которых конструктивно и/или функционально одинаковые элементы обозначены одинаковыми номерами.

На фиг. 2 показаны аппаратные средства, которые предназначены для практической реализации изобретения и которые представляют собой типичную систему 213 обработки данных в соответствии с изобретением, в состав которой входят центральный процессор (ЦП) 210, например обычный микропроцессор, и несколько других блоков, соединенных системной шиной 212. В состав системы 213 обработки данных входит далее запоминающее устройство 214 с произвольной выборкой (ЗУПВ), постоянное запоминающее устройство (ПЗУ) 216, адаптер 218 ввода-вывода, предназначенный для подключения к шине 212 периферийных устройств, например дисководов 220 и накопителей 240 на магнитной ленте, адаптер 222 пользовательского интерфейса, предназначенный для подключения к шине 212 клавиатуры 224, мыши 226 и/или других устройств, обеспечивающих взаимодействие с пользователем, например сенсорного экрана (не показан), связной адаптер 234, предназначенный для подключения рабочей станции 213 к сети обработки данных, и дисплейный адаптер 236, предназначенный для подключения шины 212 к дисплею 238. В состав ЦП 210 могут входить и другие не показанные на чертеже схемы, в том числе схемы, обычно входящие в состав микропроцессора, например функциональный модуль, блок сопряжения с шиной, арифметико-логическое устройство и т.д. Предлагаемый в изобретении интерфейс может быть включен в состав ЦП 210. Кроме того, предлагаемое в изобретении устройство может быть включено в состав запоминающих устройств, например ЗУПВ 214 (которое может включать не показанные на чертеже схемы управления памятью). ЦП 210 может быть также в составе единой интегральной схемы.

На фиг.3 показан предлагаемый в изобретении интерфейс 300. Такой интерфейс 300 встроен в каждую из микросхем 302 и 304, которые обмениваются друг с другом данными с использованием этого интерфейса 300. (Хотя настоящее изобретения проиллюстрировано на примере интерфейса, обеспечивающего взаимодействие между микросхемами, тем не менее предлагаемое в изобретении решение может использоваться и в интерфейсе, обеспечивающем взаимодействие между любой парой синхронизируемых схем-защелок). Данные между микросхемами 302 и 304 передаются со скоростью, определяемой тактовыми сигналами шины, а именно, тактовыми сигналами 306 и 308 шины. Тактовые сигналы 306 и 308 шины номинально имеют одну и ту же частоту, и формируются на основании опорного тактового сигнала 310, поступающего в ФАПЧ 312 в каждой из микросхем 302 и 304. В рассматриваемом варианте опорный тактовый сигнал 310 может являться системным тактовым сигналом. Каждая из ФАПЧ 312 выдает локальный тактовый сигнал, а именно, локальный тактовый сигнал 314 в микросхеме 302 и локальный тактовый сигнал 316 в микросхеме 304, которые синхронизированы по фазе с опорным тактовым сигналом 310 и период которых может быть равен периоду опорного тактового сигнала 310, умноженному на предварительно выбранное целое число М. Локальный тактовый сигнал 314 буферизируется драйвером 318 для выдачи тактового сигнала 306 шины с микросхемы 302. Аналогичным образом локальный тактовый сигнал 316 буферизируется драйвером 320 для выдачи тактового сигнала 308 шины с микросхемы 304.

Тактовый сигнал шины направляется микросхемой вместе с передаваемыми данными. Данные 322 из микросхемы 302 фиксируются выходной схемой-защелкой 324 и выводятся и буферизируются драйвером 326. Данные фиксируются по предварительно заданному фронту локального тактового сигнала 314. Данные принимаются с использованием мультиплексора 328. При проведении процедуры выравнивания мультиплексор 328 также принимает предварительно определенную синхронизирующую последовательность или комбинацию. Этот процесс более подробно рассмотрен ниже.

Данные 322 буферизируются приемником 330 и направляются в гибкий интерфейс 332. Тактовый сигнал 306 шины, переданный вместе с данными 322, буферизируется приемником 334, на выходе которого формируется тактовый сигнал 336 ввода-вывода, также передаваемый в гибкий интерфейс 332. Данные из микросхемы 304, передаваемые в микросхему 302 вместе с тактовым сигналом 308 шины, аналогичным образом принимаются интерфейсом 300 в микросхеме 302, и поэтому очевидно, что приведенное ниже описание гибкого интерфейса 332 в равной мере относится и к приему микросхемой 302 данных от микросхемы 304.

Блок 339 задания целевого такта задает целевой такт, на котором в принимающей микросхеме происходит фиксация данных на основании локального тактового сигнала, например, на основании локального тактового сигнала 316 в микросхеме 304. Целевой такт, подробно рассматриваемый с использованием фиг. 4А-Б, иллюстрируется на примере интерфейса 322, имеющего двукратную степень гибкости. Чтобы интерфейс имел степень гибкости Е, блок задания целевого такта может включать схему деления на Е. В дополнение к этому блок 339 задания целевого такта может иметь программируемый регистр, предназначенный для хранения предварительно заданного значения целевого такта, которое может быть загружено с использованием целевой программы 341. Значение целевого такта, запрограммированное в блоке 339 задания целевого такта микросхемы 302, может отличаться от значения целевого такта, запрограммированного в блоке 339 задания целевого такта микросхемы 304. Блок 339 задания целевого такта выдает сигнал 343 управления выбором, который в зависимости от варианта осуществления блока 332 интерфейса и соответствующей степени гибкости Е может включать множество сигналов. Сигнал 343 управления выбором будет далее рассмотрен с использованием фиг.4А-8Б, на которых показаны варианты осуществления блока 332 интерфейса.

На фиг.4А показан один из вариантов выполнения гибкого интерфейса 332 в соответствии с изобретением. В состав этого интерфейса 332 входит мультиплексор 402 с входом 404, на который поступают данные от приемника 330. Выход 406 мультиплексора 402 соединен с входом данных (D) схемы-защелки 408. Схема-защелка 408 синхронизируется тактовым сигналом 336 ввода-вывода. Схема-защелка 408 фиксирует данные на своем входе D по нарастающему фронту тактового сигнала 436, и удерживает данные до следующего нарастающего фронта тактового сигнала 336. Выход 410 схемы-защелки 408 соединен со вторым входом мультиплексора 402, с входом 412. Мультиплексор 402 под управлением стробирующих импульсов 414 выбирает вход 404 или вход 412 для вывода выходного сигнала 406.

Стробирующие импульсы 414 получаются на основании тактового сигнала 306 шины, и имеют период, в два раза превышающий период тактового сигнала 306 шины. Стробирующие импульсы 414 могут генерироваться с использованием системы автоматической подстройки по задержке (АППЗ). Один из вариантов выполнения такой АППЗ, который может использоваться в изобретении, описан в одновременно поданной заявителем заявке, озаглавленной "Динамический волновой конвейерный интерфейс и способ его применения" ("Dynamic Wave Pipelined Interface Apparatus and Method Therefor"), которая включена в настоящее описание в качестве ссылки. Фаза стробирующих импульсов 414 задается во время рассматриваемой далее процедуры инициализационного выравнивания, и действие стробирующих импульсов 414 будет далее рассмотрено с использованием фиг.4Б.

Данные от приемника RX 330 также параллельно направляются во второй мультиплексор, в мультиплексор 416, вход 418. Выход 420 мультиплексора 416 соединен с входом D второй схемы-задержки, схемы-задержки 422, для синхронизации которой также используется тактовый сигнал 336 ввода-вывода, и данные фиксируются по нарастающему фронту тактового сигнала 336 ввода-вывода, и удерживаются до следующего нарастающего фронта тактового сигнала. Выход 424 схемы-защелки 422 соединен со вторым входом, с входом 426 мультиплексора 416.

Мультиплексор 416 выбирает вход 418 или вход 426 под управлением стробирующего сигнала 428, являющегося дополнением стробирующего сигнала 414. Таким образом, когда один из мультиплексоров 402 и 416 выбирает данные, получаемые от приемника 330, другой выбирает данные, удерживаемые соответствующей схемой-защелкой, одной из схем-защелок 408 и 422. Таким образом, бит данных, ранее хранившихся в одной из схем-защелок 408 и 422, будет удерживаться в течение дополнительного периода тактового сигнала 336 ввода-вывода.

При этом создается два потока данных, каждый из которых действителен в течение двух периодов тактового сигнала 336 ввода-вывода. Ввиду обращения фаз между стробирующим сигналом 414 и стробирующим сигналом 428, два потока данных смещены относительно друг друга на длительность одного значения данных, т.е. на один период тактового сигнала 336 ввода-вывода.

Вышесказанное поясняется на фиг.4Б, на которой приведена временная диаграмма, иллюстрирующая работу гибкого интерфейса 332 по фиг.4А. Как уже описывалось выше, данные 325, хранящиеся в выходной схеме-защелке, направляются синхронно с локальным тактовым сигналом 314 микросхемы 202. Данные 322, принимаемые приемником 230 микросхемы 204, задерживаются на время ожидания для пути между микросхемами 202 и 204, как описывалось выше с использованием фиг.1Г. При нарастающем фронте t1 тактового сигнала 336 ввода-вывода, элемент данных "а" для данных 322 захватывается схемой-защелкой 408 через выход 406 мультиплексора 402. В связи с тем, что стробирующий импульс 414 является положительным или "отпирающим", то для вывода мультиплексором 402 выбираются данные от приемника 330 на входе 404. (Стробирующий импульс будет считаться отпирающим, если соответствующий мультиплексор выбирает для вывода принимаемый входной поток данных. Хотя в варианте осуществления изобретения, показанном на фиг. 4, это связано с "высоким" логическим уровнем, очевидно, что формуле изобретения соответствует и вариант его осуществления, в котором отпирающий стробирующий импульс соответствует "низкому" логическому уровню).

При этом, наоборот, стробирующий импульс 428 является отрицательным. В соответствии с этим мультиплексор 416 выбирает предыдущее значение данных, хранящееся в схеме-защелке 422, и которое направляется назад во вход D схемы-защелки 422 через мультиплексор 416. Таким образом, значение данных, хранящееся в схеме-защелке 422, сохраняется на один дополнительный период тактового сигнала 336 ввода-вывода, что позволяет получить тактовый сигнал для схем-защелок 408 и 322, как было указано при описании фиг.4А.

Как показано на фиг.3, тактовый сигнал 336 ввода-вывода получается на основании тактового сигнала 306 шины. Предполагается, что при запуске тактовый сигнал 306 шины сцентрирован в окне действительности данных, как показано на фиг. 4Б. Центрирование тактового сигнала шины описывается в одновременно поданной заявителем заявке, озаглавленной "Динамический волновой конвейерный интерфейс и способ его применения", которая включена в настоящее описание в качестве ссылки. Тактовый сигнал 306 шины испытывает такую же задержку на интерфейсе, как и данные. Время ожидания для тактового сигнала 306 шины для микросхемы 304 можно сравнить с величиной Т1, и это отражается на тактовом сигнале 336 ввода-вывода, который таким образом, центрируется по отношению к данным 322.

Стробирующие импульсы 414 генерируются таким образом, что фронты стробирующих импульсов 414 являются когерентными по фазе с задними фронтами тактового сигнала 336 ввода-вывода. На фронте t2 тактового сигнала 336 ввода-вывода устанавливается задний фронт t3 стробирующего импульса 414. При этом мультиплексор 402 выбирает для выходного сигнала 406 выходной сигнал 410 схемы-защелки 408, соединенной с входом 412 мультиплексора 402. При отрицательном значении стробирующего импульса 414 становится положительным значение стробирующего импульса 428, при этом мультиплексор 416 выбирает для вывода на выход 420 данные, поступившие от приемника 330 на вход 418. Эти данные поступают на вход D схемы-защелки 422. Полученные от приемника 330 данные теперь будут совпадать со значением элемента данных "b" для данных 322.

На фронте t4 тактового сигнала 336 ввода-вывода схемы-защелки 408 и 422 фиксируют данные на своих соответствующих входах D. Для схемы-защелки 408 эти данные соответствуют предыдущему удерживаемому значению данных, значению данных 322, которое затем удерживается в течение дополнительного периода локального тактового сигнала 416. Схема-защелка 422 фиксирует значение данных "b" на своем входе D через мультиплексор 416 на выходе 424.

При следующем переходе t7 тактового сигнала 336 ввода-вывода захватывается значение данных "с". Так как на фронте t7 увеличивается значение стробирующего сигнала 414, то значение данных 322 поступает на выход 406 мультиплексора 402. Значение данных "b" сохраняется схемой-защелкой 422, так как уменьшается значение стробирующего сигнала 428, который является дополнением стробирующего сигнала 414. Поскольку поток данных 322 продолжает поступать, гибкий интерфейс 332 продолжает генерировать два потока данных на выходах 410 и 424 схем-защелок 408 и 422, соответственно. Два потока данных содержат чередующиеся части потока входных данных 422, которые являются действительными для двух периодов локального тактового сигнала 416, как показано на фиг.4Б.

Структура потока входных данных восстанавливается посредством попеременного выбора величин из одного из двух потоков данных в синхронизации с локальным тактовым сигналом 416. Выбирается целевой такт локального тактового сигнала. Целевой такт является тактом, на котором данные захватываются целевой схемой-защелкой посредством локального тактового сигнала, например, локального тактового сигнала 316, показанного на фиг.3 и 4. Целевой такт определяется на основании анализа. Целевой такт должен наступать по времени позднее, чем время ожидания для наихудшего случая в интерфейсе. Так, например, для показанного на фиг.4Б варианта был задан целевой такт, равный трем периодам локального тактового сигнала 316 и совпадающий с фронтом t8. Целевой такт измеряется от нулевого момента времени, определяемого опорным тактовым сигналом 310, как ранее было описано для опорного тактового сигнала 106, показанного на фиг.1А. В варианте осуществления изобретения с двукратной степенью гибкости, показанном на фиг.4А и 4Б, данные могут приходить ранее целевого такта вплоть до двух периодов локального тактового сигнала. В таком варианте осуществления изобретения показанный на фиг.3 блок 339 задания целевого такта имеет схему деления на два.

При заданном целевом такте производится выбор данных для захвата целевой схемой-защелкой 430 под управлением локального тактового сигнала 316 и с использованием мультиплексора 432. В мультиплексоре 432 имеется два входа, 434 и 436. Вход 434 соединен с выходом 410 схемы-защелки 408, а вход 436 соединен с выходом 424 схемы-защелки 422. Под действием сигнала 343 управления выбором мультиплексор 422 выбирает для вывода один из двух потоков данных, представленных выходами схем-защелок 408 и 422. Когда сигнал 343 управления выбором находится в первом логическом состоянии, "высоком" для варианта осуществления изобретения, показанного на фиг.4Б, мультиплексор 432 направляет данные с входа 434 на вход D схемы-защелки 430, а когда сигнал 343 управления выбором находится во втором логическом состоянии, "низком" для варианта осуществления изобретения, показанного на фиг.4Б, данные на входе 436 мультиплексора 432 направляются на вход D схемы-защелки 430. Период сигнала 343 управления выбором в два раза превышает период локального тактового сигнала 316, и по фазе он является синхронным с локальным тактовым сигналом 316, при этом сигнал 343 управления выбором имеет первое логическое состояние и сцентрирован с целевым тактом. Таким образом, на фиг.4Б для фронта t8 локального тактового сигнала 316, значение данных "а" на выходе 410 через мультиплексор 432 направляется на вход D схемы-защелки 430, и фиксируется по фронту t8 локального тактового сигнала 316. На следующем нарастающем фронте t9 локального тактового сигнала 316, следующая порция передаваемого потока данных фиксируется целевой схемой-защелкой 430. Сигнал 343 управления выбором смещается по фазе на один полупериод и, таким образом, находится во втором логическом состоянии, при этом выход 424 схемы-защелки 422 через мультиплексор 432 соединяется с входом D схемы-защелки 430. При фронте t9 значение данных "b" на выходе 424 схемы-защелки 422 фиксируется схемой-защелкой 430, и значение данных "b" появляется на выходе 338 данных. При последующих периодах локального тактового сигнала 316 гибкий интерфейс 332 восстанавливает поток данных 225 посредством попеременного выбора выхода 410 схемы-защелки 408, и выхода 424 схемы-защелки 422.

До передачи данных через гибкий интерфейс 322, предварительно должен быть инициализирован стробирующий сигнал 414 (и при этом дополнительный к нему стробирующий сигнал 428). В связи с тем, что время ожидания для интерфейса может изменяться в пределах свыше одного периода локального тактового сигнала, то стробирующий сигнал 414 должен быть инициализирован с правильной фазой. Как уже описывалось выше, период стробирующего сигнала 414 в два раза превышает период тактового сигнала 336 ввода-вывода и локального тактового сигнала 316. По фазе стробирующий сигнал 414 синхронизирован с тактовым сигналом 316 ввода-вывода таким образом, что плоская часть импульсов стробирующего сигнала 414 сцентрирована по предварительно выбранным фронтам тактового сигнала 336 ввода-вывода, по фронтам нарастания в варианте осуществления изобретения, показанном на фиг.4Б.

В варианте осуществления настоящего изобретения стробирующий сигнал 414 может инициализироваться посредством передачи синхронизирующей последовательности при включении питания или при сбросе системы. На фиг.3 показано, что при включении питания или при сбросе системы обработки данных подается сигнал 340 режима процедуры инициализационного выравнивания (ПИВ), и при этом мультиплексор 328 выбирает для вывода предварительно заданную синхронизирующую последовательность. В варианте осуществления изобретения сигнал 340 режима ПИВ может вводиться ЦП 210 в соответствии с командой базовой системы ввода-вывода (BIOS), записанной в ПЗУ 216.

В показанном на фиг.4А варианте выполнения гибкого интерфейса 332 данные могут поступать в течение окна длительностью два такта, при этом не будут возникать ранее описанные проблемы с синхронизацией. Степень гибкости гибкого интерфейса 332 по фиг.4А равна двум. Для ПИВ синхронизирующая последовательность должна быть периодической с периодом Р, равным или превышающим степень гибкости гибкого интерфейса. Таким образом, для гибкого интерфейса 332, показанного на фиг. 4Б, соответствующая синхронизирующая последовательность будет представлять собой множество битов, чередующихся между "1" и "0", и первоначальный бит будет равен "1". Ниже рассмотрены варианты выполнения гибких интерфейсов со степенью гибкости, отличной от двух, и для них синхронизирующая последовательность будет изменена соответствующим образом. Так, например, для гибкого интерфейса со степенью гибкости N (рассмотренного ниже со ссылкой на фиг.8А и 8Б), соответствующая синхронизирующая последовательность будет иметь первоначальный бит "1", за которым будет следовать N-1 битов "0", после чего последовательность будет повторяться. Могут использоваться и другие битовые последовательности. Так, например, в другом варианте могут использоваться битовые последовательности, являющиеся дополнительными к вышеописанным последовательностям.

При задании фазы стробирующего сигнала 414 во время направления синхронизирующей последовательности может контролироваться выход 410 схемы-защелки 408. Стробирующий сигнал 414 инициализируется с предварительно выбранной фазой. Если для вышеописанной синхронизирующей последовательности для гибкого интерфейса 332 со степенью гибкости два на выходе 410 будет выявлена "1", то это указывает на то, что стробирующий сигнал 414 и связанный с ним стробирующий сигнал 428 правильно сфазированы. В противном случае фаза стробирующего сигнала 414 и соответствующего стробирующего сигнала 428 должны быть сдвинуты на половину периода тактового сигнала 336 ввода-вывода. Как уже описывалось выше, стробирующий сигнал 414 может генерироваться с использованием АППЗ, один из вариантов выполнения которой описан в упоминавшейся выше одновременно поданной заявителем заявке, озаглавленной "Динамический волновой конвейерный интерфейс и способ его применения", которая включена в настоящее описание в качестве ссылки.

Работа гибкого интерфейса, например гибкого интерфейса 300 по изобретению, проиллюстрирована со ссылкой на фиг.5. Как показано на фиг.5, микросхема 302 обменивается данными с микросхемой 304, как и на фиг.3, и дополнительно с микросхемой 306. Микросхема 302 содержит два интерфейса 300, один из которых связывает микросхему 302 с микросхемой 304 через интерфейс 300 микросхемы 304, а второй связывает микросхему 302 с микросхемой 306, которая также имеет интерфейс 300, соответствующий варианту осуществления настоящего изобретения. Путь 502, соединяющий микросхемы 302 и 304, может являться быстрым путем, аналогичным пути 154 на фиг.1Г, и имеющим время ожидания TF, а путь 504, соединяющий микросхему 302 с микросхемой 306, может являться медленным путем, аналогичным пути 152 на фиг.1Г, и со временем ожидания Ts. Как описано выше, для известных типов интерфейсов, если разность времени ожидания между путями 502 и 504 превысит период тактового сигнала шины, то с целью поддержания синхронизации данных для пути 502 потребуется использовать заполнение. Однако интерфейсы 300, включая гибкий интерфейс 332, компенсируют разность времени ожидания между путями 502 и 504. Посредством задания одинакового целевого такта для каждого из гибких интерфейсов 332 микросхем 304 и 306 обеспечивается синхронность данных между микросхемами 302, 304 и 306.

Ниже рассмотрены другие варианты выполнения настоящего изобретения. На фиг. 6А показан альтернативный вариант выполнения интерфейса 332, имеющего степень гибкости два. В показанном на фиг.6А варианте гибкий интерфейс 232, как и в показанном на фиг.4А варианте выполнения гибкого интерфейса 232, включает мультиплексоры 402 и 416, управляющие схемами-защелками 408 и 422. Однако в показанном на фиг.6А гибком интерфейсе 332 в дополнение к схеме-защелке 630, которая соответствует схеме-защелке 430 в варианте, показанном на фиг. 4А, имеется вторая захватывающая схема-защелка - схема-защелка 628, синхронизируемая локальным тактовым сигналом 316. В дополнение к этому, в варианте осуществления блока 332 интерфейса, показанном на фиг.6А, выходной мультиплексор 632, соответствующий мультиплексору 432 на фиг.4А, находится после захватывающих схем-защелок.

Таким образом снижается время ожидания в самом интерфейсе. Входы D схем-защелок 628 и 630 соединены с выходами 424 и 410 схем-защелок 422 и 408, соответственно. Данные на входах D схем-защелок 628 и 630 синхронизируются со схемами-защелками по локальному тактовому сигналу 316. Таким образом, данные синхронизируются по локальному тактовому сигналу 316 до мультиплексора 632. Поток данных 322 восстанавливается посредством выбора для вывода одного из выходов 634 и 636 схем-защелок 628 и 630 с помощью мультиплексора 632 и под управлением сигнала 343 управления выбором, что аналогично действию выходного мультиплексора 432 в варианте осуществления изобретения, показанном на фиг.4А, однако, сигнал 343 управления выбором сдвинут по фазе на половину периода по сравнению с сигналом 343 управления выбором на фиг.4А. В варианте осуществления интерфейса 322, показанном на фиг.6А, данные фиксируются по нарастающему фронту локального тактового сигнала 316. Однако любому специалисту будет понятно, что в альтернативных вариантах осуществления изобретения фиксация данных может выполняться по заднему фронту при условии, что другие управляющие сигналы будут соответствующем образом сдвинуты по фазе. Например, в варианте осуществления изобретения, в котором схемы-защелки 628 и 630 фиксируются по заднему фронту локального тактового сигнала 316, сигнал 343 управления выбором должен быть смещен по фазе на половину периода.

Ниже со ссылкой на фиг.6Б, на которой представлена временная диаграмма, поясняется работа интерфейса 332 по фиг.6А. В связи с тем, что мультиплексоры 402 и 416, схемы-защелки 408 и 422, а также тактовый сигнал 336 ввода-вывода и локальный тактовый сигнал 316, являются общими с вариантами осуществления блока 332 интерфейса, показанными на фиг.4А и 4Б, то в целях краткости не будут снова рассматриваться те части временной диаграммы, приведенной на фиг.6Б, которые связаны с указанными структурами.

Ниже рассмотрена та часть приведенной на фиг.6Б временной диаграммы, которая связана со схемами-защелками 628 и 630, и с мультиплексором 632; значение данных "а" фиксируется на выходе 634 схемы-защелки 630 по фронту t8' локального тактового сигнала 316. Аналогичным образом, значение данных "b" фиксируется на выходе 636 схемы-защелки 628 по фронту t9' локального тактового сигнала 316. Чтобы данные поступили на выход 338 данных на целевом такте, нарастающий фронт сигнала 343 управления выбором должен быть задержан до фронта t9' локального тактового сигнала 316, который совпадает с целевым тактом. Таким образом, значение данных "а" поступает от мультиплексора 632 на выход 338 данных одновременно с фронтом t10 сигнала 343 управления выбором. Таким образом, сигнал 343 управления выбором является синхронным по фазе с локальным тактовым сигналом 316, его верхние плоские части импульсов сцентрированы с фронтами нарастания локального тактового сигнала 316. Аналогичным образом, значение данных "b" поступает на выход 338 данных одновременно с задним фронтом t11 сигнала 343 управления выбором, и далее восстановление потока 322 данных продолжается при последующих переходах сигнала 343 управления выбором.

Кроме того, в соответствии с изобретением могут быть осуществлены и другие варианты гибкого интерфейса 232 с другими предварительно заданным значениями степени гибкости. В том числе могут использоваться значения степени гибкости, соответствующие половине периода. На фиг.7А показан вариант осуществления изобретения со степенью гибкости 1,5 периода. Данные 322 поступают на входы D схем-защелок 702 и 704. Схемы-защелки 702 и 704 являются схемами-защелками "с запоминанием полярности сигнала" или "сквозными" схемами-защелками. Их также называют "прозрачными" схемами-защелками. Когда тактовый сигнал (С) схемы-защелки 702 находится в первом предварительно заданном логическом состоянии или на первом уровне, данные на входе D свободно проходят на выход 706. При переходе тактового сигнала из первого состояния во второе предварительно заданное логическое состояние, схема-защелка 702 фиксирует данные на входе D, и данные на выходе 706 удерживаются до последующего перехода тактового сигнала из второго в первое состояние. (В показанном на фиг. 7 варианте осуществления изобретения первое состояние соответствует "низкому" логическому состоянию, а второе состояние соответствует "высокому" логическому уровню, а переход представляет собой нарастающий фронт. Однако формуле настоящего изобретения будет соответствовать и альтернативный вариант его осуществления с дополняющими логическими состояниями). При нахождении тактового сигнала С схемы-защелки 704 на втором логическом уровне, данные на входе D схемы-защелки свободно проходят на ее выход 708. Данные фиксируются при переходе тактового сигнала со второго на первый логический уровень, и удерживаются до перехода тактового сигнала со второго на первый логический уровень, который в варианте осуществления изобретения, показанном на фиг.7, является "низким" уровнем. Свойство сквозного пропускания позволяет использовать данные не дожидаясь тактового сигнала схемы-защелки, при этом осуществляется вариант блока 332 интерфейса "с малым временем ожидания и малой гибкостью".

В показанном на фиг.7А варианте выполнения гибкого интерфейса 322 схемы-защелки 702 и 704 синхронизируются тактовым сигналом 726 ввода-вывода. Гибкий интерфейс 322, показанный на фиг.7А, является устройством с двойной скоростью передачи данных (ДСПД), это объясняется тем, что данные фиксируются одной из схем-защелок 702 и 704 при каждом переходе тактового сигнала 726 ввода-вывода, и период тактового сигнала 726 ввода-вывода в два раза превышает период локальных тактовых сигналов, локального тактового сигнала 314 и локального тактового сигнала 316, а также тактового сигнала 306 шины. Тактовый сигнал 306 шины сцентрирован в окне данных, ширина которого равна двум периодам локального тактового сигнала.

Работу показанного на фиг.7А гибкого интерфейса 332 можно проиллюстрировать на примере временной диаграммы, приведенной на фиг.7Б. При поступлении значения данных "а" в гибкий интерфейс 332 оно проходит напрямую на выход 706 схемы-защелки 702, поскольку уровень тактового сигнала 716 ввода-вывода является "низким" для плоской части импульса 752. Другими словами, значение данных "а" появляется на выходе 706 схемы-защелки 702 до фронта t1 тактового сигнала 716 ввода-вывода.

Порция данных "а" поступает раньше перехода t1 на одну четверть периода тактового сигнала 336 ввода-вывода, что соответствует половине периода локального тактового сигнала 316. Тактовый сигнал 336 ввода-вывода получается из тактового сигнала шины и, как было описано ранее, при запуске сдвигается по фазе относительно тактового сигнала шины на время ожидания для пути между микросхемами. Кроме того, для тактового сигнала 716 ввода-вывода используется опережающий сдвиг по фазе на четверть периода. В момент поступления фронта t1 значение данных "а" фиксируется, и после этого удерживается в течение одного периода локального тактового сигнала 316.

Аналогичным образом значение данных "b" при поступлении в гибкий интерфейс 332 от приемника 230 передаются напрямую на выход 708 схемы-защелки 704, поскольку уровень тактового сигнала 716 ввода-вывода является высоким для плоской части импульса 754. Затем значение данных "b" удерживается на выходе 708 отрицательным фронтом t2 тактового сигнала ввода-вывода 716. Значение данных "b" удерживается в течение одного периода локального тактового сигнала 316. Таким образом, значение данных появляется на выходах 706 и 708 схем-защелок 702 и 704, соответственно, в течение 1,5 периодов локального тактового сигнала, и это значение является степенью гибкости для показанного на фиг.7А гибкого интерфейса 332.

Поток данных 332 реконструируется на выходах 338 схемами-защелками 710 и 712, и мультиплексором 714. Два потока данных, представленные выходами 706 и 708, соответственно, под управлением локального тактового сигнала 316 фиксируются схемами-защелками 710 и 712. Данные фиксируются по предварительно заданному фронту (положительному для варианта осуществления изобретения, показанного на фиг.7) локального тактового сигнала 316, в то время как положение целевого такта может быть задано в любом месте в пределах полутора периодов гибкости для значения данных "а", как было описано выше. Таким образом, в соответствии с временной диаграммой, показанной на фиг.7Б, значение данных "а" фиксируется схемой-защелкой 710 по фронту t3 локального тактового сигнала 316, и направляется в данные 338 с помощью мультиплексора 714 и под действием сигнала 343 управления выбором. Данные берутся со схемы-защелки 710 в том случае, если сигнал 343 управления выбором имеет первое предварительно заданное значение, и со схемы-защелки 712, если сигнал 343 управления выбором имеет второе предварительно заданное значение. В варианте осуществления изобретения, показанном на фиг. 7, первое значение является "высоким", а второе - "низким", однако очевидно, что изобретение распространяется и на другие предварительно заданные значения. Значение данных "b" фиксируется схемой-защелкой 712 по фронту t4 локального тактового сигнала 316 и направляется в данные 338, так как сигнал 343 управления выбором имеет второе значение. Затем дальнейшие значения данных последовательно выводятся на выход 338 посредством попеременного выбора выхода схем-защелок 710 и 712 с помощью мультиплексора 714, как показано на фиг.7Б.

Кроме того, гибкие интерфейсы, соответствующие принципам настоящего изобретения, являются расширяемыми, таким образом их степень гибкости может увеличиваться посредством добавления управляющих и запоминающих элементов. На фиг. 8А представлен вариант выполнения гибкого интерфейса со степенью гибкости, равной N-1 периодов тактового сигнала шины. Интерфейс 332 имеет множество N мультиплексоров 802. Первый вход 704 каждого мультиплексора принимает поток 322 данных от приемника 330. Второй вход 806 принимает сигнал, выдаваемый одной из соответствующих схем-защелок 808-818. Каждая из схем-защелок 808-818 включает пару схем-защелок. В каждой из схем-защелок 808, 812 и 816, для каждой пары схем-защелок внутренний выход первой схемы-защелки в паре соединен с внутренним входом второй схемы-защелки в паре, как главное и подчиненное устройства. В схемах-защелках 808, 812 и 816 выход 820 подчиненной части соединен с входом 806 соответствующего мультиплексора 802. Подчиненная часть схем-защелок 808, 812 и 816 фиксирует данные на входе D по нарастающему фронту тактового сигнала 336 ввода-вывода. Соответствующие входы D схем-защелок 808, 812 и 816 связаны с выходом соответствующего мультиплексора 802. Схемы-защелки 810, 814 и 818 соединяют выход 822 первой из схем-защелок в паре с входом 806 соответствующего мультиплексора 802. Первая из схем-защелок в паре является прозрачной, и данные на первом входе 828 проходят насквозь на выход 822 при плоской части импульса тактового сигнала 336 ввода-вывода. Вход 828 каждой из схем-защелок 810, 814 и 818 соединен с соответствующим выходом 826 второй из схем-защелок в паре. Кроме того, вход 830 второй из схем-защелок в паре соединен с выходом соответствующего мультиплексора 802. Вторая из схем-защелок в паре также является прозрачной, и пропускает данные насквозь при плоской части импульса тактового сигнала 336 ввода-вывода. Первые и вторые из образующих пары схем-защелок 810, 814 и 818 пропускают данные насквозь при плоской части импульсов тактового сигнала 336 ввода-вывода, имеющей противоположную полярность.

Мультиплексоры 802 выбирают сигналы на входах 804 и 806 под действием соответствующего стробирующего сигнала из стробирующих сигналов 832-842. Стробирующие сигналы 832-840 будут рассматриваться далее с использованием временной диаграммы, приведенной на фиг.8Б.

Данные фиксируются по локальному тактовому сигналу с помощью схем-защелок 844 данных, каждая из которых получает выходной сигнал от одной из соответствующих схем-защелок 808-818. Данные фиксируются схемами-защелками 844 данных с использованием локального тактового сигнала 316. Выходные сигналы 824 схем-защелок 808, 812 и 816 подаются на вход D соответствующей схемы-защелки 844 данных. Выходные сигналы 824 поступают от главной части схем-защелок 808, 812 и 816, которые являются прозрачными, как описывалось выше. На входы D остальных схем-защелок 844 данных поступает сигнал с выхода 826 от вторых схем-защелок в парах, образуемых схемами-защелками 810, 814 и 818. Вторая из схем-защелок в парах также является прозрачной схемой-защелкой со сквозным пропусканием данных в том случае, если полярность тактового сигнала 336 ввода-вывода будет противоположна полярности, при которой происходит сквозное пропускание данных первыми из схем-защелок в парах.

Мультиплексор 846 выбирает для вывода один из сигналов, удерживаемых схемами-защелками 844 данных. Выход каждой схемы-защелки 844 данных соединен с соответствующим входом, являющимся одним из входов 848-858. Сигнал направляется в микросхему, например, в микросхему 302 или 304 на выходе 860 мультиплексора 846. Мультиплексор 846 выбирает один из входов 848-858 с использованием сигнала 343 управления выбором. Сигнал 343 управления выбором включает k сигналов, причем 2k равняется N.

С использованием элементов, показанных на фиг.8А, может быть осуществлен другой вариант изобретения со степенью гибкости N. Посредством соединения соответствующих входов D схем-защелок 844 данных с выходами 820 соответствующих схем-защелок 808, 812 и 816, и с выходами 826 соответствующих схем-защелок 810, 814 и 818 (вместо выходов 824 и 822, как показано на фиг.8А), получается степень гибкости N. Во всем остальном элементы блока 332 интерфейса, показанные на фиг.8А, не изменяются.

На фиг.8Б показана временная диаграмма для блока 332 интерфейса, приведенного на фиг.8А. Значение данных "а" поступает в потоке данных 322 после времени ожидания Т1 для интерфейса; и после подачи на один из соответствующих мультиплексоров 802 стробирующего сигнал 832, представленного плоской частью импульса 862, значение данных "а" проходит через соответствующий мультиплексор 802 на вход D схемы-защелки 808. При поступлении фронта t1 тактового сигнала 336 ввода-вывода, схема-защелка 808 удерживает значение данных "а", которое направляется назад с выхода 820 схемы-защелки 808 на вход 806 соответствующего из мультиплексоров 802. При поступлении фронта t2 стробирующего сигнала 832, соответствующий мультиплексор 802 выбирает сигнал на входе 806, на котором находится значение данных "а". Стробирующий сигнал 832 является отрицательным в течение N-1 периодов тактового сигнала 306 шины, и при этом значение данных "а" сохраняется на входе D схемы-защелки 808 и, таким образом, на выходе 824 схемы-защелки 808. При наступлении перехода t3 тактового сигнала 336 ввода-вывода, значение данных "а" удерживается в течение дополнительного периода тактового сигнала 306 шины, после чего переход t4 стробирующего сигнала 832 приводит к переключению соответствующего мультиплексора 802 для выполнения выбора для потока данных 322, затем при поступлении фронта t5 тактового сигнала 336 ввода-вывода, (N+2)-е значение данных для данных 2 фиксируется схемой-защелкой 808 по фронту t5 тактового сигнала 336 ввода-вывода. Значение данных "а" фиксируется схемами-защелками 844 данных, получающими выходной сигнал 824 схемы-защелки 808 при поступлении фронта t6 локального тактового сигнала 316, и это значение возникает на выходе 848. Значение данных "а" удерживается на выходе 848 в течение N периодов тактового сигнала 306 шины.

Следующее значение данных 332, значение данных "b", аналогичным образом удерживается схемой-защелкой 844 данных, соединенной со схемой-защелкой 810, в течение N периодов тактового сигнала 306 шины. При поступлении значения данных "b" в блок 332, отпирается и стробирующий сигнал 834, представленный плоской частью импульса 864, и производится выбор данных 332 на входе 804 соответствующего мультиплексора 802. Значение данных "b" появляется на входе 830 схемы-защелки 810 и фиксируется по фронту t7 тактового сигнала 336 ввода-вывода, после чего значение данных "b" появляется в выходном сигнале 826 схемы-защелки 810. Выходной сигнал 826 схемы-защелки 810 направляется назад на вход 828 схемы-защелки 810. Так как тактовый сигнал 336 ввода-вывода становится отрицательным после фронта t7, то значение данных "b" в выходном сигнале 826 схемы-защелки 810 проходит на выход 822 схемы-защелки 810, откуда оно направляется назад на вход 806 соответствующего мультиплексора 802. При поступлении фронта t8 тактового сигнала 336 ввода-вывода, значение данных "b" удерживается на выходе 822 схемы-защелки 810. При поступлении фронта t9 стробирующего сигнала 834, соответствующий мультиплексор 802 переключается и выбирает вход 806 для вывода значения данных "b", удерживаемого на выходе 822 схемы-защелки 810, для его направления на вход 830 схемы-защелки 810. Затем значение данных "b" проходит на выход 826 схемы-защелки 810, откуда оно направляется назад на вход 828 схемы-защелки 810, и значение данных "b" продолжает возвращаться на вход 806 соответствующего мультиплексора, принимающего стробирующий сигнал 834. Таким образом, значение данных "b" удерживается на выходе 826 схемы-защелки 810 в течение N+1 периода тактового сигнала 306 шины, т.е. в течение одного периода тактового сигнала фронта t10 перехода стробирующего сигнала 834.

Стробирующий сигнал 836 отстает по фазе от стробирующего сигнала 834 на один период тактового сигнала 836 ввода-вывода, и аналогичным образом каждый последующий стробирующий сигнал 838-842 отстает по фазе от предшествующего стробирующего сигнала в цепочке на один период тактового сигнала 336 ввода-вывода. Таким образом, каждая последующая схема-защелка 808-818 хранит последующее значение данных для данных 332, и хранит это значение данных в течение N+1 периода тактового сигнала 306 шины. Каждое значение данных в соответствующей схеме-защелке 808-810 затем фиксируется соответствующей схемой-защелкой 844 данных для каждого периода локального тактового сигнала 316. Таким образом, значение данных "b" фиксируется соответствующими схемами-защелками 844 данных по фронту t11 локального тактового сигнала 316, и затем появляется на выходе 850; аналогичным образом значение данных "с" синхронизируется соответствующей схемой-защелкой 844 данных по фронту t12 локального тактового сигнала 316, и затем появляется на выходе 852. Последняя схема-защелка 844 данных, связанная со схемой-защелкой 818, фиксирует (N+1)-e значение данных по фронту t12 локального тактового сигнала 316.

Данные выводятся мультиплексором 846 под управлением сигнала 343 управления выбором, который включает k сигналов. Каждый из k сигналов сигнала 343 управления выбором является периодическим. Сигнал "обнуления", обозначаемый S(0), имеет полупериод, равный периоду тактового сигнала 306 шины. (k-1)-й сигнал имеет полупериод, равный N периодам тактового сигнала шины. Каждый сигнал в последовательности между S(0) и S(N) имеет периодичность, равную удвоенному периоду предшествующего сигнала. Значения данных, хранящиеся в схемах-защелках 844 данных, и появляющиеся на соответствующем входе 848-858 мультиплексора 846, последовательно, выводятся на выход 860 данных под управлением сигнала 343 управления выбором. Значение данных "а" выводится по целевому такту, имеющему степень гибкости N-1, и по фронту t14 S(N) сигнала 343 управления выбором. Остальные значения данных последовательно выводятся под управлением циклических переходов k сигналов сигнала 343 управления выбором. Хотя здесь было указано, что фазы сигналов, составляющих сигнал 343 управления выбором, синхронизированы по нарастающему фронту, специалистам будет понятно, что в альтернативном варианте осуществления изобретения могут использоваться дополняющие фазы.

Показанный на фиг. 8 блок 332 инициализируется на стадии ПИВ, как было описано выше с использованием фиг.4. Для варианта осуществления изобретения со степенью гибкости N-1, соответствующей степени гибкости варианта блока 332, показанного на фиг.8, подходящая последовательность инициализации может иметь периодичность N-1. Для вышеописанного альтернативного варианта со степенью гибкости N, синхронизирующая последовательность может иметь периодичность N. Во время инициализации с использованием синхронизирующей последовательности, в состав которой входит "1", после которой следует несколько "0", значение "1" будет выявляться схемой-защелкой 808 при правильной последовательности сигналов для сигнала 343 управления выбором.

Таким образом, был предложен механизм поддержания синхронизации данных для интерфейсов системы обработки данных. Принимаемые данные захватываются несколькими запоминающими элементами и селективно направляются в принимающую микросхему на предварительно выбранном целевом такте, который синхронизирован с тактовым сигналом микросхемы. Первоначальная синхронизация устанавливается динамически посредством выполнения ПИВ. Механизм в соответствии с настоящим изобретением обеспечивает синхронизацию данных в системе обработки данных, в которой значения времени ожидания изменяются больше, чем на один период тактового сигнала шины.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ВОЛНОВОЙ КОНВЕЙЕРНЫЙ ИНТЕРФЕЙС И СПОСОБ ЕГО ПРИМЕНЕНИЯ | 2000 |

|

RU2213992C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ПРЯМОГО ДОСТУПА (DASD) ЕМКОСТЬЮ БОЛЬШЕ 528 МЕГАБАЙТ И СПОСОБ ЕГО ВОПЛОЩЕНИЯ ДЛЯ ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ | 1994 |

|

RU2155369C2 |

| КОМПЬЮТЕРНАЯ СИСТЕМА, ИМЕЮЩАЯ ШИННЫЙ ИНТЕРФЕЙС | 1995 |

|

RU2140667C1 |

| УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ ОРГАНИЗАЦИИ ДОСТУПА К ОБЩЕЙ ШИНЕ ВО ВРЕМЯ ПЕРЕДАЧИ ДАННЫХ С ПРЯМЫМ ДОСТУПОМ К ПАМЯТИ | 1991 |

|

RU2110838C1 |

| МИКРОКОМПЬЮТЕР И СПОСОБ ЕГО ТЕСТИРОВАНИЯ | 2006 |

|

RU2374679C2 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ЗАПРОСОВ НА ДОСТУП К ШИНЕ | 1990 |

|

RU2067314C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2110839C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ МОДУЛЯЦИИ ЦИФРОВЫХ ДАННЫХ, В ЧАСТНОСТИ ПРОБЛЕСКОВЫЙ ИНФРАКРАСНЫЙ МОДЕМ С КОДИРОВАНИЕМ ТИПА NRZI | 1995 |

|

RU2126595C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2072553C1 |

Изобретение относится к системам обработки данных, в частности к интерфейсу между динамическими или синхронизируемыми интегральными схемами в системе обработки данных. Технический результат заключается в создании интерфейса, обеспечивающего передачу данных с увеличенной тактовой частотой, а также обеспечивающего синхронизацию данных между интегральными схемами системы обработки данных. Интерфейс содержит первое запоминающее устройство для хранения первого набора данных, второе запоминающее устройство для хранения второго набора данных, схемы, предназначенные для последовательного вывода в ответ на один управляющий сигнал первых данных из первого запоминающего устройства и вторых данных из второго запоминающего устройства. 3 с. и 23 з.п. ф-лы, 16 ил.

| US 5838936 А, 17.11.1998 | |||

| US 5692216 А, 25.11.1997 | |||

| US 5649162 А, 15.07.1997 | |||

| УСТРОЙСТВО СОПРЯЖЕНИЯ ИНТЕРФЕЙСОВ | 1990 |

|

RU2022345C1 |

| ШИННАЯ СИСТЕМА ОДНОКАНАЛЬНОЙ МНОГОСТАНЦИОННОЙ СВЯЗИ | 1994 |

|

RU2122234C1 |

Авторы

Даты

2003-09-10—Публикация

2000-03-03—Подача