Настоящее изобретение относится к системам обработки данных, в частности к шинным интерфейсам в системах обработки данных.

По мере повышения системной тактовой частоты в системах обработки данных, отражающей повышение тактовой частоты центральных процессоров, должна соответствующим образом увеличиваться скорость передачи данных по системным шинам. Скорость передачи данных по шине, соединяющей компоненты системы обработки данных, естественным образом ограничивается физическим разделением компонентов. Одним из разработанных методов передачи данных по шине является волновой конвейерный метод, в котором сигнал данных передается на шину до того, как предыдущие данные были захвачены приемным устройством на шине. Иными словами, данные направляются через интерфейс шины между элементами системы обработки данных как по "конвейеру". После заполнения "конвейера" данные доставляются со средней скоростью, превышающей время ожидания для интерфейса.

В типовой системе обработки данных последние могут пересылаться от передающего устройства к нескольким приемным устройствам. Различные приемные устройства будут соединены с исходным или передающим устройством с помощью интерфейсов шины, имеющих различную длину электрического пути и, следовательно, различное время ожидания.

Кроме того, если одно устройство получает множество сигналов данных, для каждого сигнала может быть свое время ожидания. Различия могут возникать в связи с допусками при изготовлении, ограничениями конструкции, например, различиями в длине линий, и в связи с зависящими от времени эффектами, например, зависящим от данных дрожанием (межсимвольная интерференция), дрожанием тактового сигнала и шумами.

Кроме того, предполагается, что данные будут поступать синхронно. То есть ожидается, что данные будут поступать на предварительно заданном такте системного тактового генератора. Если данные поступят раньше или позже, чем ожидалось, могут возникнуть ошибки.

В волновом конвейерном интерфейсе анализ временных зависимостей является более сложным, так как одинаково важными являются как быстрые, так и медленные пути. Уменьшается интервал достоверности данных, т.е. интервал времени, в течение которого возможен надежный прием данных, так как увеличивается разница по времени между быстрыми и медленными путями, связывающими исходное или передающее устройство с одним или несколькими приемными устройствами. Синхронизация будет потеряна, если разница по времени между быстрым и медленным путем достигнет периода тактового сигнала шины. Кроме того, расфазировка тактового сигнала приемного устройства может еще больше сузить область достоверности данных. По мере увеличения быстродействия интерфейса шины должны быть уменьшены расхождениями по времени между быстрым и медленным путями, и более жесткими становятся допуски на расфазировку тактового сигнала. Однако при этом управление расфазировкой тактового сигнала и расхождениями по времени может ограничиваться физическими характеристиками системы обработки данных. В связи с этим существует потребность в наличии способов и устройств, позволяющих выполнять выравнивание данных на приемной стороне интерфейса, а также увеличить период времени, в течение которого может производиться надежный прием данных.

В US 5229668 описывается "сигнал данных, который может приниматься с высокой скоростью с использованием тактового сигнала посредством пропускания сигнала данных и тактового сигнала через серию элементов задержки данных и тактового сигнала, соответственно, и фиксации задержанного сигнала данных и тактового сигнала. Таким образом скорость приема контролируется относительной расфазировкой тактового сигнала и сигнала данных, которая может быть сделана сравнительно небольшой и может ограничиваться только шумами и случайными отклонениями при изготовлении. При этом может быть получена высокая скорость дискретизации".

У Wong и др. в "Inserting Active Dalay Elements to Achieve Wave Pipelining" описаны алгоритмы автоматического уравнивания задержек посредством ввода минимального числа активных элементов задержки, предназначенных для удлинения коротких путей.

Задачей настоящего изобретения является разработка способа, который позволял бы устранить вышеописанные недостатки.

В соответствии с настоящим изобретением предлагается интерфейс, имеющий множество устройств задержки, каждое из которых служит для приема соответствующего сигнала данных и имеет предварительно выбираемый период задержки, а также служит для вывода сигнала данных по истечении предварительно выбранного периода задержки, и схему, соединенную со множеством устройств задержки и предназначенную для задания каждого предварительно выбираемого периода задержки на основании времени поступления, при этом указанная схема, предназначенная для задания каждого предварительно выбираемого периода задержки, имеет логическую схему сравнения данных, предназначенную для приема заданного подмножества сигналов данных и для вывода первого заданного значения выходного сигнала, когда указанное подмножество сигналов данных содержит первый заданный набор значений, и для вывода второго заданного значения выходного сигнала, когда подмножество сигналов данных содержит второй заданный набор значений, причем в зависимости от соответствующего времени поступления указанное подмножество сигналов данных включает один из указанных первого и второго заданных наборов значений, а также имеет схему, предназначенную для изменения предварительно выбранных периодов задержки в зависимости от первого и второго заданных значений выходного сигнала.

Предлагается и способ осуществления динамической волновой конвейерной передачи в интерфейсе, имеющем множество устройств задержки и схему, соединенную со множеством указанных устройств задержки, заключающийся в том, что осуществляют прием с помощью указанных устройств задержки, каждое из которых имеет предварительно выбираемый период задержки, соответствующего сигнала данных и вывод этого сигнала данных по истечении предварительно выбранного периода задержки, и с помощью указанной схемы задают каждый предварительно выбираемый период задержки, причем каждый из таких предварительно выбранных периодов задержки задают на основании времени поступления, при этом указанная схема имеет логическую схему сравнения данных, предназначенную для приема заданного подмножества сигналов данных и для вывода первого заданного значения выходного сигнала, когда указанное подмножество сигналов данных содержит первый заданный набор значений, и для вывода второго заданного значения выходного сигнала, когда подмножество сигналов данных содержит второй заданный набор значений, причем в зависимости от соответствующего времени поступления указанное подмножество сигналов данных включает один из указанных первого и второго заданных наборов значений, а также имеет схему, предназначенную для изменения предварительно выбранных периодов задержки в зависимости от первого и второго заданных значений выходного сигнала.

Предлагается также система обработки данных с интерфейсом, имеющая центральный процессор (ЦП) и приемное устройство, которое соединено с этим ЦП и предназначено для приема по меньшей мере одного сигнала данных от ЦП и которое имеет блок приема данных с интерфейсом согласно изобретению.

Выше было дано довольно общее описание особенностей и технических преимуществ изобретения, чтобы было более понятным приводимое ниже его подробное описание. Далее также будут описаны дополнительные особенности и преимущества изобретения.

Ниже изобретение более подробно рассмотрено на примере некоторых вариантов его выполнения со ссылкой на прилагаемые чертежи, на которых показаны:

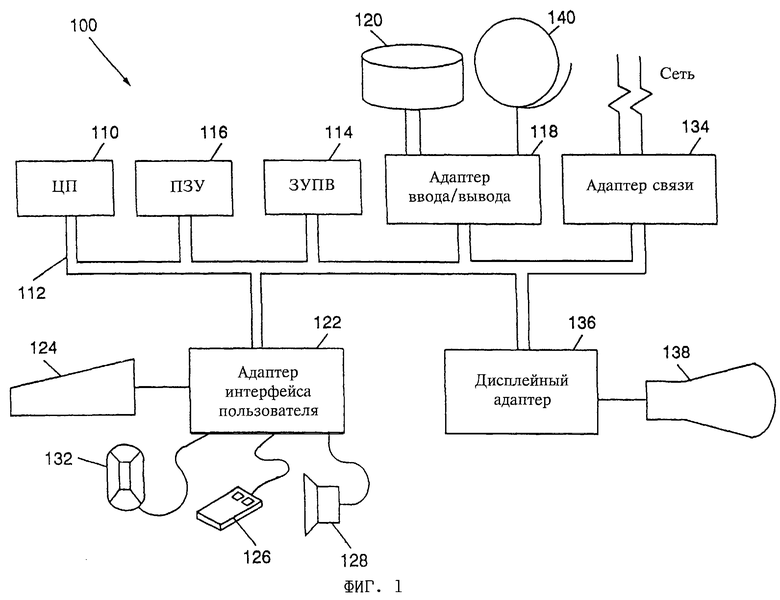

на фиг. 1 - структурная схема системы обработки данных в соответствии с вариантом осуществления изобретения,

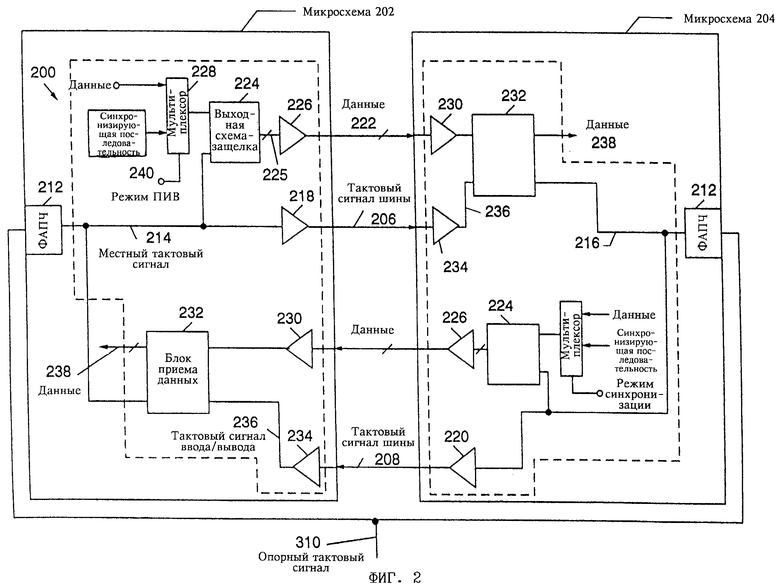

на фиг. 2 - структурная схема варианта осуществления динамического волнового конвейерного интерфейса в соответствии с изобретением,

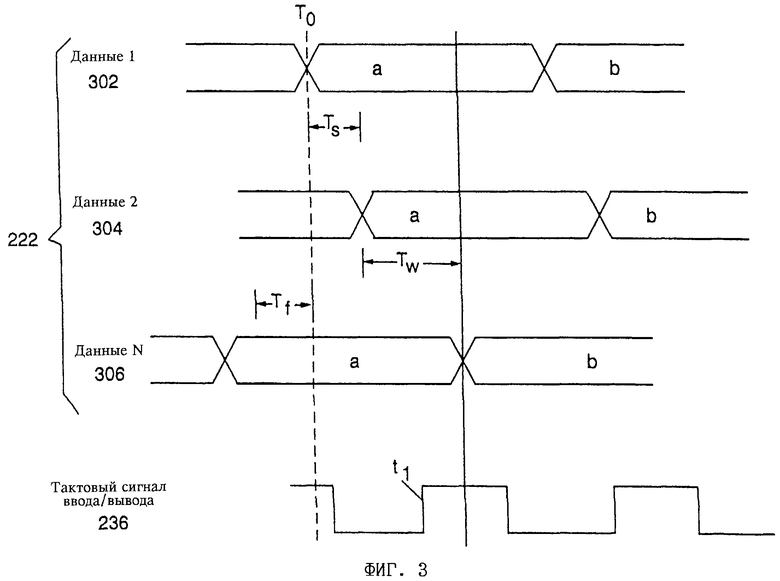

на фиг. 3 - входная временная диаграмма для интерфейса, показанного на фиг.2,

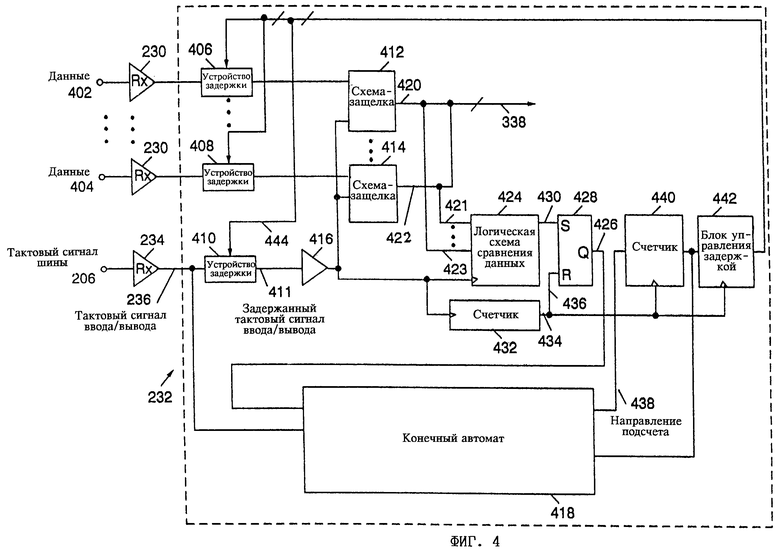

на фиг. 4 - структурная схема блока приема данных в соответствии с вариантом осуществления изобретения,

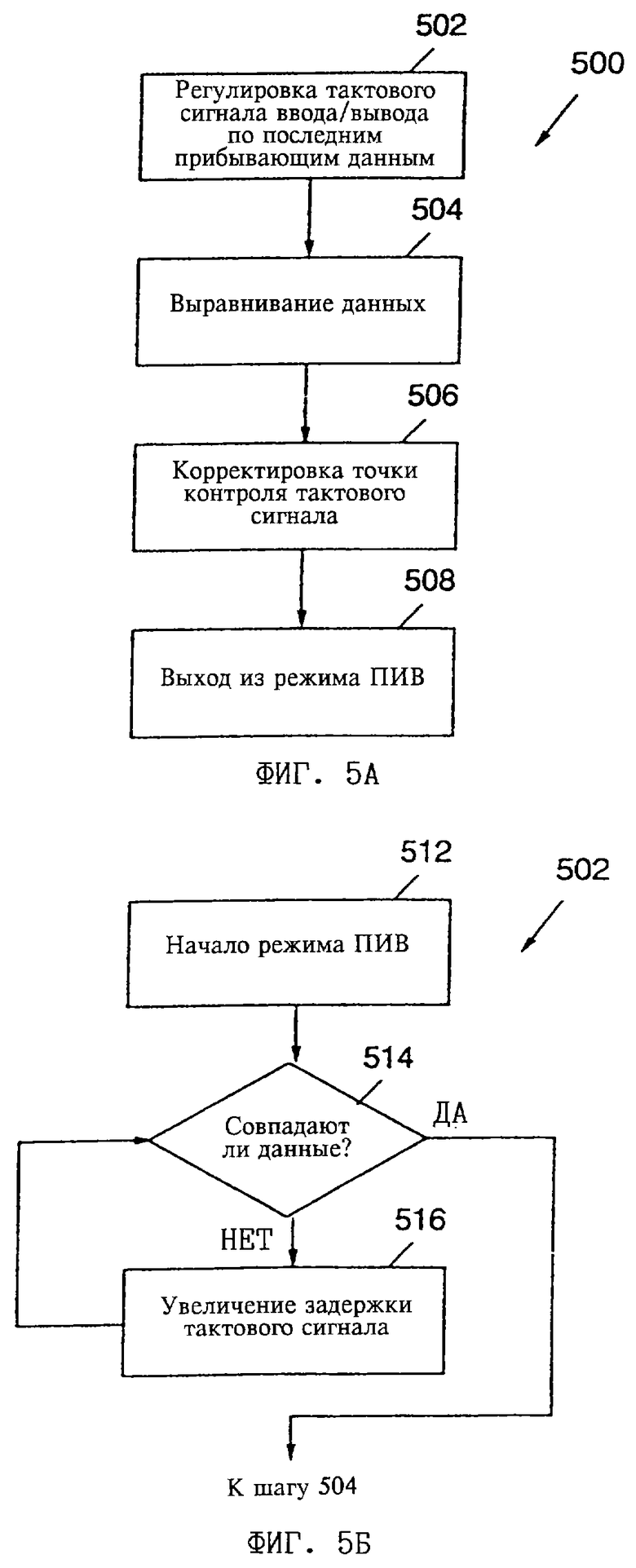

на фиг.5А - блок-схема методики в соответствии с вариантом осуществления изобретения,

на фиг. 5Б - блок-схема способа корректировки тактового сигнала в соответствии с вариантом осуществления изобретения,

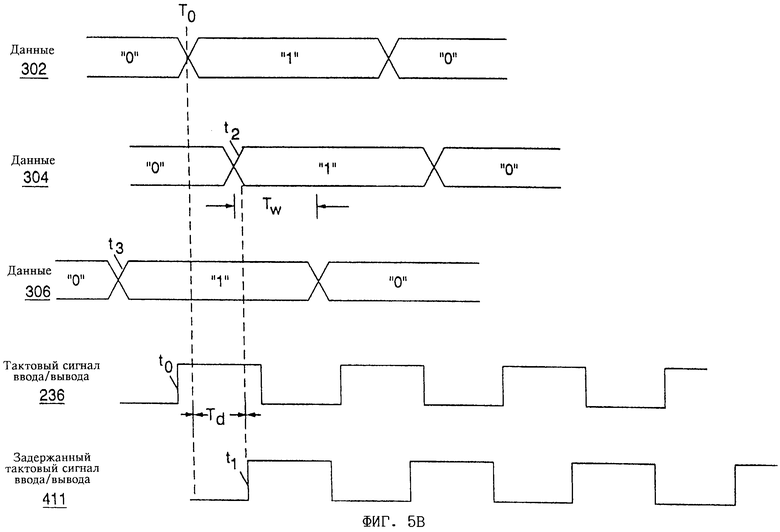

на фиг. 5В - временная диаграмма, соответствующая показанному на фиг.5Б способу,

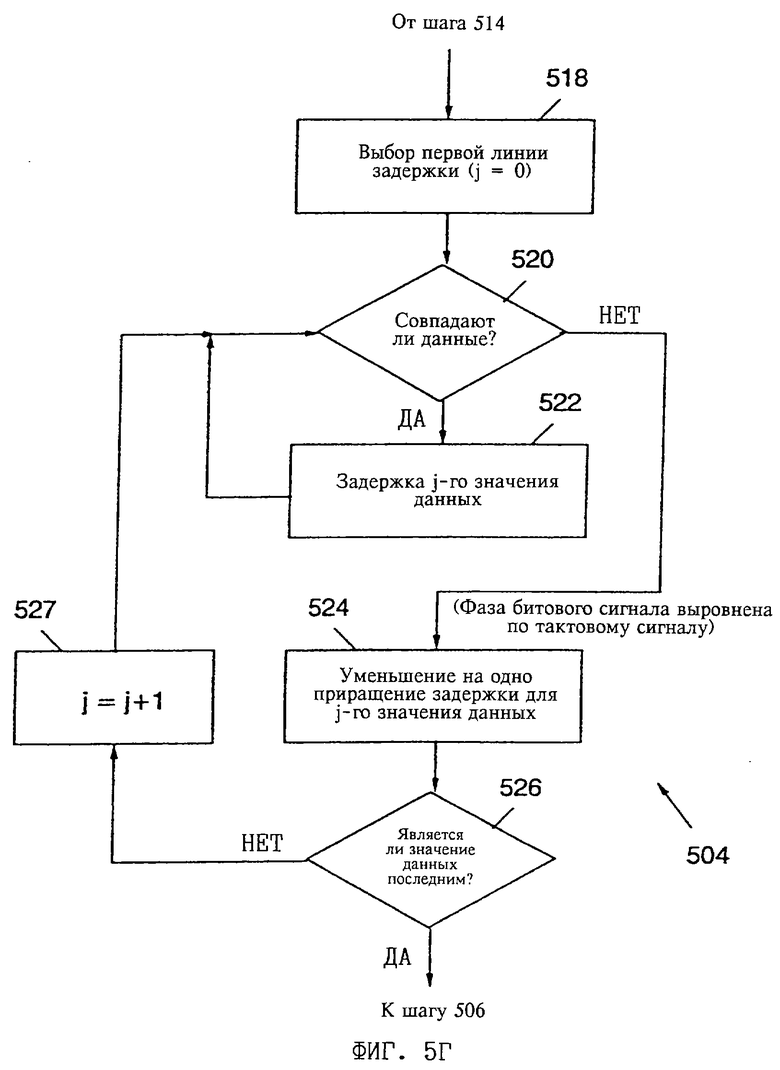

на фиг. 5Г - блок-схема способа выравнивания данных в соответствии с вариантом осуществления изобретения,

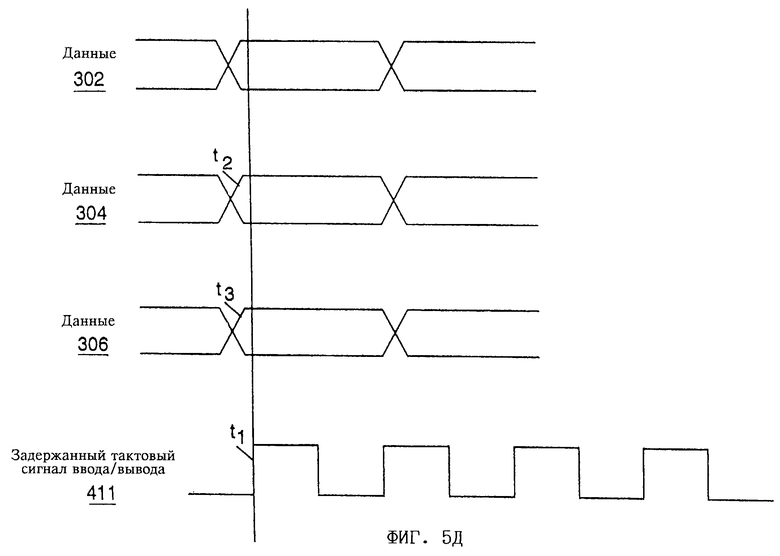

на фиг. 5Д - временная диаграмма, соответствующая показанному на фиг.5Г способу,

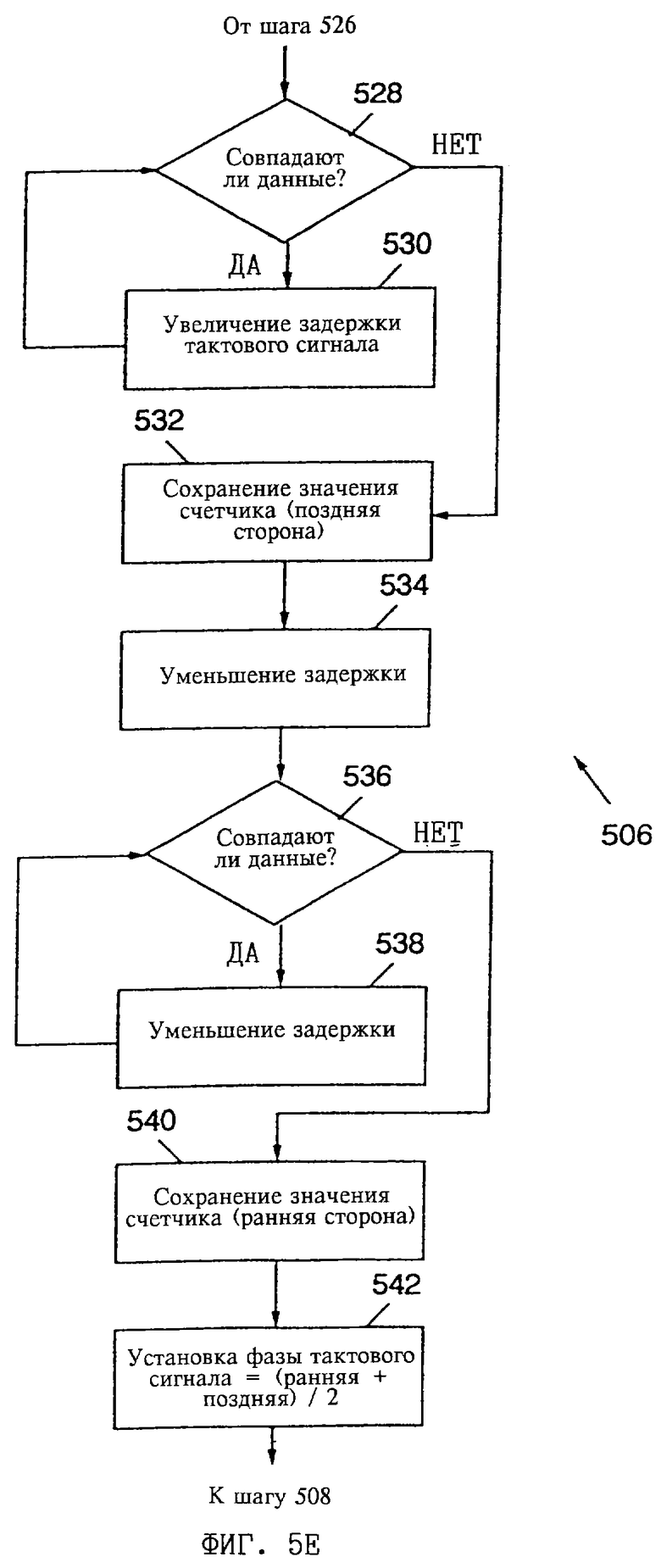

на фиг. 5Е - блок-схема способа корректировки фазы тактового сигнала в соответствии с вариантом осуществления изобретения и

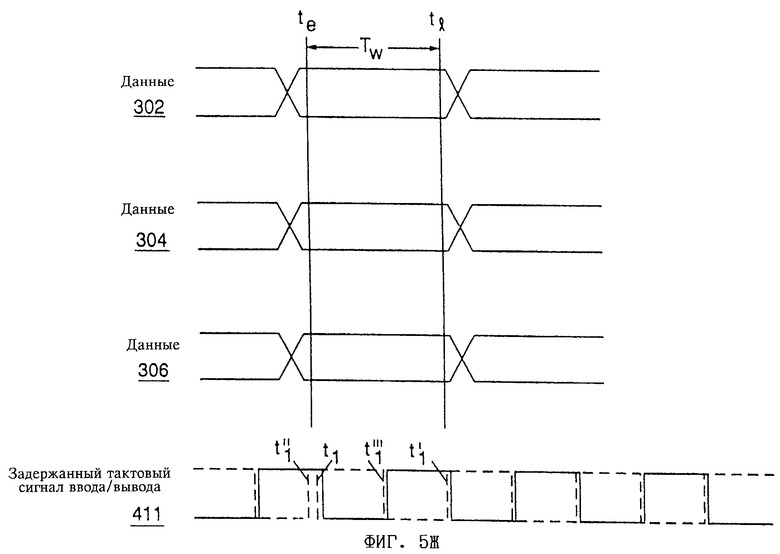

на фиг. 5Ж - временная диаграмма, соответствующая показанному на фиг.5Е способу.

В соответствии с настоящим изобретением предлагается волновой конвейерный механизм, позволяющий уменьшить разность времени прихода данных и дрожание тактовых импульсов. При выполнении процедуры инициализации может быть увеличен размер зоны достоверности данных с соответствующим снижением чувствительности интерфейса к временным расхождениям между подключенными к шине микросхемами. Временные расхождения для множества сигналов данных, поступающих на приемное устройство, устраняются посредством определения сигналов данных, которые приходят самыми первыми и самыми последними, и задерживания сигнала данных, который приходит самым первым, на предварительно выбранную величину, определяемую разностью времени прихода для сигналов данных, которые приходят самыми первыми и самыми последними. Кроме того, устраняется расфазировка тактового сигнала шины, поступающего от передающего устройства, и получаемый таким образом тактовый сигнал центрируется приблизительно по окну данных.

В дальнейшем описании для детального понимания сущности настоящего изобретения приводится большое количество конкретных данных, например тактовые частоты шины, фронты тактовых сигналов и т.д. Однако специалистам понятно, что изобретение может быть осуществлено без таких конкретных данных. В других случаях хорошо известные цепи приводятся в виде структурной схемы, чтобы не обременять изобретение ненужными деталями.

Ниже рассмотрены фиг.1-5Ж, на которых элементы не всегда изображаются в масштабе и на которых одинаковые или похожие элементы обозначаются одинаковыми номерами позиций.

На фиг. 1 показаны аппаратные средства, в которых может использоваться настоящее изобретение и которые представляют собой типичную аппаратную конфигурацию процессора 100 данных по изобретению, в которую входит центральный процессор (ЦП) 110, например обычный микропроцессор, и несколько других блоков, соединенных системной шиной 112. В состав процессора 100 данных входит запоминающее устройство 114 с произвольной выборкой (ЗУПВ), постоянное запоминающее устройство (ПЗУ) 116, адаптер 118 ввода/вывода, предназначенный для подключения к шине 112 периферийных устройств, например дисководов 120 и накопителей 140 на магнитной ленте, адаптер 122 интерфейса пользователя, предназначенный для подключения к шине 112 клавиатуры 124, мыши 126 и/или других устройств пользовательского интерфейса, например сенсорного экрана (не показан), связной адаптер 134, предназначенный для подключения процессора 100 к сети обработки данных, и дисплейный адаптер 136, предназначенный для подключения шины 112 к дисплейному устройству 138. В состав ЦП 110 могут входить другие не показанные здесь схемы, в том числе схемы, обычно входящие в состав микропроцессора, например операционный блок, блок сопряжения с шиной, блок арифметической логики и т.д. ЦП 110 может также входить в состав одной интегральной схемы.

На фиг. 2 показан волновой конвейерный интерфейс 200 в соответствии с изобретением. Интерфейс 200 встроен в каждую из микросхем 202 и 204, которые обмениваются данными одна с другой с использованием интерфейса 200. В варианте осуществления изобретения микросхемы 202 и 204 могут, например, соответствовать ЦП 110 и ЗУПВ 114 процессора 100 данных. Данные между микросхемами 202 и 204 передаются со скоростью, определяемой тактовыми сигналами шины, тактовыми сигналами 206 и 208 шины. Тактовые сигналы 206 и 208 шины номинально имеют одну и ту же частоту и получаются на основании опорного тактового сигнала 310, направляемого в ФАПЧ 212 в каждой из микросхем 202 и 204. В варианте осуществления изобретения опорный тактовый сигнал 310 может являться системным тактовым сигналом. Каждая из ФАПЧ 212 выдает локальный тактовый сигнал 214 в микросхеме 202 и локальный тактовый сигнал 216 в микросхеме 204, которые синхронизированы по фазе с опорным тактовым сигналом 310 и период которых может быть равен периоду опорного тактового сигнала 310, умноженному на предварительно выбранное целое число М. Локальный тактовый сигнал 214 буферизируется драйвером 218 с целью получения тактового сигнала 206 шины для микросхемы 202. Аналогичным образом локальный тактовый сигнал 216 буферизируется драйвером 220 с целью получения тактового сигнала 208 шины для микросхемы 204.

Тактовый сигнал шины направляется микросхемой вместе с передаваемыми данными. Данные 222 из микросхемы 202 фиксируются выходной схемой-защелкой 224 и выводятся и буферизируются драйвером 226. Данные фиксируются по предварительно заданному фронту локального тактового сигнала 214. Данные принимаются с использованием мультиплексора 228. При проведении процедуры инициализационного выравнивания (ПИВ) мультиплексор 228 также принимает предварительно определенную синхронизирующую последовательность. Подробное пояснение дано ниже.

Данные 222 буферизируются приемником 230 и направляются в блок 232 приема данных. Тактовый сигнал 206 шины, направленный вместе с данными 222, буферизируется приемником 234, выходной сигнал которого формирует тактовый сигнал 236 ввода/вывода, также направляемый в блок 232 приема данных. Данные из микросхемы 204, направляемые в микросхему 202 вместе с тактовым сигналом 208 шины, аналогичным образом принимаются интерфейсом 200 в микросхеме 202, и очевидно, что приводимое ниже описание блока 232 приема данных в той же мере распространяется на прием микросхемой 202 данных от микросхемы 204.

На фиг. 3 приведена временная диаграмма прихода данных 222 на вход микросхемы 204. Хотя синхронизация описывается для данных 222, интерфейс 200 является двусторонним, и аналогичная диаграмма в равной степени относится к передаче данных, направляемых из микросхемы 204 в микросхему 202. Первый сигнал данных, данные 302, поступает после номинального времени ожидания, связанного с конечным временем передачи на пути между микросхемами 202 и 204. На фиг.3 показано, что данные 302 поступают в начальный момент времени T0. Для второго сигнала данных, данных 304, время ожидания будет больше времени ожидания для сигнала данных 302, и их поступление задерживается относительно начального момента времени на величину ТS, которая будет считаться максимальным временем задержки для множества сигналов данных, передающихся с задержкой по шине данных 222. Аналогичным образом для третьего сигнала данных, данных 306, время ожидания будет меньше номинального, и они поступят раньше данных 302. На схеме показано, что данные 306 поступают раньше начального момента времени T0 на величину Тf. В последующем описании работы блока 232 приема данных предполагается, что величина Тf соответствует самому раннему времени поступления для множества сигналов данных, поступающих по шине данных 222 до начального момента времени. Разность времени поступления данных по шине данных 222 называется расфазировкой данных. Расфазировка данных может вызываться различными причинами, в том числе допусками при изготовлении, ограничениями конструкции, например различиями в длине линий, и зависящими от времени эффектами, например зависящим от данных дрожанием (межсимвольная интерференция), дрожанием тактового сигнала и шумами. (Для простоты изображения временной диаграммы на фиг.3 начальные моменты времени показаны по отношению к центрам переходов. Специалистам будет понятно, что допустимые переходы могут быть заданы по отношению к другим предварительно заданным процентным величинам от значений стационарного состояния).

Данные фиксируются приемным устройством, например микросхемой 204, по фронту тактового сигнала 236 ввода/вывода. При отсутствии расфазировки данных данные могут захватываться в пределах окна достоверности данных, ширина которого равна периоду тактового сигнала 236 ввода/вывода. Расфазировка данных снижает ширину окна достоверности данных Тw на сумму величин Тf и TS.

С целью восстановления ширины окна достоверности данных интерфейс 200 в соответствии с настоящим изобретением вводит множество сигналов данных в блок 232 приема данных, показанный на фиг.4. Данные буферизируются приемником 230 и поступают в программируемую линию устройства задержки, в одну из линий устройств 406-408 задержки. Программируемые линии устройств 406-408 задержки обеспечивают предварительно заданную задержку соответствующего сигнала данных, вводимого в линию задержки. Линия задержки, получающая сигнал с самым поздним временем прихода, соответствующий данным 304 на фиг.3, программируется на нулевую задержку. (Очевидно, что для каждой цепи имеется минимальное время прохождения сигнала. Очевидно также, что нулевая задержка задается относительно такого минимального времени прохождения). Таким образом, для приведенного на фиг.4 примера, данные 402 соответствуют данным 304 на фиг.3, и для линии устройства 408 задержки программируется нулевая задержка. Линии задержки, в которые поступают другие сигналы данных, программируются на все большие значения задержки, и линия задержки, в которую поступает сигнал с самым ранним временем прихода, соответствующий данным 306 на фиг.3, программируется на максимальную задержку. Таким образом, для приведенного на фиг.4 примера, данные 404 соответствуют сигналу данных с самым ранним временем прихода, при этом линия задержки устройства 408 программируется на максимальное значение задержки. При этом все сигналы данных, вводимые в микросхему 204, т.е. данные 402-404, выравниваются по сигналу данных с самым последним временем прихода. Хотя вариант осуществления изобретения, показанный на фиг.4, был продемонстрирован и описан для отдельных сигналов данных, очевидно, что принципы изобретения могут быть применены к группам сигналов данных, например к байтам данных или к любым другим группам сигналов данных. Такой альтернативный вариант осуществления изобретения будет укладываться в задаваемые формулой изобретения рамки.

Линии задержки устройств 406-408 программируются на предварительно выбранные значения задержки во время выполнения процедуры инициализационного выравнивания (ПИВ). ПИВ может выполняться при включении питания или при сбросе процессора 100 обработки данных, в которой имеется волновой конвейерный интерфейс 200. В варианте осуществления изобретения выполнение ПИВ может контролироваться сигналом ЦП 110, показанного на фиг.1. При выполнении ПИВ предварительно заданная синхронизирующая последовательность направляется по шине данных 222 посредством выбора 240 режима ПИВ, при этом мультиплексор 228 выводит предварительно заданную синхронизирующую последовательность. Синхронизирующая последовательность направляется со всеми сигналами данных, передаваемых по шине данных 222.

Синхронизирующая последовательность фиксируется схемами-защелками 412-414, которые принимают выходной сигнал линий задержки устройств 406-408. Вводимые в схемы-защелки 412-414 данные фиксируются по фронту тактового сигнала 236 ввода/вывода, который получается из тактового сигнала 206 шины с использованием буфера 234. Тактовый сигнал 236 ввода/вывода задерживается в линии устройства 410 задержки блока 232 приема данных. Задержанный тактовый сигнал ввода/вывода регенерируется в буфере 416 и направляется в схемы-защелки 412-414.

Управление линией устройства 410 задержки, а также линиями устройств 406-408 задержки производится с помощью конечного автомата 418. При выполнении ПИВ конечный автомат 418 регулирует программируемые задержки линий устройств 406-408 и 410 задержки в соответствии с захватом синхронизирующей последовательности схемами-защелками 412-414.

Выходы 420-422 соединены с соответствующими входами логической схемы 424 сравнения данных. Использование подходящей синхронизирующей последовательности позволяет произвести однозначное разрешение захвата синхронных данных в условиях отсутствия любой расфазировки данных. Одна такая последовательность представляет собой последовательность значений данных "100010001000". Эта последовательность является периодической, и ее период равен четырем периодам тактового сигнала ввода/вывода, такая последовательность используется для гибкого интерфейса, имеющего степень гибкости, равную четырем периодам тактового сигнала. Гибкий интерфейс описан в одновременно поданной заявителем заявке на патент США, озаглавленной "An Elastic Interface Apparatus and Method Therefor" ("Гибкий интерфейс и способ его применения"), которая включена в настоящее описание в качестве ссылки. Может использоваться и другая синхронизирующая последовательность, при условии, что такая синхронизирующая последовательность должна обеспечивать однозначное разрешение захвата синхронных данных. Например, в качестве альтернативного варианта может использоваться синхронизирующая последовательность, являющаяся дополнительной к вышеприведенной последовательности данных. Далее будет описан выбор задержек в линиях устройств 406-408 и 410 задержки, причем при этом будет описана работа конечного автомата 418.

На фиг.5А показана методика 500 выбора задержек с помощью конечного автомата 418. При выполнении шага 502 тактовый сигнал ввода/вывода регулируется по сигналу данных с последним временем прихода посредством выбора подходящей задержки для линии устройства 410 задержки. Шаг 502 будет дополнительно рассмотрен с использованием фиг.5Б и 5В. Сигналы данных выравниваются при выполнении шага 504, который будет дополнительно рассмотрен с использованием фиг. 5Г и 5Д. При выполнении шага 508 корректируется точка приема тактового сигнала ввода/вывода. Шаг 508 будет дополнительно рассмотрен с использованием фиг.5Е и 5Ж.

На фиг. 5Б приведена блок-схема шага 502 задержки тактового сигнала ввода/вывода. При выполнении шага 512 производится запуск ПИВ вместе с вводом синхронизирующей последовательности, как было описано выше. При выполнении шага 514 конечный автомат 418, показанный на фиг.4, определяет, соответствует ли синхронизирующая последовательность, зафиксированная схемами-защелками 412-414, тому же сигналу данных, который для вышеописанного примера синхронизирующей последовательности равен "1". Конечный автомат 418 определяет, был ли зафиксирован тот же сигнал данных, посредством определения того, был ли сброшен выход 426 RS-триггера 428. Выход 426 RS-триггера 428 контролируется логической схемой 424 сравнения данных, которая выявляет отсутствие совпадения, и в этом случае выдает положительный сигнал на свой выход 430. В том случае, если на все входы 421-423 логической схемы 424 сравнения данных поступает один и тот же сигнал данных, на выход 430 выдается отрицательный сигнал и при этом происходит сброс RS-триггера. Логическая схема 424 сравнения данных стробируется с помощью задержанного тактового сигнала 411 ввода/вывода, и при этом выходной сигнал поступает на выход 430 логической схемы 424 сравнения данных на основании фиксации данных схемами-защелками 412-414. Примером осуществления логической схемы 424 сравнения данных, соответствующим положительной логике, является использование логической функции НЕ-И для сигналов на входах 421-423 и стробирующего сигнала, получаемого на основании задержанного тактового сигнала 411. В альтернативном варианте примера осуществления с отрицательной логикой может использоваться логическая функция ИЛИ для входов 421-423 и стробирующего сигнала, получаемого на основании дополнения задержанного тактового сигнала 411. Такой вариант осуществления будет соответствовать рассмотренной выше дополнительной синхронизирующей последовательности.

Статистические вариации при задании задержек для линий устройств 406-408 и 410 задержек могут быть снижены посредством приема синхронизирующей последовательности в течение большого числа циклов задержанного тактового сигнала 411 ввода/вывода. Задержанный тактовый сигнал 411 ввода/вывода вызывает приращение показаний счетчика 432. Счетчик 432 выдает сигнал на выход 434 после предварительно заданного числа К задержанных периодов тактового сигнала 411 ввода/вывода, после чего происходит переброс триггера 432. Выход 434 счетчика 432 соединен с входом 436 сброса RS-триггера 428, в результате чего происходит сброс выхода 426. Может быть выполнена следующая синхронизирующая последовательность / последовательность выявления несовпадения. Если для любого цикла контроля будет выявлено несовпадение, то будет установлен RS-триггер 428.

Фиг. 5Б: если в течение периода контроля, определяемого значением целого числа К, на всех входах 421-423 логической схемы 424 сравнения данных будет один и тот же сигнал данных, то на шаге 514 будет выполнена ветвь "Да", и для методики 500 будет произведен переход к шагу 504. Для этого случая будет действовать приведенная на фиг.5В временная диаграмма, для которой еще не были заданы задержки для линий устройств 406-408 задержки. Тактовый сигнал 236 ввода/вывода задерживается с помощью линии устройства 410 задержки на величину Тd, и фронт t1 попадает в окно достоверности данных, определяемое временным интервалом ТW.

Первоначально длительность задержки Тd может быть равна нулю, при этом фронт T0 находится за пределами окна достоверности данных, и по фронту Т0 происходит фиксация значения "1" одной из схем-защелок 412-414, принимающих данные 306, и значения "0" схемами-защелками, принимающими данные 302 и 304. Возникает несовпадение. При этом выводится сигнал на выход 430 логической схемы 424 сравнения данных, и сигнал на выход 426 RS-триггера 428. В результате этого при выполнении шага 514 на фиг.5Б используется ветвь "Нет". При выполнении шага 516 конечный автомат 418 увеличивает время задержки для линии устройства 410 задержки.

Задержка увеличивается конечным автоматом 418 посредством направления сигнала "Вверх" в направлении подсчета 438 реверсивного счетчика 440. Значение счетчика 440 увеличивается в случае подачи счетчиком 432 сигнала на выход 434, что происходит в случае достижения счетчиком 432 конца интервала суммирования, задаваемого значением целого числа К. Показания реверсивного счетчика 440 направляются в блок 442 управления задержкой. Блок 442 управления задержкой декодирует показания счетчика и направляет соответствующий управляющий сигнал 444 в линию устройства 410 задержки, в результате чего линия устройства 410 задержки увеличивает длительность задержки Тd на предварительно заданное значение времени. (Программируемая линия устройства 410 задержки, которая может использоваться в изобретении, описана в одновременно поданной заявителем заявке на патент США, озаглавленной "Programmable Delay Loccked Loop" ("Устройство программируемой подстройки по задержке"), которая включена в настоящее описание в качестве ссылки. Затем с шага 502 задержки тактового сигнала ввода/вывода происходит возврат к шагу 514.

Если при выполнении шага 514 увеличенного значения Тd будет достаточно для помещения фронта t1 в окно достоверности данных, то тогда при выполнении шага 514 будет использоваться ветвь "Да", как это описано выше. В противном случае время задержки для линии устройства 410 задержки будет снова увеличено при выполнении шага 516, и шаг 502 задержки тактового сигнала ввода/вывода будет циклически повторяться с выполнением шагов 514 и 516 до тех пор, пока фронт t1 не попадет в окно достоверности данных. После этого конечный автомат 418 перейдет к шагу 504, на котором происходит выравнивание данных.

Шаг 504 выравнивания данных подробно описывается с использованием фиг. 5Г. При выполнении шага 504 производится программирование множества линий устройств 406- 408 задержки. При выполнении шага 518 для выполнения программирования выбирается первая линия задержки, соответствующая первому сигналу данных. (Это может соответствовать инициализации индекса j для первого значения, и этот индекс может быть равен нулю). При выполнении шага 520 производится сравнение данных. Сравнение данных при выполнении шага 520 производится точно так же, как сравнение данных при выполнении шага 514 на фиг. 5Б, и поэтому не будет описываться повторно.

Если все сигналы данных синхронизированы, то тогда при выполнении шага 522 будет задано приращение задержки для j-й линии задержки, соответствующей j-му сигналу данных. Первоначально ввиду выполнения шага 502 регулировки тактового сигнала ввода-вывода для шага 520 будет использоваться ветвь "Да". После приращения задержки при выполнении шага 522 будет снова выполнен шаг 520 сравнения данных. Затем шаг 504 выравнивания данных будет циклически повторяться между шагами 520 и 522, пока не будет потеряна синхронизация данных и на шаге 520 не будет выполнена ветвь "Нет", на которой при выполнении шага 524 задержка j-го сигнала данных будет уменьшена на один шаг приращения задержки. Таким образом, может быть произведено выравнивание фазы j-го сигнала данных по тактовому сигналу ввода/вывода.

Для большей ясности следует снова обратиться к фиг.5В. Если для примера сначала предположить, что при выполнении шагов 520 и 522 j-й сигнал данных является сигналом данных с самым поздним временем прихода - данные 304, тогда добавление первого приращения задержки для соответствующей линии задержки приведет к такому смещению данных 304, что их фронт t2 будет приходить после фронта t1 задержанного тактового сигнала 411 ввода/вывода. Затем при выполнении сравнения данных на шаге 520 сравнение будет происходить по ветви "Нет" с выполнением шага 524, на котором будет вычтено одно приращение задержки, добавленное при выполнении шага 522. Таким образом, для сигнала с самым поздним временем прихода не будет добавлена дополнительная задержка. Это является желательным для выполнения шага 504 выравнивания данных, так как сигнал с самым поздним временем прихода может использоваться в качестве опорного сигнала для выравнивания всех остальных сигналов данных.

Теперь для примера рассмотрено выполнение шагов 520 и 522 для сигнала данных, являющегося сигналом данных с самым ранним временем прихода - данные 306 на фиг.5В. Для сигнала данных с самым ранним временем прихода производится многократное приращение задержки для соответствующей программируемой линии задержки посредством повторяющегося выполнения шагов 520 и 522 до тех пор, пока фронт t3 этого сигнала не будет приходить позже фронта t1 задержанного тактового сигнала 411 ввода/вывода. После этого, как уже описывалось ранее для данных 304, для шага 520 сравнения данных будет выполнена ветвь "Нет" с шагом 524, на котором для программируемой задержки будет вычтено одно приращение задержки, и фронт t3 будет выровнен по фронту t1 задержанного тактового сигнала 411 ввода/вывода.

После выравнивания j-гo сигнала данных на шаге 526 шага 504 выравнивания данных определяется, были ли запрограммированы все задержки сигналов данных. Если нет, то выполняется шаг 527, и шаг 504 выравнивания выполняется для следующей линии задержки, затем производится возврат к шагу 520. После регулировки всех линий задержки все сигналы данных оказываются выровненными по фронту t1 задержанного тактового сигнала 411 ввода/вывода, как схематически показано на временной диаграмме на фиг.5Д, и от шага 504 выравнивания происходит переход к шагу 506 методики 500.

На шаге 506 корректировки точки приема тактового сигнала фронт t1 задержанного тактового сигнала 411 ввода/вывода может быть смещен к центру окна достоверности данных. Хотя фронт тактового сигнала может быть сцентрирован при запуске, однако, на приемнике может произойти его расфазировка, вызываемая различиями времени ожидания для путей, шумами и т. д. Шаг 506 корректировки положения точки приема выравнивает тактовый сигнал. Далее на шаге 528 выполняется сравнение данных (фиг.5Е).

Первоначально ввиду выполнения шага 506 выравнивания данных для шага 526 сравнения выполняется ветвь "Да" к шагу 540, и при выполнении шага 530 происходит приращение времени задержки, запрограммированного для линии устройства 410 задержки, на один шаг приращения. После этого для шага 506 корректировки точки приема тактового сигнала происходит возврат к шагу 528, на котором снова производится сравнение данных. Затем для шага 506 корректировки точки приема тактового сигнала производится циклическое повторение шагов 528 и 530 до тех пор, пока на шаге 528 сравнения данных не произойдет несовпадение, что будет указывать на то, что фронт t1 задержанного тактового сигнала 411, обозначенный t1', перешел на позднюю сторону t1 окна достоверности данных, фиг.5Ж. Затем для шага 528 сравнения данных выполняется ветвь "Нет", и на шаге 532 сохранятся значение, подсчитанное счетчиком 440.

Затем на шаге 506 корректировки точки приема тактового сигнала определяется ранняя сторона окна достоверности данных. При выполнении шага 534 на одно значение приращения увеличивается задержка для линии устройства 410 задержки. Затем на шаге 536 выполняется сравнение данных. В связи с тем, что на шаге 534 фронт t1' был снова смещен в окно достоверности данных, то для шага 536 сравнения данных выполняется ветвь "Да" и задержка, запрограммированная для линии устройства 410 задержки, дополнительно уменьшается на одно значение приращения. После этого для шага 506 корректировки точки контроля тактового сигнала циклически повторяются шаги 536 и 538, пока при выполнении шага 536 сравнения данных не будет выявлено несовпадение. Это указывает на то, что фронт t1 задержанного тактового сигнала 411 ввода/вывода на фиг.5Ж поступил раньше ранней стороны te окна достоверности данных. Этот переход задержанного тактового сигнала 411 ввода/вывода обозначается t1''. После этого для шага 536 сравнения данных выполняется ветвь "Нет", и на шаге 540 сохраняется значение счетчика 440 для ранней стороны.

На шаге 542 для фазы задержанного тактового сигнала 411 ввода/вывода задается среднее значение для фронтов ранней и поздней сторон окна достоверности данных. На фиг.5Ж это соответствует сплошной части кривой задержанного тактового сигнала 411 ввода/вывода и фронту t1'''. После этого для шага 506 корректировки точки приема задержанного тактового сигнала происходит переход к шагу 508, и для методики 500 завершается использование режима ПИВ.

Устройство и способы, проиллюстрированные выше на примере вариантов осуществления изобретения, позволяют получить динамический волновой конвейерный интерфейс. Для множества поступающих в интерфейс сигналов данных производится их выравнивание относительно один другого с компенсацией разности синхронизации сигналов данных, разности путей между тактовым сигналом ввода/вывода и сигналами данных, а также конструктивных допусков для сигналов данных, например, в отношении подключения проводов к микросхеме, модулю и плате. В результате этого увеличивается ширина области сигнала данных. Интерфейс также корректирует тактовый сигнал для его центрирования по точке приема в середине окна достоверности данных, в результате чего могут быть компенсированы разности путей между тактовым сигналом ввода/вывода и данными, для подключения проводов к модулю и плате.

Заявленное изобретение относится к системам обработки данных, в частности к шинным интерфейсам. Техническим результатом является обеспечение возможности выравнивания данных на приемной стороне интерфейса. Для этого интерфейс содержит устройства задержки, схему задания каждого предварительно выбираемого периода задержки, логическую схему сравнения данных и схему для изменения предварительно выбранных периодов задержки. В способе сигналы данных, принимаемые от передающей схемы, задерживаются с помощью программируемого устройства задержки, соответствующего каждому сигналу, и затем фиксируются приемным устройством, программируемая задержка задается для каждого устройства задержки при проведении процедуры инициализации, в результате чего производится выравнивание каждого сигнала по последнему поступающему сигналу. Кроме того, фаза тактового сигнала ввода-вывода, управляющего фиксацией сигналов данных, регулируется таким образом, чтобы переход фиксации данных располагался практически посредине окна достоверности данных. 3 c. и 12 з.п. ф-лы, 5 ил.

| US 5229668 А, 20.07.1993 | |||

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ С ПРОЦЕССОРОМ | 1991 |

|

RU2033636C1 |

| RU 2058041 С1, 10.04.1996. | |||

Авторы

Даты

2003-10-10—Публикация

2000-03-03—Подача