ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к области техники обмена данными в промышленной сети и, в частности, к преобразователю протоколов между шиной CPCI и шиной ISA и соответствующему ему способу преобразования, которые подходят для обмена данными между центральными процессорами железнодорожных транспортных средств и устройствами с многофункциональной шиной транспортного средства MVB.

ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

Шина ISA (архитектура промышленного стандарта) представляет собой стандарт шины, предусмотренный корпорацией IBM для персональных компьютеров. Шина ISA имеет тактовую частоту 8 МГц и максимальную скорость передачи данных 16 Мбайт/с. Шина ISA имеет низкую скорость передачи и занимает значительную часть ресурсов центрального процессора. С развитием технологий создания шин шину ISA постепенно заменяют высокоскоростной шиной CPCI.

Шина CPCI (подключение компактных периферийных компонент) представляет собой стандарт спецификации интерфейса высокоскоростной шины, предложенный Международной группой изготовителей промышленных компьютеров в прошлом веке. Шина CPCI, основанная на спецификации электрического интерфейса стандартной шины PCI, является шиной с высокой совместимостью и высокой надежностью; и вследствие этого тактовая частота шины может достигать 66 МГц.

Шины ISA высоко совместимы. С многолетним накоплением технологий появляется большое количество устаревшей продукции шины ISA. Благодаря возможности горячего подключения, высокой совместимости, высокой надежности и высокой скорости передачи шины CPCI широко применяются в контроллерах тяги железнодорожных транспортных средств. Однако интерфейсы шин ISA все еще широко применяются в коммуникационных устройствах MVB железнодорожных транспортных средств. Осуществление стабильного и надежного обмена данными между высокоскоростной шиной CPCI и низкоскоростной шиной ISA с предоставлением шинного преобразователя между шиной CPCI и шиной ISA является проблемой, с которой сталкиваются все специалисты по разработке железнодорожных транспортных средств.

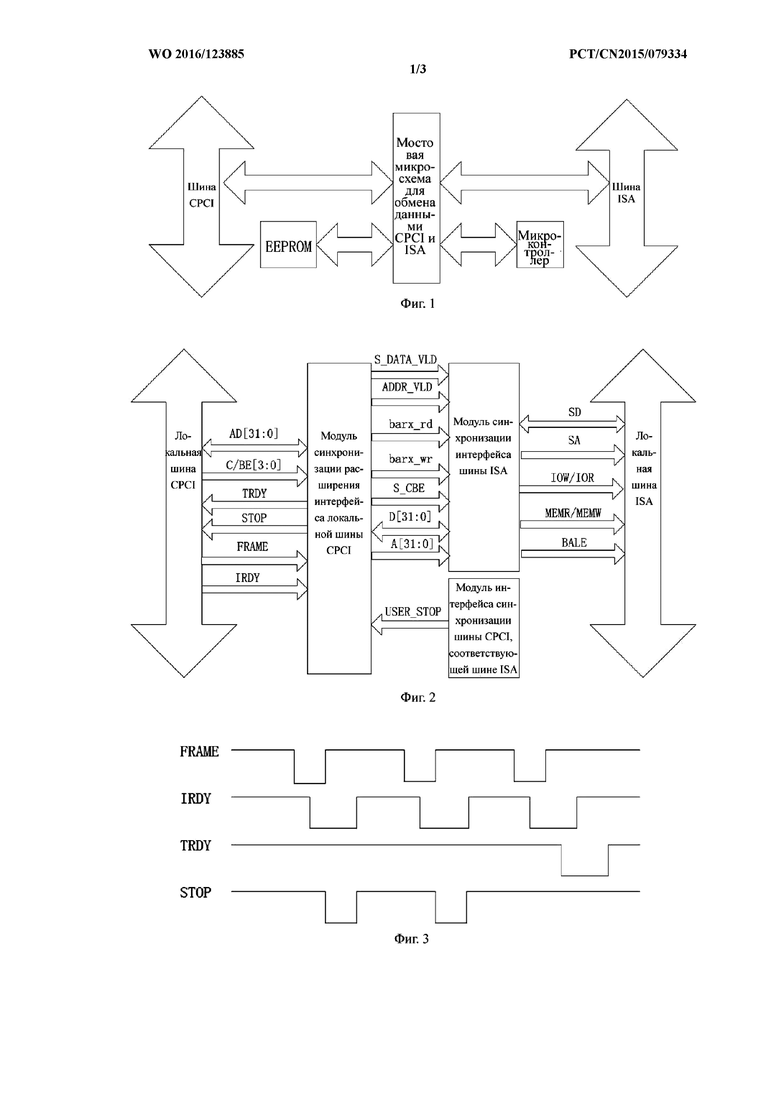

Ключевая технология для создания стабильного и надежного обмена данными между высокоскоростной шиной CPCI и низкоскоростной шиной ISA заключается в разработке локального интерфейса шины CPCI, который соответствует интерфейсу шины ISA. В настоящее время самым распространенным решением реализации является использование специально предназначенных мостовых микросхем, изготовленных компаниями PLX и AMCC, для преобразования с обеспечением обмена данными между устройством шины CPCI и устройством шины ISA. Принимая во внимание режим работы шины мостовой микросхемы, предлагается стандартный интерфейс шины ISA, при этом интерфейс шины ISA на мостовой микросхеме непосредственно соединяется с интерфейсом шины ISA на устройстве; EEPROM (электрически стираемая перепрограммируемая постоянная память) используется для хранения информации о конфигурации мостовой микросхемы; разумеется, необходим микроконтроллер для обеспечения тактового сигнала шины ISA, и, таким образом, адрес шины ISA, управляющий сигнал и интерфейс шины CPCI соответствуют друг другу. Архитектура аппаратного обеспечения конкретного варианта осуществления показана на фиг. 1. Благодаря выполненной таким образом архитектуре специалисты по разработке опустили ее рассмотрение, тем самым сэкономив усилия, чтобы направить их на углубленное понимание спецификаций интерфейса CPCI. Это является невыгодным для поддержки существующей продукции и разработки последующей продукции. Что еще хуже, пользователь не может контролировать синхронизацию шины CPCI в соответствии со своими идеями из-за ограничений аппаратными мостовыми микросхемами. Кроме того, это увеличивает нагрузку для разработчика аппаратного обеспечения. Другими словами, разрабатывается дополнительная интерфейсная плата для преобразования с шины CPCI на шину ISA, таким образом увеличиваются затраты на проектирование; более того, большинство пользователей используют только некоторые функции преобразования мостовой микросхемы, что приводит таким образом к большому объему растрачивания ресурсов.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Целью настоящего изобретения является предоставление преобразователя протоколов между шиной CPCI и шиной ISA и соответствующего ему способа преобразования для того, чтобы в известном уровне техники решить проблему, которая заключается в том, что прямой обмен данными между шиной CPCI на центральном процессоре и шиной ISA на устройстве MVB не может быть реализован.

В настоящем изобретении используются следующие технические решения.

Поскольку обмен данными между основным устройством управления центральным процессором и панелью управления в имеющемся контроллере тяги поезда выполняется с помощью стандартной шины CPCI, при выполнении обмена данными в реальном времени между основным устройством управления центральным процессором и устройством MVB, имеющим интерфейс шины ISA на панели управления, выполнен преобразователь протоколов между шиной CPCI и шиной ISA для того, чтобы сохранить место на панели, улучшить соотношение затрат и производительности и универсальность конструкции. Преобразователь протоколов содержит модуль синхронизации расширения интерфейса локальной шины CPCI, модуль синхронизации интерфейса шины ISA, модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, и модуль управления тактовой синхронизацией.

Модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI посредством сигнала адреса/данных AD [31:0], сигнала команды/разрешения байтов C/BE [3:0], сигнала готовности к действию ведомого устройства TRDY, стоп-сигнала передачи данных STOP, сигнала периода цикла FRAME и сигнала готовности к действию ведущего устройства IRDY;

при этом модуль синхронизации интерфейса шины ISA обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала разрешения передачи данных S_DATA_VLD, сигнала разрешения адреса ADDR_VLD, сигнала разрешения считывания barx_rd, сигнала разрешения записи barx_wr, сигнала разрешения байтов S_CBE, сигнала данных D [31:0] и сигнала адреса A [31:0];

модуль синхронизации интерфейса шины ISA обменивается данными с локальной шиной ISA посредством сигнала данных SD, сигнала адреса SA, сигнала считывания/записи устройства ввода-вывода IOW/IOR, сигнала считывания/записи c устройства памяти MEMR/MEMW, сигнала защелки адреса BALE;

модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала прерывания и повторного соединения USER_STOP; и

модуль управления тактовой синхронизацией обеспечивает рабочую синхронизацию для модуля синхронизации расширения интерфейса локальной шины CPCI, модуля синхронизации интерфейса шины ISA и модуля интерфейса синхронизации шины CPCI, соответствующей шине ISA.

Предпочтительно, когда модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI, и когда шина CPCI получает доступ в виде ввода/вывода, сигнал ожидания S_WAIT включен в операцию считывания/записи шины CPCI для управления сигналом готовности к действию ведомого устройства TRDY шины CPCI.

Предпочтительно, когда модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI, и когда шина CPCI получает доступ в виде памяти, стоп-сигнал передачи данных STOP включен в операцию считывания/записи шины CPCI; и стоп-сигнал передачи данных STOP прерван посредством сигнала прерывания и повторного соединения USER_STOP.

По сравнению с известным уровнем техники настоящее изобретение имеет следующие преимущества:

1) удобство в работе: преобразователь протоколов между шиной CPCI и шиной ISA выполнен на основе FPGA (программируемой логической интегральной схемы) и общепринятые мостовые микросхемы преобразования заменяют преобразователями протоколов, при этом не меняя структуру контроллера тяги и другие устройства в системе;

2) высокий уровень гибкости: синхронизация преобразования между шиной CPCI и шиной ISA может быть настроена по мере необходимости для обеспечения различных функций преобразования; и

3) многообразие функций: поддерживается 8-разрядная или 16-разрядная шина ISA и поддерживается работа устройства шины ISA устройством шины CPCI в виде ввода/вывода или в виде памяти.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

На фиг. 1 изображено схематическое структурное представление общепринятого обмена данными между шиной CPCI и шиной ISA.

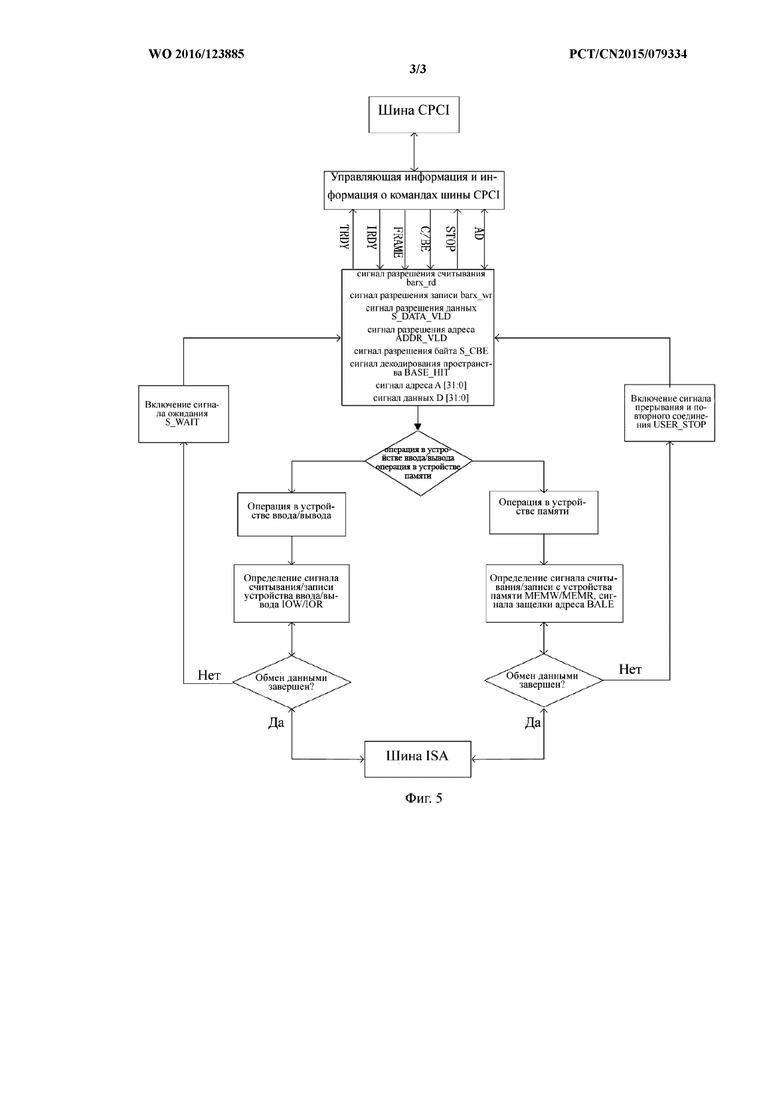

На фиг. 2 изображено схематическое структурное представление преобразователя протоколов.

На фиг. 3 изображена конкретная диаграмма синхронизации сигналов TRDY, STOP, FRAME и IRDY.

На фиг. 4 изображена частичная диаграмма синхронизации доступа считывания в виде ввода/вывода преобразователем протоколов.

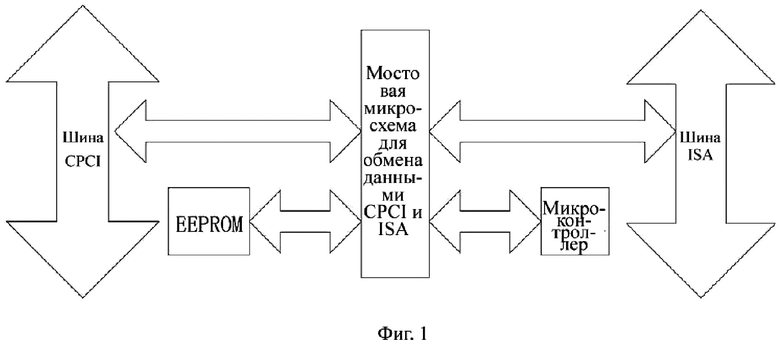

На фиг. 5 изображена блок-схема доступа преобразователем протоколов.

Подробное описание

Для того чтобы сделать цели, технические решения и преимущества вариантов осуществления изобретения настоящего изобретения более ясными, технические решения в вариантах осуществления настоящего изобретения будут описаны ясно и полностью со ссылкой на прилагаемые графические материалы. Очевидно, описанные варианты осуществления представляют собой всего лишь некоторые, но не все варианты осуществления настоящего изобретения. На основе вариантов осуществления настоящего изобретения все другие варианты осуществления, полученные специалистами в данной области техники без приложения каких-либо творческих усилий, должны попадать в объем охраны настоящего изобретения.

Вариант осуществления 1

Преобразователь протоколов между шиной CPCI и шиной ISA предусмотрен для обеспечения обмена данными в реальном времени между основным устройством управления, содержащим интерфейс шины CPCI, и устройством MVB, содержащим интерфейс шины ISA. Преобразователь протоколов в основном состоит из четырех модулей, соответственно: модуль синхронизации расширения интерфейса локальной шины CPCI, модуль синхронизации интерфейса шины ISA, модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, и модуль управления тактовой синхронизацией.

Модуль синхронизации расширения интерфейса локальной шины CPCI в основном используется для конфигурирования пространства доступа ввода/вывода/памяти шины CPCI, управления доступом считывания/записи шины CPCI, декодирования адресов и декодирования команд. Интерфейсное соединение между локальной шиной CPCI и модулем синхронизации расширения интерфейса локальной шины CPCI является таким, как показано на фиг. 2. Основными сигналами между ними двумя являются: сигнал адреса/данных AD [31:0], сигнал команды/разрешения байтов C/BE [3:0], сигнал готовности к действию ведомого устройства TRDY, стоп-сигнал передачи данных STOP, сигнал периода цикла FRAME и сигнал готовности к действию ведущего устройства IRDY.

Для стоп-сигнала передачи данных STOP факт того, что шина CPCI является высокоскоростным устройством, в то время как шина ISA является низкоскоростным устройством, и шина CPCI является быстрой при операции считывания/записи, так что устройство MVB, которое напрямую обменивается данными с шиной CPCI, может с трудом давать ответ, приводит к высокой вероятности потери пакета данных. Когда шина CPCI получает доступ в виде ввода/вывода, сигнал ожидания S_WAIT включают в операцию считывания/записи шины CPCI для управления сигналом готовности к действию ведомого устройства TRDY шины CPCI. Когда шина CPCI получает доступ в виде памяти, стоп-сигнал передачи данных STOP включен в операцию считывания/записи шины CPCI; до завершения текущей операции устройства памяти шина CPCI постоянно находится в состоянии прерывания и повторного соединения, так что шина CPCI постоянно запрашивает текущие операции считывания/записи; и шина CPCI будет инициировать следующий доступ для считывания/записи, пока в предыдущую операцию не будет включен стоп-сигнал передачи данных STOP. Стоп-сигнал передачи данных STOP отправляется ведомым устройством; когда стоп-сигнал передачи данных STOP допустимый, это указывает на то, что ведомое устройство запрашивает ведущее устройство о завершении текущей передачи данных. На фиг. 3 изображена конкретная диаграмма синхронизации сигнала готовности к действию ведомого устройства TRDY, стоп-сигнала передачи данных STOP, сигнала периода цикла FRAME и сигнала готовности к действию ведущего устройства IRDY.

Интерфейсное соединение между модулем синхронизации расширения интерфейса локальной шины CPCI и модулем синхронизации интерфейса шины ISA является таким, как показано на фиг. 2. Основными сигналами между ними двумя являются: сигнал разрешения передачи данных S_DATA_VLD, сигнал разрешения адреса ADDR_VLD, сигнал разрешения считывания barx_rd, сигнал разрешения записи barx_wr, сигнал разрешения байта S_CBE, сигнал данных D [31:0] и сигнал адреса A [31:0].

Команда исполнения с шины CPCI распознается модулем IP-ядра компании XILINX для генерирования сигнала разрешения считывания/записи S_WRDN, сигнала разрешения адреса ADDR_VLD, сигнала разрешения передачи данных S_DATA_VLD, сигнала разрешения байта S_CBE и сигнала декодирования пространства BASE_HIT.

Для сигнала разрешения передачи данных S_DATA-VLD, поскольку шина CPCI и шина ISA несовместимы на скорости считывания/записи, создается промежуточная область буферизации данных BUFFER. То есть перед выполнением операции записи шины CPCI данные шины CPCI записываются в область буферизации данных BUFFER, а затем передаются в шину ISA; и перед выполнением операции считывания шины CPCI данные шины ISA передаются в область буферизации данных BUFFER, а затем передаются в шину CPCI.

Сигнал разрешения считывания barx_rd и сигнал разрешения записи barx_wr получают следующим образом: в текущих контроллерах тяги устройство MVB, основанное на шинах ISA, может представлять собой устройство ввода-вывода или устройство памяти или и то, и другое, поскольку способы исполнения шин ISA, поддерживаемых устройствами MVB от разных изготовителей, разные, пространство доступа шины CPCI должно быть сконфигурировано в соответствии с действительными требованиями; затем определяется сигнал выбора микросхемы устройства MVB в соответствии с сигналом адреса и сигналом разрешения адреса ADDR_VLD, предусмотренными шиной CPCI; затем определяется пространство ввода/вывода/памяти текущей операции путем дополнительного рассмотрения сигнала считывания/записи S_WRDN и сигнала декодирования пространства BASE_HIT; и, наконец, получают использованные в действительности сигнал разрешения считывания barx_rd и сигнал разрешения записи barx_wr. При этом x в сигнале разрешения считывания barx_rd представляет выбранное пространство, x = 0, 1 или 2; и x в сигнале разрешения записи barx_wr представляет выбранное пространство, x = 0, 1 или 2.

Интерфейсное соединение между модулем интерфейса синхронизации шины CPCI, соответствующей шине ISA, и модулем синхронизации расширения интерфейса локальной шины CPCI является таким, как показано на фиг. 2. Основным сигналом между ними двумя является сигнал прерывания и повторного соединения USER_STOP, который в основном используется для прерывания стоп-сигнала передачи данных STOP. Устройство шины CPCI инициирует доступ к устройству шины ISA, и при доступе в виде памяти модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, отправляет сигнал прерывания и повторного соединения USER_STOP в режиме реального времени для прерывания стоп-сигнала передачи данных STOP, чтобы оставить достаточно времени устройству шины ISA для завершения данного доступа считывания/записи. Таким образом, проблема того, что шина CPCI и шина ISA несовместимы на рабочей скорости считывания-записи, решена.

Интерфейсное соединение между модулем синхронизации интерфейса шины ISA и локальной шиной ISA является таким, как показано на фиг. 2. Основными сигналами между ними двумя являются: сигнал данных SD, сигнал адреса SA, сигнал считывания/записи устройства ввода-вывода IOW/IOR, сигнал считывания/записи с устройства памяти MEMR/MEMW и сигнал защелки адреса BALE.

Модуль управления тактовой синхронизацией обеспечивает рабочую синхронизацию для модуля синхронизации расширения интерфейса локальной шины CPCI, модуля синхронизации интерфейса шины ISA и модуля интерфейса синхронизации шины CPCI, соответствующей шине ISA, посредством внутренней сети синхронизации FPGA и цепи фазовой синхронизации.

На фиг. 4 изображена частичная диаграмма синхронизации доступа считывания в виде ввода/вывода преобразователем протоколов.

На фиг. 5 изображена блок-схема доступа преобразователем протоколов. Основное устройство управления центральным процессором получает доступ к устройству MVB с интерфейсом шины ISA посредством шины CPCI следующим образом:

1) происходит определение пространства доступа ввода/вывода/памяти шины CPCI, включение стоп-сигнала передачи данных STOP, когда шина CPCI получает доступ в виде памяти, и включение сигнала ожидания S_WAIT для ожидания готовности устройства шины ISA, когда шина CPCI получает доступ в виде ввода/вывода;

2) определяются сигнал действительного адреса SA и режим доступа для шины CPCI для доступа к шине ISA посредством сигнала разрешения доступа ADDR_VLD, сигнала разрешения считывания barx_rd, сигнала разрешения записи barx_wr и сигнала разрешения байта S_CBE, при этом режим доступа содержит операцию записи и операцию считывания;

3) определяется сигнал защелки адреса BALE шины ISA;

4) принимается решение на счет данных в байтах, разрешенных в 32-разрядных данных, в соответствии с сигналом разрешения байта S_CBE; и соответствующие 8-разрядные данные или 16-разрядные данные убираются с промежуточной области буферизации данных BUFFER для взаимодействия данных с устройством MVB;

5) происходит определение сигнала считывания/записи устройства ввода-вывода IOW/IOR или сигнал считывания/записи устройства памяти MEMR/MEMW в соответствии с шириной импульса сигнала считывания/записи, заданной шиной ISA, и, таким образом, основное устройство управления центральным процессором получает доступ к устройству MVB с интерфейсом шины ISA посредством шины CPCI в режиме реального времени.

Специалистам в данной области техники следует понимать, что приложенные графические материалы всего лишь являются схематическими видами одного предпочтительного варианта осуществления, и последовательность операций в приложенных графических материалах не является обязательной для осуществления настоящего изобретения.

Наконец, следует отметить, что вышеизложенные варианты осуществления всего лишь используются для описания технических решений настоящего изобретения, а не ограничения настоящего изобретения. Несмотря на то что настоящее изобретение было описано подробно со ссылкой на вышеизложенные варианты осуществления, специалистам в данной области техники следует понимать, что модификации могут быть сделаны по отношению к техническим решениям, приведенным в вышеизложенных вариантах осуществления, или что эквивалентные замены могут быть сделаны по отношению к некоторым техническим признакам. Эти модификации или замены не должны приводить к тому, что сущность соответствующих технических решений будет выходить за пределы технических решений вариантов осуществления настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА РЕГУЛИРОВАНИЯ ТЯГОВОГО УСИЛИЯ ДЛЯ НЕСКОЛЬКИХ ЭЛЕКТРОСЕКЦИЙ | 2015 |

|

RU2641558C1 |

| КОМПЬЮТЕРНАЯ СИСТЕМА, ИМЕЮЩАЯ ШИННЫЙ ИНТЕРФЕЙС | 1995 |

|

RU2140667C1 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2002 |

|

RU2221270C2 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| УСТРОЙСТВО КОММУТАЦИИ, СОДЕРЖАЩЕЕ ШИНЫ ВРЕМЕННЫХ ИНТЕРВАЛОВ И НЕСКОЛЬКО БУФЕРОВ | 2002 |

|

RU2291479C2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| СКООРДИНИРОВАННЫЕ ОПЕРАЦИИ ЗАПИСИ ПО АДРЕСНОМУ КАНАЛУ ШИНЫ | 2007 |

|

RU2405195C2 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

Изобретение относится к технологиям сетевой связи. Технический результат заключается в повышении скорости передачи данных в сети. В способе определяют пространства доступа ввода/вывода/памяти шины CPCI, включают стоп-сигнал передачи данных STOP, когда шина CPCI получает доступ в виде памяти, и включают сигнал ожидания S_WAIT для ожидания готовности устройства шины ISA, когда шина CPCI получает доступ в виде ввода/вывода; для определения сигнала действительного адреса SA и режима доступа для шины CPCI для доступа к шине ISA используются сигнал разрешения адреса ADDR_VLD, сигнал разрешения считывания barx_rd, сигнал разрешения записи barx_wr и сигнал разрешения байта S_CBE, определяют сигнал защелки адреса BALE шины ISA; принимают решение на счет данных в байтах, разрешенных в 32-разрядных данных, определяют сигнал считывания/записи устройства ввода-вывода IOW/IOR или сигнал считывания/записи устройства памяти MEMR/MEMW в соответствии с шириной импульса сигнала считывания/записи, заданной шиной ISA. 2 н. и 2 з.п ф-лы, 5 ил.

1. Преобразователь протоколов между шиной CPCI и шиной ISA, отличающийся тем, что преобразователь протоколов содержит модуль синхронизации расширения интерфейса локальной шины CPCI, модуль синхронизации интерфейса шины ISA, модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, и модуль управления тактовой синхронизацией;

при этом модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI посредством сигнала адреса/данных AD [31:0], сигнала команды/разрешения байтов С/ВЕ [3:0], сигнала готовности к действию ведомого устройства TRDY, стоп-сигнала передачи данных STOP, сигнала периода цикла FRAME и сигнала готовности к действию ведущего устройства IRDY;

модуль синхронизации интерфейса шины ISA обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала разрешения передачи данных S_DATA_VLD, сигнала разрешения адреса ADDR_VLD, сигнала разрешения считывания barx_rd, сигнала разрешения записи barx_wr, сигнала разрешения байта S_CBE, сигнала данных D [31:0] и сигнала адреса А [31:0];

модуль синхронизации интерфейса шины ISA обменивается данными с локальной шиной ISA посредством сигнала данных SD, сигнала адреса SA, сигнала считывания/записи устройства ввода-вывода IOW/IOR, сигнала считывания/записи с устройства памяти MEMR/MEMW, сигнала защелки адреса BALE;

модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала прерывания и повторного соединения USER_STOP; и

модуль управления тактовой синхронизацией обеспечивает рабочую синхронизацию для модуля синхронизации расширения интерфейса локальной шины CPCI, модуля синхронизации интерфейса шины ISA и модуля интерфейса синхронизации шины CPCI, соответствующей шине ISA.

2. Преобразователь протоколов между шиной CPCI и шиной ISA по п. 1, отличающийся тем, что, когда модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI и когда шина CPCI получает доступ в виде ввода/вывода, сигнал ожидания S_WAIT включен в операцию считывания/записи шины CPCI для управления сигналом готовности к действию ведомого устройства TRDY шины CPCI.

3. Преобразователь протоколов между шиной CPCI и шиной ISA по п. 1, отличающийся тем, что, когда модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI и когда шина CPCI получает доступ в виде памяти, стоп-сигнал передачи данных STOP включен в операцию считывания/записи шины CPCI; и стоп-сигнал передачи данных STOP прерван посредством сигнала прерывания и повторного соединения USER_STOP.

4. Способ преобразования протокола для шины CPCI и шины ISA по п. 1, отличающийся тем, что

1) происходит определение пространства доступа ввода/вывода/памяти шины CPCI, включение стоп-сигнала передачи данных STOP, когда шина CPCI получает доступ в виде памяти, и включение сигнала ожидания S_WAIT для ожидания готовности устройства шины ISA, когда шина CPCI получает доступ в виде ввода/вывода;

2) для определения сигнала действительного адреса SA и режима доступа для шины CPCI для доступа к шине ISA используются сигнал разрешения адреса ADDR_VLD, сигнал разрешения считывания barx_rd, сигнал разрешения записи barx_wr и сигнал разрешения байта S_CBE, при этом режим доступа включает операцию записи и операцию считывания;

3) происходит определение сигнала защелки адреса BALE шины ISA;

4) принимается решение на счет данных в байтах, разрешенных в 32-разрядных данных, в соответствии с сигналом разрешения байта S_CBE; и соответствующие 8-разрядные данные или 16-разрядные данные убираются с промежуточной области буферизации данных BUFFER для взаимодействия данных с устройством MVB;

5) происходит определение сигнала считывания/записи устройства ввода-вывода IOW/IOR или сигнал считывания/записи устройства памяти MEMR/MEMW в соответствии с шириной импульса сигнала считывания/записи, заданной шиной ISA, и, таким образом, основное устройство управления центральным процессором получает доступ к устройству MVB с интерфейсом шины ISA посредством шины CPCI в режиме реального времени.

| CN 103530256 A, 22.01.2014 | |||

| CN 102411553 A, 11.04.2012 | |||

| CN 101963948 A, 02.02.2011. |

Авторы

Даты

2017-05-16—Публикация

2015-05-20—Подача