Предлагаемое устройство относится к области обработки сигналов посредством решения обратной задачи с целью повышения их соответствия входным для устройства сигналам и, в первую очередь, к области обработки сигналов с целью подавления межсимвольной интерференции и соответствующего повышения разрешения их элементов, повышения скорости передачи данных при той же физической полосе частот устройства.

Известны [1] устройства для обработки сигналов, содержащие последовательно соединенные частотный фильтр (ЧФ) и оптимальный восстанавливающий фильтр, обеспечивающие при гауссовом шуме минимальную среднеквадратичную ошибку восстановления. Недостатком этих устройств является недостаточное разрешение элементов сигналов.

Известны [2] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и конвольвер и обеспечивающие примерно вдвое более высокое разрешение элементов сигнала. Эти устройства имеют недостаток, состоящий в высоком уровне осцилляции (паразитных осцилляций, «хвостов», боковых лепестков) за пределами подлежащих разрешению элементов входного сигнала и в пониженном контрасте элементов и групп элементов малой протяженности.

Известны [3] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и интерполятор, в которых представление сигналов в базисе сфероидальных волновых функций и соответствующая более высокая концентрация энергии в области низких частот обеспечивают некоторое понижение уровня паразитных осцилляций и повышение разрешения. Эти устройства имеют недостаток, состоящий в недостаточно пониженном уровне паразитных осцилляций, в низком контрасте малопротяженных элементов сигнала и в недостаточном разрешении элементов сигнала.

Общей чертой названных устройств является максимизация разрешения элементов сигнала в рамках имеющейся физической полосы частот, что лишь незначительно уменьшает межсимвольную интерференцию (МСИ) и чем обусловлены основные указанные их недостатки. Более перспективны в части повышения разрешения элементов сигнала указанные ниже устройства, в которых действиями в ограниченной полосе частот достигается более широкополосный результат.

Известны [4] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и блок реставрации сигналов методом Монте-Карло, обеспечивающие не ограниченные полосой частот ЧФ крутизну перепадов и расстояние разрешения. Недостатком таких устройств является низкая вероятность соответствия реставрированного сигнала входному, поскольку принцип их действия базируется на интегральной информации о сигнале (энергия), причем не входном для устройства, а входном для блока реставрации.

Известны устройства [5] для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и блок редукции устройства к квазисовершенному, предназначенный для интерполирования отсчетов сигнала, выявления в них перепадов и формирования сокращенного описания сигнала в виде последовательности перепадов с характеристиками, приближенными к характеристикам перепадов во входном сигнале. Недостатком таких устройств являются недостаточная чувствительность к малоконтрастным элементам сигнала, низкое быстродействие и высокая сложность, что обусловлено принципом действия - синтезом сигнала на основе выявления перепадов и их коррекции по результатам сравнения реакций ЧФ на входной и синтезированный сигналы. А именно, некоторые перепады, особенно малого контраста, могут быть пропущены из-за их маскирования осцилляциями, то есть из-за собственного шума устройства; низкое быстродействие и высокая сложность связаны с необходимостью вычисления реакции ЧФ на синтезированный сигнал и с необходимостью ее сравнения с реакцией ЧФ на входной сигнал.

От этого недостатка свободны устройства [6] для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и блок редукции устройства к совершенному, производящий подмену прошедших через устройство узкополосных элементов сигнала исходными широкополосными элементами сигнала, действующего на входе системы. Это непосредственно и радикально уменьшает межсимвольную интерференцию и соответственно повышает разрешение элементов сигнала, пропускную способность устройства. Иначе говоря, в результате обработки сигнала в блоке редукции устройства к совершенному устройство обретает виртуальную полосу частот, которая шире исходной физической полосы частот устройства.

Однако и эти устройства имеют недостаток, состоящий в недостаточно высоком разрешении элементов сигнала, в недостаточной чувствительности к малоконтрастным элементам сигнала, в низком быстродействии и в высокой сложности, что обусловлено принципом действия, который состоит в эвристическом (недетерминированном) характере подмены прошедших через устройство узкополосных элементов сигнала исходными широкополосными элементами сигнала, которая имеет итеративный вид с контролем завершения процедуры по критерию достижения обрабатываемым сигналом заранее заданных или динамично определяемых характеристик. А именно, элементы малого контраста могут быть пропущены из-за снижения точности представления сигнала при итеративных вычислениях, то есть из-за собственного шума устройства; низкое быстродействие и высокая сложность обусловлены эвристическим, итеративным характером вычислений и необходимостью средств, контролирующих завершение синтеза восстановленного сигнала.

Предлагаемое изобретение направлено на уменьшение собственного шума устройства за счет исключения эвристических итеративных вычислений, а также на исключение средств, контролирующих завершение синтеза восстановленного сигнала.

Решение этой задачи обеспечивает:

- повышение разрешения элементов сигнала, в том числе, малоконтрастных;

- повышение чувствительности к малоконтрастным элементам сигнала;

- повышение быстродействия;

- уменьшение сложности устройства.

Для этого (в первом варианте предлагаемого устройства) в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно вводится блок редукции к совершенному прибору (блок РСП), предназначенный для интерполирования поступающих на его вход из дискретизатора отсчетов, определения (с использованием оценок коэффициентов разложения совокупности интерполированых отсчетов в обобщенный ряд Фурье по отсчетам ортогонализированных измеренных или запасенных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала) коэффициентов веса базисных конечной длительности элементов (сигналов) во входном сигнале и формирования отсчетов выходного для устройства сигнала в виде отсчетов оценки входного для устройства сигнала посредством суперпозиции базисных сигналов с учетом коэффициентов их веса во входном сигнале (накопительного суммирования произведений отсчетов базисных элементов входного сигнала и коэффициентов веса базисных элементов во входном сигнале), причем вход блока РСП соединен с выходом дискретизатора, а выход является выходом устройства. Это позволяет в дискретизаторе получать отсчеты прошедшего через ЧФ сигнала, в блоке РСП интерполировать полученные из дискретизатора отсчеты, по интерполированным отсчетам с использованием отсчетов ортогонализированных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала определять коэффициенты веса базисных элементов во входном сигнале и посредством накопительного суммирования отсчетов базисных элементов входного сигнала, помноженных на коэффициенты веса базисных элементов во входном сигнале, формировать отсчеты выходного сигнала в виде отсчетов оценки входного для устройства сигнала, тем самым с проектным допуском выполняя совершенное широкополосное (с подавленной межсимвольной интерференцией) восстановление сигнала вплоть до предельно разрешаемых и с предельно малой амплитудой его элементов.

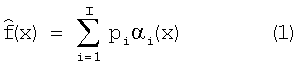

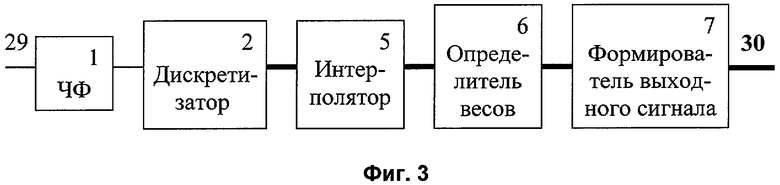

Входной для устройства представимый непрерывным преобразованием Фурье сигнал f(x) может быть описан приемлемой (с проектным допуском) его оценкой  (x) как суперпозицией

(x) как суперпозицией

где pi. - коэффициенты веса;

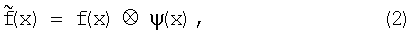

αi(х) - базисные сигналы (элементы) конечных протяженностей (длительностей). Соответственно, выходные реакции ЧФ (ЧФ совместно с чувствительными элементами дискретизатора) на сигнал f(х) и на его оценку  (x) есть

(x) есть

где ⊗ - операция свертки;

ψ(х) - импульсная реакция ЧФ (импульсная функция, импульсная характеристика; функция рассеяния точки).

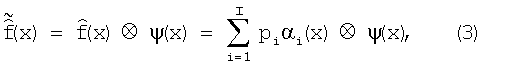

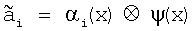

Из (3) следует, что весовые коэффициенты рi являются также коэффициентами разложения сигнала  в обобщенный ряд Фурье по базисным сигналам

в обобщенный ряд Фурье по базисным сигналам  , если последние ортогональны.

, если последние ортогональны.

Поэтому в предлагаемом устройстве для достижения обозначенных целей обратная задача (задача определения оценки входного сигнала по реакции на него ЧФ) решается выполнением следующих действий:

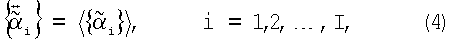

а) ортогонализация [7]

(в общем случае, необходимая) реакций  на базисные сигналы

на базисные сигналы  , где

, где

{·} - обозначение множества элементов;

〈·〉 - операция ортогонализации;

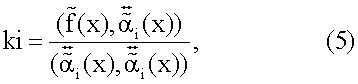

б) определение коэффициентов

разложения реакции  (x) ЧФ на входной сигнал f(x) в ряд Фурье [7] по ортогонализированным базисным сигналам

(x) ЧФ на входной сигнал f(x) в ряд Фурье [7] по ортогонализированным базисным сигналам  , где

, где

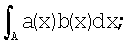

(a(x),b(x))=

А - область определения сигналов а(х) и b(х);

в) определение оценки  входного сигнала в виде (1) при

входного сигнала в виде (1) при

где si - коэффициенты веса (относительные уровни) сигналов  в

в  , определяемые конкретным их видом. При прочих равных условиях предпочтение отдается методам ортогонализации, обеспечивающим значение si=1.

, определяемые конкретным их видом. При прочих равных условиях предпочтение отдается методам ортогонализации, обеспечивающим значение si=1.

Совместное рассмотрение (1) и (3) позволяет интерпретировать РСП как принцип подмены узкополосных сигналов  широкополосными базисными сигналами а(х).

широкополосными базисными сигналами а(х).

Относительно восстановления входного сигнала устройство для обработки сигналов описанным методом является асимпотически (с повышением детальности базисных сигналов а(х)) совершенным. Относительно восстановления оценки (1) входного сигнала такое устройство является совершенным независимо от степени ее приближения к входному сигналу.

Предельное разрешение «сюжетных» элементов сигнала f(x) в оценке  (х) ограничивается принятым набором базисных сигналов αi(х), шагом дискретизации восстановленного сигнала и шумами, снижающими точность определения коэффициентов Фурье ki. Указанный выше проектный допуск на выбор оценки

(х) ограничивается принятым набором базисных сигналов αi(х), шагом дискретизации восстановленного сигнала и шумами, снижающими точность определения коэффициентов Фурье ki. Указанный выше проектный допуск на выбор оценки  (x) входного для устройства сигнала учитывает погрешность определения коэффициентов pi.

(x) входного для устройства сигнала учитывает погрешность определения коэффициентов pi.

Набор базисных сигналов в простейшем случае может состоять, например, из совокупности прямоугольных импульсов при различных их количественных характеристиках; более сложный набор может состоять, например, из функций Хаара [4] или из совокупности, например, прямоугольного импульса, треугольного импульса, импульсов произвольной формы при различных их количественных характеристиках.

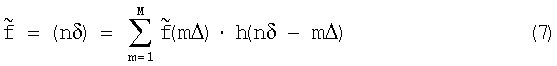

Интерполяция, предшествующая определению коэффициентов Фурье, производится, например, в соответствии с интерполяционной формулой

теоремы [4] об отсчетах. Здесь

n=1, 2, …, N - номера отсчетов сигнала  (х) на выходе интерполятора;

(х) на выходе интерполятора;

N - число отсчетов сигнала  (х) на выходе интерполятора;

(х) на выходе интерполятора;

m - номера отсчетов сигнала  (х) на входе интерполятора;

(х) на входе интерполятора;

М - число отсчетов сигнала  (x) на входе интерполятора;

(x) на входе интерполятора;

Δ - шаг дискретизации сигнала  (x);

(x);

δ=Δ/q - шаг интерполяции;

q≥1 - коэффициент интерполяции;

h(x) - интерполирующее ядро вида h(x)=sinc(πx/Δ); sinc(x)=sin(x)/x.

При ориентации устройства только на значение q=1 функция интерполяции может в нем отсутствовать.

Второй вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введены последовательно соединенные блок подавления помех, предназначенный для уменьшения уровня помех посредством нормализации поступающих на его вход отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций ЧФ, и блок РСП, предназначенный для интерполирования поступающих на его вход из дискретизатора отсчетов, определения (с использованием оценок коэффициентов разложения совокупности интерполированых отсчетов в ряд Фурье по отсчетам ортогонализированных измеренных или запасенных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала) коэффициентов веса базисных элементов во входном сигнале и формирования отсчетов выходного для устройства сигнала посредством суперпозиции базисных сигналов с учетом коэффициентов их веса во входном сигнале (в виде отсчетов оценки входного для устройства сигнала посредством накопительного суммирования произведений отсчетов базисных элементов входного сигнала и коэффициентов веса базисных элементов во входном сигнале), причем вход блока подавления помех соединен с выходом дискретизатора, а выход блока РСП является выходом устройства. Это позволяет в блоке подавления помех уменьшать уровень помех посредством нормализации поступающих с выхода дискретизатора отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций ЧФ, а в блоке РСП выполнять вышеописанным для первого варианта устройства образом формирование отсчетов выходного для устройства сигнала. Уменьшение блоком подавления помех уровня помех дополнительно повышает достижимое в устройстве разрешение элементов входного для него сигнала.

Третий вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введены последовательно соединенные интерполятор, вход которого соединен с выходом дискретизатора, определитель (с использованием оценок коэффициентов разложения совокупности интерполированых отсчетов в ряд Фурье по отсчетам ортогонализированных измеренных или запасенных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала) весов базисных конечной длительности элементов (сигналов) во входном для устройства сигнале и формирователь отсчетов выходного для устройства сигнала в виде отсчетов оценки входного для устройства сигнала посредством суперпозиции базисных сигналов с учетом коэффициентов их веса во входном сигнале (посредством накопительного суммирования произведений отсчетов базисных элементов входного сигнала и коэффициентов веса базисных элементов во входном сигнале), причем выход формирователя отсчетов является выходом устройства. Это позволяет в дискретизаторе получать отсчеты прошедшего через ЧФ входного сигнала, в интерполяторе формировать детальное представление обрабатываемого сигнала вплоть до масштаба мельчайших подлежащих разрешению элементов, в определителе весов базисных сигналов во входном сигнале определять коэффициенты веса базисных элементов во входном для устройства сигнале (с использованием оценок коэффициентов разложения совокупности интерполированых отсчетов в обобщенный ряд Фурье по отсчетам ортогонализированных измеренных или запасенных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала) вычислять коэффициенты веса базисных элементов во входном сигнале, а в формирователе отсчетов выходного для устройства сигнала посредством суперпозиции базисных сигналов с учетом коэффициентов их веса во входном сигнале (посредством накопительного суммирования отсчетов базисных элементов входного сигнала, помноженных на коэффициенты веса базисных элементов во входном сигнале), вычислять отсчеты выходного для устройства сигнала, тем самым с проектным допуском формируя реакцию совершенного устройства на входной сигнал.

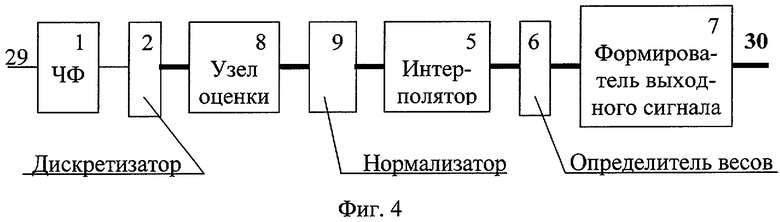

Четвертый вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введены последовательно соединенные узел оценки скорости роста сигнала, вход которого соединен с выходом дискретизатора, нормализатор, интерполятор, определитель (с использованием оценок коэффициентов разложения совокупности интерполированых отсчетов в ряд Фурье по отсчетам ортогонализированных измеренных или запасенных реакций частотного фильтра на базисные конечной длительности элементы входного для устройства сигнала) весов базисных конечной длительности элементов (сигналов) во входном для устройства сигнале и формирователь отсчетов выходного для устройства сигнала посредством суперпозиции базисных сигналов с учетом коэффициентов их веса во входном сигнале (в виде отсчетов оценки входного для устройства сигнала посредством накопительного суммирования произведений отсчетов базисных элементов входного сигнала и коэффициентов веса базисных элементов во входном сигнале), причем выход формирователя отсчетов является выходом устройства. Это позволяет в дискретизаторе получать отсчеты прошедшего через ЧФ входного сигнала, в узле оценки скорости роста и в узле нормализации проверять соответствие импульсных элементов возможным выходным реакциям ЧФ, нормализовывать недопустимо искаженные импульсные элементы и тем самым обеспечивать условия для более эффективной работы интерполятора, определителя весов базисных элементов (сигналов) во входном сигнале и формирователя отсчетов выходного сигнала, которые вышеописанным для третьего варианта устройства образом определяют веса базисных элементов во входном сигнале и вычисляют отсчеты выходного для устройства сигнала, тем самым формируя (с проектным допуском) реакцию совершенного устройства на входной сигнал в условиях пониженного уровня помех.

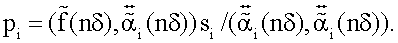

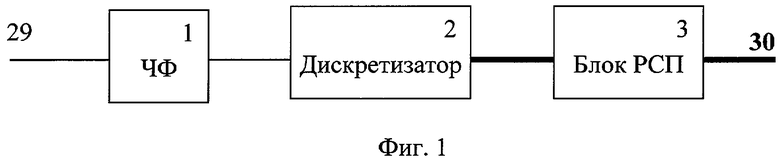

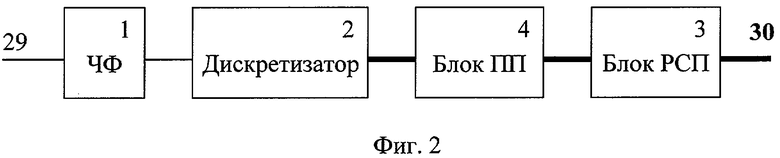

На фиг.1, фиг.2, фиг.3, фиг.4 представлены блок-схемы предлагаемого устройства для обработки сигналов по пунктам 1, 2, 3, 4 формулы изобретения.

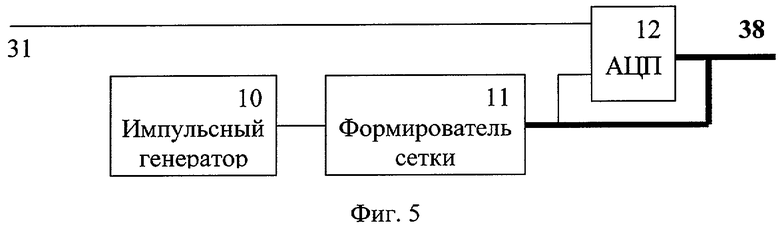

На фиг.5 представлен пример блок-схемы дискретизатора.

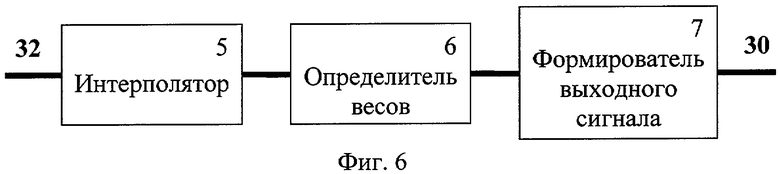

На фиг.6 представлен пример блок-схемы блока РСП.

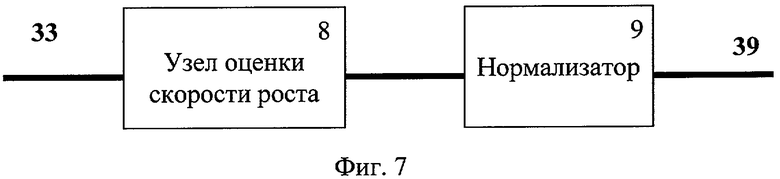

На фиг.7 представлен пример блок-схемы блока подавления помех (блока ПП).

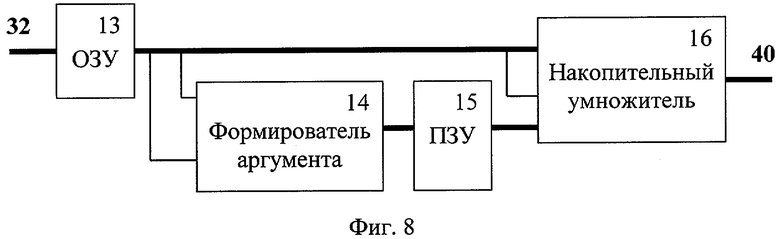

На фиг.8 представлен пример блок-схемы интерполятора.

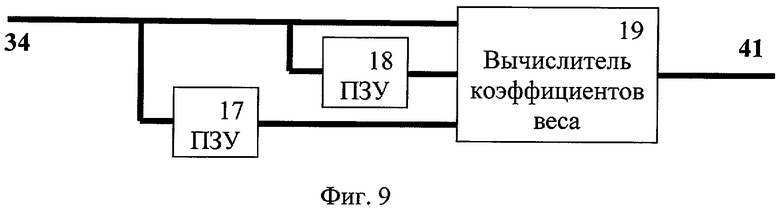

На фиг.9 представлен пример блок-схемы определителя коэффициентов веса базисных элементов во входном сигнале (определителя весов).

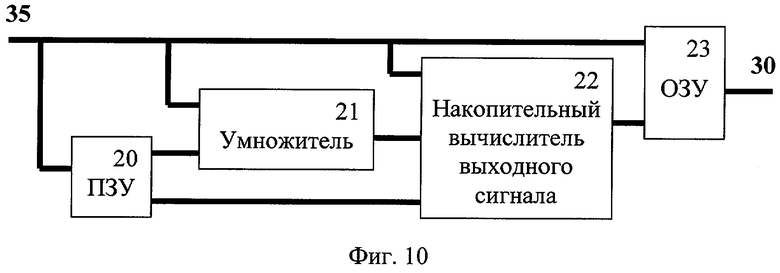

На фиг.10 представлен пример блок-схемы формирователя отсчетов выходного сигнала (формирователя выходного сигнала).

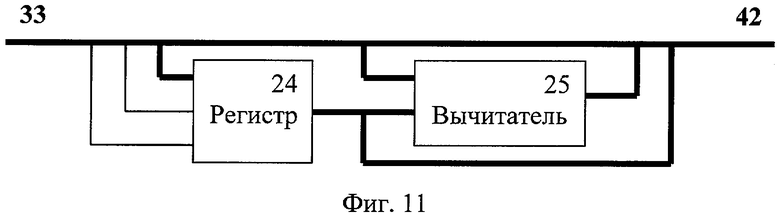

На фиг.11 представлен пример блок-схемы узла оценки скорости роста (узла оценки).

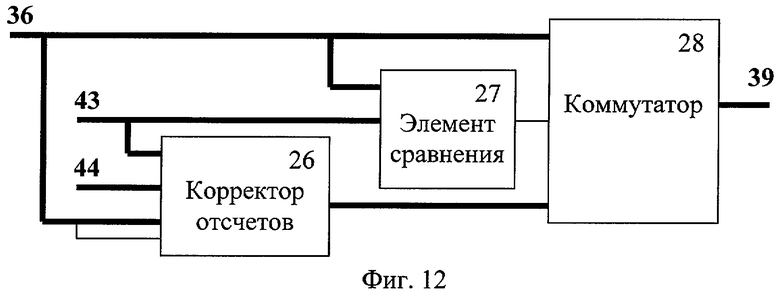

На фиг.12 представлен пример блок-схемы нормализатора.

Первый вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 РСП.

Второй вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 РСП, блок 4 ПП.

Третий вариант устройства содержит ЧФ 1, дискретизатор 2, интерполятор 5, определитель 6 весов, формирователь 7 выходного сигнала.

Четвертый вариант устройства содержит ЧФ 1, дискретизатор 2, интерполятор 5, определитель 6 весов, формирователь 7 выходного сигнала, узел 8 оценки, нормализатор 9.

ЧФ1 представляет собой, например (в простейшем случае, при обработке временн  х входных сигналов), резистивно-емкостной фильтр низких частот.

х входных сигналов), резистивно-емкостной фильтр низких частот.

Дискретизатор 2 содержит, например, импульсный генератор 10, формирователь 11 сетки частот, аналого-цифровой преобразователь (АЦП) 12.

Блок 3 РСП содержит, например, интерполятор 5, определитель 6 весов, формирователь 7 выходного сигнала (при коэффициенте интерполяции равном единице интерполятор 5 выполняет тождественное преобразование и может отсутствовать).

Блок 4 ПП содержит, например, узел 8 оценки, нормализатор 9.

Интерполятор 5 содержит, например, оперативное запоминающее устройство (ОЗУ) 13, формирователь 14 аргумента, постоянное запоминающее устройство (ПЗУ) 15, накопительный умножитель 16.

Определитель 6 весов содержит, например, ПЗУ 17, ПЗУ 18, вычислитель 19 коэффициентов веса.

Формирователь 7 выходного сигнала содержит, например, ПЗУ 20, умножитель 21, накопительный вычислитель 22 отсчетов выходного сигнала, ОЗУ 23.

Узел 8 оценки содержит, например, регистр 24, вычитатель 25.

Нормализатор 9 содержит, например, корректор 26 отсчетов, элемент 27 сравнения, коммутатор 28.

АЦП 12 может быть выполнен, например, в виде микросхемы AD9461 [8].

ПЗУ 15, ПЗУ 17, ПЗУ 18, ПЗУ 20 могут быть выполнены на основе, например, микросхем М558РР4 [9].

ОЗУ 13, ОЗУ 23 могут быть выполнены на основе, например, микросхем 537РУ16 [9].

Входы устройства:

29 - информационный вход.

Выходы устройства:

30 - информационный выход.

Входы и выходы составных частей, являющиеся входами и выходами составной части более высокого уровня, имеют номера входов и выходов составной части более высокого уровня.

Остальные входы (дискретизатора 2, блока 3 РСП, блока 4 подавления помех, определителя 6 параметров элементов входного сигнала, формирователя 7 выходного сигнала, нормализатора 9):

31 - сигнальный вход дискретизатора 2,

32 - вход блока 3 РСП,

33 - вход блока 4 ПП,

34 - вход определителя 6 весов,

35 - вход формирователя 7 выходного сигнала,

36 - вход нормализатора 9.

Остальные выходы (ЧФ 1, дискретизатора 2, блока 4 ПП, интерполятора 5, определителя 6 весов, узла 8 оценки):

37 - выход ЧФ 1,

38 - выход дискретизатора 2,

39 - выход блока 4 ПП,

40 - выход интерполятора 5,

41 - выход определителя 6 весов,

42 - выход узла 8 оценки.

Внутренние входные шины - источники констант, задаваемых подключением отдельных линий к уровням логических «0» или «1»:

43 - код максимальной скорости роста,

44 - код коэффициента запаса по скорости роста,

На фиг.1-12 тонкими линиями представлены одиночные связи для передачи одиночных сигналов, толстыми линиями - групповые связи для передачи групп сигналов.

Для упрощения описания далее рассматривается обработка одномерного сигнала.

В исходном состоянии всех вариантов устройства на их информационном входе 29 сигнал отсутствует (действует сигнал, равный нулю), устройство обрабатывает нулевой сигнал, формируя нулевой сигнал во всех информационных сечениях и на своем выходе 30, то есть устройство находится в состоянии динамической готовности к обработке сигнала.

Первый вариант устройства для обработки сигналов работает следующим образом. С поступлением сигнала на вход 29 устройства ЧФ 1 преобразовывает его соответственно своей импульсной реакции. С выхода ЧФ 1 сигнал с ограниченным спектром поступает на вход дискретизатора 2, который подвергает его дискретизации с шагом А и квантованию, например, равномерным двоичным 16-разрядным кодом. С выхода дискретизатора 2 двоичные коды отсчетов (отсчеты) сигнала поступают на вход блока 3 РСП, который интерполирует с коэффициентом q полученные отсчеты сигнала, по интерполированным отсчетам и отсчетам ортогонализованных реакций ЧФ 1 на базисные элементы определяет коэффициенты веса базисных элементов во входном для устройства сигнале и по этим коэффициентам формирует отсчеты выходного для устройства сигнала, являющегося оценкой входного для устройства сигнала, посредством накопительного суммирования отсчетов базисных элементов, помноженных на эти коэффициенты, и тем самым выполняет совершенное восстановление сигнала вплоть до предельно разрешаемых и с предельно малой амплитудой его элементов. С выхода блока 3 РСП сформированный таким образом сигнал поступает на выход 30 устройства.

Второй вариант устройства для обработки сигналов работает следующим образом.

С поступлением сигнала на вход 29 устройства ЧФ 1 и дискретизатор 2 вышеописанным для первого варианта устройства образом формируют на своем выходе коды отсчетов сигнала, которые поступают на вход блока 4 подавления помех. Блок 4 подавления помех уменьшает уровень помех посредством модификации поступающих с выхода дискретизатора 2 отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций ЧФ 1, и выдает полученные отсчеты в блок 3 РСП, который вышеописанным для первого варианта устройства образом выполняет совершенное восстановление сигнала и выдает его на выход 30 устройства.

Третий вариант устройства для обработки сигналов работает следующим образом.

С поступлением сигнала на вход 29 устройства ЧФ 1 и дискретизатор 2 вышеописанным для первого варианта устройства образом формируют на своем выходе коды отсчетов сигнала, которые поступают на вход интерполятора 5. Интерполятор 5 производит интерполяцию этих отсчетов с коэффициентом q, то есть формирует детальное представление обрабатываемого сигнала вплоть до масштаба мельчайших подлежащих разрешению элементов и выдает интерполированные отсчеты в определитель 6. Определитель 6 по интерполированным отсчетам вычисляет коэффициенты веса базисных элементов во входном сигнале (с использованием определяемых в определителе 6 коэффициентов разложения интерполированных отсчетов в обобщенный ряд Фурье по ортогонализированным реакциям частотного фильтра на базисные элементы) и выдает их в формирователь 7 отсчетов выходного сигнала, который по этим коэффициентам формирует отсчеты выходного для устройства сигнала, являющегося оценкой входного для устройства сигнала, посредством накопительного суммирования отсчетов базисных элементов, помноженных на коэффициенты веса. С выхода формирователя 7 отсчеты выходного сигнала поступают на выход 30 устройства.

Четвертый вариант устройства работает следующим образом.

С поступлением сигнала на вход 29 устройства ЧФ 1 и дискретизатор 2 вышеописанным для первого варианта устройства образом формируют на своем выходе коды отсчетов сигнала, которые поступают на вход узла 8 оценки скорости роста. Узел 8 определяет скорость роста импульсных элементов сигнала и выдает ее значение в нормализатор 9, который определяет соответствие этой скорости возможным в выходных реакциях ЧФ 1 и приводит к норме недопустимо искаженные импульсные элементы, оставляя остальные без изменения. Нормализованные таким образом отсчеты поступают в интерполятор 5, который совместно с определителем 6 параметров элементов сигнала и формирователем 7 вышеописанным для третьего варианта устройства образом формируют отсчеты выходного для устройства сигнала. С выхода формирователя 7 отсчеты выходного сигнала поступают на выход 30 устройства.

Дискретизатор 2 работает следующим образом.

Генератор 10 вырабатывает импульсы постоянной частоты, поступающие с его выхода на вход формирователя 11 сетки частот. Формирователь 11 формирует из импульсов генератора 10 необходимые для работы устройства тактовые импульсы, поступающие в выходную шину 38 и на синхровход АЦП 12. АЦП 12 по переднему фронту каждого тактового импульса, поступающего на его синхровход, производит выборку (отсчет) значения сигнала, поступающего со входа 31 дискретизатора 2 на его сигнальный вход, и преобразовывает это значение в линейный двоичный, например, 16-разрядный код, поступающий в виде данных с выхода АЦП 12 в выходную шину 38 дискретизатора 2. По шине 38 тактовые импульсы поступают на вход блока 3 РСП (интерполятора 5, определителя 6 весов базисных сигналов, формирователя 7 выходного сигнала) и блока 4 подавления помех (узла 8 оценки скорости роста, нормализатора 9). Необходимые тактовые импульсы транслируются этими блоками и всеми их составными частями и благодаря этому присутствуют во всех информационных шинах устройства на всех уровнях (чтобы не перегружать рисунки, на фиг.1-12 трансляция тактовых импульсов не отражена).

Блок 3 РСП, состоящий в качестве примера из интерполятора 5, определителя 6 весов и формирователя 7, работает вышеописанным для этих узлов в третьем варианте устройства образом.

Блок 4 подавления помех, состоящий в качестве примера из узла 8 оценки скорости роста и нормализатора 9, работает вышеописанным для этих узлов в четвертом варианте устройства образом.

Интерполятор 5 работает в соответствии с выражением (7) следующим образом.

Со входа 32 отсчеты прошедшего через ЧФ 1 сигнала, произведенные дискретизатором 2, записываются в ОЗУ 13, после чего циклически считываются из него (один цикл на каждый интерполируемый отсчет) и поступают на (информационный) вход накопительного умножителя 16. При этом из входной шины 32 на первый и второй входы формирователя 14 аргумента приходят тактовые импульсы-инкременты, соответствующие  (mΔ) и интерполируемым отсчетам

(mΔ) и интерполируемым отсчетам  (nδ). По этим импульсам формирователь 14 формирует коды n-mq аргументов отсчетов ядра h((n-mq)δ), поступающие на вход ПЗУ 15 в качестве адресов предварительно запасенных в нем этих отсчетов ядра, вычисленных с шагом интерполяции. Соответствующие этим адресам отсчеты h((n-mq)δ) интерполирующего ядра из ПЗУ 15 поступают на второй вход накопительного умножителя 16, который для каждого из N интерполируемых отсчетов производит суммирование М произведений

(nδ). По этим импульсам формирователь 14 формирует коды n-mq аргументов отсчетов ядра h((n-mq)δ), поступающие на вход ПЗУ 15 в качестве адресов предварительно запасенных в нем этих отсчетов ядра, вычисленных с шагом интерполяции. Соответствующие этим адресам отсчеты h((n-mq)δ) интерполирующего ядра из ПЗУ 15 поступают на второй вход накопительного умножителя 16, который для каждого из N интерполируемых отсчетов производит суммирование М произведений  (mΔ)h((n-mq)δ) с записью (по тактовым импульсам, поступающим на третий вход накопительного умножителя 16 по линии в составе выходной шины ОЗУ 13) каждой такой накопленной суммы в запоминающее устройство в составе накопительного умножителя 16 в качестве очередного интерполированного отсчета. С выхода накопительного умножителя 16 интерполированные отсчеты выдаются (по тактовым импульсам на линии в составе шины выхода 40) на выход 40 интерполятора 5.

(mΔ)h((n-mq)δ) с записью (по тактовым импульсам, поступающим на третий вход накопительного умножителя 16 по линии в составе выходной шины ОЗУ 13) каждой такой накопленной суммы в запоминающее устройство в составе накопительного умножителя 16 в качестве очередного интерполированного отсчета. С выхода накопительного умножителя 16 интерполированные отсчеты выдаются (по тактовым импульсам на линии в составе шины выхода 40) на выход 40 интерполятора 5.

Определитель 6 весов работает следующим образом.

С входа 34 определителя 6 весов базисных элементов отсчеты  (nδ) реакции на входной для устройства сигнал поступают на вход вычислителя 19 коэффициентов веса. Одновременно на второй вход вычислителя 19 с выхода ПЗУ 18 и на третий вход вычислителя 19 с выхода ПЗУ 17 поступают отсчеты (коды отсчетов) предварительно запасенных в этих ПЗУ отсчетов соответственно ортогонализованных реакций

(nδ) реакции на входной для устройства сигнал поступают на вход вычислителя 19 коэффициентов веса. Одновременно на второй вход вычислителя 19 с выхода ПЗУ 18 и на третий вход вычислителя 19 с выхода ПЗУ 17 поступают отсчеты (коды отсчетов) предварительно запасенных в этих ПЗУ отсчетов соответственно ортогонализованных реакций  , вычисленных с шагом интерполяции, и величин si/(

, вычисленных с шагом интерполяции, и величин si/( ,

, соответственно выражениям (4, 5, 6), например, для si=1. По линиям в составе шины 34 на входы ПЗУ 17 и ПЗУ 18 поступает сигнал режима работы этих ПЗУ, задающий режим чтения. Выдача отсчетов из ПЗУ 17 и ПЗУ 18 производится в соответствии с кодами адресов, которые состоят из номера i реакции и номера отсчета этой реакции и формируются в составе ПЗУ 17, ПЗУ 18 по тактовым инкрементным импульсам номеров i реакций и номеров их отсчетов с установкой кодов адресов в «нулевое» состояние по импульсам сброса на входе этих ПЗУ. Последовательность поступления указанных кодов на первый, второй и третий входы вычислителя 19 обеспечивает вычисление в нем значений (

соответственно выражениям (4, 5, 6), например, для si=1. По линиям в составе шины 34 на входы ПЗУ 17 и ПЗУ 18 поступает сигнал режима работы этих ПЗУ, задающий режим чтения. Выдача отсчетов из ПЗУ 17 и ПЗУ 18 производится в соответствии с кодами адресов, которые состоят из номера i реакции и номера отсчета этой реакции и формируются в составе ПЗУ 17, ПЗУ 18 по тактовым инкрементным импульсам номеров i реакций и номеров их отсчетов с установкой кодов адресов в «нулевое» состояние по импульсам сброса на входе этих ПЗУ. Последовательность поступления указанных кодов на первый, второй и третий входы вычислителя 19 обеспечивает вычисление в нем значений ( (nδ),

(nδ), ) и оценок коэффициентов рi веса базисных сигналов в виде

) и оценок коэффициентов рi веса базисных сигналов в виде  Вычисленные оценки коэффициентов веса по синхроимпульсам из вычислителя 19 выдаются на выход 41 определителя 6 весов.

Вычисленные оценки коэффициентов веса по синхроимпульсам из вычислителя 19 выдаются на выход 41 определителя 6 весов.

Формирователь 7 отсчетов выходного сигнала работает следующим образом (в ПЗУ 20 предварительно запасены отсчеты αi(nδ) базисных элементов, заданные с шагом интерполяции).

С выхода 41 определителя 6 весов коэффициенты pi поступают на вход 35 формирователя 7 отсчетов выходного сигнала и далее на вход умножителя 21. На вход ПЗУ 20 по линиям в составе входной шины 35 поступают сигнал сброса (установки в нулевое состояние) адреса его ячеек и инкрементные (плюс 1) сигналы для формирования номера i базисного сигнала αi(nδ) и номера n отсчета этого сигнала. Совместно эти номера составляют адреса ячеек ПЗУ 20. Отсчеты αi(nδ) базисных сигналов, соответствующие этим адресам, с выхода ПЗУ 20 последовательно поступают на второй вход умножителя 21. Со второго выхода ПЗУ 20 на вход накопительного вычислителя 22 поступают коды номеров отсчетов базисных сигналов. Умножитель 21 вычисляет отсчеты произведения piαi(nδ) и выдает их на второй вход накопительного вычислителя 22. На третий вход накопительного вычислителя 22 по линиям в составе входной шины 35 поступают сигнал сброса (установки в нулевое состояние) адреса операндов, инкрементные сигналы для формирования адреса n выходных отсчетов, сигналы накопительного суммирования, сигнал (признак) выдачи из вычислителя 22 отсчетов выходного сигнала. Накопительный вычислитель 22 формирует адрес i+n накопительно модифицируемого отсчета и к содержимому своей памяти по этому адресу прибавляет произведение piαi(nδ), поступившее на его второй вход из умножителя 22. После завершения накопительного формирования таким образом (в соответствии с (1, 6)) каждого отсчета выходного сигнала этот отсчет в сопровождении его адреса с выхода вычислителя 22 выдается на вход ОЗУ 23 и записывается в него. По сигналу сброса адреса операндов, признаку выдачи из ОЗУ 23 отсчетов выходного сигнала, инкрементным сигналам формирования адреса n выходных отсчетов, поступающим на второй вход ОЗУ 23 по линиям в составе входной шины 35, из ОЗУ 23 отсчеты выходного сигнала выдаются на выход 30 формирователя 7, являющийся выходом устройства.

Узел 8 оценки скорости роста работает следующим образом.

С выхода дискретизатора 2 текущие отсчеты сигнала поступают на вход 33 узла 8 оценки скорости роста и далее на информационный вход регистра 24, на вход уменьшаемого вычитателя 25 и в выходную шину 42. Тактовыми импульсами, приходящими из шины 33 на синхровходы регистра 24, отсчеты сигнала заносятся в этот регистр 24 и с его выхода поступают на вход вычитаемого вычитателя 25 и в выходную шину 42. При этом (предыдущие) отсчеты сигнала в регистр 24 заносятся первым тактовым импульсом (приходящим на первый синхровход) по переднему фронту, а остальными (приходящими на второй синхровход) - по заднему фронту. Таким образом, вычитатель 25 вычисляет разности между текущим и предшествующим отсчетами и выдает полученные модули разностей, являющиеся текущими значениями скорости роста сигнала, и знаковый разряд разности на выход 42 узла 8 оценки скорости роста; при этом для первого отсчета в качестве предшествующего используется он сам.

Нормализатор 9 работает следующим образом.

Значения скорости роста сигнала, приходящие с выхода 42 узла 8 оценки скорости роста на вход 36 нормализатора 9, поступают на вход элемента 27 сравнения. С того же входа 36 на вход коммутатора 28 поступают текущие отсчеты сигнала. На второй вход элемента 27 сравнения и на вход корректора 26 со внутреннего входа 43 узла 9 нормализации приходит код максимально возможной скорости роста сигнала, обусловленной фильтром ЧФ 1. Результат сравнения скорости роста сигнала с максимально возможной поступает с выхода элемента 27 сравнения на второй вход коммутатора 28. На второй и третий входы корректора 26 со входа 36 поступают соответственно код предыдущего отсчета и знак скорости роста. Корректор 26 отсчетов вычисляет произведение максимальной скорости роста и коэффициента запаса (меньшего единицы), код которого со внутреннего входа 44 нормализатора 9 приходит на четвертый вход корректора 26, и с учетом знака скорости роста прибавляет его к предыдущему отсчету. Полученный таким образом скорректированный текущий отсчет поступает с выхода корректора 26 на третий вход коммутатора 28. Коммутатор 28 при значении управляющего сигнала с выхода элемента 27 сравнения, соответствующем допустимой скорости роста, выдает на выход 39 нормализатора 9 отсчет сигнала со входа 36 в неизменном виде, в противном случае - скорректированное значение отсчета, соответствующее допустимой скорости роста сигнала, поступающее на его третий вход, и тем самым нормализует сбойные отсчеты сигнала.

Работоспособность каждого варианта устройства обеспечивается при адекватности запасаемых в ПЗУ 15, ПЗУ 17, ПЗУ 18, ПЗУ 20 данных, а также констант на внутренних шинах 43, 44.

Сущность предлагаемого изобретения не меняется при перераспределении функций между составными частями устройства, при изменениях его состава или функций, не меняющих принципы решения обратной задачи и подавления помех, например, при включении в его состав дополнительных средств для рационализации формы представления обрабатываемых данных, для ортогонализации реакций на базисные сигналы, при уточнении режимов обработки данных (например, в реальном или нереальном времени).

Предлагаемое устройство для обработки сигналов применимо в линейных системах с известной импульсной реакцией и необходимостью решения обратной задачи. Наибольший эффект предлагаемое устройство для обработки сигналов дает при его применении, например, в системах, проблемно реализуемых по массе и энергопотреблению (оптико-электронные системы, в том числе, телевизионные), в системах с дорогостоящими ресурсами коллективного пользования (системы связи, особенно широкополосные).

Коэффициент повышения разрешения и скоростей передачи данных без расширения физической полосы частот может достигать значений в несколько единиц. Возможно также уменьшение массы, габаритов, энергопотребления устройств при сохранении имеющихся разрешения и скоростей передачи данных.

Литература

1. Василенко Г.И. Теория восстановления сигналов. О редукции к идеальному прибору в физике и технике. - М.: Сов. радио, 1979.

2. Михайлов Б.А. К выбору частоты дискретизации, достаточной для восстановления формы непрерывного сигнала. - Электронная техника. Сер. 10. Микроэлектронные устройства, вып.4 (46), 1984.

3. Michael L. Hilton, Bjorn D. Jawerth, Ayan Sengupta. Compressing Still and Moving Images with Wavelets. - Multimedia Systems, Vol.2, No. 3, April 18,1994, p.7-11.

4. Обработка изображений и цифровая фильтрация. Под редакцией Т. Хуанга. - М.: Мир, 1979.

5. Патент RU №2141737.

6. Патент RU №2195014.

7. Корн Г., Корн Т. Справочник по математике для научных работников и инженеров. - М.: Наука, 1974.

8. http://www.analog.com.

9. Цифровые и аналоговые интегральные микросхемы. Каталог, часть 1. Технические характеристики. - М.: Издательство ФГУП ЦКБ «Дейтон», 2002.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2195014C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ПАНХРОМАТИЧЕСКИХ ИЗОБРАЖЕНИЙ (ВАРИАНТЫ) | 2011 |

|

RU2476926C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| Устройство для сжатия информации | 1982 |

|

SU1056244A1 |

| Цифровой измеритель частоты | 1983 |

|

SU1091086A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Панорамный измеритель спектра | 1982 |

|

SU1187092A2 |

| Устройство для измерения центральнойчАСТОТы СпЕКТРА СигНАлА | 1979 |

|

SU813290A1 |

Изобретение относится к области обработки сигналов для повышения их соответствия входным для устройства сигналам. Техническим результатом изобретения является повышение разрешения и чувствительности к элементам сигнала, повышение быстродействия и упрощение устройства для обработки сигналов. Технический результат достигается благодаря тому, что устройство содержит последовательно соединенные частотный фильтр, дискретизатор и блок редукции к совершенному прибору (РСП), предназначенный для интерполяции поступающих на его вход отсчетов, определения веса базисных конечной длительности сигналов во входном сигнале на основе разложения интерполированных отсчетов в ряд Фурье по ортогонализированным реакциям частотного фильтра на базисные сигналы и для формирования выходного сигнала как суперпозиции базисных сигналов с учетом их веса во входном сигнале, причем варианты устройства предусматривают включение между дискретизатором и блоком РСП блока подавления помех или последовательно соединенных узла оценки скорости роста сигнала и узла нормализации. 4 н.п. ф-лы, 12 ил.

1. Устройство для обработки сигналов, содержащее последовательно соединенные частотный фильтр, вход которого является входом устройства, и дискретизатор, отличающееся тем, что в него дополнительно введен блок редукции к совершенному прибору, предназначенный для интерполяции поступающих на его вход отсчетов, определения веса базисных конечной длительности сигналов во входном сигнале на основе разложения интерполированных отсчетов в ряд Фурье по ортогонализированным реакциям частотного фильтра на базисные сигналы и для формирования выходного сигнала как суперпозиции базисных сигналов с учетом их веса во входном сигнале, причем вход блока редукции к совершенному прибору соединен с выходом дискретизатора, а выход является выходом устройства.

2. Устройство для обработки сигналов, содержащее последовательно соединенные частотный фильтр, вход которого является входом устройства, и дискретизатор, отличающееся тем, что в него дополнительно введены последовательно соединенные блок подавления помех, предназначенный для уменьшения уровня помех посредством нормализации поступающих на его вход отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций частотного фильтра, и блок редукции к совершенному прибору, предназначенный для интерполяции поступающих на его вход отсчетов, определения веса базисных конечной длительности сигналов во входном сигнале на основе разложения интерполированных отсчетов в ряд Фурье по ортогонализированным реакциям частотного фильтра на базисные сигналы и для формирования выходного сигнала как суперпозиции базисных сигналов с учетом их веса во входном сигнале, причем вход блока подавления помех соединен с выходом дискретизатора, а выход блока редукции к совершенному прибору является выходом устройства.

3. Устройство для обработки сигналов, содержащее последовательно соединенные частотный фильтр, вход которого является входом устройства, и дискретизатор, отличающееся тем, что в него дополнительно введены последовательно соединенные интерполятор, вход которого соединен с выходом дискретизатора, определитель весов базисных конечной длительности сигналов во входном сигнале и формирователь выходного сигнала как суперпозиции базисных сигналов с учетом их веса во входном сигнале, выход которого является выходом устройства.

4. Устройство для обработки сигналов, содержащее последовательно соединенные частотный фильтр, вход которого является входом устройства, и дискретизатор, отличающееся тем, что в него дополнительно введены последовательно соединенные узел оценки скорости роста сигнала, вход которого соединен с выходом дискретизатора, узел нормализации, интерполятор, определитель весов базисных конечной длительности сигналов во входном сигнале и формирователь выходного сигнала как суперпозиции базисных сигналов с учетом их веса во входном сигнале, выход которого является выходом устройства.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2195014C2 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| US 20080151987 A1, 26.06.2008 | |||

| US 4218704, 19.08.1980 | |||

| ЕР 1720337 А1, 08.11.2006. | |||

Авторы

Даты

2010-03-27—Публикация

2008-08-28—Подача