2.Линейный интерполятор по п.1, отличающийся тем, что блок вычисления интервала интерполяции содержит последовательно соединенные первый элемент И, пятый и шестой регистры сдвига, узел выделения заднего фронта импульса, выход которого соединен с R-входом R5 -триггера, а также является синхровыходом блока вычисления интервала интерполяции,5 ВХОД R5 -триггера подключен к выходу первого элемента И, выход R5 -триггера соединен

с входом узла выделения переднего фронта импульса и вторым входом второго элемента И, а также является выходом признака интерполяции блока вычисления интервала интерполяции, выход второго элемейта И подключен к счетному входу двоичного счетчика, а выход узла вьщеления переднего фронта импульса соединен с входом установки нуля двоичного счетчика и является первым синхровыходом блока вычисления интервала интерполяции информационным выходом которого является выход двоичного счетчика, первые входы первого и второго элемен-, тов И, а также синхровходы пятого и шестого регистров сдвига объединены и являются синхровходом блока вычисления интервала интерполяции, управлякяцим входом которого является второй вход первого элемента И.

3.Линейньй интерполятор по п. 1, отличающийся тем, что блок вычисления приращения содержит второй и третий регистры хранения, вычитатель и делитель, информационны входы регистров объединень и являются первым информационным входом блок вычисления приращения, выходы второго итретьего регистров соединены соответственно с входами вычитания и сло

жения вычитателя, выход которого подключен к информационному входу делителя, первый информационный вход и выход делителя являются соответственно вторьы информационным входом и выходом блока вычисления приращения, первый и второй синхровходы блока вычисления приращения соединены соответственно с синхровходом второго регистра хранения, синхровходами третьего регистра хранения и делителя.

4. Линейный интерполятор по п.1, отличающийся тем, что блок формирования массива слагаемых содержит регистр сдпиг.1 частного и элемент задержки, установочные входы всех ячеек регистра сдвига частного объединены и являются информационным входом .блока формирования массива слагаемых, выходом которого является выход регистра сдвига частного, управляющие входы ключей объединены и являются вторым синхровходом блока формирования массива слагаемых, первым синхровходом которого является вход элемента задержки, шины импульсов сдвига регистра сдвига признаков записи и регистра сдвига частного объединены и являются третьим синхровходом блока формирования массива слагаемьк, выход элемента задержки соединен с иной записи регистра сдвига признаков записи, вход последовательного приема которого соединен с шиной огического нуля, установочные входы регистра сдвига признаков записи подключены к шине логической единицы, выход «чеек регистра сдвига признаков записи соединены с информационными входами ключей, выходы которых оединены с входами записи соответствукидих ячеек регистра сдвига частного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1986 |

|

SU1401481A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Линейный интерполятор | 1988 |

|

SU1522157A1 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

| Сплайн-интерполятор | 1989 |

|

SU1686461A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

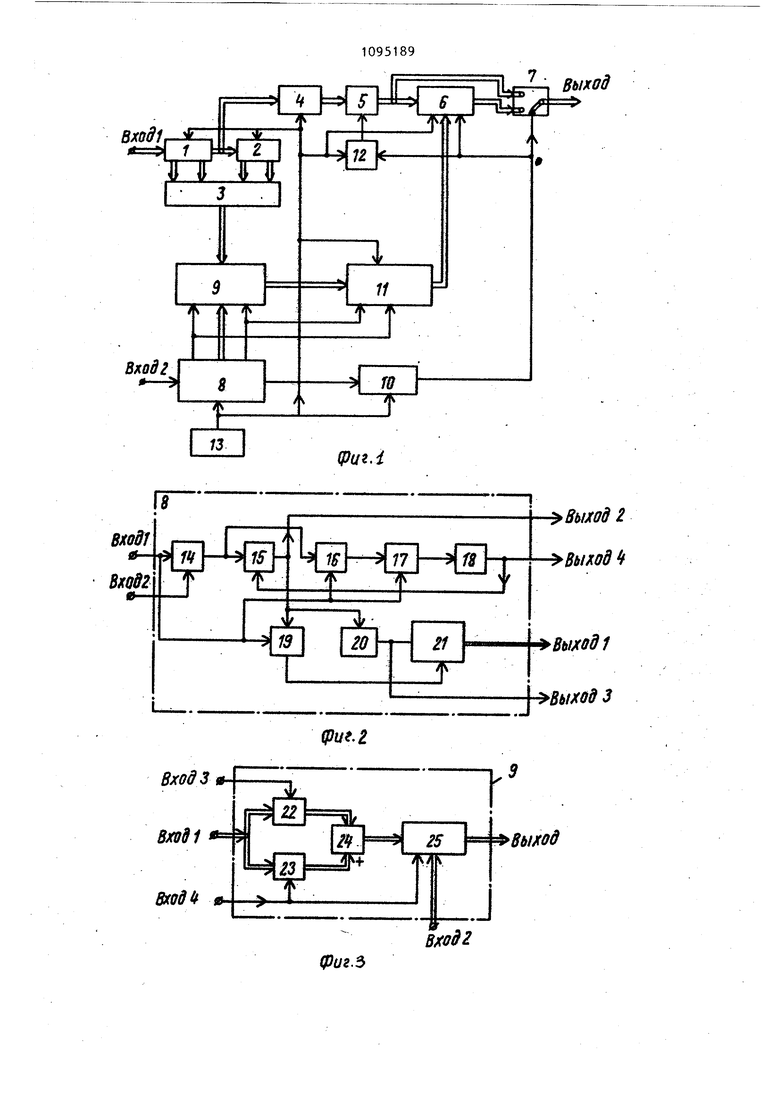

1. ЦИФРОВОЙ АДАПТИВНЫЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР, содержащий генератор синхроимпульсов и последовательно включенные регистр хранения и накапливающий сумматор, о т л и чающий.с я тем, что, с целью обеспечения линейного интерполирования процессов при наличии шумов в реальном масштабе времени, в него введены четыре регистра сдвига, многовходовьй сумматор, блок вычисления интервала интерполяции, блок вычисления приращения, блок формирования массива слагаемых, ключ и коммутатор, причем выходы многоразрядных ячеек первого и второго регистров сдвига соединены с входами сумматора, выход первого регистра сдвига соединен с информационными входами второго и третьего регистров сдвига, выход многовходового сумматора подключен к первому информационному входу блока вычисления приращения, выход rekeратора синхроимпульсов соединен с синхровходами блока вычисления интервала интерполяции, первого, второго, третьего и четвертого регистров сдвига, КЛЮЧ0, накапливающего сумматора ВГРО| Ш д , :--ft ЬйБ4Йу. и третьим синхровходом блока формирования массива слагаемых, управляющий вход блока вычисления интервала интерполйции является вторым входом интерполятора, информационный, первый и второй синхровыходы блока вычисления интервала интерполяции соединены соответственно с вторым информационным, первлм и вторым синхровходами блока вычисления приращения, .выход признака интерполяции блока вычисления интервала интерполяции соединен с информационным входом четвертого регистра сдвига, информационный вход блока формирования массива слаi гаемых соединен с выходом блока вычисления приращения, первый и второй (Л синхровходы блока формирования массива слагаемых соединены соответственно с первым и вторым синхровыход-ами блока вычисления интервала интерполяции, выход третьего регистра сдвига соединен с входом записи регистра хранения, выход которого подключен к первым информационным со входам накапливающего сумматора и коммутатора, выход четвертого регист СП ра сдвига соединен с входами управления ключа, накапливающего суммато00 ра и коммутатора, выход блока формисо рования массива слагаемых подключен к второму информационному входу накапливающего сумматора, выход ключа соединен с входом записи регистра хранения, выход накапливаюп1его сумматора подключен к второму информационному входу коммутатора, выход коммутатора является выходом линейного интерполятор.ч, а информационньй вход первого регистра сдвига является первым.входом интерполятора.

Изобретение относится к средствам обработки экспериментальной информации и может быть использовано при работе в реальном масштабе времени для линейного интерполирования обра

батываемых процессов при наличии аддитивных йумов и импульсных помех. В практике обработки экспериментальной информации, представленной в виде случайных процессов, часто

возникает ситуация, когда обрабатываемь й процесс у (t) содержит наряду с полезным сигналом (процессом) 5 (t) компоненту аддитивных шумов Пщ (t) и компоненту импульсных помех n(-t)

МП /

т р

1)а)5а)+пц,(ч)-ьп1,„па). (о

Такие условия характерны при передаче информации по каналам с шумами и импульсными помехами, в частности, в радиолокации, радиосвязи, телеметрии, а также для цифровой обработки информации при наличии сбоев в аппаратуре, при восстановл ении фонограмм

Исключение влияния импульсных помех при обработке исходного процесса достигается интерполяцией процесса .на интервалах существования импульрных помех..

Известны интерполяторы, производящие линейную, ленейно-круговую и нелинейную интерполяцию детерминированных процессов lj

Однако нелинейные интерполяторы сложны в реализации и не позволяют обрабатывать.случайные процессы в реальном масштабе времени.

Линейный интерполятор 2J , принятьй за прототип, содержит генератор импульсов, реверсивный счетчик, регистр хранения, выход которого через набор схем совпадения соединен с входом накапливающего сумматора. Вход вычитания счетчика соединен с выходом генератора импульсов. Вход начальной установки счетчика является первым входом интерполятора - на этот вход подается число в двоичном коде, соответствующее длительности интервала интерполяции. Вторьм входом интерполятора являются установочные входы регистра хранения, на которые подается число, соответствующее тангенсу угла наклона (к оси времени) интерполируемой прямой. Исходные данные вводятся в реверсивный счетчик и регистр хранения до включения генератора импульсов. При включении генератора импульсов последовательность импульсов поступает на .вход вычитания реверсивного счетчика, а также на второй вход набора схем совпадения. При обнулении счётчика на его выходе появляется импуль Окончание счета. По появлении этого импульса процесс интерполяции заканчивается. В процессе счета сумма на выходе накапливающего сумматора при поступлении следующего счетного

импульса увеличивается на величину, внесенную в регистр хранения.

Недостатком известного линейного интерполятора является то, что при интерполировании необходимо заранее знать наклон прямой ( к оси времени и длительность интервала интерполяции (ДЬ)..При обработке в реальном масштабе времени экспериментальной информации, заданной в виде процессов, таких данных нет - наклон прямой и длительность интервала интерполяции (т.е. длительность импульсной помехи) могут быть произвольными. Кроме того, при наличии в обрабатываемом процессе lj(t) шумовой компоненты hjj, (t) непосредственное определение наклона интерполирующей прямой на интервале интерполяции (т.е. производной процесса 5(i) затруднено.

Цель изобретения - обеспечение линейного интерполирования процессов при наличии шумов в реальном масштабе времени.

Поставленная цель достигается тем, что цифровой адаптивный линейный интерполятор, содержащий генератор синхроимпульсов и последовательно включенные регистр хранения и накапливающий сумматор, содержит также дополнительные четыре регистра сдвига, многовходовый сумматор, блок вычисления интервала интерполяции, блок высисления приращения, блок формирования массива слагаемых, ключ и коммутатор, причем выходы многоразрядных ячеек первого и второго регистров сдвига соединены с входами сумматораj выход первого регистра сдвига соединен с информационными входами второго и третьего регистров сдвига, выход многовходового сумматора подключен к первому информационному входу блока вычисления приращения, выход генератора синхроимпульсов соединен с синхровходами блока вычисления интервала интерполяции, первого, второго, третьего и четвертого регистров сдвига, ключа, накапливающего сумматора и третьим синхровходом блока формирования массива слагаемых., управляющий вход блока вычисления интервала интерполяции является вторым входом интерполятора, информационный, первый и второй синхровходы блока вычисления интервала интерполяции соединены соответственно с вторым информационный

первым и вторым синхровходами блока вычисления приращения, х-йькод признака интерполяции блока вычисления интервала интерполяции соединен с информационным входом четвертого регистра сдвига, информационный вход блока формирования массива слагаемых соединен с выходом блока вычисления приращения, первый и второй синхровходы блока формирования массива слагаемых соединены соответственно с первым и вторым синхровыходами блока вычисления интервала интерполяции, выход третьего регистра сдвига соединен с входом записи регистра хранения, выход которого подключен к первым информационным входам накапливакяцего сумматора и коммутатора, выход четвертого регистра сдвига соединен с входами управления ключа, накапливающего сумматора и коммутатора, выход блока формирования массива слагаемых подключен к второму информационному входу накапливающего сумматора, выход ключа соединен с входом записи регистра хранения, вьгход накапливакицего сумматора подключен к второму информационному входу коммутатора, выход коммутатора является выходом линейного интерполятора, а информационный вход первого регистра сдвига является первым входом интерполятора.

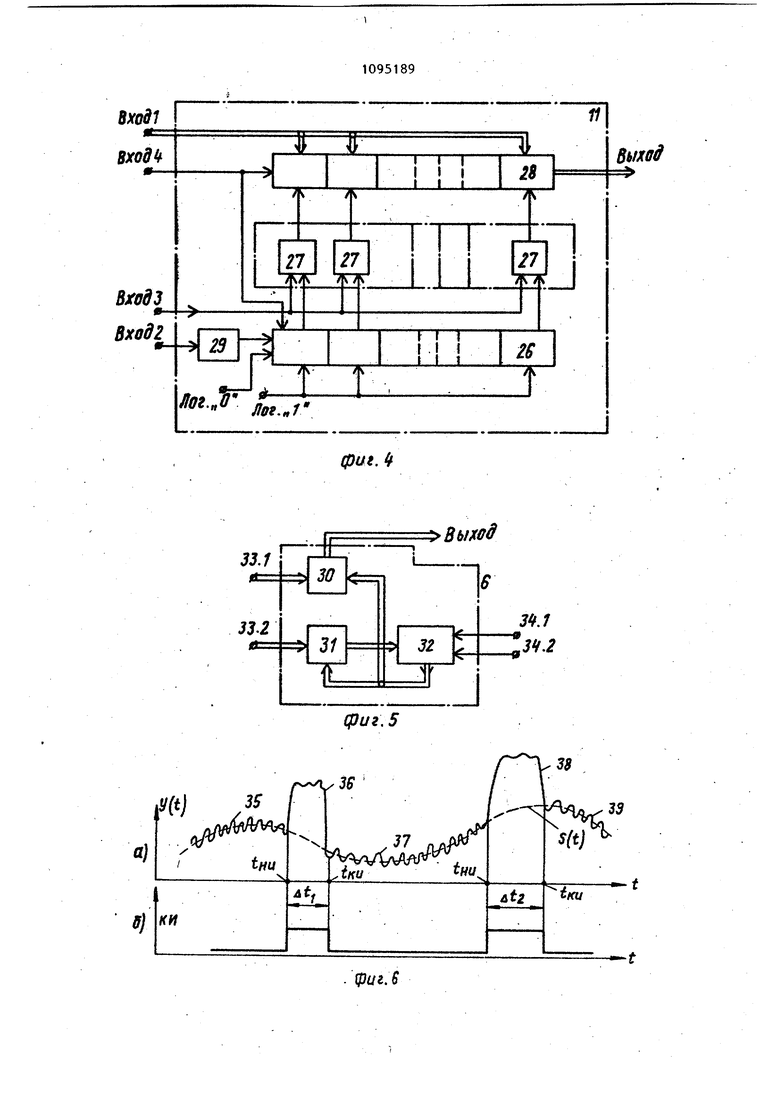

Блок вычисления интервала интерполяции содержит последовательно соединенные первый элемент И, пятый и шес той регистры сдвига, узел выделения заднего фронта импульса, выход которого соединен с R-входом R5 -триггера, а также является вторым синхровы ходом блока вычисления интервала интерполяции ,5 -вход R5 -триггера подключен к выходу первого элемента И, выход R5 -триггера соединен с входом узла вьщеления переднего фронта импульса и BTOpfiiM входом второго элемента И, а также является вь1ходом признака интерполяции блока вьгаисления интервала интерполяции, вьгход второго элемента И подключен к счетному входу двоичного счетчика, а выход узла выделения переднего фрон-га импульса соединен с входом установки нуля двоичного счетчика и является первым синхровыходом блока вычисления интервала интерполяции, информационным выходом которого является выход двоичного счетчика, первые входы первого и второго элементов И, а также синхровходы пятого и шестого

регистров сдвига объединены и являются синхровходом блока.вычисления интервала интерполяции, управляющим входом которого является вход первого элемента И. .

Блок вычисления приращения содержит второй и третий регистры хранения, вычитатель и делитель, информационные входы регистров объединены и являются первым информационным входам блока вычисления приращения, выходы второго и третьего регистров соединены соответственно с входами вычитания и сложения вычитателя, выход которого подключен -к информационному входу делителя, первый информационный вход и выход делителя являются соответственно вторым информационным входом и выходом блока вычисления приращения, первый и второй синхровходы блока вычисления приращения соединены соответственно с синхровходом второго регистра хранения, синхровходами третьего регистра хранения и делителя.

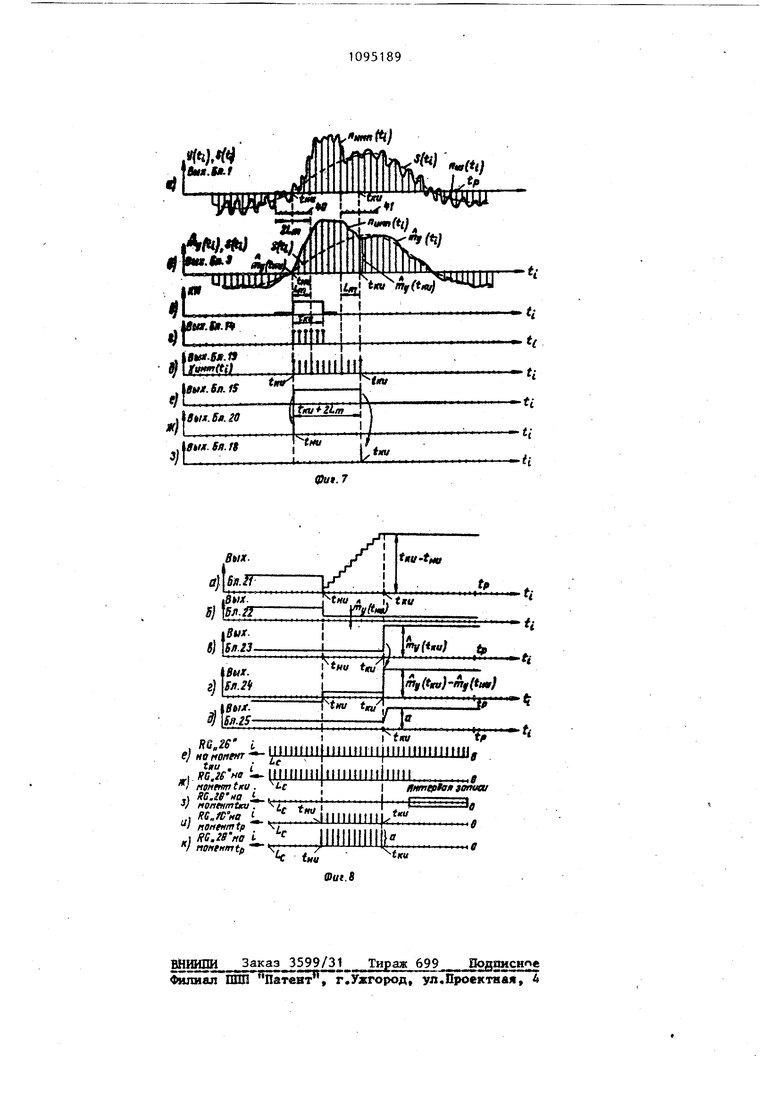

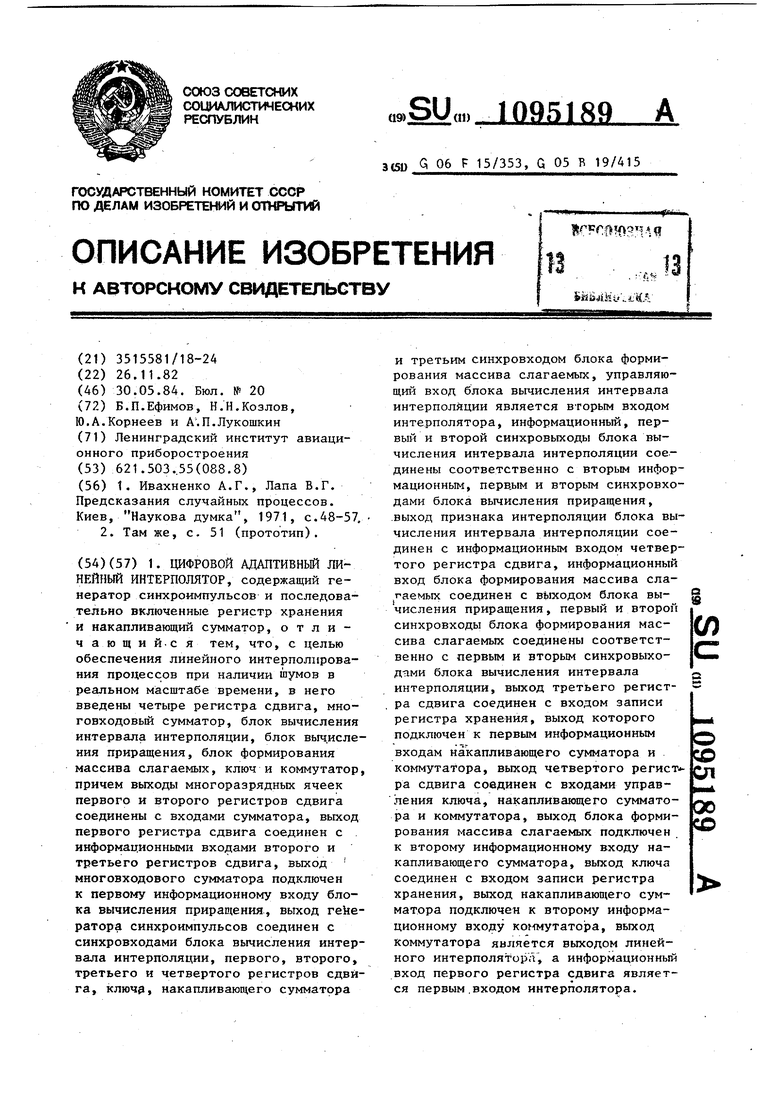

Блок формирования массива слагаемых содержит регистр сдвига частного и элемент задержки, установочные входы всех ячеек регистра сдвига частного объединены и являются информационным входом блока формирования массива слагаемых, выходом которого является выход регистра сдвига частного, управлякщие входы ключей объединены и являются вторым синхровхоДОМ блока формирования массива слагаемых, первым синхровходом которого является вход элемента задержки, шины импульсов сдвига регистра сдвига признаков записи и регистра сдвига частного объединены и являются третьим синхровходом блока формирования массива слагаемых, выход элемента задержки соединен с шиной записи регистра сдвига признаков записи, вход последовательного приема которого соединен с шиной логического нудя, установочные входы регистра сдвига признаков записи подключены к шине логической единвды, выходы ячеек регистра сдвига признаков эаписи соединены с информационными входами набора ключей, выходы ключей соединены с входами записи соответствующих ячеек регистра сдвига частного. На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока вычисления интервала интерполяции; на фиг. 3 - схема блока вычисления приращения; на фиг. 4 - схема блока формирования массива слагаемых; на фиг, 5 - схемы накапливакщего сумма тора; на фиг.,6 - эпюры, поясняющие работу интерполятора; на фиг. 7 и 8 эпюры сигналов основных блоков инте полятора. Устройство (фиг. 1) содержит пер вый 1 и второй 2 (многоразрядные) р гистры сдвига с отводами длиной ячеекi разрядность регистров соотве ствует разрядности обрабатываемых операндов, многовходовьй сумматор 3 с делением результата суммирования на 2L, третий (многоразрядный) ре гистр 4 сдвига длиной Lj, ячеек, регистр 5 хранения, накапливагаций сум матор 6, коммутатор 7, блок 8 вычис ления интервала интерполяции., блок вычисления приращения, четвертый (одноразрядный) регистр 10 сдвига длиной LJ, ячеек, блок 11 формирования массива слагаемых, ключ 12, генератор 13 синхроимпульсов. Блок 8 (фиг. 2) содержит первый элемент И 14, R5 -триггер 15, пятый 16 и шестой 17 однозарядные регистры сдвига длиной L ячеек каждый, узел 18 выделения заднего фрон та импульса, второй элемент И 19, узел 20 выделения переднего фронта импульса и двоичный счетчик 21. Блок 9 (фиг. 3) содержит второй и третий 23 регистры хранения, вычи татель 24 и делитель 25. Блок 11 содержит (фиг. 4) одноразрядный регистр 26 сдвига признаков записи длиной Lj, ячеек, ключи 27, многоразрядный регистр 28 сдвигд частного длиной Lf ячеек, элемент 29 задержки. Накапливающий сумматор 6 (фиг. 5 содержит первый 30 и второй 3t Комбинационные сумматоры, регистр 32 хранения и входы 33.1, 33.2 и 34.1, 34.2. На фиг. 6 приведены эпюры, по ясняющие условия работы интерполято ра, на фиг. 6а показан процесс у(t) на входе интерполятора, где 5 (t) полезньп сигнал (штриховая линия) , rqe, обозначены интервалы времени 35 36, 37, на которыхотсутствуют им11ул5ьсные помехи, т.е. процесс и (t). представляет на них смесь полезного сигнала 5 (t) и hb,(t), импульс ные помехи 38, 39, bi, . 2 длительность помеховых импульсов, i ц tm - начало и конец интервалов интерполяции; на фиг. 6 б показаны импульсы КИ (команда интерполяции), подаваемые на вход интерполятора от внешних устройств на интервалах времени, на которых должна осуществляться интерполяция процесса у (i). На фиг. 7 и фиг. 8 показаны эпюры сигналов основных блоков интерполятора. На фиг. 7а представлен обрабатываемый процесс Ц (i) на выходе регистра 1, где 5 (ti) полезный сигнал (пунктир); tiwMn(ii) импульсная помеха; Пщ (t;) аддитивный шум; inQ , i 1(4 моменты времени, соответствукяцие началу и концу интервала интерполяции; 40, 41 - положение интервала памяти сглаживающего фильтра в моменты времени i цу и , соответственно; 2 длина интервала памяти сглаживающего фильтра. На фиг. 7 б показана оценкатекущего среднего Гоц(ti) на выходе сумматора 3 (на выходе сглаживающего фильтра) ; на фиг. 7 в - команда интерполяции, подаваемая на второй вход интерполятора (фиг. 1), 2 «ч длительность команды интерполяции (соответствует длительности импульсной помехи); на фиг. 7 г - импульсы на выходе элемента И 14; на фиг. 7д импульсы интерполяции )fj,.j (i) на выходе элемента И 19; на фиг. 7 е импульс на выходе R5- триггера 15; на фиг. 7ж - импульс на выходе узла 20; на фиг. 7з - импульс на выходе узла 18; на фиг. 8а - изменения состояния счетчика 21 во времени, ( - число на выходе счетчика 21 после момента времени , , iviq- момент обнуления счетчика 21; на фиг. 86 - изменение состояния регистра 22 во времени (запись в регистр производится в момент времени на фиг. 8в - изменение состояния регистра 23 во времени, запись в регистр производится в момент времени ; на фиг, 8г - эпюра на выходе вычитателя 24; на фиг. 8д - эпюра на выходе делителя 25 (выход блока 9). На фиг. 8е и 8к показаны состояния ячеек регистров 10, 26, 28 в различные моменты времени. Нумерация ячеек регистров на этих эпюрах производится справа налево. Длина эпюр соответствует числу ячеек (длине Uс ) регистров сдвига. На фиг. 8е показано состояние ячеек регистра 26 в моМент времени (после записи логической единицы во все ячейки регистра импульсом с выхода элемента 29 (фиг. А); на фИг, 8ж - состояние ячеек регистра 26 в момент времени ; на фиг. 8з - интервал записи в момент ixu частного а в регистр 28; на фиг. 8и - состояние ячеек регистра 10 в момент времени Ip (to обозн чен на эпюрах 7а, За - 8д); на фиг. 8ж - состояние ячеек регистра 28 в момент времени р. Принцип работы устройства заклю.чается в следующем. Обрабатываемый процесс 1( (i) в параллельном двоичном коде подается на первый вход интерполятора. Эпюра процесса на выходе регистра 1 приведена на фиг. 7а (шаг временной дискретизации на фиг. 7 и 8 показан делениями на временной оси). Регист ры 1 и 2 и сумматор 3 образуют сгла живающий фильтр. Количество входов сумматора равно общему числу Ячеек памяти обоих регистров сдвига, т.е. равно 2Lf. Процесс П1у (1; ) на выходе суммато ра 3 представлен на фиг. 76: гдetт).(t;) - оценка текущего среднег процесса и (t). Операция деления (округления) на 2L, реализуется в сумматоре 3 бл годаря рациональному выбору длины регистров 1 и 2. При (где К - целое) операция деления ре лизуется путем сдвига результата сум мирования вправо на (К+1) двоичных разрядов. На практике L равно 2-4 В случае отсутствия шумов адаптив ное линейное интерполирование обраба тываемого процесса производится по отсчетам Vj (ii), взятым на концах интервала интерполяции, равного длител ности it.-команды интерполяции (фиг При этом на интервале длительности команды интерполяции формируется полином первого порядка ; Ча..Ьу1,,, где t. ,1цц,1цц - момент времен соответствующий началу интервала интерполяции; i((u -.момент времени, соответствующий концу интервала инте поляции; О,- коэффициент полинома, определяемый по отсчетам.процесса 1(1цч), V) (Цц). ji.(tHu) .и--Ьич (О где моменты времени t ,ц ,i соответствуют передне и заднему фронту импульсной-fiOMexH (фиг. 6а) . Наличие шумовой компоненты и (-t;) в процессе ij (i) при такой процедуре интерполирования приводит к большим флюктуациям наклона интерполирующей прямой, что недопустимо при дальнейшем выделении полезной информации из обрабатываемого процесса. Введение предварительного сглаживания обеспечивает cyщecтвe нoe уменьшение дисперсии (в 2 1д раз) оценки текущего среднего WM(1) по сравнению с дисперсией исходного процесса U (i;j), так как 1 UO . В такое же число раз уменьшается дисперсия наклона интерполирующей прямой. Использование предварительного сглаживания фильтром с конечной памятью, имеющего память в 2 L интервалов временной дискретизации, приводит к особенностям при формировании (определении) интервала интерполяции. Эти особенности состоят в том, что длительность импульсных помех п JIMP (i), прошедших через сглаживающий фильтрJувеличивается на величину интервала памяти сглаживающего фильтра, т.е. 2 L интервалов дискретизации. Поэтому в блоке 8 вычисления интервала интерполяции (фиг. 1 и 2) определение интервала интерполяции производится с учетом эффекта удлинения длительности импульсной помехи. Блок 8 работает следующим образом. На синхронизирующий вход блока по«даются синхроимпульсы с выхода генератора 13. На управляющий вход блока 8 подается команда интерполяции (фиг. 7в), длительность которой соответствует исходной длительности импульсной помехи (фиг. 7а). Первым элементом И 14 производится стробирование последовательности синхроимпульсов командой интерполяции. 11 Гребенка синхроимпульсов на выходе, элементов И 14 показана на фиг. 7г. Первым импульсом гребенки с выхода первого элемента И 14 R5-триггер 15 устанавливается в единичное состоя- ние. Видеоимпульс, формируемый на выходе триггера 15, подается на вход элемента И 19, на другой вход которо го подаются импульсы с выхода генера тора 13. Кроме того, гребенка видеоимпульсов с выхода элемента И 14 подается на последовательно соединенный пятый и шестой регистры 16 и 17, каждый из которых обеспечивает задержку информации наЬуу, интервалов временной дискретизации. Таким образом, на выходе регистра 17 формирует ся видеоимпульс, форма которого повторяет форму команды интерполяции (фиг. 7в, г), а задний фронт видеоимпульса задерживается относительно исходной команды интерполяции на 21, интервалов дискретизации (фиг. 8д,е). Узел 18 формирует з ы6 MeHTijcq импульс окончания интервала интерполяции (фиг. 7з). Этот импульс подается наR -вход RS-триггера, уста навливая его в нулевое состояние. Та ким образом, длительность видеоимпульса, формируемого на выходе (5-триггера 15 (фиг. 7е), равна Ь(41+2С , гдеS щ, - длительность команды интерполяции, подаваемой на вход интерполятора (фиг. 1), 2о( интервал памяти сглаживающего фильтра. Из переднего фронта видеоимпульса, формируемого на выходе триггера 15 (фиг. 7е) узлом 20, в момент времени , соответствующий началу интервала интерполяции, формируется импульс (фиг. 7ж), подаваемый на вхо установки нуля счетчика 21, а также на синхронизирующий выход блока .8. На выходе элемента И 19 формирует ся гребенка импульсов j (i) (фиг. 7д), число которых определяется длительностью строба на выходе триггера 15 (фиг. 7е). Значение длительности интервала интерполяции определяется как число импульсов временной дискретизации (фиг. 7д) от моментаЧц4 до момента t цц путем счета импульсов гребенки счетчиком- 21 (фиг. 8а). Таким образом, на выходы блока 8 подаются следующ1 е сигналы (импульсы): на информационный выход - число в двоичном коде, соответствукнцее дли тельности интервала интерполяции; 8912 на выход признака интерполяции видеоимпульс, соответствующий интервалу интерполяции (фиг. 7е); на первый синхронизирующий выход - импульс, соответствующий началу интервала интерполяции (фиг. 7ж); на второй синхронизирующий выход - импульс , соответствующий концу интервала интерполяции (фиг. 7з) . Блок 9 (фиг. 3) работает следующим образом. Информационные входы регистров 22 и 23 объединены и являются первым информационным входом блока 9. На первый информационный вход блока 9 подается процесс гпц ( t) с выхода сумматора 3 (фиг. 7б). По импульсу, формируемому на выходе узла 20 и подаваемому на синхровход регистра 22, в момент времени t (ц с первого синхровхода блока 9 в регистр 22 записьтается отсчет процесса гПц () (фиг.,8б). По импульсу, формируемому на выходе узла 18 и подаваемому на синхровход регистра 23 с второго синхроБхода блока 9, в момент времени ivi, в регистр 23 записывается -КЧ отсчет процесса (кц (фиг. 8в). ) КЦ В момент времениt на выходе вычитателя 24 формируется разность My (t (.,ц)-П1ц(1нч) которая поступает на второй информационный вход делителя 25 (фиг. 8г). На первый информационный вход делителя в этот же момент времени поступает разность (ij-vj-tHn) с выхода счетчика 21 (фиг. 2 и 8а), равная числу импульcoB yH(t) на интервале интерполяции (фи. 7д). По импульсу, подаваемому на синхровход делителя 25, на выходе делителя формируется частное (приращение) (фиг. 8д) Alty;i,)-A(tH4 т ч (6) которое подается на информационньй вход блока 11 (фиг. 4). На первый и второй синхровходы блока 11 подаются импульсы начала (фиг. 7ж) и конца, (фиг. 7з) интервала интерполяции, и на третий синхровход блока 11 подаются импульсы с выхода генератора 13. Блок 11 работает следующим образом. Частное а подаётся на устанопочные входы всех ячеек регистра 28. Число ячеек (элементов задержки) н регистрах 4, 10,, 26 и одинаково и равноЬс изС имякс Д кимагГ

13

максимальная длительность команды интерполяции (она определяется условиями работы интерполятора, конкретным его применением). Продвижение информации по регистрам 4, 10, 26 и 28 производится импульсами сдвига с генератора 13. В регистр 1 последовательно записываются (по информационному входу регистра) импульсы; / ;).

На фиг. 8и показана информация (состояния ячеек регистра), записанная в регистр 10 на момент времени to (положение момента времени показано на фиг. 8 а-д).

В регистр 26 запись информации производится с установочных входов ячеек регистра по команде, подаваемой с первого синхровхода блока 11 чере;з элемент 29, при этом во все ячейки регистра 26 записьшается логическая единица. Введение элемента 29 необходимо для разнесения во времени операции сдвига информации в регистре 26 и операции записи информации с установочных входов регистра. Состояние ячеек регистра 26 на- момент времени ,ц (после поступления импульса Запись) показано на фиг. 8е. Вход последовательного приема регистра 26 подключен к шине логического нуля, поэтому на момент записи в регистр 10 всей группы импульсов Y (t;j), соответствующих интервалу интерполяции, (например, момент 1(ц на фиг. 7а и 8а) в первых кц нч ячейках регистра 26 будут записаны нули (фиг. Вж). Импульс из узла 18 блока 8, подаваемый на второй сннхровход блока 11, проходит только через те ключи 27, на входы запрета которых подаются логические нули (фиг. 8ж). Импульсы, прошедшие ключи 27, поступают на шины записи ячеек регистра 28, при этом только в эти ячейки и записывается частное а (6) , соответствующее данному Интервалу интерполяции (фиг. 8з). Таким образом, в каждом цикле записи информации в регистр 28 запись производится только в те ячейки, которые соответствуют текущему интервалу интерполяции. Другие ячейки регистра 28 находятся при этом в режиме хр нения. Состояние (записанная информация) регистра 28 на момент времени tp показано на фиг. 8к.

На выходе ключа 12 формируются имггульсы Инверсные по факту появ9518914

Ленин к импульсамуj, (ti) , т.е. при поступлении с выхода регистра 10 первого из импульсов ,( ij) регистр 5 переводится в режим хранения (на него 5 не подаются импульсы записи), при

этом в нем записывается отсчету (). На второй информационный вход сумматора 6 в каждом интервале дискретизации данного интервала интерполяции

О поступает частное а и по каждому импульсу временной дискретизации на интервале интерполяции производится суммирование промежуточной суммы с частным а с сохранением нового

5 результата до следующего.цикла суммирования. Таким образом реализуется алгоритм формирования 1 gi (1, ), описываемый формулой (3). При этом коммутатор 7 переведен управляющим

0 сигналом с выхода регистра 10 в нижнее положение и на выход интерполятора подаются отсчеты Q дц( ii) Вне интервала интерполяции j, (tj)0 подвижные контакты коммутатора 7

5 переводятся в верхнее положение и на выход интерполятора подаются отсчеты Ц (i) с выхода регистра 5. Реги.:тры 4 и 10 служат для компенсации задержки исходного процесса и

- решений об интерполяцииjj,(i), появляющейся при измерении длительности команды интерполяции в блоке 8.

Схема сумматора 6 приведена на фиг. 5. Сумматор 6 состоит из комби5 национных сумматоров 30 и 31 и регистра хранения 32. На вход 33.1 сумматора 6 подаются операнды с выхода регистра 5. На вход 33.2 сумматора 6 подается частное а с выхода бло ка 11i На вход 34.1 (перевода в режим записи) сумматора 6 (т.е. на вход установки нуля регистра 32) подаются сигналы jj Ci) с выхода регистра 10, при этом регистр 32 переводится из режима обнуления в режим записи. На вход 34.2 синхронизирующего сумматора 6 подаются импульсы с выхода генератора 13; этими импульсами обеспечивается запись ре зультата сложения с выхода сумматора 31 в регистр 32. В t -ом интервале дискретизации на выходэ суммато1-1

ра 31 формируется сумма (21 О +а),

5 при этом на выходе сумматора 30

(т.е. на выходе сумматора 6) образуется текущий результат интерполирования(trtHO. Вне интервала интерполирования сигнал с выхода регистра 10 равен нулю регистр 32 обнуляется и суммирования в накапливающем сумматоре при посту лении синхроимпульсов не происходит В блоке 8 узлы выделения заднего 18 и переднего 20 фронтов реализ ются как схемы формирования коротки импульсов из перепадов. Таким образом, введение новых блоков и связей между ними наряду с имеющимися в прототипе блоками и связями позволяет реализовать следующие операции: с помощьк сглаживающего фильтра, образованного первым и вторым регистрами сдвига и .многовходовым сумматором, сгладит флюктуации, обусловленные наличием во входном процессе 4 (Ьр шумовой компонентылц, (i) ; вычислить, исходя из длительности команды интерполяции и интервала памяти сглаживающего фильтра, длительность интервала интерполяции; по отсчетам процес са с выхода сглаживающего фильтра, взятым на концах интервала интерполяции, и длительности интервала интерполяции вычислить приращение интерполированного процесса, отнесенное к одному интервалу временной -J .. - . f - . дискретизации входного про,цесса (ра

ному периоду повторения синхроимп ьсов с выхода генератора); сформировать продвигающийся по регистрам сдвига синхронно с продвижением входного процесса массив слагаемых, каждый член которого равенприращению интерполированного процесса .на интервале временной дискретизации;

полируемой прямой и длительности интервала интерполяции и.может быть использован при обработке информации, передаваемой по каналам с шумами и импульсными помехами (или сбоями в аппаратуре), при обработке фонограмм, а также в радиолокации и радиосвязи. 8916 по сигналам с четвертого регистра сдвига в накапливающем сумматоре на интервалах интерполяции из исходного отсчета входного процесса (для каждого массива) и массивов слагаемых (с выхода блока формирования массива слагаемых) сформировать интерполированный процесс. Реализация предлагаемым интерполятором перечисленных операций обеспечивает интерполяцию входного процесса по командам интерполяции в реальном масштабе времени. Для осуществления интерполяции с помощью известных устройств необходимо заранее знать наклон интерполируемой прямой и длину интервала интерполяции. Такие условия работы интерполяторов характерны и допустимь1 при программном управлении станками. При обработке в реальном масштабе времени экспериментальной информации, задаваемой в виде процессов (цифровых последовательностей), таких данных априорно не существует. Кроме того, при наличии шумов интерполирование процессов по алгоритмам, реализуемым известными устройствами, осуществляется со значительными флюктуапионньми ошибками. Предлагаемый цифровой линейньй адаптивный интерполятор позволяет осуществлять в реальном масштабе времени интерполяцию процессов при - - С ----- -l -w априорно неизвестных наклоне интерФи.г

(риг.5

Выход

бы/од

B/oS2

r-Л

фиг. 5

фиг.5 36

nOHtHlntf,

tHO

яи

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Предсказания случайных процессов | |||

| Киев, Наукова думка, 1971, с.48-57 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1984-05-30—Публикация

1982-11-26—Подача