Устройство относится к области обработки сигналов с целью повышения их соответствия входным для устройства сигналам и, в первую очередь, к области обработки сигналов с целью повышения разрешения их элементов, в том числе, в случаях экономных хранения и передачи дискретных данных о сигнале.

Известны [1] устройства для обработки сигналов, содержащие последовательно соединенные частотный фильтр (ЧФ) и оптимальный восстанавливающий фильтр, обеспечивающие при гауссовом шуме минимальную среднеквадратичную ошибку восстановления. Недостатком этих устройств является недостаточное разрешение элементов сигналов.

Известны [2] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и конвольвер и обеспечивающие примерно вдвое более высокое разрешение элементов сигнала. Эти устройства имеют недостаток, состоящий в высоком уровне осцилляции (паразитных осцилляций, "хвостов", боковых лепестков) за пределами подлежащих разрешению элементов входного сигнала и в пониженном контрасте элементов и групп элементов малой протяженности.

Известны [3] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и интерполятор, в которых, благодаря представлению сигналов в базисе сфероидальных волновых функций, верхняя частота гармонического спектра сигнала может превышать половину частоты дискретизации, что позволяет использовать этот дополнительный ресурс для некоторого понижения уровня паразитных осцилляций и повышения разрешения. Эти устройства имеют недостаток, состоящий в недостаточно пониженном уровне паразитных осцилляций, в низком контрасте малопротяженных элементов сигнала и в недостаточном разрешении элементов сигнала.

Известны [4] устройства для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и блок реставрации сигналов методом Монте-Карло, обеспечивающие не ограниченные полосой частот ЧФ крутизну перепадов и расстояние разрешения. Недостатком таких устройств является низкая вероятность соответствия реставрированного сигнала входному, поскольку принцип их действия базируется на интегральной информации о сигнале (энергия), причем не входном для устройства, а входном для блока реставрации.

От этого недостатка свободны устройства [5] для обработки сигналов, содержащие последовательно соединенные ЧФ, дискретизатор и блок редукции устройства к квазисовершенному, предназначенный для интерполирования отсчетов сигнала, выявления в них перепадов и формирования сокращенного описания сигнала в виде последовательности перепадов с характеристиками, приближенными к характеристикам перепадов во входном сигнале.

Однако и эти устройства имеют недостаток, состоящий в недостаточно высоком разрешении элементов сигнала, в недостаточной чувствительности к малоконтрастным элементам сигнала, в низком быстродействии и в высокой сложности, что обусловлено принципом действия - синтезом сигнала на основе выявления перепадов и их коррекции по результатам сравнения реакций ЧФ на входной и синтезированный сигналы. А именно, некоторые перепады, особенно малого контраста, могут быть пропущены из-за их маскирования осцилляциями, то есть из-за собственного шума устройства; низкое быстродействие и высокая сложность связаны с необходимостью вычисления реакции ЧФ на синтезированный сигнал и с необходимостью ее сравнения с реакцией ЧФ на входной сигнал.

Заявляемое изобретение направлено на уменьшение собственного шума устройства, то есть на исключение реагирования на паразитные осцилляции сигнала и на исключение необходимости вычисления реакции ЧФ на синтезированный сигнал и ее сравнения с реакцией ЧФ на входной сигнал.

Решение этой задачи обеспечивает:

- повышение разрешения элементов сигнала, в том числе, малоконтрастных;

- повышение чувствительности к малоконтрастным элементам сигнала;

- повышение быстродействия;

- уменьшение сложности устройства.

Для этого (в первом варианте предлагаемого устройства) в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно вводится блок редукции к совершенному устройству, вход которого соединен с выходом дискретизатора, а выход является выходом устройства. Это позволяет интерполировать отсчеты, поступающие с выхода дискретизатора, определять по интерполированным отсчетам параметры элементов входного для устройства сигнала и (в пределах функционирования устройства) формировать (синтезировать) описание или вычислять отсчеты входного сигнала (являющиеся и описанием, отсчетами выходного для совершенного устройства сигнала) посредством (путем) накопительного суммирования заранее запасенных или вычисляемых отсчетов элементов входного сигнала при одновременном последовательном (накопительном) вычитании из интерполированных отсчетов, отсчетов выходных реакций ЧФ на эти элементы входного сигнала с повторением этих (описанных) действий до достижения таким образом уменьшаемыми интерполированными отсчетами наперед (заранее) заданных или динамично определяемых характеристик и тем самым выполнять совершенное [6] восстановление сигнала вплоть до предельно разрешаемых и с предельно малой амплитудой его элементов.

При этом предельное разрешение ограничивается коэффициентом вышеупомянутой интерполяции и шумами, не позволяющими определить параметры элементов малой амплитуды, поэтому в качестве вышеназванной характеристики уменьшаемых интерполированных отсчетов (в качестве критерия окончания синтеза сигнала) могут быть использованы, например, энергия, сумма модулей, максимальное из значений остаточных интерполированных отсчетов.

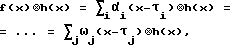

Входной для устройства сигнал f(x) может быть представлен бесконечным числом разложений f(x) = ∑iαi(x-τi) = ... = ∑jωj(x-τj) по различного рода элементарным сигналам αi(x-τi), ..., ωj(x-τj), в том числе, конечных длительностей.

Соответственно, выходная реакция ЧФ на этот сигнал есть

где ⊗ - операция свертки, h(x) - импульсная функция ЧФ (импульсная реакция, импульсная характеристика, функция рассеяния точки), τi и τj - смещения (координаты) элементов сигнала.

Из этого следует, что при любом выборе элементов αi(x-τi) сигнала (элементарных сигналов) в процессе синтеза синтезированный сигнал сходится к f(x), если характеристика уменьшаемых интерполированных отсчетов

f(x)⊗h(x)-∑

соответствующая вышеуказанному критерию остановки синтеза, с ростом I стремится (при отсутствии шума) к нулю. Промежуточные ошибки в выборе элементов сигнала могут только увеличить время синтеза, но не более. Поэтому даже стохастический выбор элементов сигнала в процессе синтеза приводит к положительному результату, если учитывать только те из них (или хотя бы только такую их совокупность), которые (которая) ведут (ведет) к завершению синтеза по вышеуказанному критерию. Но быстродействие устройства (скорость синтеза) существенно зависит от принятого множества (набора) элементарных сигналов и от рационального применения этого множества в процессе синтеза. Такой набор в простейшем случае может состоять, например, из одного прямоугольного импульса при различных его количественных характеристиках; более сложный, но и более эффективный (обеспечивающий более высокое быстродействие устройства) набор может состоять, например, из прямоугольного импульса, треугольного импульса, импульсов криволинейной формы при различных их количественных характеристиках.

Второй вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введены последовательно соединенные блок подавления помех, вход которого соединен с выходом дискретизатора, и блок редукции к совершенному устройству, выход которого является выходом устройства. Это позволяет в блоке подавления помех уменьшать уровень шума посредством нормализации поступающих с выхода дискретизатора отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций ЧФ, а в блоке редукции к совершенному устройству выполнять вышеописанным для первого варианта устройства образом синтез описания, в том числе, при необходимости, вычисление отсчетов входного для устройства сигнала. Уменьшение блоком подавления помех уровня шума дополнительно повышает достижимое в устройстве разрешение элементов входного для него сигнала.

Третий вариант предлагаемого устройства состоит в том, что в устройстве для обработки сигналов по п. 1 или п.2 блок редукции к совершенному устройству по окончании синтеза входного сигнала прибавляет к синтезированной (совершенно восстановленной) части входного сигнала остаток интерполированных отсчетов или его преобразование, например, в виде текущего среднего. Это позволяет, например, частично компенсировать возможную неоптимальность выбора очередных элементов сигнала в процессе синтеза, улучшить передачу устройством "тонких" изменений входного сигнала (например, типа медленных изменений сигнального фона).

Четвертый вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введен блок редукции к совершенному устройству, вход которого соединен с выходом дискретизатора, а выход является выходом устройства, причем блок редукции к совершенному устройству содержит последовательно соединенные интерполятор, узел определения параметров элементов (входного) сигнала и синтезатор описания (выходного) сигнала, при этом вход интерполятора является входом, а выход синтезатора описания входного сигнала является выходом блока редукции к совершенному устройству. Это позволяет (благодаря интерполятору) формировать детальное представление обрабатываемого сигнала вплоть до масштаба мельчайших подлежащих разрешению элементов, посредством узла определения параметров элементов входного сигнала определять, например, положение, амплитуду, форму очередных элементов, а посредством синтезатора описания (выходного) сигнала формировать описание восстановленного сигнала (например, в виде совокупности его элементов и/или отсчетов) и тем самым получать реакцию совершенного устройства на входной сигнал.

Пятый вариант предлагаемого устройства состоит в том, что в устройство для обработки сигналов, содержащее последовательно соединенные ЧФ, вход которого является входом устройства, и дискретизатор, дополнительно введены последовательно соединенные блок подавления помех, вход которого соединен с выходом дискретизатора, и блок редукции к совершенному устройству, выход которого является выходом устройства, причем блок подавления помех содержит последовательно соединенные узел оценки скорости роста (сигнала) и узел нормализации, блок редукции к совершенному устройству содержит последовательно соединенные интерполятор, узел определения параметров элементов (входного) сигнала и синтезатор описания (выходного) сигнала, при этом вход узла оценки скорости роста (сигнала) и выход узла нормализации являются соответственно входом и выходом блока подавления помех, вход интерполятора и выход синтезатора описания сигнала являются соответственно входом и выходом блока редукции к совершенному устройству. Это позволяет в узле оценки скорости роста проверять динамическое (по особенностям нарастания и спада, например, по длительности) и амплитудное соответствие импульсных элементов возможным выходным реакциям ЧФ, а в узле нормализации модифицировать недопустимо искаженные импульсные элементы с приведением их в соответствие возможным выходным реакциям ЧФ и тем самым обеспечивать условия для более эффективной работы блока редукции к совершенному устройству, в составе которого интерполятор, узел определения параметров элементов сигнала и синтезатор описания сигнала вышеописанным для четвертого варианта устройства образом выполняют совершенное восстановление входного сигнала вплоть до предельно разрешаемых и с предельно малой амплитудой его элементов в условиях пониженного уровня шума.

Шестой вариант предлагаемого устройства состоит в том, что в устройстве для обработки сигналов по четвертому или пятому вариантам, узел определения параметров элементов входного сигнала в составе блока редукции к совершенному устройству содержит последовательно соединенные коммутатор, определитель параметров элементов сигнала, формирователь выходной реакции ЧФ на элемент сигнала, накопительный (запоминающий разности) вычитатель и схему принятия решения о завершении синтеза, причем вход коммутатора и выходы определителя параметров элементов сигнала, накопительного вычитателя, схемы принятия решения о завершении синтеза являются соответственно входом и выходом узла определения параметров элементов входного сигнала (то есть выходом узла определения параметров элементов входного сигнала являются выход определителя параметров элементов сигнала, выход накопительного вычитателя и выход схемы принятия решения о завершении синтеза), выход коммутатора соединен со вторым входом (входом уменьшаемого) накопительного вычитателя, а выход накопительного вычитателя и выход схемы принятия решения о завершении синтеза соединены соответственно со вторым и третьим входами коммутатора. Это позволяет пропускать через коммутатор сначала интерполированные отсчеты, поступающие с выхода интерполятора, а потом уменьшенные с каждым элементом сигнала интерполированные отсчеты с выхода накопительного вычитателя, в определителе параметров элементов сигнала определять количественные характеристики очередных элементов сигнала (например, координату, амплитуду, протяженность, форму), выдавать эти характеристики на выход узла определения параметров элементов сигнала, в формирователе выходной реакции ЧФ на элемент сигнала определять по параметрам очередных элементов сигнала отсчеты выходной реакции ЧФ на эти элементы, в накопительном вычитателе вычитать из уменьшаемых интерполированных отсчетов отсчеты реакции ЧФ на очередной элемент сигнала, в схеме принятия решения о завершении синтеза анализировать уменьшаемые интерполированные отсчеты и по вышеописанным критериям определять момент завершения синтеза.

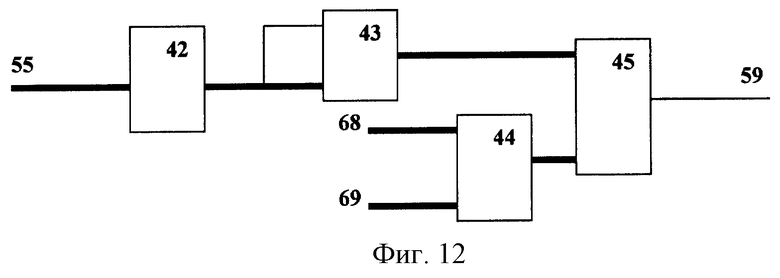

На фиг.1, представлена блок-схема предлагаемого устройства для обработки сигналов по п.1 и п.3 формулы изобретения.

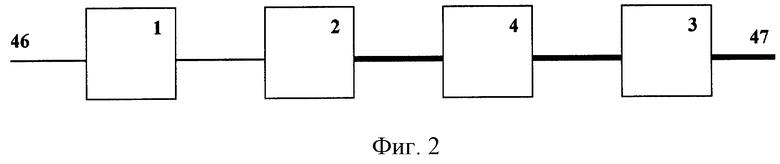

На фиг.2 представлена блок-схема предлагаемого устройства для обработки сигналов по п.2 и п.3 формулы изобретения.

На фиг.3 представлена блок-схема блока редукции к совершенному устройству в составе предлагаемого устройства для обработки сигналов по п.4 и п.5 формулы изобретения.

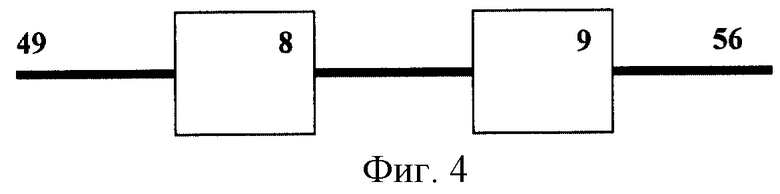

На фиг. 4 представлена блок-схема блока подавления помех в составе предлагаемого устройства для обработки сигналов по п.5 формулы изобретения.

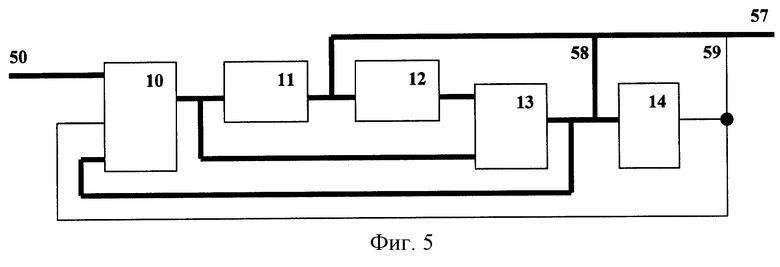

На фиг. 5 представлена блок-схема узла определения параметров элементов сигнала в составе блока подавления помех предлагаемого устройства для обработки сигналов по п.6 формулы изобретения.

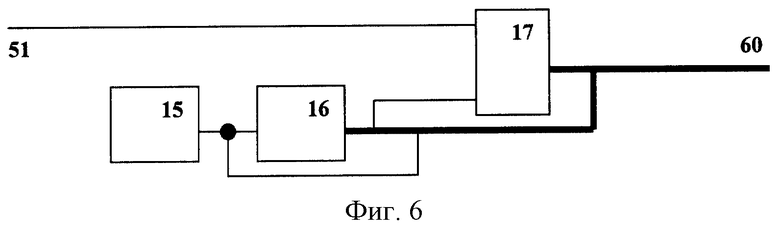

На фиг.6 представлен пример блок-схемы дискретизатора.

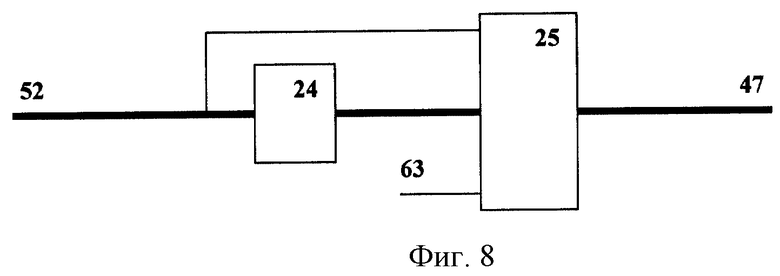

На фиг.7, 8, представлены примеры блок-схем соответственно интерполятора и синтезатора описания входного сигнала.

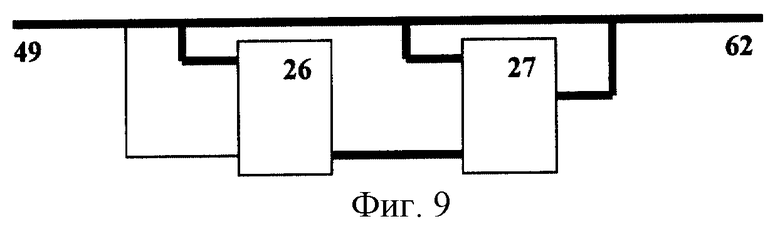

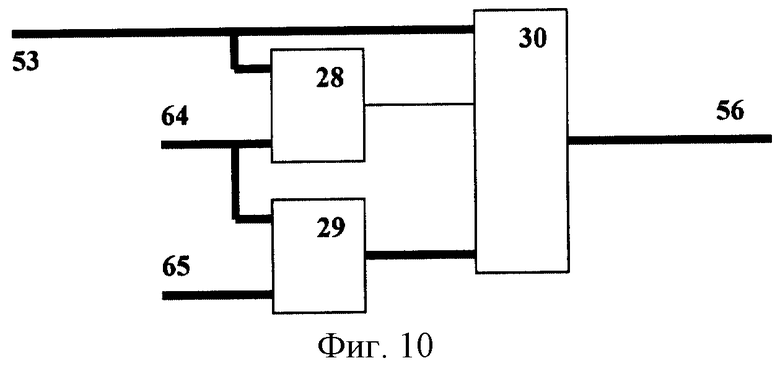

На фиг. 9, 10 представлены примеры блок-схем соответственно узла оценки скорости роста и узла нормализации.

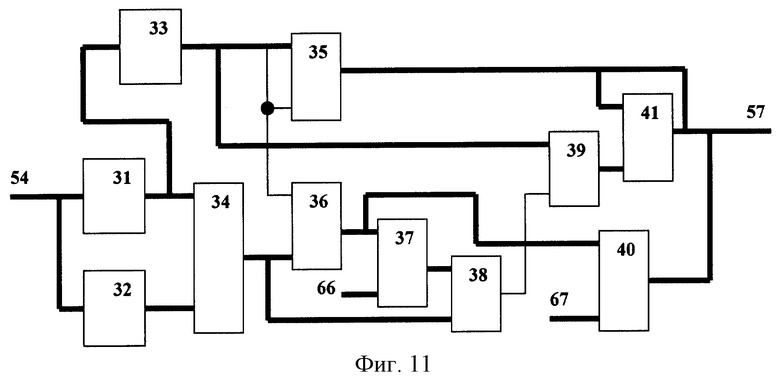

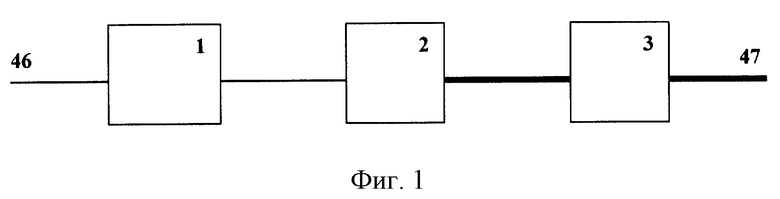

На фиг. 11, 12 представлены примеры блок-схем определителя параметров элемента сигнала и схемы принятия решения о завершении синтеза.

Первый вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству.

Второй вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству и блок 4 подавления помех.

Третий вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству или ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству и блок 4 подавления помех.

Четвертый вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству, содержащий интерполятор 5, узел 6 определения параметров элементов входного сигнала, синтезатор 7 описания выходного сигнала.

Пятый вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству и блок 4 подавления помех, а также в составе блока 3 редукции к совершенному устройству интерполятор 5, узел 6 определения параметров элементов входного сигнала, синтезатор 7 описания выходного сигнала и в составе блока 4 подавления помех узел 8 оценки скорости роста и узел 9 нормализации.

Шестой вариант устройства содержит ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству или ЧФ 1, дискретизатор 2, блок 3 редукции к совершенному устройству и блок 4 подавления помех, а также в составе блока 3 редукции к совершенному устройству интерполятор 5, узел 6 определения параметров элементов входного сигнала, синтезатор 7 описания выходного сигнала, в составе блока 4 подавления помех узел 8 оценки скорости роста и узел 9 нормализации и в составе узла 6 определения параметров элементов входного сигнала коммутатор 10, определитель 11 параметров элементов сигнала, формирователь 12 выходной реакции ЧФ 1 на элемент сигнала, накопительный вычитатель 13, схему 14 принятия решения о завершении синтеза.

Дискретизатор 2 содержит, например, импульсный генератор 15, формирователь 16 сетки частот, аналого-цифровой преобразователь (АЦП) 17.

Интерполятор 5 содержит, например, ЧФ 18, триггер 19, коммутатор 20, цифровые линии (ЦЛЗ) 21 и 22 задержки, коммутатор 23.

Синтезатор 7 описания выходного сигнала содержит, например, узел 24 памяти, оптимизатор 25 описания выходного сигнала.

Узел 8 оценки скорости роста содержит, например, регистр 26, вычитатель 27.

Узел 9 нормализации содержит, например, элемент 28 сравнения, умножитель 29, коммутатор 30.

Определитель 11 параметров элемента сигнала содержит, например, сглаживатель 31, вычислитель 32 текущего среднего, вычислитель 33 координат максимума и нуля, вычитатель 34, регистры 35 и 36, умножитель 37, элемент 38 сравнения, регистр 39, умножитель 40, вычитатель 41.

Схема 14 принятия решения о завершении синтеза содержит, например, формирователь 42 количественной характеристики, регистр 43, умножитель 44, элемент 45 сравнения.

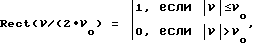

ЧФ 1 представляет собой, например, фильтр низких частот, может быть выполнен, например, на основе индуктивностей и конденсаторов или резисторов и конденсаторов. Частотная характеристика ЧФ 1 описывается, например, весовым окном Гаусса [7]

G(ν) = exp[-0,5•(A•ν/νo)2]•Rect(ν/(2•νo)),

где νo - граничная частота ЧФ 1 как фильтра низких частот,

А - параметр,

АЦП 17 может быть выполнен, например, в виде микросхемы AD570 [8].

ЧФ 18 является интерполирующим, то есть имеет импульсную характеристику вида (sinx)/x, и может быть выполнен, например, на основе сумматоров, умножителей, регистров, логических элементов [9].

Узел 24 памяти может быть выполнен, например, в виде ЦЛЗ.

Входы устройства:

46 - информационный вход.

Выходы устройства:

47 - информационный выход.

Входы и выходы составных частей, являющиеся входами и выходами составной части более высокого уровня, имеют номера входов и выходов составной части более высокого уровня.

Остальные входы блока 3 редукции к совершенному устройству, блока 4 подавления помех, дискретизатора 2, узла 6 определения параметров элементов сигнала, синтезатора 7 описания входного сигнала, узла 9 нормализации, определителя 11 параметров элемента сигнала, схемы 14 принятия решения о завершении синтеза:

48 - вход блока 3 редукции к совершенному устройству,

49 - вход блока 4 подавления помех,

50 - вход узла 6 определения параметров элементов сигнала,

51 - сигнальный вход дискретизатора 2,

52 - вход синтезатора 7 описания входного сигнала,

53 - вход узла 9 нормализации,

54 - вход определителя 11 параметров элемента сигнала,

55 - вход схемы 14 принятия решения о завершении синтеза.

Остальные выходы блока 4 подавления помех, узла 6 определения параметров элементов сигнала, схемы 14 принятия решения о завершении синтеза в составе выхода 57 узла 6 определения параметров элементов сигнала, дискретизатора 2, интерполятора 5, узла 8 оценки скорости роста:

56 - выход блока 4 подавления помех,

57 - выход узла 6 определения параметров элементов сигнала,

58 - выход накапливающего вычитателя 13 в составе выхода 57 узла 6 определения параметров элементов сигнала,

59 - выход схемы 14 принятия решения о завершении синтеза в составе выхода 57 узла 6 определения параметров элементов сигнала,

60 - выход дискретизатора 2,

61 - выход интерполятора 5,

62 - выход узла 8 оценки скорости роста.

Внутренние входные шины - источники констант, задаваемых подключением отдельных линий к уровням логических "0" или "1":

63 - признак использования остаточных интерполированных отсчетов,

64 - код максимальной скорости роста,

65 - код коэффициента запаса по скорости роста,

66 - относительный уровень нуля элемента сигнала,

67 - коэффициент амплитудной поправки,

68 - код энергии шума,

69 - код коэффициента запаса по энергии шума.

На фиг. 1 - фиг.12 тонкими линиями представлены одиночные связи для передачи одиночных сигналов, толстыми линиями - групповые связи для передачи групп сигналов.

Для упрощения описания далее рассматривается обработка одномерного сигнала.

В исходном состоянии всех вариантов устройства на их информационном входе 46 сигнал отсутствует (действует сигнал, равный нулю), устройство обрабатывает нулевой сигнал, формируя нулевой сигнал во всех информационных сечениях и на своем выходе 47, то есть устройство находится в состоянии динамической готовности к обработке сигнала.

Первый вариант устройства для обработки сигналов работает следующим образом.

С поступлением сигнала на вход 46 устройства ЧФ 1 преобразовывает его, ограничивая спектр соответственно своей граничной частоте νo. С выхода ЧФ 1 сигнал с ограниченным спектром поступает на вход дискретизатора 2, который подвергает его дискретизации, например, с частотой 2•νo и квантованию, например, равномерным двоичным 12-разрядным кодом. С выхода дискретизатора 2 двоичные коды отсчетов сигнала поступают на вход блока 3 редукции к совершенному устройству, который интерполирует полученные отсчеты сигнала, определяет по интерполированным отсчетам параметры элементов входного для устройства сигнала и синтезирует описание (в частности, при необходимости вычисляет отсчеты) этого сигнала посредством накопительного суммирования заранее запасенных или вычисляемых отсчетов элементов входного сигнала при одновременном последовательном (накопительном) вычитании из интерполированных отсчетов отсчетов выходных реакций ЧФ 1 на эти элементы входного сигнала с повторением этих (описанных) действий до достижения таким образом уменьшаемыми интерполированными отсчетами заранее заданных или динамично определяемых характеристик и тем самым выполняет совершенное восстановление сигнала вплоть до предельно разрешаемых и с предельно малой амплитудой его элементов. С выхода блока 3 редукции к совершенному устройству сформированный таким образом сигнал поступает на выход 47 устройства.

Второй вариант устройства для обработки сигналов работает следующим образом.

С поступлением сигнала на вход 46 устройства ЧФ 1 и дискретизатор 2 вышеописанным образом формируют на своем выходе коды отсчетов сигнала, которые поступают на вход блока 4 подавления помех. Блок 4 подавления помех уменьшает уровень шума посредством модификации поступающих с выхода дискретизатора 2 отсчетов импульсных элементов с характеристиками, не соответствующими характеристикам возможных выходных реакций ЧФ 1, и выдает полученные отсчеты в блок 3 редукции к совершенному устройству, который вышеописанным для первого варианта устройства образом выполняет синтез описания, а при необходимости, вычисление отсчетов выходного сигнала и выдает их на выход 47 устройства.

Третий вариант устройства для обработки сигналов работает как первый или второй его варианты, но перед выдачей на выход 47 устройства совершенно восстановленной части входного сигнала блок 3 редукции к совершенному устройству прибавляет к ней преобразованные (например, сглаженные) остаточные (на момент завершения синтеза) интерполированные отсчеты.

Четвертый вариант устройства отличается от первого его варианта детализацией состава блока 3 редукции к совершенному устройству, который работает следующим образом.

Двоичные коды отсчетов сигнала с выхода дискретизатора 2 поступают на вход 48 блока 3 редукции к совершенному устройству, являющийся входом интерполятора 5, который производит вычисление отсчетов с меньшим шагом дискретизации и выдает их в узел 6 определения параметров элементов входного сигнала. Узел 6 определяет по интерполированным отсчетам параметры элементов входного для устройства сигнала (например, координаты, амплитуду, протяженность, форму), а также формирует выходные реакции ЧФ, эквивалентного ЧФ 1, на элементы сигнала, производит накопительное вычитание этих реакций из уменьшаемых интерполированных отсчетов, вырабатывает признак завершения синтеза сигнала и выдает результаты своей работы в синтезатор 7 описания входного сигнала, который формирует описание (в частности, при необходимости вычисляет отсчеты) этого сигнала посредством накопительного суммирования заранее запасенных или вычисляемых отсчетов элементов входного сигнала и выдает результат на свой выход, являющийся выходом 47 устройства. При этом в синтезаторе 7 описания выходного сигнала остаток уменьшаемых интерполированных отсчетов используется только при необходимости его добавления к синтезированной (совершенно восстановленной) части выходного сигнала.

Пятый вариант устройства характеризуется наличием и детализацией состава блока 4 подавления помех, который работает следующим образом.

Двоичные коды отсчетов сигнала с выхода дискретизатора 2 поступают на вход 49 блока 4 подавления помех, являющийся входом узла 8 оценки скорости роста, который вычисляет приращение каждого текущего отсчета сигнала по отношению к предыдущему и выдает его вместе с отсчетами сигнала в узел 9 нормализации. Узел 9 нормализации сопоставляет эти приращения с максимально допустимыми при данных характеристиках ЧФ 1 и выдает на свой выход, являющийся выходом 56 блока 4 подавления помех, либо неизмененные отсчеты сигнала, если соответствующие им приращения меньше максимально допустимых, либо отсчеты сигнала, приведенные в соответствие с характеристиками ЧФ 1, в противном случае и тем самым уменьшает уровень шума на входе блока 3 редукции к совершенному устройству.

Шестой вариант устройства характеризуется детализацией состава узла 6 определения параметров элементов сигнала, который работает следующим образом.

В начальном состоянии (определяемом, например, сигналом о включении питающего напряжения) коммутатор 10 находится в состоянии пропускания сигналов с первого своего входа. С поступлением интерполированных отсчетов с выхода интерполятора 5 на вход 50 узла 6 определения параметров элементов сигнала, являющийся первым входом коммутатора 10, эти отсчеты проходят через коммутатор 10 и поступают на вход определителя 11 параметров элементов сигнала и на второй вход (вход уменьшаемого) накопительного вычитателя 13. Определитель 11 параметров элементов сигнала определяет по интерполированным отсчетам характеристики (параметры) максимального по амплитуде элемента входного для устройства сигнала и выдает эти параметры на вход формирователя 12 выходной реакции ЧФ 1 на элемент сигнала и на выход 57 узла 6 определения параметров элементов сигнала. Формирователь 12 выходной реакции ЧФ на элемент сигнала определяет эту реакцию как свертку сигнального элемента с импульсной характеристикой ЧФ 1 и выдает ее (реакцию) на первый вход (вход вычитаемого) накопительного вычитателя 13. Накопительный вычитатель 13 вычисляет разность между интерполированными отсчетами и выходной реакцией ЧФ 1 на элемент сигнала и выдает отсчеты этой разности на второй вход коммутатора 10, в шину 58 из состава выходной шины 57 и на вход схемы 14 принятия решения о завершении синтеза. По завершении вычитания реакции ЧФ 1 на первый элемент сигнала (например, по сигналу с выхода накопительного вычитателя 13 в составе шины, соединяющей его выход со вторым входом коммутатора 10) коммутатор 10 переходит в состояние пропускания сигналов со второго своего входа. После этого на вход определителя 11 параметров элементов сигнала поступают уменьшаемые интерполированные отсчеты с выхода накопительного вычитателя 13 и узел 6 определения параметров элементов сигнала многократно повторяет вышеописанные свои действия, но над этими уменьшаемыми интерполированными отсчетами. При этом схема 14 принятия решения о завершении синтеза анализирует каждую итерацию уменьшаемых интерполированных отсчетов и по достижении ими заданных характеристик вырабатывает на своем выходе 59 сигнал завершения синтеза, поступающий на третий вход коммутатора 10 и в выходную шину 57. По этому сигналу коммутатор 10 переходит в состояние пропускания сигналов со своего первого входа, узел 6 определения параметров элементов сигнала готов к обработке следующей группы отсчетов со входа 50.

Дискретизатор 2 работает следующим образом.

Генератор 15 вырабатывает импульсы постоянной частоты, поступающие с его выхода в выходную шину 60 дискретизатора 2 и на вход формирователя 16 сетки частот. Формирователь 16 формирует из импульсов генератора 15 необходимые для работы устройства тактовые импульсы, поступающие в выходную шину 60 и на синхровход АЦП 17. АЦП 17 по переднему фронту каждого тактового импульса, поступающего на его синхровход, производит выборку (отсчет) значения сигнала, поступающего со входа 51 дискретизатора 2 на его сигнальный вход и преобразовывает это значение в линейный двоичный, например, 12-разрядный код, поступающий в виде данных с выхода АЦП 17 в выходную шину 60 дискретизатора 2. По шине 60 тактовые импульсы поступают на вход блока 3 редукции или блока 4 подавления помех. Необходимые тактовые импульсы транслируются этими блоками и всеми их составными частями и, благодаря этому, присутствуют во всех информационных шинах устройства на всех уровнях (чтобы не перегружать чертежи, на фиг.1 - фиг.12 трансляция тактовых импульсов не отражена).

Интерполятор 5 работает следующим образом.

Со входа 48 отсчеты сигнала, произведенные дискретизатором 2, поступают на вход интерполирующего ЧФ 18, с выхода которого интерполированные отсчеты с более высокой соответственно коэффициенту интерполяции частотой (например, вчетверо более высокой частотой) поступают на информационные входы ЦЛЗ 21 и 22, на синхровход одной из которых через коммутатор 20 из входной шины 48 приходят тактовые импульсы, по задним фронтам которых происходит запись интерполированных данных в соответствующую ЦЛЗ 21 или 22. На синхровход другой из этих ЦЛЗ 21 или 22 через коммутатор 20 из входной шины 48 поступают другие тактовые импульсы, по задним фронтам которых происходит считывание данных из этой ЦЛЗ 21 или 22 через коммутатор 23 на выход 61. Коммутаторы 20 и 23 управляются по своим управляющим входам сигналом с выхода триггера 19, который меняет свое состояние на противоположное по заднему фронту каждого специального импульса, приходящего из входной шины 48 с периодом, соответствующим емкости (одинаковой) ЦЛЗ 21 и 22. При сигнале логической "1" на выходе триггера 19 коммутатор 20 пропускает на синхровходы ЦЛЗ 21 и 22 импульсы соответственно первый и второй из вышеназванных, а коммутатор 23 передает на выход 61 данные с выхода ЦЛЗ 22. При сигнале логического "0" на выходе триггера 19 картина обратная: коммутатор 20 пропускает на синхровходы ЦЛЗ 21 и 22 импульсы соответственно второй и первый из вышеназванных, а коммутатор 23 передает на выход 61 данные с выхода ЦЛЗ 21. Это обеспечивает работу интерполятора 5 в условиях непрерывного потока данных на выходе дискретизатора 2.

Синтезатор 7 описания выходного сигнала работает следующим образом.

На вход 52 синтезатора 7 описания выходного сигнала поступают коды параметров элементов входного сигнала, сигнал окончания синтеза и остаточные после синтеза интерполированные отсчеты. Коды параметров элементов входного сигнала по мере их поступления записываются в узел 24 памяти и образуют описание входного для устройства сигнала вплоть до мельчайших разрешаемых устройством и с предельно малой амплитудой элементов этого сигнала, являющееся описанием и выходного сигнала устройства (отсюда его совершенство). По сигналу окончания синтеза, приходящему со входа 52 синтезатора 7 на управляющий вход оптимизатора 25 описания входного сигнала, оптимизатор 25 считывает из узла 24 памяти параметры элементов входного сигнала и преобразовывает их в более целесообразную форму, а именно, например, переводит описание сигнала из базирующегося на совокупности троек {Аi, mi, τi} параметров, в описание, базирующееся на совокупности двоек {δj j, nj} параметров, где Аi - амплитуда элементов сигнала, mi - координата элемента сигнала, τi - протяженность элемента сигнала, δj - величина перепада, nj - координата перепада; такое представление описания сигнала не только ускоряет вычисление отсчетов сигнала, но и уменьшает объем представляющих его данных. В случае заранее заданного (логической "1" на внутреннем входе 63 синтезатора 7 описания выходного сигнал) использования остаточных интерполированных отсчетов синтезатор 7 переводит параметры элементов входного сигнала, получаемые из узла 24 памяти в коды отсчетов и прибавляет к ним значения остаточных интерполированных отсчетов. По окончании описанных преобразований синтезатор 7 описания выходного сигнала выдает результаты своей работы на выход 47.

Узел 8 оценки скорости роста работает следующим образом.

С выхода дискретизатора 2 отсчеты сигнала поступают на вход 49 блока 4 подавления помех, являющийся входом узла 8 оценки скорости роста, и далее на информационный вход регистра 26, на вход уменьшаемого вычитателя 27 и в выходную шину 62. По задним фронтам тактовых импульсов, приходящих из шины 49 на синхровход регистра 26, отсчеты сигнала заносятся в этот регистр 26 и с его выхода поступают на вход вычитаемого вычитателя 27. Таким образом, вычитатель 27 вычисляет разности между текущим и предшествующим отсчетами и выдает модули этих разностей, являющиеся текущим значением скорости роста сигнала, на выход 62 узла 8 оценки скорости роста.

Узел 9 нормализации работает следующим образом.

Значения скорости роста сигнала, приходящие с выхода 62 узла 8 оценки скорости роста на вход 53 узла 9 нормализации, поступают на вход элемента 28 сравнения и на вход коммутатора 30. На второй вход элемента 28 сравнения и на вход умножителя 29 со внутреннего входа 64 узла 9 нормализации приходит код максимальной скорости роста сигнала, обусловленной фильтром ЧФ 1. Результат сравнения скорости роста сигнала с максимально возможной поступает с выхода элемента 28 сравнения на второй вход коммутатора 30, а произведение максимальной скорости роста и коэффициента запаса (меньшего единицы), код которого со внутреннего входа 65 узла 9 нормализации приходит на второй вход умножителя 29, поступает с выхода умножителя 29 на третий вход коммутатора 30. Коммутатор 30 при значении управляющего сигнала с выхода элемента 28 сравнения, соответствующем допустимой скорости роста, выдает на выход 56 узла 9 нормализации отсчеты сигнала со входа 53, в противном случае - значение, соответствующее допустимой скорости роста сигнала, поступающей на его третий вход, и тем самым нормализует сбойные отсчеты сигнала.

Определитель 11 параметров элемента сигнала работает следующим образом.

Со входа 54 интерполированные отсчеты поступают на входы сглаживателя 31 и вычислителя 32 текущего среднего. Сглаженные значения отсчетов с выхода сглаживателя 31 поступают на вход вычислителя 33 координат максимума и нуля (очередного элемента сигнала) и на вход уменьшаемого вычитателя 34, на вход вычитаемого которого поступает текущее среднее значение отсчетов с выхода вычислителя 32 текущего среднего. С выхода вычитателя 34 соответствующая разность поступает на информационные входы регистра 36 и элемента 38 сравнения. Координаты максимума и нуля с выхода их вычислителя 33 поступают на информационные входы регистров соответственно 35 и 39. Координата максимума в регистр 35 и разность, являющаяся амплитудой элемента сигнала, в регистр 36 заносятся по заднему фронту импульса, вырабатываемого вычислителем 33 координат максимума и нуля и приходящего на синхровходы регистров 35 и 36. Координата максимума с выхода регистра 35 поступает на вход вычитаемого вычитателя 41 и на выход 57 определителя 11 параметров элемента сигнала. Значение амплитуды элемента сигнала с выхода регистра 36 поступает на входы умножителей 37 и 40, на вторые входы которых со внутренних входов соответственно 66 и 67 поступают относительный уровень нуля элемента сигнала (меньший единицы) и коэффициент (больший единицы) амплитудной поправки. С выхода умножителя 37 уровень нуля элемента сигнала поступает на второй вход элемента 38 сравнения, а скорректированная амплитуда элемента сигнала с выхода умножителя 40 на выход 57 определителя 11 параметров элемента сигнала. Когда значение элемента сигнала после прохождения максимума достигает уровня нуля, элемент 38 сравнения вырабатывает сигнал, поступающий на синхровход регистра 39 и заносящий в него координату, являющуюся координатой нуля элемента сигнала, которая с выхода регистра 39 поступает на вход уменьшаемого вычитателя 41. Разность с выхода вычитателя 41, являющаяся кодом протяженности элемента сигнала, поступает на выход 57 определителя 11 параметров элемента сигнала. Таким образом, координата, амплитуда и протяженность как характеристики очередного прямоугольного элемента сигнала сформированы и выданы на выход 57 определителя 11 параметров элемента сигнала.

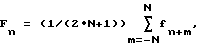

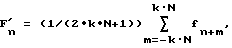

При этом сглаженные отсчеты на выходе сглаживателя 31

отсчеты текущего среднего на выходе вычислителя 32 текущего среднего

протяженность очередного элемента сигнала

τ = mo-mm,

амплитуда очередного элемента сигнала на выходе умножителя 40

A = β(F(mm)-F′(mm)),

где fn - интерполированные отсчеты на входе 54 определителя 11 параметров элемента сигнала,

k - коэффициент увеличения области текущего усреднения интерполированных отсчетов по сравнению с областью сглаживания,

m0 и mm - координаты нуля и максимума очередного элемента сигнала,

β - вышеупомянутый коэффициент (больший единицы) амплитудной поправки.

Схема 14 принятия решения о завершении синтеза работает следующим образом. Остаточные интерполированные отсчеты со входа 55 схемы 14 принятия решения о завершении синтеза поступают на вход формирователя 42 количественной характеристики, который вычисляет эту характеристику, например, в виде энергии остаточных интерполированных отсчетов и выдает ее код на информационный вход регистра 43, в который она заносится импульсом, вырабатываемым в формирователе 42 и поступающим на синхровход регистра 43. С выхода регистра 43 код энергии остаточных интерполированных отсчетов поступает на вход элемента 45 сравнения. Со внутренних входов 68 и 69 на входы умножителя 44 поступают соответственно код заранее заданной энергии остаточных интерполированных отсчетов как константы - уставки (которая при полном исчерпании возможностей совершенного восстановления входного сигнала равна энергии шума) и код коэффициента запаса (большего единицы), необходимого для надежного завершения синтеза. Полученное в умножителе 44 произведение с его выхода поступает на второй вход элемента 45 сравнения. По достижении энергией остаточных интерполированных отсчетов значения, равного или меньшего, чем значение уставки, действующей на втором входе элемента 45 сравнения, элемент 45 сравнения вырабатывает и выдает на выход 59 схемы 14 принятия решения сигнал о завершении синтеза.

Работоспособность каждого варианта устройства обеспечивается при адекватном задании на входах 68 и 69 схемы 14 принятия решения о завершении синтеза энергии шума остаточных интерполированных отсчетов в виде константы - уставки (то есть при возможности завершения синтеза входного сигнала) и при строгом соответствии вычитаемых из интерполированных отсчетов реакций ЧФ 1 тем элементам сигнала, которые прибавляются к синтезированному.

Сущность предлагаемого изобретения не меняется при перераспределении функций между составными частями устройства, при включении в его состав дополнительных средств, например, для повышения контраста малоразличимых элементов сигнала.

Сокращенное описание обработанного сигнала с использованием, например, вышеописанных пар параметров, в силу его компактности, является предпочтительной формой хранения синтезированного сигнала.

Для анализа данных, обработанных предлагаемым устройством, требуется поточечное восстановление сигнала.

Наибольший эффект предлагаемое устройство для обработки сигналов дает при его применении в системах с необходимостью хранения и/или передачи данных, где, помимо повышения разрешения, важно и уменьшение объема данных, представляющих обрабатываемые сигналы.

Коэффициент повышения разрешения (по сравнению с устройствами-аналогами), при котором обеспечивается анализ обработанных сигналов, имеет значения, не меньшие нескольких единиц. При этом коэффициент уменьшения объема данных (при одинаковом разрешении предлагаемого устройства и устройств-аналогов) достигает в случае одномерных сигналов значений 2,0-4,0 и возрастает по степенному закону соответственно размерности обрабатываемых сигналов.

Источники информации

1. Василенко Г.И. Теория восстановления сигналов. О редукции к идеальному прибору в физике и технике. - М.: Сов. радио, 1979, стр. 109-121.

2. Михайлов Б.А. К выбору частоты дискретизации, достаточной для восстановления формы непрерывного сигнала. - Электронная техника. Сер. 10. Микроэлектронные устройства, вып. 4 (46), 1984.

3. Michael L. Hilton, Bjorn D. Jawerth, Ayan Sengupta. Compressing Still and Moving Images with Wavelets. - Multimedia Systems, vol. 2, 3, April 18, 1994, p. 7-11.

4. Обработка изображений и цифровая фильтрация. Под редакцией Т.Хуанга. - М.: Мир, 1979, стр. 261.

5. Патент РФ 2141737, кл. H 04 N 7/12, 1998.

6. А.Папулис. Теория систем и преобразований в оптике. - М.: Мир, 1971, стр. 28.

7. Ф. Дж. Хэррис. Использование окон при гармоническом анализе методом дискретного преобразования Фурье. - ТИИЭР, т. 66, 1, 1978, стр. 82.

8. DESIGN - IN Reference Manual. - Analog Devices, Inc., 1994, стр. 2.18.

9. Триполитов С.В., Ермилов А.В. Микросхемы, диоды, транзисторы. Справочник. - М.: Машиностроение, 1994, стр. 205-207, 218-232, 310-313.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2008 |

|

RU2385489C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| Синхронный режекторный фильтр | 1986 |

|

SU1413699A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| Устройство передачи и приема сигналов | 1983 |

|

SU1312746A1 |

| Панорамный измеритель спектра | 1982 |

|

SU1187092A2 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1996 |

|

RU2104199C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

Изобретение относится к области обработки сигналов. Достигаемый технический результат - повышение разрешения элементов сигнала и чувствительности к его малоконтрастным элементам, повышение быстродействия и уменьшение сложности устройства. Устройство содержит частотный фильтр, дискретизатор и блок редукции к совершенному устройству. Варианты устройства содержат также блок подавления помех, интерполятор, узел определения параметров элементов входного сигнала и синтезатор описания сигнала, в составе блока подавления помех - узел оценки скорости роста сигнала, узел нормализации, в составе узла определения параметров элементов входного сигнала - коммутатор, определитель параметров следующего элемента сигнала, формирователь выходной реакции частотного фильтра на элемент сигнала, накопительный вычитатель, схему принятия решения о завершении синтеза. 4 с. и 2 з.п.ф-лы, 12 ил.

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| MICHAEL L | |||

| et al | |||

| Compressing Still and Moving Images with Wavelets | |||

| Multimedia Systems, vol | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Обработка изображений и цифровая фильтрация./ Под ред | |||

| Т | |||

| ХУАНГА: М.: Мир, 1979, с | |||

| Одновальный, снабженный дробителем, торфяной пресс | 1919 |

|

SU261A1 |

| ПАПУЛИС А | |||

| Теория систем и преобразований в оптике | |||

| - М.: Мир, 1971, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

Авторы

Даты

2002-12-20—Публикация

2000-12-15—Подача