Изобретение относится к вычислительной техникe и может быть использовано для построения систем передачи и переработки дискретной информации.

Известно матричное устройство умножения по а.с. СССР N 259479, М.кл. G 06 F 7/38, 1969, содержащее матрицу из КхК элементов И, соединенных выходами с входами К элементов ИЛИ, где K - модуль.

Недостатком устройства является его сложность. В случае K=7 оно содержит 91 элемент И, ИЛИ, НЕ. Кроме того, на его входы необходимо подавать параллельный унитарный позиционный код, а выходной сигнал вырабатывается в этом же коде. Это требует при работе в натуральном двоичном коде установки на входах устройства двух дешифраторов, а на выходе шифратора из (K+1)-го элемента ИЛИ. В результате суммарная сложность устройства составит 122 элемента И, ИЛИ, НЕ. Таким образом, недостатком устройства является его сложность.

Известно устройство для умножения по модулю семь по а.с. СССР N 1647561, М. кл. G 06 F 7/49, 1991, содержащее шесть групп элементов И, три элемента ИЛИ, три элемента И и три элемента ИЛИ-НЕ, причем каждая группа элементов И содержит по три элемента, вход первого разряда первого сомножителя устройства соединен с первыми входами первых элементов И каждой группы, вход второго разряда первого сомножителя устройства соединен с первыми входами вторых элементов И каждой группы, вход третьего разряда первого сомножителя устройства соединен с первыми входами третьих элементов И каждой группы, вход первого разряда второго сомножителя устройства соединен с вторыми входами второго и третьего элементов И первой группы, вторыми входами первого элемента И второй группы, первого и третьего элементов И третьей группы, второго элемента И четвертой группы, первого и второго элемента И пятой группы и третьего элемента И шестой группы, вход второго разряда второго сомножителя устройства соединен с вторым входом первого и третьим входом второго элемента И первой группы, вторым входом третьего элемента И второй группы, вторым входом второго и третьим входом третьего элементов И третьей группы, вторым входом первого элемента И четвертой группы, третьим входом первого и вторым входом третьего элементов И пятой группы и вторым входом второго элемента И шестой группы, вход третьего разряда второго сомножителя устройства соединен с третьими входами первого и третьего элементов И первой группы, вторым входом второго элемента И второй группы, третьими входами первого и второго элементов И третьей группы, вторым входом третьего элемента И четвертой группы, третьими входами второго и третьего элементов И пятой группы и вторым входом первого элемента И шестой группы, выходы первого, второго и третьего элементов И второй, четвертой и шестой группы соединены с первым, вторым и третьим входами соответственно первого, второго и третьего элементов ИЛИ, выходы которых соединены с первыми входами первого, второго и третьего элементов И, выходы которых соединены соответственно с выходами первого, второго и третьего разрядов результата устройства, а вторые входы - с выходами первого, второго и третьего элементов ИЛИ - НЕ, первый, второй и третий входы которых соединены с выходами первого, второго и третьего элементов И соответственно первой, третьей и пятой групп.

Недостатком устройства является его сложность, поскольку оно содержит 27 многовходовых элементов И, ИЛИ, ИЛИ-НЕ, а с учетом сложности самих логических элементов, т.е. в пересчете на двухвходовые элементы его сложность составит 42 элемента. Последний показатель более точно характеризует сложность устройства, поскольку учитывает число входов использованных логических элементов, т.е. их собственную сложность.

Наиболее близким по технической сущности и функциональным возможностям к заявляемому является устройство для умножения по модулю семь по а.с. СССР N 1647560, М. кл. G 06 F 7/49, 1991, содержащее шесть групп элементов И, три элемента ИЛИ, три элемента И, три элемента ИЛИ-НЕ, причем каждая группа содержит три элемента И, причем вход первого разряда первого сомножителя устройства соединен с первыми входами первых элементов И первой, второй и третьей групп, вход первого разряда второго сомножителя устройства соединен с первыми входами вторых элементов И первой и второй групп, вторым входом первого элемента И третьей группы, первыми входами первых элементов И четвертой, пятой и шестой групп, вход второго разряда первого сомножителя устройства соединен с первыми входами третьего элемента И первой группы и второго элемента И третьей группы и вторым входом второго элемента И второй группы, вход второго разряда второго сомножителя устройства соединен с вторым входом третьего элемента И первой группы, вторым входом первого элемента И второй группы, первым входом третьего элемента И третьей группы и первыми входами вторых элементов И четвертой, пятой и шестой групп, вход третьего разряда первого сомножителя устройства соединен с вторым входом второго элемента И первой группы, первым входом третьего элемента И второй группы, вторым входом третьего элемента И третьей группы, вход третьего разряда второго сомножителя устройства соединен с вторым входом первого элемента И первой группы, вторым входом третьего элемента И второй группы, вторым входом второго элемента И второй группы, вторым входом третьего элемента И третьей группы и первыми входами третьих элементов И четвертой, пятой и шестой групп, выходы первого, третьего и второго элементов И первой группы соединены с первым, вторым и третьим входами первого элемента ИЛИ и вторыми входами соответственно второго, первого и третьего элементов И шестой группы, выходы которых соединены с первым, вторым и третьим входами первого элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с выходом первого разряда результата устройства, а второй вход - с выходом второго элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами второго, третьего и первого элементов И третьей группы и вторыми входами второго, первого и третьего элемента И пятой группы, выходы которых соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ-НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с выходом второго разряда результата устройства, а второй вход - с выходом третьего элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами третьего, первого и второго элементов И второй группы и вторыми входами второго, первого и третьего элементов И четвертой группы, выходы которых соединены соответственно с первым, вторым и третьим входами третьего элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с выходом третьего разряда результата устройства, а второй вход - с выходом первого элемента ИЛИ.

Недостатком устройства является его сложность, поскольку оно содержит 27 многовходовых элементов И, ИЛИ, ИЛИ-НЕ, а в пересчете на двухвходовые элементы его сложность составит 33 элемента. Последний из показателей более точно отражает сложность известного устройства, поскольку учитывает сложность используемых в нем логических элементов.

В соответствии с этим задачей заявляемого изобретения является упрощение устройства умножения по модулю семь за счет уменьшения числа используемых логических элементов и сокращения числа их входов.

Указанная задача решается за счет того, что в устройстве для умножения по модулю семь, содержащее четыре элемента И и элемент ИЛИ, входы которого соединены с выходами второго и третьего элемента И, введены восемь сумматоров по модулю два и два элемента запрет, причем вход первого разряда первого сомножителя соединен с первым входом второго сумматора по модулю два, выход которого соединен с первыми входами третьего и четвертого элементов И, вход второго разряда первого сомножителя соединен с первым входом первого сумматора по модулю два, выход которого соединен с первыми входами первого и второго элементов И, вход первого разряда второго сомножителя соединен с первым входом четвертого сумматора по модулю два, выход которого соединен с вторыми входами второго и четвертого элементов И, вход второго разряда второго сомножителя соединен с первым входом третьего сумматора по модулю два, выход которого соединен с первыми входами первого и третьего элементов И, вторые входы первого и второго сумматоров по модулю два соединены с первым входом пятого сумматора по модулю два и входом третьего разряда первого сомножителя, вторые входы третьего и четвертого сумматоров по модулю два соединены с вторым входом пятого сумматора по модулю два и входом третьего разряда второго сомножителя, первый элемент запрет соединен прямым входом с выходом первого элемента И, инверсным входом - с выходом четвертого элемента И, а выходом - с первым входом шестого сумматора по модулю два, первый элемент ИЛИ соединен выходом с первым входом седьмого сумматора по модулю два, второй элемент запрет соединен прямым входом с выходом четвертого элемента И, инверсным входом - с выходом первого элемента И, а выходом - с первым входом восьмого сумматора по модулю два, вторые входы шестого, седьмого и восьмого сумматоров по модулю два соединены с выходом пятого сумматора по модулю два, а выходы - с выходами третьего, второго и первого разрядов результата соответственно.

Введение восьми сумматоров по модулю два и двух элементов запрет, а также новых связей между элементами обеспечивает получение устройства умножения по модулю семь, имеющего сложность в пересчете на двухвходовые элементы, равную 15, что в 2,2 раза меньше, чем у известного устройства по а.с. СССР N1647560, выбранного в качестве прототипа, тем самым получен технический результат, а именно упрощение устройства умножения по модулю семь как за счет сокращения числа использованных логических элементов, так и за счет сокращения числа их входов. Кроме того, предложенное устройство имеет более высокую надежность за счет меньшего объема оборудования.

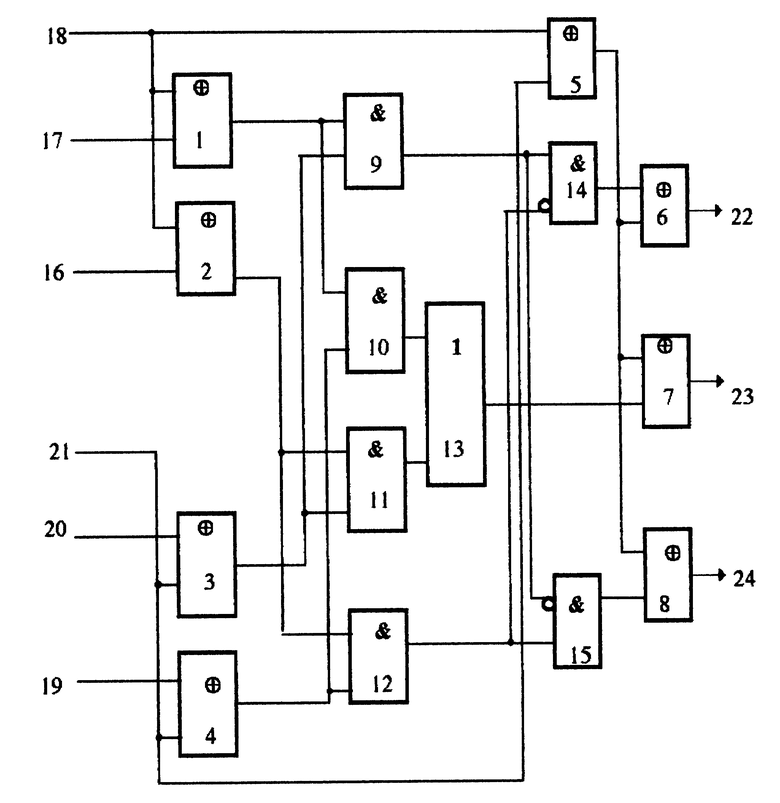

Сущность заявленного технического решения поясняется чертежом, на котором изображена схема устройства умножения по модулю семь.

Устройство умножения по модулю семь содержит сумматоры по модулю два 1-8, элементы И 9-12, элемент ИЛИ 13, элементы запрет 14 и 15.

Вход первого разряда 15 первого сомножителя соединен с первым входом сумматора 2 по модулю два, выход которого соединен с первыми входами элементов И 11 и 12, вход 17 второго разряда первого сомножителя соединен с первым входом сумматора 1 по модулю два, выход которого соединен с первыми входами элементов И 9 и 10, вторые входы сумматоров 1 и 2 по модулю два соединены с первым входом сумматора 5 по модулю два и входом 18 третьего разряда первого сомножителя, вход 19 первого разряда второго сомножителя соединен с первым входом сумматора 4 по модулю два, выход которого соединен с вторыми входами элементов И 10 и 12, вход 20 второго разряда второго сомножителя соединен с первым входом сумматора 3 по модулю два, выход которого соединен с первыми входами элементов И 9 и 11, вторые входы сумматоров 3 и 4 по модулю два соединены с вторым входом сумматора 5 по модулю два и входом 21 третьего разряда второго сомножителя, элемент запрет 14 соединен прямым входом с выходом элемента И 9, инверсным входом - с выходом элемента И 12, а выходом - с первым входом сумматора 6 по модулю два, элемент ИЛИ 13 соединен входами с выходами элементов И 10 и 11, а выходом - с первым входом сумматора 7 по модулю два, элемент запрет 15 соединен прямым входом с выходом элемента И 12, инверсным входом - с выходом элемента И 9, а выходом - с первым входом сумматора 8 по модулю два, вторые входы сумматора 6, 7 и 8 по модулю два соединены с выходом сумматора 5 по модулю два, а выходы - с выходами третьего 22, второго 23 и первого 24 разрядов результата соответственно.

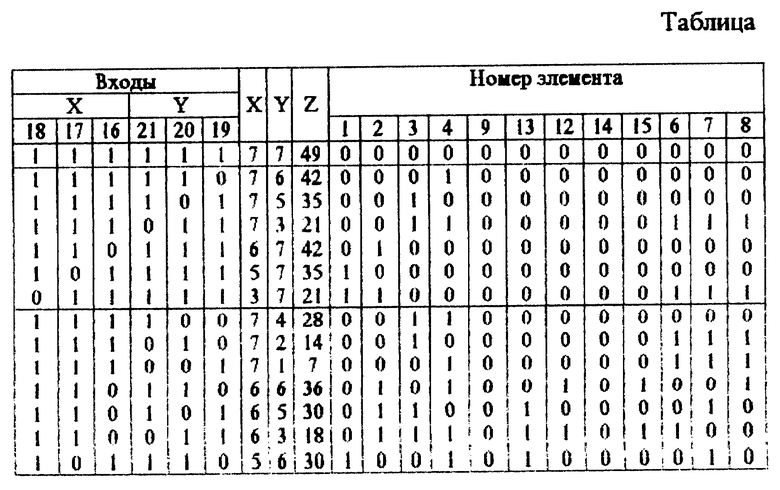

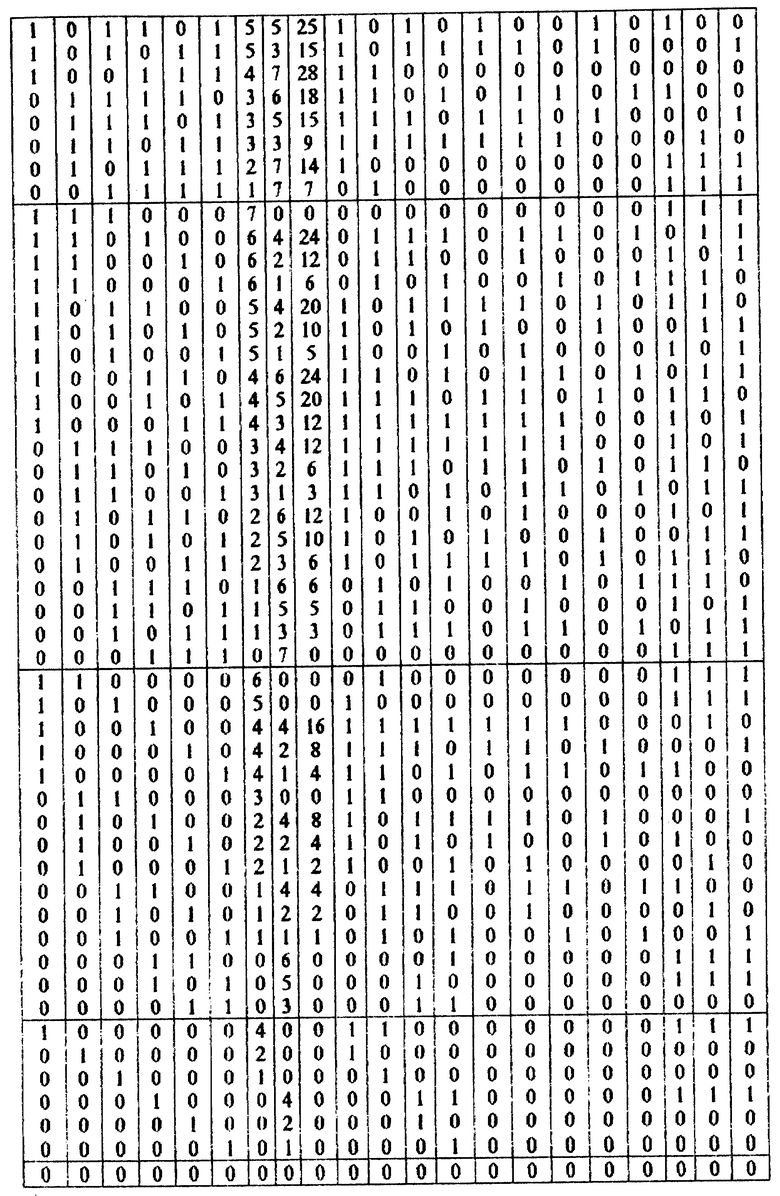

Функционирование устройства умножения описывается таблицей, в которой приведены выходные сигналы элементов схемы для всех разрешенных комбинаций значений сомножителей, а также для входных комбинаций, соответствующих значениям сомножителей, равным 7.

В таблице использованы следующие обозначения:

X - первый операнд;

Y - второй операнд;

Z = X • Y.

Из данных таблицы видно, что при подаче на входы устройства любых комбинаций сомножителей устройство формирует на выходах двоичных код числа (X•Y)mod7. При подаче на входы одного из сомножителей нулевого кода, а на входы второго из сомножителей кода числа, большего 3, на выходах устройства формируется код 111=7, что по модулю 7 соответствует нулю. Причем устройство дает правильный результат даже в том случае, когда сомножители принимают запрещенные значения 111.

Таким образом, предложенное устройство для умножения по модулю семь обеспечивает уменьшение сложности в 2,2 раза, т.е. достигается технический результат, заключающийся в сокращении количества логических элементов в устройстве и уменьшении числа их входов, что обеспечивает упрощение устройства и повышение его надежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ПО МОДУЛЮ СЕМЬ | 1999 |

|

RU2149442C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ПО МОДУЛЮ ПЯТЬ | 2000 |

|

RU2181904C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ПРОГРАММНО-УПРАВЛЯЕМОЙ СРЕДЫ | 1997 |

|

RU2132081C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ С ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1997 |

|

RU2132082C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1999 |

|

RU2156998C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

Изобретение относится к вычислительной техникe и может быть использовано для построения систем передачи и переработки дискретной информации. Технический результат заключается в упрощении устройства умножения по модулю семь и достигается за счет уменьшения числа используемых логических элементов и сокращения числа их входов. Устройство содержит четыре элемента И, элемент ИЛИ, восемь сумматоров по модулю два и два элемента запрет. 1 табл., 1 ил.

Устройство для умножения по модулю семь, содержащее четыре элемента И и элемент ИЛИ, входы которого соединены с выходами второго и третьего элементов И, отличающееся тем, что в него введены восемь сумматоров по модулю два и два элемента запрет, причем вход первого разряда первого сомножителя соединен с первым входом второго сумматора по модулю два, выход которого соединен с первыми входами третьего и четвертого элементов И, вход второго разряда первого сомножителя соединен с первым входом первого сумматора по модулю два, выход которого соединен с первыми входами первого и второго элементов И, вход первого разряда второго сомножителя соединен с первым входом четвертого сумматора по модулю два, выход которого соединен с вторыми входами второго и четвертого элементов И, вход второго разряда второго сомножителя соединен с первым входом третьего сумматора по модулю два, выход которого соединен с первыми входами первого и третьего элементов И, вторые входы первого и второго сумматоров по модулю два соединены с первым входом пятого сумматора по модулю два и входом третьего разряда первого сомножителя, вторые входы третьего и четвертого сумматоров по модулю два соединены с вторым входом пятого сумматора по модулю два и входом третьего разряда второго сомножителя, первый элемент запрет соединен прямым входом с выходом первого элемента И, инверсным входом - с выходом четвертого элемента И, а выходом - с первым входом шестого сумматора по модулю два, элемент ИЛИ соединен выходом с первым входом седьмого сумматора по модулю два, второй элемент запрет соединен прямым входом с выходом четвертого элемента И, инверсным входом - с выходом первого элемента И, а выходом - с первым входом восьмого сумматора по модулю два, вторые входы шестого, седьмого и восьмого сумматоров по модулю два соединены с выходом пятого сумматора по модулю два, а выходы - с выходами третьего, второго и первого разрядов результата соответственно.

| Устройство для умножения по модулю семь | 1989 |

|

SU1647560A1 |

| Устройство для умножения по модулю семь | 1989 |

|

SU1647561A1 |

| Устройство для умножения чисел по модулю | 1989 |

|

SU1667055A1 |

| Устройство для направленного бурения | 1981 |

|

SU1013624A1 |

| JP 05257649 A, 08.10.93. | |||

Авторы

Даты

1999-12-27—Публикация

1999-03-16—Подача