Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и экономичных цифровых устройств умножения чисел в прямых кодах.

Известно "Устройство для умножения в конечных полях" (патент №5064139/09), позволяющее выполнять умножения полиномов.

Известно также "Множительное устройство" (патент №93031693/09), позволяющее умножать двоичные числа.

Кроме того, известен "Ассоциативный умножитель чисел" (патент №95104047/09), позволяющий производить умножение произвольных чисел.

В качестве прототипа выбрано "Устройство для умножения чисел в позиционном коде" (патент №94001646/09), которое выполняет операцию умножения двоичных чисел в прямых кодах.

Задача заключается в следующем:

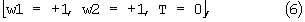

1) уменьшить аппаратные затраты устройства,

2) упростить алгоритм блока управления,

3) повысить скорость операции суммирования-вычитания чисел в прямых кодах,

4) повысить надежность работы умножителя.

В представленном умножителе происходит умножение двоичных чисел в прямых кодах. Предлагаемый умножитель позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы, а также значительно упростит алгоритм работы устройства.

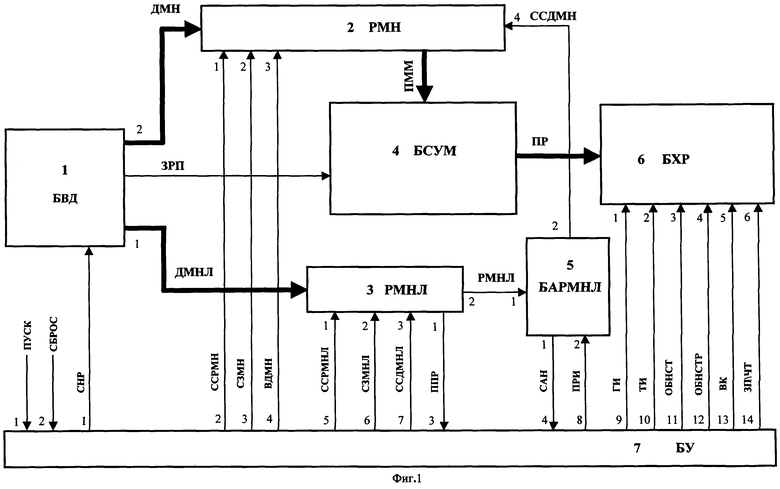

Решение задачи осуществляется тем, что умножитель на нейронах, содержащий регистр множимого и регистр множителя, отличающийся тем, что дополнительно введены: блок ввода данных, блок суммирования, блок анализа разряда множителя, блок хранения результата, блок управления, причем первый управляющий выход блока управления соединен с управляющим входом блока ввода данных, первый информационный выход которого соединен с информационным входом регистра множителя, первый управляющий выход которого соединен с третьим управляющим входом блока управления, со второго по четвертый управляющие выходы которого соединены соответственно с первым по третий управляющими входами регистра множимого, информационный выход которого соединен с информационным входом блока суммирования, информационный выход которого соединен с информационным входом блока хранения результата, с первого по шестой управляющие входы которого соединены соответственно с девятым по четырнадцатый управляющими выходами блока управления, с пятого по седьмой управляющие выходы которого соединены соответственно с первым по третий управляющими входами регистра множителя, второй управляющий выход которого соединен с первым управляющим входом блока анализа разряда множителя, первый управляющий выход которого соединен с четвертым управляющим входом блока управления, восьмой управляющий выход которого соединен со вторым управляющим входом блока анализа разряда множителя, второй управляющий выход которого соединен с четвертым управляющим входом регистра множимого, информационный вход которого соединен с информационным выходом блока ввода данных, управляющий выход блока ввода данных соединен с управляющим входом блока суммирования, первый и второй управляющие входы блока управления "ПУСК" и "СБРОС" являются внешними входами устройства.

Умножение, выполняемое методом накопления частичных произведений. Операция умножения в современных ЭВМ чаще всего выполняется суммированием сдвинутых на один или несколько разрядов частичных произведений, каждое из которых является результатом умножения множимого на соответствующий разряд (разряды) множителя. При точном умножении двух чисел количество значащих цифр произведения может в пределе достичь двойного количества значащих цифр сомножителей. Еще сложнее возникает ситуация при умножении нескольких чисел. Поэтому в произведении только в отдельных случаях используют двойное количество разрядов, обычно же ограничиваются количеством разрядов, которое имели сомножители. Наиболее просто операция умножения в ЭВМ выполняется в прямом коде. При этом на первом этапе определяется знак произведения путем сложения знаковых цифр сомножителей по модулю 2. Произведение вычисляется как сумма частичных произведений, из которых каждое получается последовательными сдвигами и умножением множимого на соответствующий разряд множителя. Произведение двух n-разрядных чисел является 2n-разрядным числом. Перемножение модулей сомножителей производится по правилам арифметики согласно двоичной таблице умножения. Результату присваивается полученный знак. Так как умножение производится в двоичной системе счисления, частные произведения либо равны 0 (при умножении на 0), либо самому сомножителю (при умножении на 1), сдвинутому на соответствующее количество разрядов.

БВД - блок ввода данных служит для ввода операндов и определения знака операции.

РМН - регистр множимого служит для хранения множимого при выполнении операции умножения.

РМНЛ - регистр множителя служит для хранения множителя при выполнении операции умножения и определения окончания операции умножения.

БСУМ - блок суммирования служит для выполнения операции сложения.

БАРМНЛ - блок анализа разряда множителя служит для генерации сигнала сдвига множимого.

БХР - блок хранения служит для хранения произведения. БУ - блок управления служит для управления устройством.

На фиг.1 изображена структурная схема умножителя на нейронах.

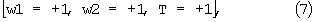

На фиг.2 представлен вариант технической реализации блока ввода данных.

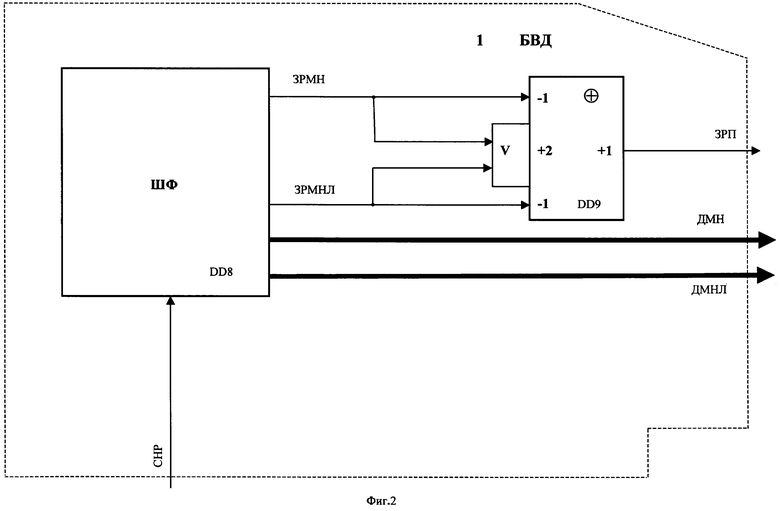

На фиг.3 представлен вариант технической реализации регистра множимого.

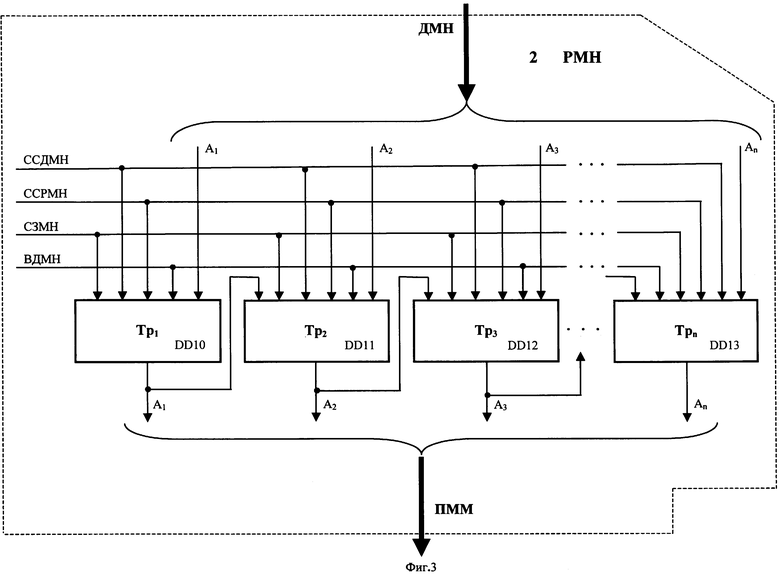

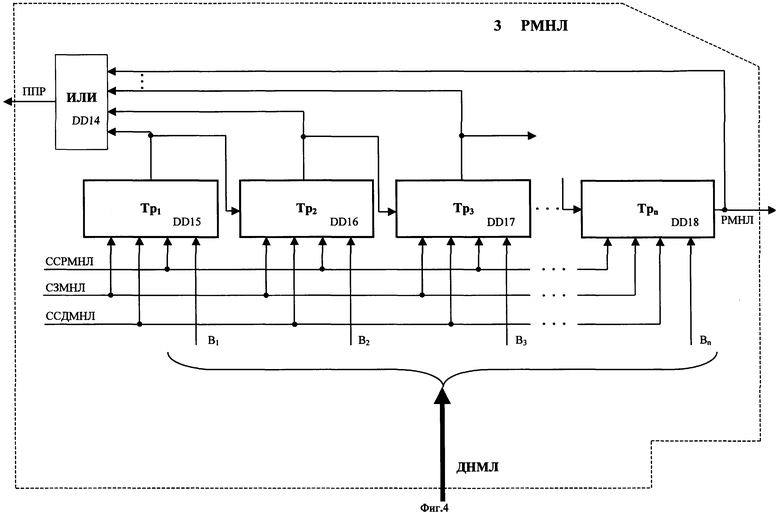

На фиг.4 представлен вариант технической реализации регистра множителя.

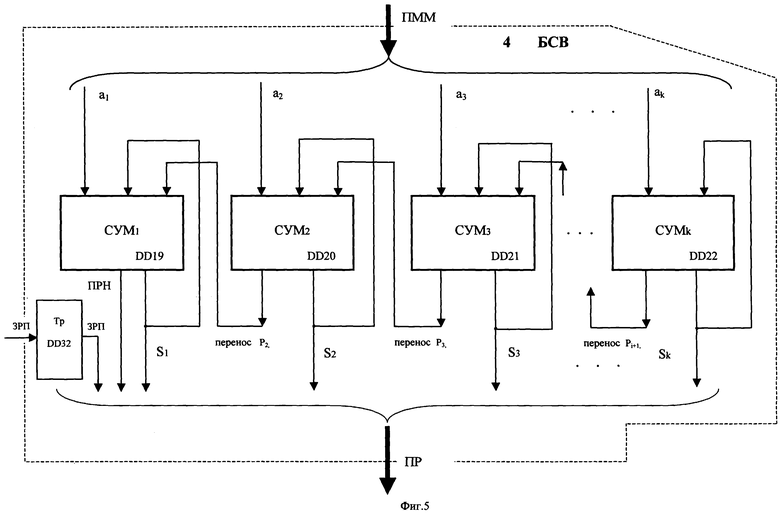

На фиг.5 представлен вариант технической реализации блока суммирования.

На фиг.6 изображена принципиальная схема одноразрядного сумматора на нейронах.

На фиг.7 представлен вариант технической реализации блока анализа разряда множителя.

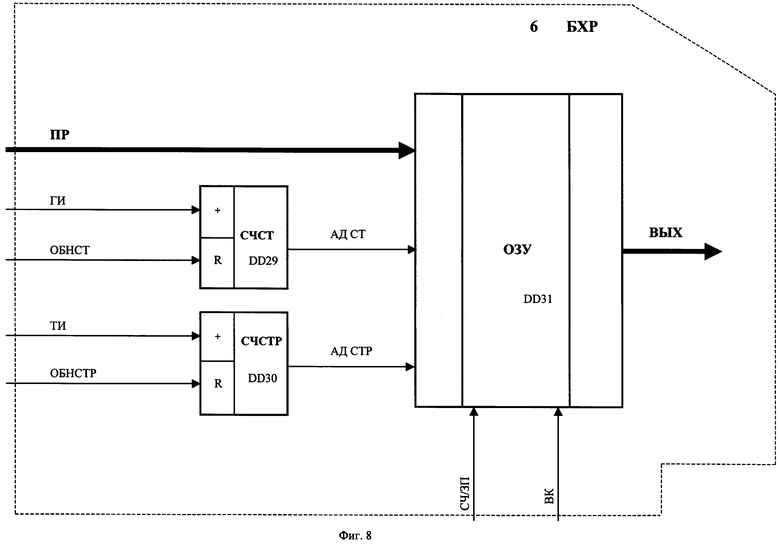

На фиг.8 представлен вариант технической реализации блока хранения.

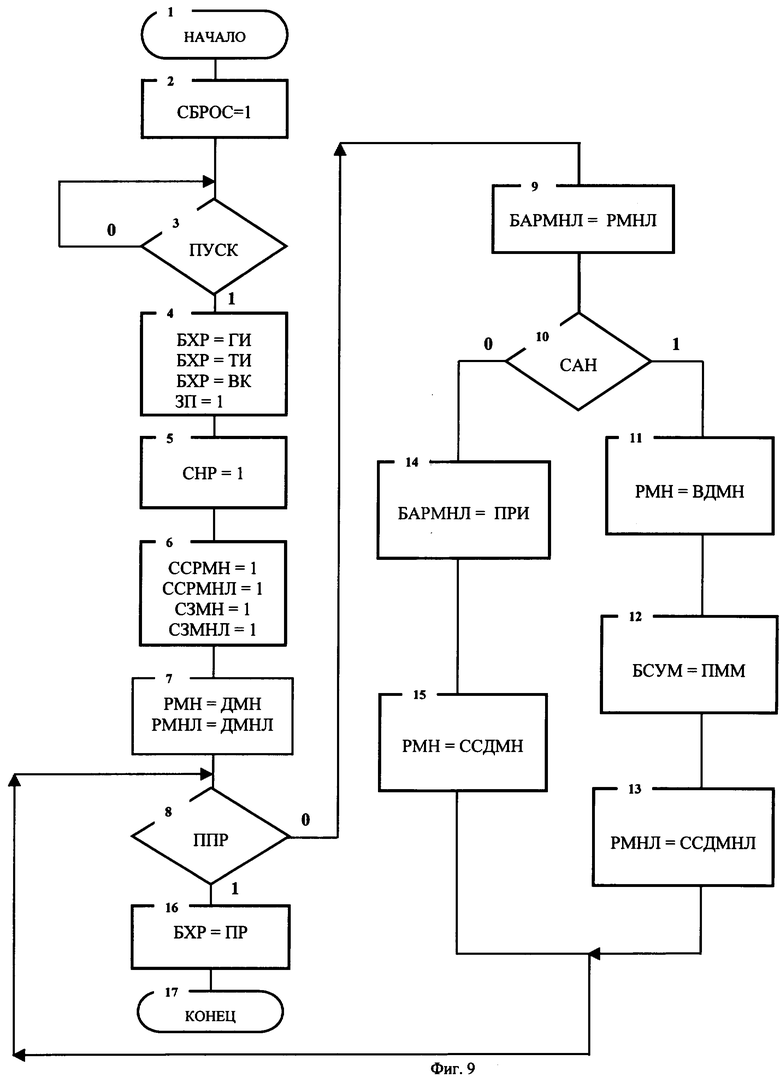

На фиг.9 содержательная граф-схема алгоритма работы блока управления умножителя на нейронах.

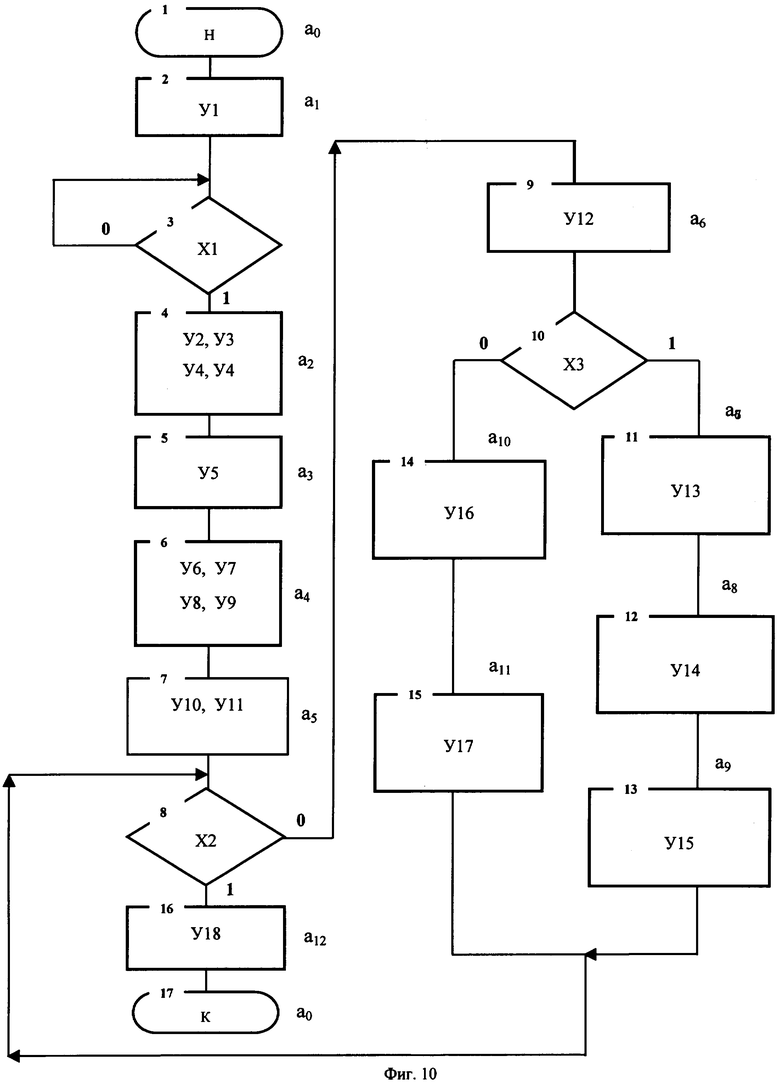

На фиг.10 - размеченная граф-схема алгоритма работы умножителя на нейронах.

Умножитель (фиг.1) содержит: блок ввода данных, регистр множимого, регистр множителя, блок суммирования, блок анализа разряда множителя, блок хранения, блок управления, пороговые элементы, нейроны.

Для описания алгоритма работы блока 7 управления используются следующие идентификаторы.

1. СНР - сигнал начало работы.

2. ССРМН - сигнал сброса регистра множимого.

3. СЗМН - сигнал записи множимого.

4. ВДМН - выдача данного множимого.

5. ССРМНЛ - сигнал сброса регистра множителя.

6. СЗМНЛ - сигнал записи множителя.

7. ССДМНЛ - сигнал сдвига множителя.

8. ППР - признак пустого регистра.

9. САН - сигнал анализа разряда множителя.

10. ПРИ - прямоугольные импульсы.

11. ГИ - генераторные импульсы.

12. ТИ - тактовые импульсы.

13. OБНСТР - сигнал обнуления строк ОЗУ.

14. OБНСТ - сигнал обнуления столбцов ОЗУ.

15. ВК - сигнал выбора кристалла.

16. ЗП/ЧТ - сигнал разрешения записи/чтения.

17. ДМН - данное множимого.

18. ДМНЛ - данное множителя.

19. ЗРП - знаковый разряд произведения.

20. ПММ - преобразованное множимое.

21. РМНЛ - разряд множителя.

22. ССДМН - сигнал сдвига множимого.

23. ПР - произведение.

24. СБРОС - сигнал сброса (обнуления) всех комбинационных блоков умножителя.

25. ПУСК - сигнал начало работы умножителя.

Работа алгоритма управления устройства.

Содержательная ГСА управления приведена на фиг.9 и отражает работу блока управления (фиг.1).

По команде "СБРОС=1" (блок 2) и сигналу "ПУСК" (блок 3) происходит установка в нуль всех элементов памяти устройства.

В блоке 4 алгоритма по командам: БХР=ГИ, БХР=ТИ, БХР=ВК, ЗП=1 на вход ОЗУ блока хранения результата поступают сигналы прямоугольных импульсов из блока управления, при этом происходит выбор кристалла, а также установка ОЗУ в режим записи.

В блоке 5 алгоритма по команде СНР=1 на вход блока ввода данных поступает разрешающий сигнал для работы шифратора.

В блоке 6 алгоритма по команде ССРМН=1 происходит сброс регистра множимого в нулевое состояние, по команде ССРМНЛ=1 происходит сброс регистра множителя в нулевое состояние. Команда СЗМН=1 разрешает запись множимого в регистр множимого. Команда СЗМНЛ=1 разрешает запись множителя в регистр множителя.

В блоке 7 по командам: РМН=ДМН, РМНЛ=ДНМЛ с помощью шифратора (клавиатуры) ШР (фиг.2) осуществляется загрузка в регистры множимого и множителя операндов.

В блоке 8 алгоритма происходит анализ содержимого регистра множителя. Это осуществляется с помощью сигнала ППР. Если ППP=1, значит, регистр множителя пуст и в этом случае происходит запись произведения в блок хранения по команде БХР=ПР блока 16 и умножитель заканчивает свою работу. Если ППР=0, то это означает, что регистр множителя не пуст, и по команде БАРМНЛ=РМНЛ блока 9 происходит подача разряда множителя в блок анализа разряда множителя.

В блоке 10 алгоритма происходит анализ разряда множителя сигнала САН. Если сигнал САН=1, тогда происходит переход к блоку 11 алгоритма. При этом по сигналу РМН=ВДМН происходит разрешение передачи множимого из регистра множимого в блок суммирования. По команде БСУМ=ПММ блока 12 происходит передача преобразованного множимого из регистра множимого в блок суммирования. По команде РМНЛ=ССДМНЛ блока 13 происходит сдвиг множителя в регистре множителя на 1 разряд вправо, после чего происходит переход к блоку 8 алгоритма.

Если сигнал САН=0, происходит переход к блоку 14 алгоритма, в котором по команде БАРМНЛ=ПРИ происходит подача прямоугольных импульсов в блок анализа разряда множителя.

В блоке 15 по команде РМН=ССДМН происходит сдвиг множимого в регистре множимого на один разряд вправо. После этого происходит переход алгоритма к блоку 8.

Блок 17 алгоритма является конечным блоком алгоритма.

Работа умножителя на нейронах заключается в следующем.

Внешние управляющие сигналы "Пуск" и "Сброс" поступают в блок 7 управления.

Блок 1 ввода данных БВД содержит шифратор (обычная стандартная клавиатура) ШФ DD8, сумматор по модулю два DD9 (фиг.2). Этот блок позволяет вводить двоичные числа (множимое и множитель). С выхода шифратора формируется двоичный код множимого и множителя со своими знаками: ДМН, ДМНЛ, ЗРМН, ЗРМНЛ. Знаковые разряды с выхода шифратора поступают на вход сумматора по модулю два. Сигнал ЗРП знаковый разряд произведения формируется на выходе элемента DD9. Сумматор по модулю два реализован на формальном нейроне ФН [2]. Выходной сигнал вычисляется по формуле [1]:

где w1, w2, w3 - коэффициенты усиления, а Т - пороговое напряжение.

Выходными сигналами блока 1 ввода данных являются двоичные коды множимого ДМН и множителя ДМНЛ, а также знаковый разряд произведения ЗРП.

Регистр множимого 2 РМН представляет собой набор D-триггеров DD10, DD11, DD12, DD13 (фиг.3). Это регистр предназначен для хранения разрядов множимого, а также для организации сдвига, разряды множимого сдвигаются на один разряд в сторону младшей части (вправо). Выходная информация D-триггера Tpi является входной для следующего D-триггера Tpi+1 (фиг.30), тем самым организован сдвиг информации вправо на один разряд. На вход регистра множимого поступают ДМН разряды множимого из блока 1 ввода данных, при этом старшие разряды записываются начиная с Tp1 и заканчиваются в Трn. Регистр множимого управляется из блока 7 управления посредством управляющих сигналов. По сигналу ССРМН сигнал сброса регистра множимого происходит сброс D-триггеров. По сигналу СЗМН сигнал записи множимого происходит запись разрядов множимого в регистр множимого. По сигналу ВДМН выдача множимого происходит считывание разрядов ПМН преобразованного множимого. По сигналу ССДМН сигнал сдвига множимого происходит сдвиг множимого на один разряд в сторону младшей части (вправо). На выходе блока формируются разряды ПМН преобразованного множимого.

Регистр множителя 3 РМНЛ представляет собой набор D-триггеров DD15, DD16, DD17, DD18 и логический элемент ИЛИ DD14 (фиг.4). Регистр множителя предназначен для хранения разрядов множителя, организации сдвига разрядов множителя на один разряд в сторону старшей части (вправо), с целью получения и анализа текущего старшего разряда множителя. Запись информации осуществляется следующем образом: старшие разряды множителя записываются в регистр в правую часть. Старший разряд заносится в Трn, младший в Тр1 (фиг.4). При каждом сдвиге вправо на один разряд происходит анализ регистра множителя на наличие разрядов множителя. Если есть хоть один разряд, равный единице, сигнал ППP признак пустого регистра равен единицу, иначе сигнал ППР принимает значение, равное нулю. Сигнал ППР поступает на вход блока 7 управления. На вход регистра множителя поступают ДМНЛ разряды множителя из блока 1 ввода данных. Регистр множителя управляется из блока 7 управления посредством управляющих сигналов. По сигналу ССРМНЛ сигнал сброса регистра множителя происходит сброс D-триггеров. По сигналу СЗМНЛ сигнал записи множителя происходит запись разрядов множителя в регистр множителя. По сигналу ССДМНЛ сигнал сдвига множителя происходит сдвиг множителя на один разряд в сторону старшей части (вправо). На выходе блока формируется сигнал РМНЛ текущий старший разряд множителя, поступающий на вход блока 5 анализа разряда множителя, а также сигнал ППР признак пустого регистра, поступающий на вход блока 7 управления.

Блок 4 суммирования БСУМ состоит из k-сумматоров на нейронах и организован на элементах: DD19, DD20, DD21, DD22. Знаковый разряд хранится в D-триггере Тр, реализованном на элементе DD32. Блок предназначен для выполнения операции суммирования, с целью получения частичных сумм на промежуточных шагах вычисления, а также разрядов произведения при окончании операции умножения и хранения знакового разряда произведения ЗРП (фиг.5). Входной информацией блока являются разряды множимого ПММ. Выходной информацией является сумма Si разрядов множимого и суммой, полученной на предыдущем этапе и перенос Pi+1 в старшие разряды. Выход каждого блока суммирования является его вторым входом, организована обратная связь, для того чтобы складывать промежуточную сумму с преобразованным множимым на следующем такте. На третий вход каждого блока сумматора поступает перенос из младших разрядов Pi. Каждый блок суммирования представляет собой одноразрядный сумматор, на входы которого поступают разряды преобразованного множимого, сумма чисел от предыдущего этапа сложения и перенос из младших разрядов. Выходом является полученная сумма Si и перенос Pi+1 в старший разряд. Произведение чисел ПР со своим знаком ЗРП записывается в оперативное запоминающее устройство ОЗУ блока хранения результата (фиг.1).

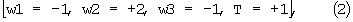

Одноразрядный сумматор блока состоит из пороговых элементов, на фиг.6 показана принципиальная схема одноразрядного сумматора, реализованного на пороговых элементах DD23 и DD24 (фиг.6). Элемент DD23 предназначен для получения разряда переноса в старший разряд. На вход элемента поступают aj j-тый разряд множимого, Рi перенос из младшего разряда с выхода предыдущего сумматора, Si-тый разряд суммы. На выходе блока формируется сигнал суммы Si и Pi+1 перенос в старший разряд. Работа данного элемента описывается с помощью формулы [3]:

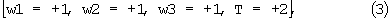

где w1, w2, w3 -коэффициенты усиления, а Т - пороговое напряжение. Элемент DD24 предназначен для получения разряда суммы. На вход элемента поступают aj j-тый разряд множимого, Рi-перенос в старший разряд с выхода предыдущего сумматора, Si i-тый разряд суммы, Pi+1-перенос в старший разряд. На выходе блока формируется сигнал Si+1 разряд суммы. Работа данного элемента описывается с помощью формулы [4]:

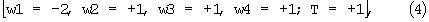

где w1, w2, w3, w4 - коэффициенты усиления, а Т - пороговое напряжение.

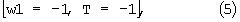

Блок 5 анализа разряда множителя БАРМНЛ состоит из пороговых элементов DD25, DD26, DD27, а также D-триггера DD28. Он предназначен для анализа текущего разряда множителя, начиная со старшего (фиг.7). На вход блока поступает РМНЛ текущий разряд множителя, а также сигнал из блока управления - ПРИ прямоугольные импульсы. На выходе формируется сигнал сдвига множимого ССДМН, а также сигнал анализа САН. Элемент DD25 выполняет функцию инвертора. Работа данного элемента описывается с помощью формулы [5]:

где w1 - коэффициент усиления, а Т - пороговое напряжение. Элемент DD26 выполняет логическую функцию дизъюнкции. Работа данного элемента описывается с помощью формулы [6]:

где w1, w2 -коэффициенты усиления, а Т -пороговое напряжение. Элемент DD27 выполняет логическую функцию конъюнкции. Работа данного элемента описывается с помощью формулы [7]:

где w1, w2 - коэффициенты усиления, а Т - пороговое напряжение. Работа блока заключается в следующем: входной сигнал - очередной разряд множителя РМНЛ поступает на входы пороговых элементов DD25 и DD26, реализующих логические функции НЕ и ИЛИ. Если разряд множителя равен единице РМНЛ=1, то эта единица через схему ИЛИ сформирует входной сигнал на выходе порогового элемента DD26. На втором входе схемы ИЛИ DD26 будет нуль, так как этот сигнал пройдет через инвертор НЕ порогового элемента DD25. Если разряд множителя равен нулю РМНЛ=0, то через инвертор НЕ DD25 на второй вход порогового элемента DD26 поступит также единица. На первый вход схемы ИЛИ DD26 поступит нуль. На выходе DD26 всегда будет единица. Комбинационная схема, состоящая из элементов DD25 и DD26, является преобразователем разряда множителя (нуль - единичная информация) в единицу. На первый вход конъюнктора DD27 поступит отпирающий сигнал, равный единице с выхода DD26. Прямоугольные импульсы из блока 7 управления поступят на второй вход конъюнктора DD27. На выходе схемы конъюнкции DD27 будут сформированы прямоугольные импульсы ССДМН, которые поступают на вход регистра множимого РМН и организуют сигнал сдвига вправо разрядов операнда. Логическая схема И, реализованная на пороговом элементе DD27, выполняет функцию электронного ключа, через который прямоугольные импульсы ПРИ из блока управления организуют операцию сдвига множимого на один разряд вправо. D-триггер всегда будет установлен в состояние, равное разряду множителя. Это необходимо для анализа поступившего разряда множителя и формирования сигнала САН с выхода триггера DD18. Сигнал анализа САН поступает на вход блока 7 управления. D-триггер DD28 выполняет функцию задержки во избежание асинхронного процесса в умножителе.

Блок 6 хранения результата БХР состоит из ОЗУ DD31, счетчика строк DD30, счетчика столбцов DD29 и служит для хранения двоичных разрядов результата при выполнении операции умножения. На вход блока поступают разряды произведения ПР. БХР управляется блоком 7 управления посредством управляющих сигналов. Сигнал ГИ генераторные импульсы поступают на вход счетчика столбцов DD29, для обеспечения записи произведения на новой строке. Сигнал ТИ тактовые импульсы поступают на вход счетчика строк DD30 для записи разрядов произведения в столбцы ОЗУ. Сигнал ОБНСТ обнуления столбцов поступает на вход счетчика столбцов DD29 и предназначен для обнуления данного счетчика. Сигнал ОБНСТР обнуления строк поступает на вход счетчика строк DD30 и предназначен для обнуления данного счетчика. Сигнал ВК выбор кристалла поступает на вход ОЗУ и предназначен для выбора кристалла ОЗУ. Сигнал ЗП/ЧТ записи/чтения устанавливает ОЗУ в режим записи/чтения.

Логические условия:

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Мкртчян С.О. Проектирование логических устройств ЭВМ на нейронных элементах. - М.: Энергия, 1977 г.

2. Дертоузос М. Пороговая логика. - М.: Мир, 1967 г.

3. Вавилов Е.И. и др. Синтез схем на пороговых элементах. - М.: Сов. радио. 1970 г.

4. Галушкин А.И. Синтез многослойных схем распознавания образов. М.: Энергия, 1974 г.

5. Позин И.В. Моделирование нейронных структур. - М.: Наука, 1970 г.

6. Патент N 94001646/09 (прототип).

7. Патент N 93031693/09 (аналог).

8. Патент N 506413 9/09 (аналог).

9. Патент N 95104047/09 (аналог).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ДЕШИФРАЦИИ ДАННЫХ | 2006 |

|

RU2319197C1 |

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и высокопроизводительных цифровых устройств умножения в прямых кодах. Техническим результатом является упрощение комбинационной схемы, а также упрощение алгоритма работы. Указанный результат достигается за счет того, что умножитель содержит блок ввода данных, регистр множимого, регистр множителя, блок суммирования, блок анализа разряда множителя, блок хранения, блок управления, пороговые элементы, нейроны. Операция умножения осуществляется анализом старших разрядов множителя со сдвигом множимого вправо. Комбинационные блоки обеспечивают параллельное, поразрядное получение разрядов произведения. 10 ил.

Умножитель на нейронах, содержащий регистр множимого и регистр множителя, отличающийся тем, что дополнительно введены: блок ввода данных, блок суммирования, блок анализа разряда множителя, блок хранения результата, блок управления, причем первый управляющий выход блока управления соединен с управляющим входом блока ввода данных, первый информационный выход которого соединен с информационным входом регистра множителя, первый управляющий выход которого соединен с третьим управляющим входом блока управления, со второго по четвертый управляющие выходы которого соединены соответственно с первым по третий управляющими входами регистра множимого, информационный выход которого соединен с информационным входом блока суммирования, информационный выход которого соединен с информационным входом блока хранения результата, с первого по шестой управляющие входы которого соединены соответственно с девятым по четырнадцатый управляющими выходами блока управления, с пятого по седьмой управляющие выходы которого соединены соответственно с первым по третий управляющими входами регистра множителя, второй управляющий выход которого соединен с первым управляющим входом блока анализа разряда множителя, первый управляющий выход которого соединен с четвертым управляющим входом блока управления, восьмой управляющий выход которого соединен со вторым управляющим входом блока анализа разряда множителя, второй управляющий выход которого соединен с четвертым управляющим входом регистра множимого, информационный вход которого соединен с информационным выходом блока ввода данных, управляющий выход блока ввода данных соединен с управляющим входом блока суммирования, первый и второй управляющие входы блока управления "ПУСК" и "СБРОС" являются внешними входами устройства.

| RU 94001646 A1, 20.03.1996 | |||

| RU 93031693 A1, 10.12.1996 | |||

| RU 95104047 A1, 20.01.1997 | |||

| МКРТЧЯН С | |||

| О | |||

| Проектирование логических устройств ЭВМ на нейронных элементах, Москва, Энергия, 1977. |

Авторы

Даты

2005-04-10—Публикация

2003-09-15—Подача