Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности, АСУТП, а также других систем, к которым предъявляются жесткие требования по надежности.

Известна распределенная система для программного управления, содержащая n•m модулей, где n - число строк, m - число столбцов, причем i-й модуль  системы содержит первый, второй, третий и четвертый блоки памяти, блок выбора, блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, мультиплексор выбора программ, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, элемент ИЛИ (патент РФ 2122229, G 05 В 19/18, G 06 F 9/28, опубл. 20.11.98, БИ 32).

системы содержит первый, второй, третий и четвертый блоки памяти, блок выбора, блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, мультиплексор выбора программ, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, элемент ИЛИ (патент РФ 2122229, G 05 В 19/18, G 06 F 9/28, опубл. 20.11.98, БИ 32).

Недостатком известной системы являются высокие требования к надежности блоков анализа, отвечающих за передачу сообщений между модулями, - блоки анализа должны функционировать при отказах модулей.

Наиболее близкой к предлагаемому устройству по технической сущности является распределенная система для программного управления технологическими процессами, содержащая nxm каналов (модулей), где n≥m, n - число модулей в строке матричной организации системы, а m - число строк, причем i-й модуль  системы содержит блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И (а.с. СССР 1605212, G 05 В 19/18, опубл. 07.11.90, БИ 41).

системы содержит блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И (а.с. СССР 1605212, G 05 В 19/18, опубл. 07.11.90, БИ 41).

Недостатком известной системы является узкая область применения, обусловленная отсутствием средств, обеспечивающих возможность ее реконфигурации и восстановления работоспособности системы при возникновении отказов отдельных модулей. Отказ по меньшей мере одного из модулей приводит к отказу системы в целом.

Технической задачей изобретения является расширение области применения распределенной системы за счет введения технических средств, обеспечивающих ее реконфигурацию и восстановление работоспособности при возникновении отказов отдельных модулей.

Техническая задача решается тем, что в распределенную систему для программного управления, содержащую n•m модулей, где n - число строк, m - число столбцов, причем i-й модуль  системы содержит первый блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, причем первый управляющий вход модуля соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен с входом первого блока памяти программ, синхронизирующий вход регистра команд соединен со вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторым информационным входом мультиплексора логических условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий модуля соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов запрета, выход которого соединен с первым информационным выходом модуля, второй управляющий вход модуля соединен с третьим входом блока синхронизации, информационный выход буферного запоминающего блока сообщений соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого и выход элемента И соединены с первым информационным входом блока анализа, управляющий выход которого соединен с первым управляющим входом буферного запоминающего блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход поля передачи управления регистра команд соединен с инверсным управляющим входом блока элементов запрета, управляющим входом блока элементов И и вторым входом элемента И, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса, вторым входом блока синхронизации и вторым управляющим входом буферного запоминающего блока сообщений, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, первый информационный вход модуля соединен со вторым информационным входом буферного запоминающего блока сообщений, второй информационный вход модуля соединен со вторым информационным входом блока анализа, второй информационный выход которого соединен со вторым информационным выходом модуля, третий информационный вход модуля соединен с третьим информационным входом блока анализа, третий информационный выход которого соединен с третьим информационным выходом модуля, дополнительно введены второй - четвертый блоки памяти программ, мультиплексор выбора программ, блок выбора алгоритма функционирования, причем входы второго - четвертого блоков памяти программ соединены с выходом регистра адреса, выходы первого - четвертого блоков памяти программ соединены соответственно с первым - четвертым информационными входами мультиплексора выбора программ, выход которого соединен с информационным входом регистра команд, четвертый выход блока выбора алгоритма функционирования соединен с первым управляющим входом мультиплексора выбора программ и с первым управляющим входом блока анализа, пятый выход блока выбора алгоритма функционирования подключен ко второму управляющему входу мультиплексора выбора программ и ко второму управляющему входу блока анализа, третий выход блока выбора алгоритма функционирования соединен с третьим управляющим выходом модуля, четвертый и пятый информационные выходы модуля соединены соответственно с четвертым и пятым информационными входами блока анализа, четвертый и пятый информационные выходы которого соединены соответственно с четвертым и пятым информационными выходами модуля, третий - седьмой управляющие входы модуля соединены соответственно с первым - пятым входами блока выбора алгоритма функционирования, первый и второй выходы блока выбора алгоритма функционирования соединены соответственно с первым и вторым управляющими выходами модуля, второй информационный выход j-го

системы содержит первый блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, причем первый управляющий вход модуля соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен с входом первого блока памяти программ, синхронизирующий вход регистра команд соединен со вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторым информационным входом мультиплексора логических условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий модуля соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов запрета, выход которого соединен с первым информационным выходом модуля, второй управляющий вход модуля соединен с третьим входом блока синхронизации, информационный выход буферного запоминающего блока сообщений соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого и выход элемента И соединены с первым информационным входом блока анализа, управляющий выход которого соединен с первым управляющим входом буферного запоминающего блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход поля передачи управления регистра команд соединен с инверсным управляющим входом блока элементов запрета, управляющим входом блока элементов И и вторым входом элемента И, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса, вторым входом блока синхронизации и вторым управляющим входом буферного запоминающего блока сообщений, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, первый информационный вход модуля соединен со вторым информационным входом буферного запоминающего блока сообщений, второй информационный вход модуля соединен со вторым информационным входом блока анализа, второй информационный выход которого соединен со вторым информационным выходом модуля, третий информационный вход модуля соединен с третьим информационным входом блока анализа, третий информационный выход которого соединен с третьим информационным выходом модуля, дополнительно введены второй - четвертый блоки памяти программ, мультиплексор выбора программ, блок выбора алгоритма функционирования, причем входы второго - четвертого блоков памяти программ соединены с выходом регистра адреса, выходы первого - четвертого блоков памяти программ соединены соответственно с первым - четвертым информационными входами мультиплексора выбора программ, выход которого соединен с информационным входом регистра команд, четвертый выход блока выбора алгоритма функционирования соединен с первым управляющим входом мультиплексора выбора программ и с первым управляющим входом блока анализа, пятый выход блока выбора алгоритма функционирования подключен ко второму управляющему входу мультиплексора выбора программ и ко второму управляющему входу блока анализа, третий выход блока выбора алгоритма функционирования соединен с третьим управляющим выходом модуля, четвертый и пятый информационные выходы модуля соединены соответственно с четвертым и пятым информационными входами блока анализа, четвертый и пятый информационные выходы которого соединены соответственно с четвертым и пятым информационными выходами модуля, третий - седьмой управляющие входы модуля соединены соответственно с первым - пятым входами блока выбора алгоритма функционирования, первый и второй выходы блока выбора алгоритма функционирования соединены соответственно с первым и вторым управляющими выходами модуля, второй информационный выход j-го  модуля k-гo

модуля k-гo  столбца соединен со вторым информационным входом (j+1)-го модуля k-гo столбца, третий информационный выход (j+1)-го модуля k-гo столбца соединен с третьим информационным входом j-го модуля k-гo столбца, четвертый информационный выход р-го

столбца соединен со вторым информационным входом (j+1)-го модуля k-гo столбца, третий информационный выход (j+1)-го модуля k-гo столбца соединен с третьим информационным входом j-го модуля k-гo столбца, четвертый информационный выход р-го  модуля q-й

модуля q-й  строки соединен с четвертым информационным входом (р+1)-го модуля q-й строки, пятый информационный выход (р+1)-го модуля q-й строки соединен с пятым информационным входом р-го модуля q-й строки, первый управляющий выход первого модуля k-го столбца соединен с третьим управляющим входом модулей k-го столбца с первого по n-й, первый управляющий выход (j+1)-го модуля k-го столбца соединен с пятым управляющим входом j-го модуля k-го столбца, второй управляющий выход р-го модуля q-й строки соединен с шестым управляющим входом (р+1)-го модуля q-й строки, второй управляющий выход р-го модуля s-й

строки соединен с четвертым информационным входом (р+1)-го модуля q-й строки, пятый информационный выход (р+1)-го модуля q-й строки соединен с пятым информационным входом р-го модуля q-й строки, первый управляющий выход первого модуля k-го столбца соединен с третьим управляющим входом модулей k-го столбца с первого по n-й, первый управляющий выход (j+1)-го модуля k-го столбца соединен с пятым управляющим входом j-го модуля k-го столбца, второй управляющий выход р-го модуля q-й строки соединен с шестым управляющим входом (р+1)-го модуля q-й строки, второй управляющий выход р-го модуля s-й  строки соединен с седьмым управляющим входом (р+1)-го модуля (s+1)-й строки, шестой управляющий вход модулей первого столбца с первого по n-й, пятый управляющий вход модулей n-й строки с первого по m-й, седьмой управляющий вход модулей первой строки с первого по m-й и первого столбца со второго по n-й предназначены для подачи сигнала логического нуля.

строки соединен с седьмым управляющим входом (р+1)-го модуля (s+1)-й строки, шестой управляющий вход модулей первого столбца с первого по n-й, пятый управляющий вход модулей n-й строки с первого по m-й, седьмой управляющий вход модулей первой строки с первого по m-й и первого столбца со второго по n-й предназначены для подачи сигнала логического нуля.

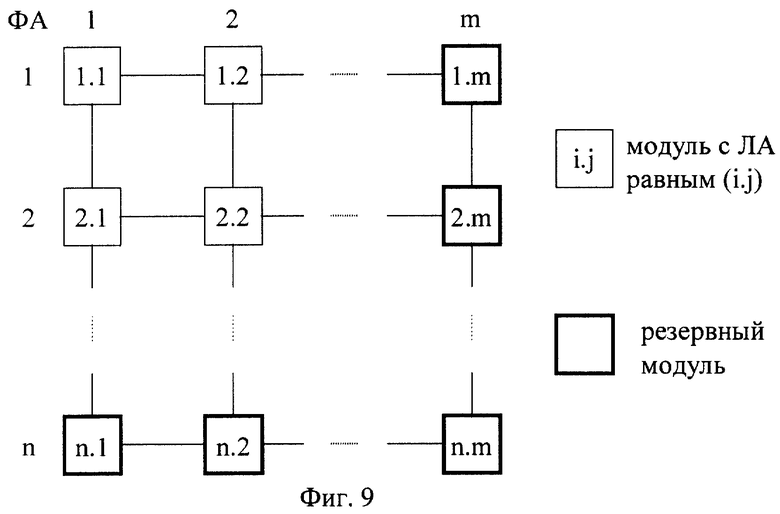

Сущность изобретения заключается в следующем. В распределенной системе из n•m модулей n-я строка и m-й столбец являются резервными.

Каждый модуль (i,j) (где  номер строки,

номер строки,  номер столбца матрицы, содержащих модуль) может выполнять как собственный алгоритм функционирования, так и алгоритм функционирования трех соседних модулей - верхнего (i-1, j)-го, левого (i,j-1)-го, и левого по диагонали (i-1,j-1)-го, в случае их отказов или изменения алгоритмов функционирования. Местоположение модуля (i,j) в матрице определятся его физическим адресом (ФА). Наряду с ФА для идентификации модулей системы используется так называемый логический адрес (ЛА). Модуль (i,j) имеет ЛА (i',j'), если он реализует алгоритм модуля с ФА(i', j'). При отсутствии отказов резервные модули не задействованы (они не имеют собственных алгоритмов функционирования), ФА и ЛА всех модулей совпадают. При возникновении отказов отдельных модулей распределенная система перестраивается.

номер столбца матрицы, содержащих модуль) может выполнять как собственный алгоритм функционирования, так и алгоритм функционирования трех соседних модулей - верхнего (i-1, j)-го, левого (i,j-1)-го, и левого по диагонали (i-1,j-1)-го, в случае их отказов или изменения алгоритмов функционирования. Местоположение модуля (i,j) в матрице определятся его физическим адресом (ФА). Наряду с ФА для идентификации модулей системы используется так называемый логический адрес (ЛА). Модуль (i,j) имеет ЛА (i',j'), если он реализует алгоритм модуля с ФА(i', j'). При отсутствии отказов резервные модули не задействованы (они не имеют собственных алгоритмов функционирования), ФА и ЛА всех модулей совпадают. При возникновении отказов отдельных модулей распределенная система перестраивается.

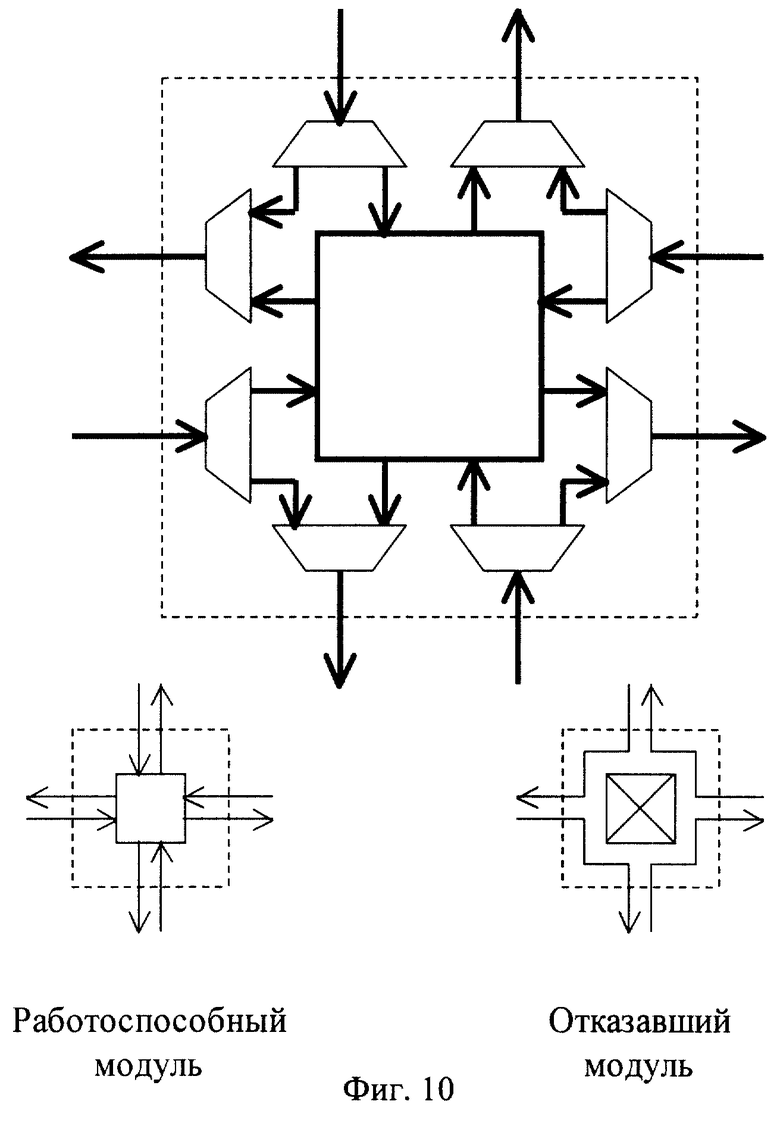

Аппаратурная перестройка системы заключается в отключении отказавших модулей путем перекоммутации их информационных входов и выходов. При этом нижний информационный вход отказавшего модуля коммутируется с его правым информационным выходом, левый информационный вход коммутируется с нижним информационным выходом, верхний информационный вход коммутируется с левым информационным выходом и правый информационный вход коммутируется с верхним информационным выходом.

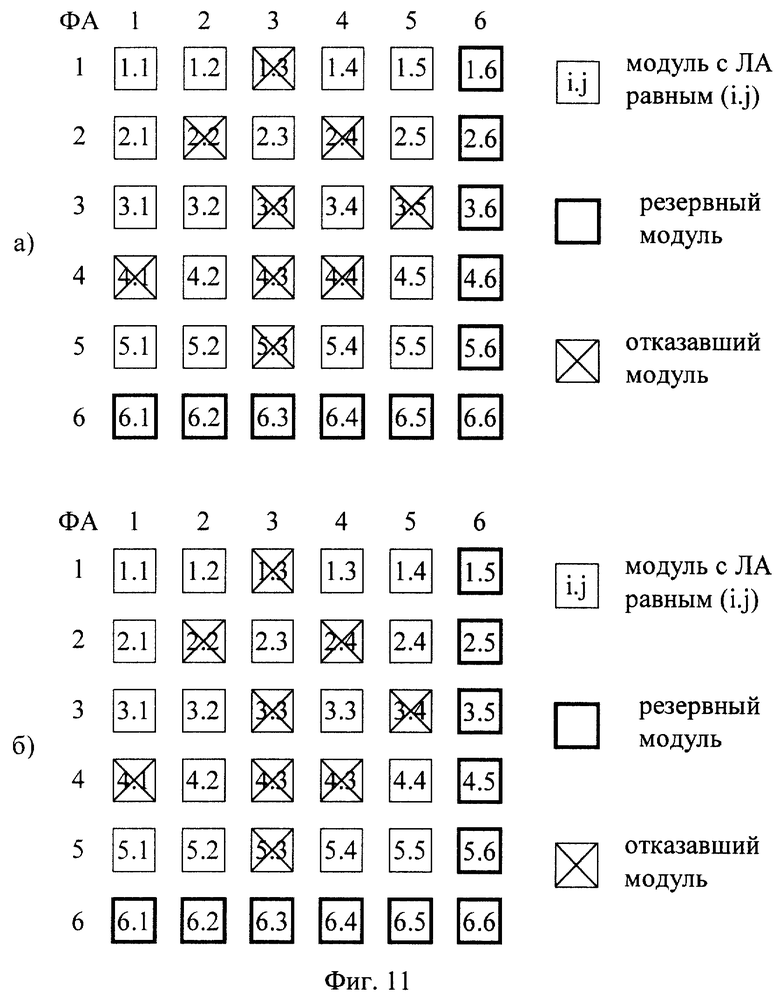

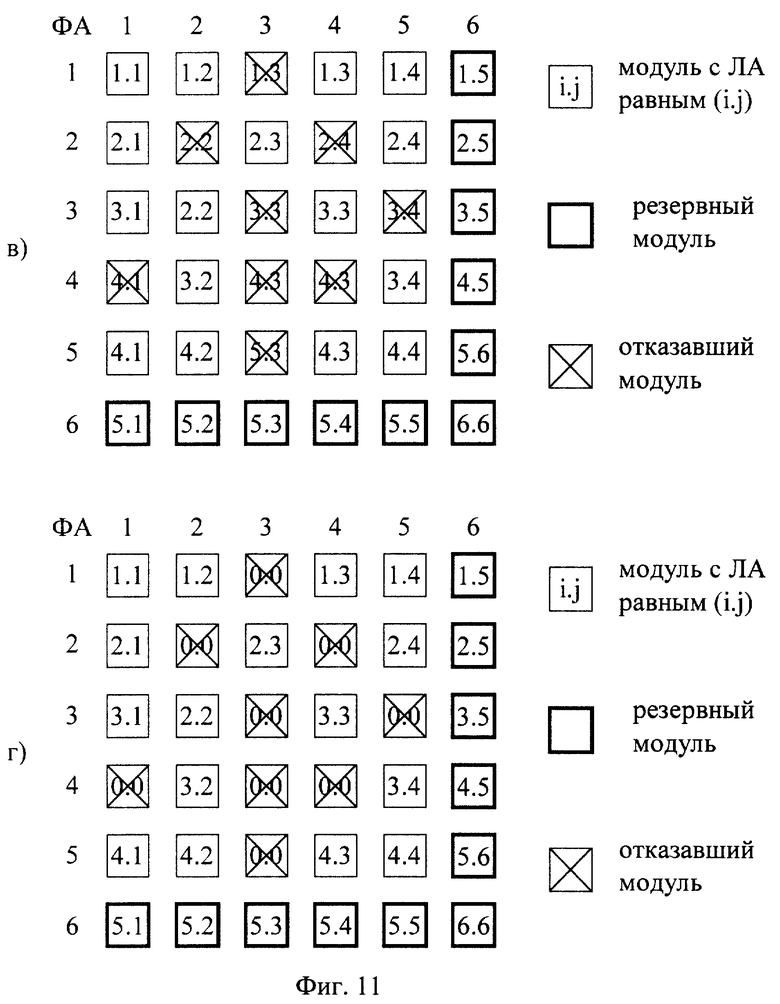

Программная перестройка системы осуществляется путем изменения алгоритмов функционирования модулей по следующим правилам:

- в каждом столбце самому нижнему отказавшему модулю присваивается статус "вертикальный отказ", а всем остальным отказавшим модулям - "горизонтальный отказ";

- если в любой строке имеется более одного модуля со статусом "горизонтальный отказ", то фиксируется фатальный отказ (ФО) распределенной системы - перестройка невозможна;

- в каждом столбце всем модулям ниже модуля со статусом "вертикальный отказ" (в том числе и резервным) присваивается статус "вертикальная перестройка";

- в каждой строке всем модулям правее модуля со статусом "горизонтальный отказ" (в том числе и резервным) присваивается статус "горизонтальная перестройка";

- ЛА модулей со статусом "горизонтальная перестройка" приобретают значение ФА модулей, стоящих от них слева;

- ЛА модулей со статусом "вертикальная перестройка", приобретают значение ФА модулей, стоящих от них сверху;

- ЛА всех отказавших модулей полагается нулевым.

Показанные выше шаги последовательного выполнения перестройки на самом деле выполняются параллельно при помощи комбинационных схем.

После перестройки, если модуль (i,j) не отказал, то он может выполнять собственный алгоритм, либо алгоритм одного из трех соседей: верхнего (i-1, j)-го, верхнего по диагонали (i-1,j-1)-го или левого (i,j-1)-го. Если алгоритм модуля (i,j) не выполняется им самим, то он выполняется одним из его трех соседей: правым (i,j+1)-м, правым по диагонали (i+1,j+1)-м или нижним (i+1,j)-м.

При возникновении новых отказов перестройка распределенной системы осуществляется заново, и так до тех пор, пока не произойдет фатальный отказ распределенной системы.

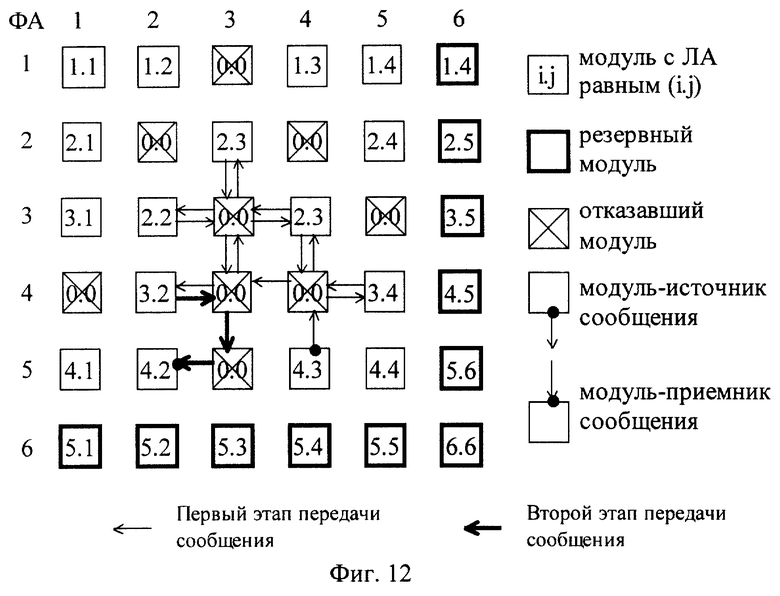

Взаимодействие модулей распределенной системы осуществляется путем обмена сообщениями. Сообщения между модулями передаются по четырем направлениям и содержат адрес программы, которую должен выполнить модуль-приемник, ФА модуля-приемника и направление выдачи сообщения.

При отсутствии в распределенной системе отказов сообщение последовательно передается от модуля-источника в модуль с ФА, равным адресу в сообщении (АС). Этот модуль будет являться модулем-приемником. Передача сообщения сначала осуществляется по столбцу (по вертикали). В ходе передачи каждый транзитный модуль сравнивает свой ЛА с АС. Если они равны, то данный модуль является модулем-приемником и сообщение передано. Иначе, модуль сравнивает вертикальную составляющую своего ФА (т.е. номер соответствующего ему столбца) с вертикальной составляющей АС. Если они не равны, он передает сообщение в соседний по вертикали модуль в сторону уменьшения разницы между вертикальными составляющими адресов. При совпадении вертикальных составляющих АС и ФА модуля направление передачи сообщения меняется на горизонтальное и сообщение аналогичным образом (путем сравнения горизонтальных составляющих ФА модулей и АС) передается по горизонтали в модуль-приемник.

При наличии в распределенной системе отказавших модулей сообщение должно быть передано в модуль с ЛА, равным АС. Для сообщения с АС=(i,j) таким модулем может являться модуль (i,j) или (i,j+1), или (i+1,j+1), или(i+1,j).

Передача сообщений в системе с отказавшими модулями осуществляется в два этапа. На первом этапе сообщение передается в модуль с ФА=AC=(i,j) аналогично передаче сообщений в системе без отказавших модулей - сначала по вертикали, затем по горизонтали. При передаче сообщения через отказавший модуль происходит изменение направления его выдачи, которое фиксируется следующим работоспособным модулем как несоответствие направления приема сообщения и направления выдачи в формате сообщения, и позволяет скорректировать дальнейшую его выдачу с учетом расположения отказавших модулей.

При приеме сообщения (i,j)-m, (i,j+1)-м, (i+1,j+1)-м или (i+1,j)-м модулем осуществляется второй этап передачи сообщения, на котором сообщение циклически передается из (i,j)-гo модуля в (i,j+1)-й, из (i,j+1)-го в (i+1, j+1)-й, из (i+1,j+1)-го в (i+1,j)-й и из (i+1,j)-го в (i,j)-й до тех пор пока ЛА одного из этих модулей не совпадет с АС.

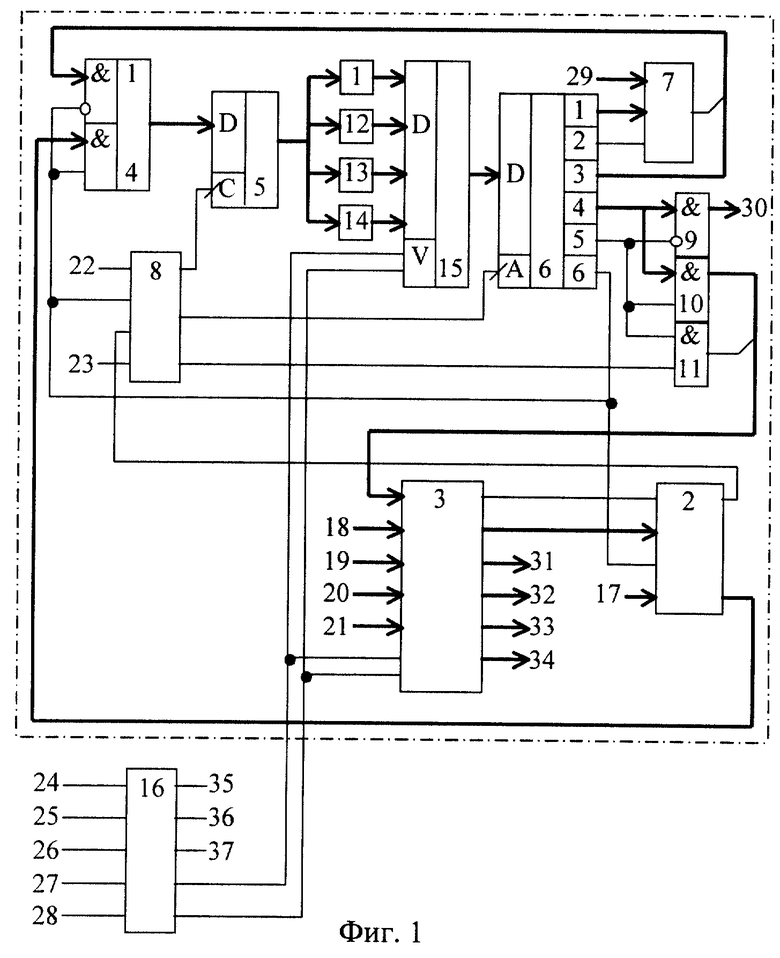

Дополнительные (со второго по четвертый) блоки памяти используются для хранения копий программ (микропрограмм) соседних модулей.

Введение блока выбора алгоритма функционирования и мультиплексора выбора программ необходимо для изменения алгоритма функционирования модуля при отказе или реконфигурации соседних модулей.

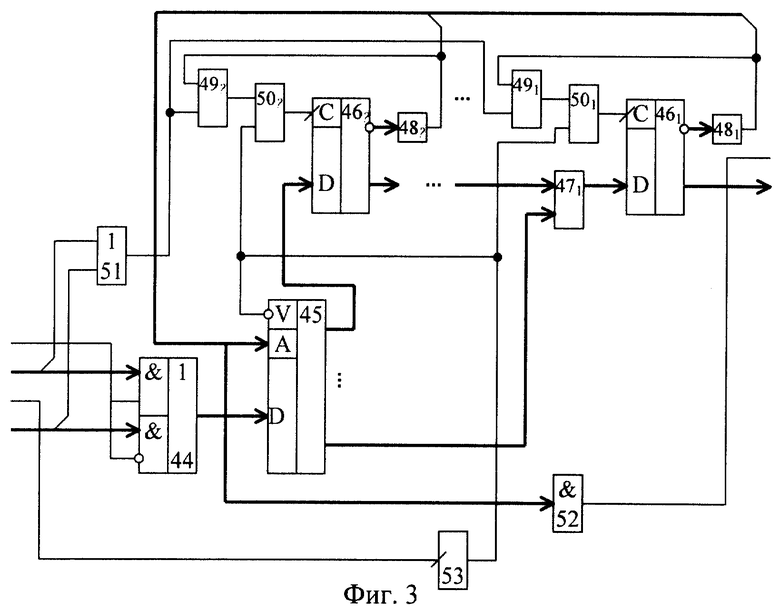

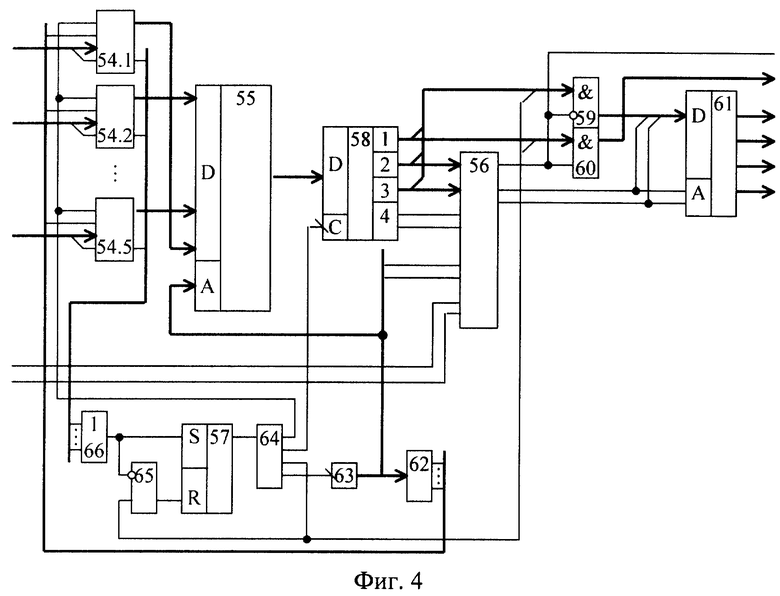

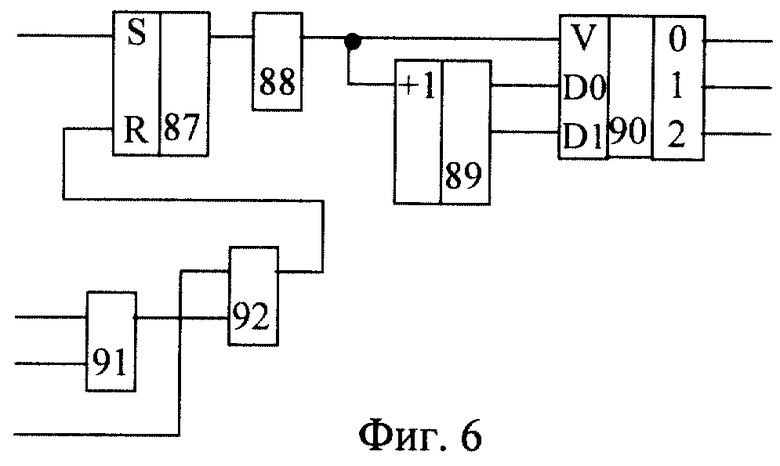

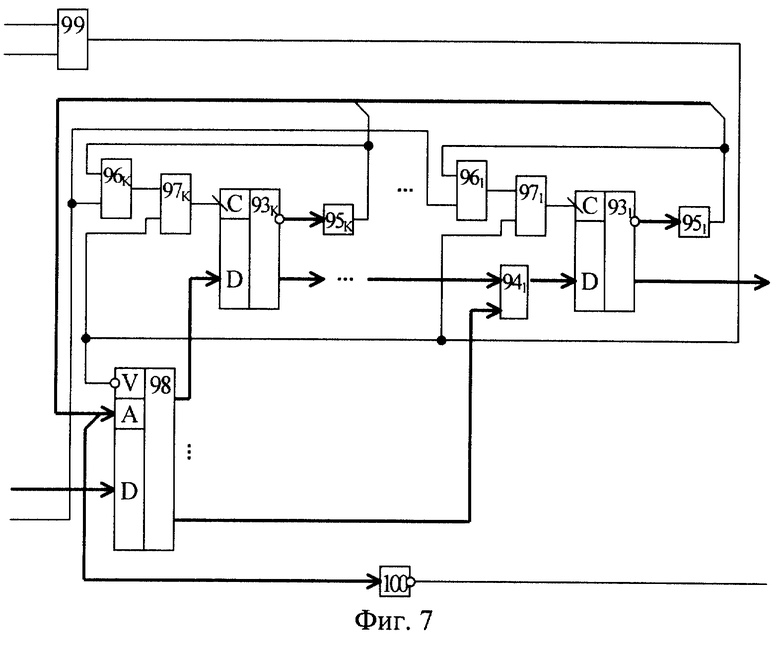

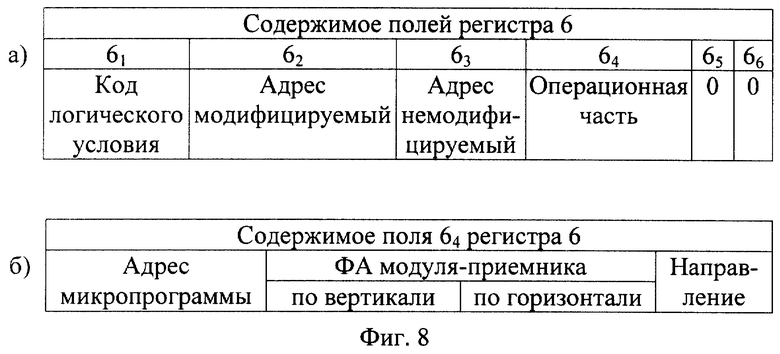

Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема i-го  модуля распределенной системы для программного управления; на фиг.2 - функциональная схема блока выбора алгоритма функционирования; на фиг. 3 - функциональная схема буферного запоминающего блока сообщений; на фиг.4 - функциональная схема блока анализа; на фиг.5 - функциональная схема блока выбора направления передачи информации; на фиг.6 - функциональная схема блока синхронизации; на фиг.7 - функциональная схема блока памяти сообщений; на фиг.8 - формат команды обработки (а) и формат операционной части команды обмена (б); на фиг.9 - структурная схема распределенной системы; на фиг.10 - структурная схема системы коммутаторов модуля; на фиг.11 - процесс пошагового выполнения перестройки распределенной системы; на фиг.12 - процесс передачи сообщения.

модуля распределенной системы для программного управления; на фиг.2 - функциональная схема блока выбора алгоритма функционирования; на фиг. 3 - функциональная схема буферного запоминающего блока сообщений; на фиг.4 - функциональная схема блока анализа; на фиг.5 - функциональная схема блока выбора направления передачи информации; на фиг.6 - функциональная схема блока синхронизации; на фиг.7 - функциональная схема блока памяти сообщений; на фиг.8 - формат команды обработки (а) и формат операционной части команды обмена (б); на фиг.9 - структурная схема распределенной системы; на фиг.10 - структурная схема системы коммутаторов модуля; на фиг.11 - процесс пошагового выполнения перестройки распределенной системы; на фиг.12 - процесс передачи сообщения.

i-й Модуль распределенной системы для программного управления (фиг.1) содержит первый 1, второй 12, третий 13 и четвертый 14 блоки памяти программ, блок 16 выбора алгоритма функционирования, буферный запоминающий блок 2 сообщений, блок 3 анализа, коммутатор 4 адреса, регистр 5 адреса, регистр 6 команд, мультиплексор 7 логических условий, мультиплексор 15 выбора программ, блок 8 синхронизации, блок 9 элементов запрета, блок 10 элементов И, элемент И 11, первый 17, второй 18, третий 19, четвертый 20 и пятый 21 информационные входы, первый 22, второй 23, третий 24, четвертый 25, пятый 26, шестой 27 и седьмой 28 управляющие входы, вход 29 логических условий, первый 30, второй 31, третий 32, четвертый 33 и пятый 34 информационные выходы, первый 35, второй 36 и третий 37 управляющие выходы, причем первый управляющий вход 22 модуля соединен с первым входом блока 8 синхронизации, первый выход которого соединен с синхронизирующим входом регистра 5 адреса, выход которого соединен со входами первого 1, второго 12, третьего 13 и четвертого 14 блоков памяти программ, синхронизирующий вход регистра 6 команд соединен со вторым выходом блока 8 синхронизации, выход 61 поля проверяемых логических условий регистра 6 команд соединен с первым информационным входом мультиплексора 7 логических условий, выход 62 модифицируемого разряда адреса регистра 6 команд соединен со вторым информационным входом мультиплексора 7 логических условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора 4 адреса, выход которого соединен с информационным входом регистра 5 адреса, вход 29 логических условий модуля соединен с управляющим входом мультиплексора 7 логических условий, выход 63 поля немодифицируемых разрядов адреса регистра 6 команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора 4 адреса, выход 64 операционного поля регистра 6 команд соединен с информационным входом блока 9 элементов запрета, выход которого соединен с первым информационным выходом 30 модуля, второй управляющий вход 23 модуля соединен с третьим входом блока 8 синхронизации, информационный выход буферного запоминающего блока 2 сообщений соединен со вторым информационным входом коммутатора 4 адреса, выход операционного поля 64 регистра 6 команд соединен с информационным входом блока 10 элементов И, выход которого и выход элемента И 11 соединены с первым информационным входом блока 3 анализа, первый управляющий выход которого соединен с первым управляющим входом буферного запоминающего блока 2 сообщений, управляющий выход которого соединен с четвертым входом блока 8 синхронизации, третий выход которого соединен с первым входом элемента И 11, выход поля 65 передачи управления регистра 6 команд соединен с инверсным управляющим входом блока 9 элементов запрета, управляющим входом блока 10 элементов И и вторым входом элемента И 11, информационный выход блока 3 анализа соединен с первым информационным входом буферного запоминающего блока 2 сообщений, первый информационный вход 17 модуля соединен со вторым информационным входом буферного запоминающего блока 2 сообщений, второй 18, третий 19, четвертый 20 и пятый 21 информационные входы модуля соединены соответственно со вторым - пятым информационными входами блока 3 анализа, второй - пятый информационные выходы которого соединены соответственно со вторым 31, третьим 32, четвертым 33 и пятым 34 информационными выходами модуля, выходы блоков 1, 12, 13 и 14 памяти программ соединены соответственно с первым - четвертым информационными входами мультиплексора 15 выбора программ, выход которого соединен с информационным входом регистра 6 команд, выход поля 66 конца программы регистра 6 команд соединен с прямым и инверсным управляющими входами коммутатора 4 адреса, вторым входом блока 8 синхронизации и вторым управляющим входом буферного запоминающего блока 2 сообщений, четвертый и пятый выходы блока 16 выбора алгоритма функционирования соединены с первым и вторым управляющими входами мультиплексора 15 выбора программ соответственно и с первым и вторым управляющими входами блока 3 анализа соответственно, третий выход блока 16 выбора алгоритма функционирования соединен с третьим управляющим выходом 37 модуля, третий 24, четвертый 25, пятый 26, шестой 27 и седьмой 28 управляющие входы модуля соединены соответственно с первым - пятым входами блока 16 выбора алгоритма функционирования, первый и второй выходы блока 16 выбора алгоритма функционирования соединены соответственно с первым 35 и вторым 36 управляющими выходами модуля, второй информационный выход 31 j-го  модуля k-гo

модуля k-гo  столбца соединен со вторым информационным входом 18 (j+1)-го модуля k-го столбца, третий информационный выход 32 (j+1)-го модуля k-гo столбца соединен с третьим информационным входом 19j-го модуля k-го столбца, четвертый информационный выход 33 р-го

столбца соединен со вторым информационным входом 18 (j+1)-го модуля k-го столбца, третий информационный выход 32 (j+1)-го модуля k-гo столбца соединен с третьим информационным входом 19j-го модуля k-го столбца, четвертый информационный выход 33 р-го  модуля q-й

модуля q-й строки соединен с четвертым информационным входом 20 (р+1)-го модуля q-й строки, пятый информационный выход 34 (р+1)-го модуля q-й строки соединен с пятым информационным входом 21 р-го модуля q-й строки, первый управляющий выход 35 первого модуля k-го столбца соединен с третьим управляющим входом 24 модулей k-го столбца с первого по n-й, первый управляющий выход 35 (j+1)-го модуля k-го столбца соединен с пятым управляющим входом 26j-го модуля k-го столбца, второй управляющий выход 36 р-го модуля q-й строки соединен с шестым управляющим входом 27 (р+1)-го модуля q-й строки, второй управляющий выход 36 p-го модуля s-й

строки соединен с четвертым информационным входом 20 (р+1)-го модуля q-й строки, пятый информационный выход 34 (р+1)-го модуля q-й строки соединен с пятым информационным входом 21 р-го модуля q-й строки, первый управляющий выход 35 первого модуля k-го столбца соединен с третьим управляющим входом 24 модулей k-го столбца с первого по n-й, первый управляющий выход 35 (j+1)-го модуля k-го столбца соединен с пятым управляющим входом 26j-го модуля k-го столбца, второй управляющий выход 36 р-го модуля q-й строки соединен с шестым управляющим входом 27 (р+1)-го модуля q-й строки, второй управляющий выход 36 p-го модуля s-й  строки соединен с седьмым управляющим входом 28 (р+1)-го модуля (s+1)-й строки.

строки соединен с седьмым управляющим входом 28 (р+1)-го модуля (s+1)-й строки.

Блок 16 выбора алгоритма функционирования (фиг. 2) содержит элемент запрета 38, первый 39 и второй 40 элементы И, первый 41 и второй 42 элементы ИЛИ, элемент И-ИЛИ 43, выход которого соединен с пятым выходом блока выбора алгоритма функционирования, первый вход которого соединен с прямым входом элемента запрета 38, выход которого соединен со вторыми входами первой и второй групп входов элемента И-ИЛИ 43 и четвертым выходом блока выбора алгоритма функционирования, второй и третий входы которого соединены соответственно с первым и вторым входами элемента ИЛИ 41 соответственно и с первым и вторым входами элемента И 39 соответственно, выход элемента ИЛИ 41 соединен с инверсным входом элемента запрета 38 и первым выходом блока выбора алгоритма функционирования, четвертый вход которого соединен со вторым входом элемента ИЛИ 42, вторым входом элемента И 40 и первым входом первой группы входов элемента И-ИЛИ 43, первый вход второй группы входов которого соединен с пятым входом блока выбора алгоритма функционирования, выход элемента И 39 соединен с первым входом элемента ИЛИ 42 и первым входом второго элемента И 40, выход которого соединен с третьим выходом блока выбора алгоритма функционирования, выход элемента ИЛИ 42 соединен со вторым выходом блока выбора алгоритма функционирования.

Буферный запоминающий блок 2 сообщений (фиг.3) содержит коммутатор 44, демультиплексор 45, блок регистров 46.1-46.l (где l - максимальная глубина очереди), группу блоков элементов ИЛИ 47.1-(47. l-1), первую группу элементов И 48.1-48. l, вторую группу элементов И 49.1-49.l, группу элементов ИЛИ 50.1-50. l, элемент ИЛИ 51, элемент И 52, одновибратор 53, причем выход одновибратора 53 соединен с инверсным управляющим входом демультиплексора 45 и первыми входами элементов ИЛИ 50.1-50. l, выходы которых соединены с синхронизирующими входами регистров 46.1-46. l соответственно, первый управляющий вход блока соединен с прямым и инверсным управляющими входами коммутатора 44, выход которого соединен с информационным входом демультиплексора 45, первый-(l-1)-й выходы которого соединены с первыми входами блоков элементов ИЛИ 47.1-дами блоков элементов ИЛИ 47.1-(47.l-1) соответственно, выходы которых соединены с информационными входами регистров 46.1-(46.l-1) соответственно, l-й выход демультиплексора 45 соединен с информационным входом регистра 46.l, второй управляющий вход блока соединен со входом одновибратора 53, первый информационный вход блока соединен с первым информационным входом коммутатора 44 и первым входом элемента ИЛИ 51, инверсные выходы блока регистров 46.1-46. l соединены со входами элементов И 48.1-48. l соответственно, выходы которых соединены с первыми входами элементов И 49.1-49. l соответственно, адресным входом демультиплексора 45 и входами элемента И 52, выход которого соединен с управляющим выходом блока, второй информационный вход которого соединен со вторым информационным входом коммутатора 44 и вторым входом элемента ИЛИ 51, выход которого соединен со вторыми входами элементов И 49.1-49.l, выходы которых соединены со вторыми входами элементов ИЛИ 50.1-50. l соответственно, прямые выходы регистров 46.2-46. l соединены со вторыми входами блоков элементов ИЛИ 47.1-(47.l-1) соответственно, прямой выход регистра 46.1 соединен с информационным выходом блока.

Блок 3 анализа (фиг.4) содержит первый 54.1, второй 54.2, третий 54.3, четвертый 54.4 и пятый 54.5 блоки памяти сообщений, мультиплексор 55, блок 56 выбора направления передачи информации, триггер 57, буферный регистр 58, блок элементов запрета 59, блок элементов И 60, выходной демультиплексор 61, дешифратор 62, счетчик 63, распределитель импульсов 64, элемент запрета 65, элемент ИЛИ 66, выход которого соединен с входом установки (S-входом) триггера 57 и инверсным входом элемента запрета 65, выход которого соединен с входом сброса (R-входом) триггера 57, прямой выход триггера 57 соединен с управляющим входом распределителя импульсов 64, четвертый выход которого соединен со счетным входом счетчика 63, выходы счетчика 63 соединены со входами дешифратора 62 и управляющими входами мультиплексора 55, выход которого соединен с информационным входом буферного регистра 58, синхронизирующий вход которого соединен со вторым выходом распределителя импульсов 64, первый и второй выходы счетчика 63 соединены с третьим и четвертым управляющими входами блока 56 выбора направления передачи информации, первый и второй управляющие входы блока 3 анализа соединены соответственно с пятым и шестым управляющими входами блока 56 выбора направления передачи информации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами выходного демультиплексора 61, первый и второй управляющие входы блока 56 выбора направления передачи информации соединены соответственно с первым и вторым выходами поля 584 направления буферного регистра 58, выход операционного поля 581 буферного регистра 58 и третий выход распределителя импульсов соединены с информационными входами блока элементов запрета 59 и блока элементов И 60, выход блока элементов И 60 соединен с первым информационным выходом блока 3 анализа, выходы полей вертикального 582 и горизонтального 583 адреса буферного регистра 58 соединены с информационным входом блока элементов запрета 59, выход которого, второй и третий выходы блока 56 выбора направления передачи информации подключены к информационному входу выходного демультиплексора 61, выходы которого с первого по четвертый соединены с информационными выходами блока 3 анализа со второго по пятый соответственно, информационные входы блока 3 анализа с первого по пятый соединены с информационным и первым управляющим входами блоков 54.1-54.5 памяти сообщений, информационные выходы блоков 54.1-54.5 памяти сообщений соединены соответственно с пятым, первым, вторым, третьим и четвертым информационными входами мультиплексора 55, управляющие выходы блоков 54.1-54.5 памяти сообщений соединены со входами элемента ИЛИ 66, третий выход распределителя импульсов 64 соединен с прямым входом элемента запрета 67, первый выход блока 56 выбора направления передачи информации соединен с управляющими входами блока элементов запрета 59, блока элементов И 60 и управляющим выходом блока 3 анализа, первый выход распределителя импульсов 64 соединен с тактовыми входами блоков 54.1-54.5 памяти сообщений, выходы дешифратора 62 соединены со вторыми управляющими входами блоков 54.1-54.5 памяти сообщений соответственно, выходы полей вертикального 583 и горизонтального 583 адреса буферного регистра 58 соединены соответственно с первым и вторым информационными входами блока 56 выбора направления передачи информации.

Блок 56 выбора направления передачи информации (фиг.5) содержит первый 67, второй 68, третий 69 и четвертый 70 блоки хранения адреса, первую 71, вторую 72, третью 73, четвертую 74, пятую 75 и шестую 76 схемы сравнения, первый 77, второй 78 и третий 79 мультиплексоры, первый 80 и второй 81 дешифраторы, шифратор 82, первый 84 и второй 85 элементы И, элемент ИЛИ 83, элемент И-ИЛИ-НЕ 86, выходы блоков 67-70 хранения адреса соединены с первыми входами схем сравнения 71-74 соответственно, выходы схем сравнения 71-74 соединены с информационными входами мультиплексора 77 с первого по четвертый соответственно, со входами элемента ИЛИ 83 с первого по четвертый соответственно и со входами первой группы информационных входов мультиплексора 78 соответственно, выход элемента ИЛИ 83 соединен с инверсным управляющим входом мультиплексора 78, пятый и шестой управляющие входы блока 56 выбора направления передачи информации соединены соответственно с первым и вторым управляющими входами мультиплексора 77, выход которого соединен с первым выходом блока 56 выбора направления передачи информации, выход блока 67 хранения адреса соединен с первыми входами схем 75 и 76 сравнения соответственно, первый и второй информационные входы блока 56 выбора направления передачи информации соединены со вторыми входами схем 71, 72, 73 и 74 сравнения, первый и второй информационные входы блока 56 выбора направления передачи информации соединены соответственно со вторыми входами схем 75 и 76 сравнения, выходы "Больше" и "Меньше" схемы 75 сравнения соединены соответственно с первым и третьим входами первой группы информационных входов мультиплексора 79, выходы которого с первого по четвертый соединены соответственно с первого по четвертый входами второй группы информационных входов мультиплексора 78, выходы которого с первого по четвертый соединены соответственно с первого по четвертый входами шифратора 82, первый и второй выходы которого соединены соответственно со вторым и третьим выходами блока 56 выбора направления передачи информации, выход "Равно" схемы 75 сравнения соединен с первыми входами элементов И 84 и 85, выходы которых соединены соответственно со вторым и четвертым входами первой группы информационных входов мультиплексора 79, выходы "Больше" и "Меньше" схемы 76 сравнения соединены со вторыми входами элементов И 84 и 85 соответственно, третий и четвертый управляющие входы блока 56 выбора направления передачи информации соединены соответственно с первым и вторым входами дешифратора 81, выходы которого с первого по четвертый соединены соответственно со входами с первого по четвертый второй группы информационных входов мультиплексора 79, первый и второй управляющие входы блока 56 выбора направления передачи информации соединены соответственно с первым и вторым входами дешифратора 80, выходы которого с первого по четвертый соединены с первыми входами первой, третьей, пятой и седьмой групп входов элемента И-ИЛИ-НЕ 86 соответственно и вторыми прямыми входами второй, четвертой, шестой и восьмой групп входов элемента И-ИЛИ-НЕ 86 соответственно, выходы дешифратора 81 с первого по четвертый соединены со вторыми входами первой, третьей, пятой и седьмой групп входов элемента И-ИЛИ-НЕ 86 соответственно и первыми прямыми входами второй, четвертой, шестой и восьмой групп входов элемента И-ИЛИ-НЕ 86 соответственно, выходы "Больше" и "Меньше" схемы 75 сравнения соединены соответственно с инверсными входами второй и четвертой групп входов элемента И-ИЛИ-НЕ 86, выходы "Больше" и "Меньше" 76 схемы сравнения соединены соответственно с инверсными входами шестой и восьмой групп входов элемента И-ИЛИ-НЕ 86, выход элемента И-ИЛИ-НЕ 86 соединен с управляющим входом мультиплексора 79.

Блок 8 синхронизации (фиг.6) содержит триггер 87 запуска, генератор 88 тактовых импульсов, счетчик 89, дешифратор 90, элементы И 91 и ИЛИ 92, причем первый вход блока соединен с S-входом триггера 87, выход которого соединен со входом генератора 88 тактовых импульсов, выход которого соединен с инкрементирующим входом счетчика 89 и управляющим входом дешифратора 90, первый и второй выходы счетчика 89 соединены соответственно с первым и вторым информационными входами дешифратора 90, первый - третий выходы которого соединены с первым - третьим выходами блока, второй и четвертый входы блока соединены соответственно с первым и вторым входами элемента И 91, выход которого соединен со вторым входом элемента ИЛИ 92, третий вход блока соединен с первым входом элемента ИЛИ 92, выход которого соединен с R-входом триггера 87.

Блоки 54.1-54.5 памяти сообщений (фиг.7) содержат блок регистров 93.1-93. К (где К - максимальная глубина очереди сообщений), группу блоков элементов ИЛИ 94.1-94. (K-l), первый блок элементов И 95.1-95.К, второй блок элементов И 96.1-96. К, блок элементов ИЛИ 97.1-97.К, демультиплексор 98, элемент И 99, элемент И-НЕ 100, причем тактовый и второй управляющий входы блока соединены с первым и вторым входами элемента И 99 соответственно, выход которого соединен со вторыми входами элементов ИЛИ 97.1-97.К и инверсным управляющим входом демультиплексора 98, первый выход которого соединен с информационным входом регистра 93. К. Со второго по К-й выходы демультиплексора 98 соединены со вторыми входами блоков элементов ИЛИ 94.(K-l)-94.1 соответственно, выходы которых соединены с информационными входами регистров 93.(К-1)-93.1 соответственно. Инверсные выходы регистров 93.1-93.K соединены со входами элементов И 95.1-95.К соответственно, выходы которых соединены с адресным входом демультиплексора 98 и входами элемента И-НЕ 100, выход которого соединен с управляющим выходом блока, информационный выход которого соединен с прямым выходом регистра 93.1. Прямые выходы регистров 93.К-93.2 соединены с первыми входами блоков элементов ИЛИ 94.(К-1)-94.1 соответственно. Первый управляющий вход блока соединен со вторыми входами элементов И 96.1-96. К, первые входы которых соединены с выходами элементов И 95.1-95.К соответственно. Выходы элементов И 96.1-96.К соединены с первыми входами элементов ИЛИ 97.1-97.К соответственно, выходы которых соединены со входами синхронизации регистров 93.1-93.К соответственно. Информационные входы блока соединены с информационными входами демультиплексора 98.

Рассмотрим процесс функционирования распределенной системы. Организация процесса управления осуществляется внешними по отношению к системе средствами управления и контроля (диспетчером). Диспетчером обеспечиваются, во-первых, как первоначальный пуск системы, так и пуски системы после выполнения перестроек; во-вторых, слежение за правильностью функционирования блоков и элементов 1 - 15 и их связей, отвечающих за формирование управляющих сигналов, передаваемых на объект управления, и фиксация неисправных модулей, в которых нарушено правильное функционирование указанных блоков и элементов, с помощью триггеров отказа для каждого из модулей, в-третьих, останов системы как после исполнения программ управления, так и после возникновения неисправностей в модулях. Система осуществляет программное управление как при отсутствии отказов модулей, так и при их наличии, и, кроме этого, перестройку (переназначением выполняемого алгоритма управления и логического адреса для каждого из модулей) после останова, вызванного отказами отдельных модулей. При реализации программного управления взаимодействие между исправными модулями в системе с отказавшими модулями осуществляется при исправной работе блоков 16, отвечающих за реконфигурацию системы, всех модулей системы.

Так как система состоит из однотипных модулей, ее работу рассмотрим на примере функционирования отдельного модуля, например модуля с физическим адресом (i,j), причем работу этого модуля будем рассматривать во взаимосвязи с другими модулями системы.

Первоначально элементы памяти модуля находятся в нулевом состоянии (за исключением разряда 66 регистра 6 команд, определяющего признак конца программы управления).

Работа модуля начинается при подаче на информационный вход 18 (фиг.1) кода операции, определяющего адрес первой команды программ управления. Этот код подается от диспетчера. Одновременно на управляющий вход 23 модуля поступает единичный сигнал запуска. Далее этот сигнал передается на первый вход блока 8 синхронизации.

Сигнал с первого входа блока 8 синхронизации (фиг.6) поступает на S-вход триггера 84, переводит этот триггер в единичное состояние и тем самым запускает генератор 85. Импульсы с выхода генератора 85 начинают поступать на инкрементирующий вход счетчика 86, а также на управляющий вход дешифратора 87. На выходе дешифратора 87 (а соответственно и блока 8 синхронизации) начинается формирование трех импульсных последовательностей, сдвинутых друг относительно друга на треть периода.

Код операции с информационного входа 18 модуля (фиг.1) поступает через коммутатор 45 буферного запоминающего блока 2 сообщений (фиг.3) на информационный вход демультиплексора 46. Так как регистры 47.1-47.l. находятся в нулевом состоянии, на выходах элементов И 49.1-49.l формируются сигналы логической единицы. Эти сигналы, поступая на адресный вход демультиплексора 46, разрешают запись информации в первый регистр 47.1 через блок элементов ИЛИ 48.1. Вместе с адресом программы (кодом операции) на информационный вход 18 модуля подается управляющий импульс. Этот импульс через элемент ИЛИ 52, элемент И 50.1 и элемент ИЛИ 51.1 поступает на синхронизирующий вход регистра 47.1 и производит запись в него поступившего кода операции. Состояние регистра 47.1 становится отличным от нулевого и на выходе элемента И 49.1 появляется сигнал логического нуля, который в объединении с единичными сигналами с выходов элементов 49.2-49.l. предопределяет запись очередного кода операции во второй регистр 47.2 буферного запоминающего блока 2 сообщений. Сигналы с выходов элементов И 49.1-49.l. также поступают на входы элемента И 53; на выходе элемента 53 формируется сигнал логического нуля, определяющий наличие информации в блоке 2.

Первый тактовый импульс с первого выхода блока 8 синхронизации (фиг.1) поступает на синхронизирующий вход регистра 5 адреса и осуществляет запись в него информации с информационного выхода буферного запоминающего блока 2 сообщений (с выхода регистра 47.1) через коммутатор 4 адреса. С выхода регистра 5 адрес команды поступает на входы первого 1, второго 12, третьего 13 и четвертого 14 блоков памяти программ и обеспечивает считывание первой команды программы управления. Считывание производится как из блока 1, так и из блоков 12, 13 и 14, однако передача команд на информационный вход регистра 6 осуществляется только из одного блока.

Выбор блока памяти программ, а, следовательно, и назначение алгоритма функционирования модуля осуществляется путем настройки мультиплексора 15. Настройка выполняется блоком 16 выбора алгоритма функционирования.

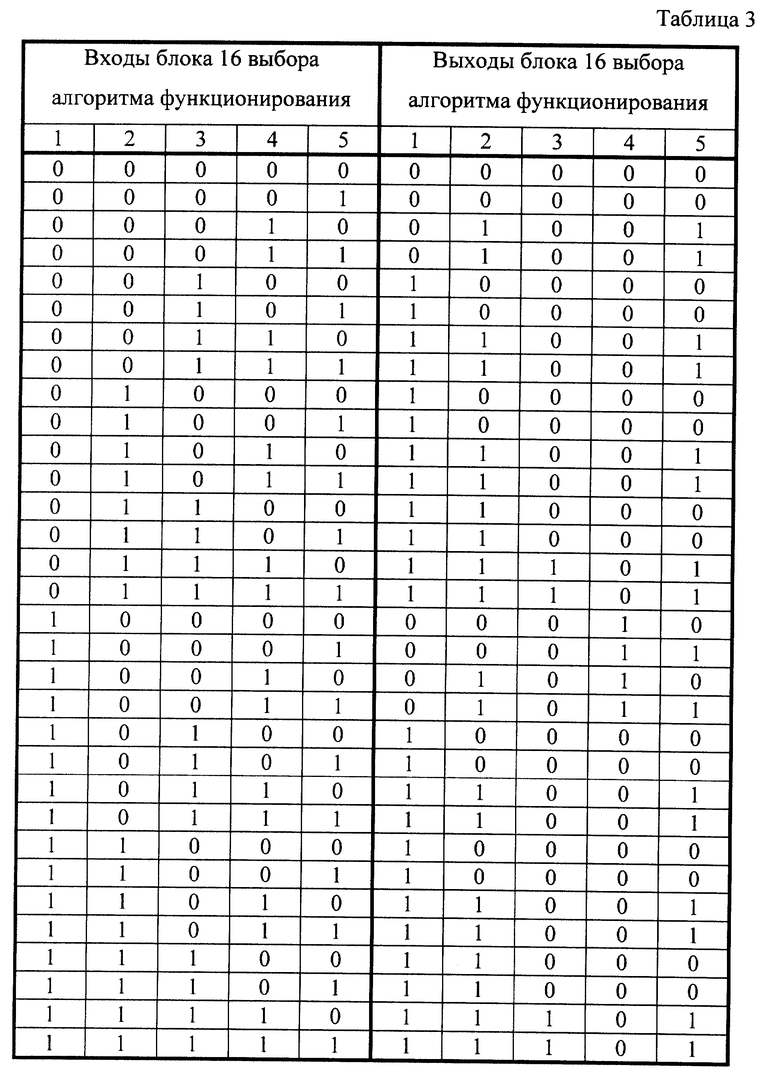

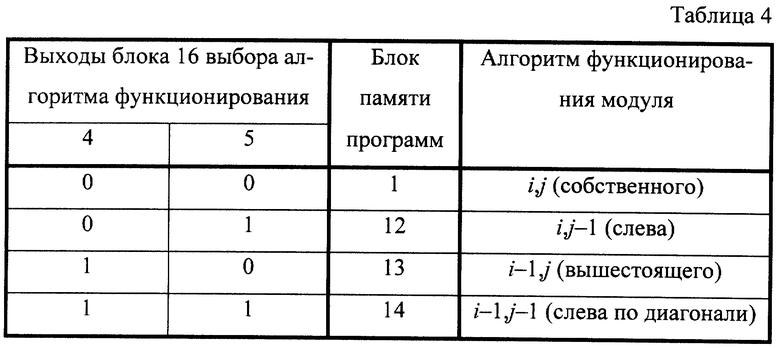

Блок 16 выбора алгоритма функционирования (фиг.2) работает следующим образом. На второй вход блока 16 с управляющего входа 26 модуля поступает сигнал от диспетчера с триггера отказа, соответствующего данному модулю. На первый, третий, четвертый и пятый входы блока 16 с управляющих входов 25, 27, 28 и 29 модуля соответственно поступают также сигналы от других модулей. Назначение сигналов на входах блока 16 описывается в табл.1. Комбинационная схема блока 16, состоящая из элементов запрета 38, И 39, 40, ИЛИ 41, 42 и И-ИЛИ 43, на основе сигналов на первом - пятом входах определяет согласно таблице истинности (табл. 3) состояния первого - пятого выходов блока 16, назначение которых описывается в табл.2. Сигналы с первого и второго выходов блока 16 через управляющие выходы 36 и 37 соответственно поступают в другие модули. Сигнал с третьего выхода блока 16 поступает через управляющий выход 38 модуля диспетчеру. Единичное его значение определяет невозможность перестройки распределенной системы - фатальный отказ. Сигналы с четвертого и пятого выходов блока 16 определяют алгоритм, по которому будет функционировать модуль (табл.4).

В случае если отказавшие модули отсутствуют (фиг.9) или имеются, но не требуют перестройки текущего модуля на реализацию другого алгоритма (например, фиг. 11, модуль с ФА (2, 3)), команды соответствующей программы считываются из блока 1. В противном случае текущий модуль переходит к выполнению программы, размещенной либо в блоке 12 (например фиг.11, модуль с ФА (3, 4)), либо 13 (например, фиг.11, модуль с ФА (5, 1)), либо 14 (например фиг. 11, модуль с ФА (5, 4)). Сигналы с четвертого и пятого выходов блока 16 выбора алгоритма функционирования поступают на адресные входы мультиплексора 15, что обеспечивает передачу на его выход команды из соответствующего блока памяти программ.

Рассмотрим процесс обработки команды. Переданная команда по тактовому импульсу со второго выхода блока 8 синхронизации записывается в регистр 6 команд (формат считанной команды представлен на фиг.8а). В зависимости от содержимого полей считанной команды, модуль может функционировать одним из следующих способов.

1. Предположим, в поле 65 регистра 6 команд признак передачи управления отсутствует. Операционная часть команды с поля 64 регистра 6 команд поступает через блок 9 элементов запрета на информационный выход 31 модуля для управления. Поля 61 62 и 63 регистра 6 команд формируют адрес очередной команды с использованием мультиплексора 7 логических условий.

Адрес следующей команды, получаемый объединением значения младшего (модифицируемого) разряда адреса с выхода мультиплексора 7 и немодифицированных разрядов с выхода 6з регистра 6, через коммутатор 4 поступает на информационный вход регистра 5 и фиксируется в данном регистре с приходом следующего импульса с первого выхода блока 8. После записи этого адреса в регистр 5 осуществляется переход к считыванию и выполнению очередной команды программы управления. Считываемая команда выполняется аналогично рассмотренному выше.

С выдачей последней команды программы управления в поле 66 регистра 6 команд заносится единичная метка - признак окончания программы. Единичный сигнал с выхода 66 регистра 6 поступает на второй управляющий вход блока 2 и передним фронтом возбуждает на выходе одновибратора 54 импульс. Этот импульс через элементы ИЛИ 51.1-51.l подается на синхронизирующие входы регистров 47.1-47. l и обеспечивает сдвиг очереди сообщений. В регистр 47.1 поступает адрес очередной программы. Одновременно сигнал выхода 66 регистра 6 поступает на управляющие входы коммутатора 4 и коммутирует его выход с информационным выходом блока 2. Кроме того, этот сигнал поступает на второй вход блока 8 и открывает элемент И 88.

Если выполнялась последняя программа, то после сдвига информации в блоке 2 очередь поступивших на обслуживание запросов становится пустой (нулевое состояние регистров 47.1-47.l). На выходах элементов И 49.1-49.l образуются сигналы логической единицы. Эти сигналы формируют единичный сигнал на выходе элемента И 53, который с выхода блока 2 (фиг.1) поступает на четвертый вход блока 8 синхронизации (фиг.6). На выходе элемента И 88 формируется сигнал логической единицы, который через элемент ИЛИ 89 устанавливает триггер 84 в нулевое состояние. Нулевой сигнал с прямого выхода триггера 84 выключает генератор 85 и модуль завершает свою работу.

Работа модуля может также завершаться при поступлении на вход 24 сигнала останова от диспетчера, выявившего отказы в системе. Диспетчер инициализирует работу только работоспособных модулей после задержки, необходимой для формирования сигналов на выходах блока 16.

2. Если в поле 65 считанной команды присутствует единичный признак передачи управления, то эта команда является командой обмена (передачи управления) и на выходе 64 операционного поля регистра 6 формируется сообщение К. Формат операционной части команды обмена представлен на фиг.8б. Сообщение К имеет вид:

К=ФАпр•Н•Ак,

где ФАпр - физический адрес модуля-приемника информации;

Н - направление выдачи;

Aк - адрес программы, которую должен выполнить модуль-приемник;

• - знак конкатенации. В свою очередь

ФАпр=ФАстлб•ФАстр,

где ФАстлб - физический номер модуля в столбце (вертикальная составляющая адреса);

ФАстр - физический номер модуля в строке (горизонтальная составляющая адреса).

Единичная метка с выхода 65 регистра 6 поступает на управляющий вход блока элементов И 10 и второй вход элемента И 11(фиг.1) и разрешает тем самым прохождение информации с поля 64 регистра 6 команд через блок элементов И 10 на первый информационный вход блока 3 анализа с целью последующей выдачи на один из выходов 32 - 35 (фиг.4) (работа блока 3 анализа рассмотрена ниже). Вместе с выдаваемым сообщением с выхода блока 8 синхронизации через элемент И 11 (фиг.1) поступает тактовый импульс.

Обмен командами в распределенной системе для программного управления осуществляется (фиг. 9) в четырех направлениях. По каждому из направлений в блоке 3 анализа (фиг.4) имеется блок памяти сообщений, причем блок 55.1 памяти сообщений предназначен для хранения сообщений от собственного модуля.

Рассмотрим процесс приема и выдачи сообщений. Допустим, сообщение поступает на информационный вход блока 55.2 памяти сообщений.

Предположим, что в текущий момент все регистры 90.1-90.К обнулены (фиг. 7). На выходах элементов И 92.1-92.К находятся единичные сигналы. Эти сигналы, поступая на вход элемента И-НЕ 97, формируют на его выходе сигнал логического нуля (этот сигнал индицирует отсутствие сообщений в блоке 55.2). Кроме того, рассматриваемые сигналы подаются на адресный вход демультиплексора 95 и коммутируют его информационный вход с К-м выходом. Эти же сигналы открывают элементы 93.1-93.К.

Сообщение с информационного входа блока через демультиплексор 95 и блок элементов ИЛИ 91.1 передается и фиксируется на информационном входе регистра 90.1. Одновременно на первом управляющем входе блока появляется тактовый импульс, сопровождающий данное сообщение. Этот импульс через открытые элементы И 93.1-93.К и элементы ИЛИ 94.1-94.К поступает на входы синхронизации регистров 90.1-90.К и задним фронтом производит запись поступающего сообщения в регистр 90.1 (состояние остальных регистров при этом не изменяется, поскольку на первом - (К-1) выходах демультиплексора 95 находятся нулевые коды). На выходе элемента 92.1 появляется сигнал логического нуля. Сигналы с выходов элементов И 92.1-92.К поступают на вход элемента И-НЕ 97, формируя на его выходе сигнал логической единицы, индицирующий наличие сообщения в блоке. Одновременно эти же сигналы подаются на адресный вход демультиплексора 95, коммутируют его информационный вход с (К-1)-м выходом и тем самым обеспечивают возможность записи последующего сообщения в регистр 90.2. Кроме того, нулевой сигнал с выхода элемента И 92.1 блокирует элемент И 93.1 и запрещает модификацию содержимого регистра 90.1. Таким образом на информационном выходе блока появляется поступившее сообщение, а на управляющий выход поступает единичный сигнал.

Единичный сигнал с управляющего выхода блока 55.2 через элемент ИЛИ 67 (фиг.4) устанавливает триггер 59 в единичное состояние и тем самым разрешает формирование тактовых импульсов на выходе распределителя импульсов 65 для синхронизации работы блока 3 анализа.

Синхронизация работы блока 3 анализа происходит по четырем импульсным последовательностям. Цикл работы состоит из четырех фаз, каждая из которых начинается тактовым импульсом соответствующей импульсной последовательности.

По первому импульсу с четвертого выхода распределителя 65 содержимое счетчика 64 увеличивается на единицу. Код с выхода счетчика 64 формирует унитарный код на выходе дешифратора 63 блока памяти сообщений 55.k, а также коммутирует выход мультиплексора 56 с его информационным входом, соответствующим блоку 55. k. Сообщение из этого блока через мультиплексор 56 передается на информационный вход регистра 60.

Тактовый импульс со второго выхода распределителя 65 фиксирует считанное сообщение в регистре 60.

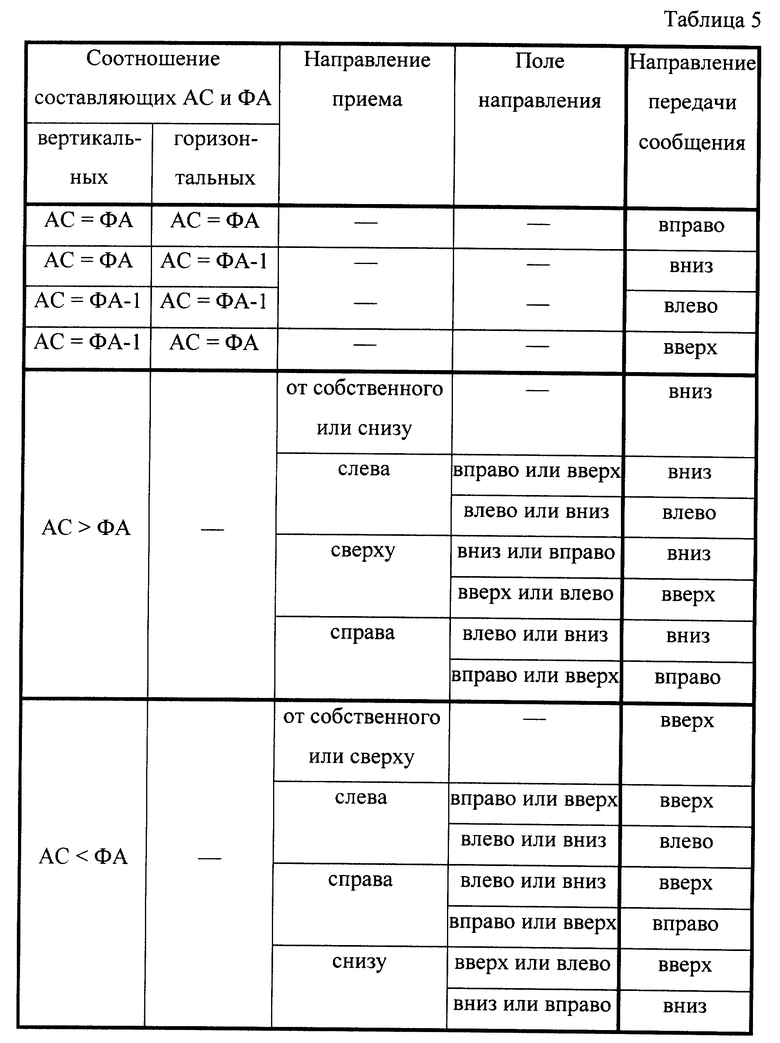

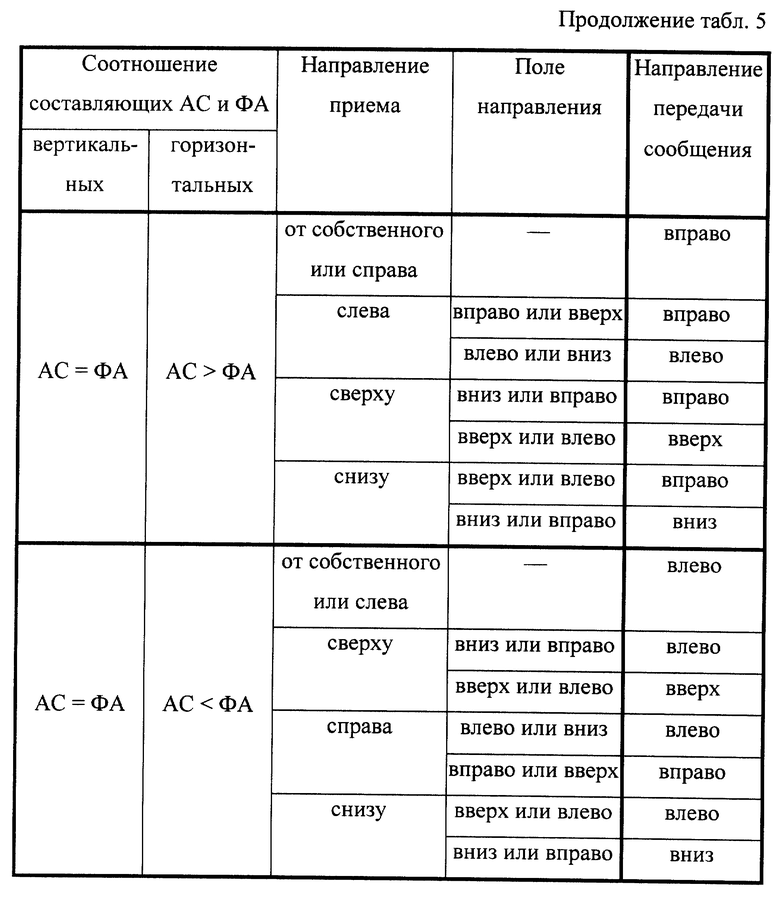

После записи сообщения в регистр 60 осуществляется выбор направления дальнейшей передачи сообщения. Этот выбор определяется соотношением вертикальных и горизонтальных составляющих ФА и АС и выполняется блоком 57.

Выбор направления передачи информации осуществляется следующим образом. АС сравнивается с ЛА модуля. Сравнение ЛА модуля и АС производится схемой сравнения 68 блока 57 (фиг.5). Если адреса равны, то данный модуль является модулем-приемником и на выходе "Равно" схемы сравнения 68 появляется единичный сигнал, который разрешает прием сообщения текущим модулем.

Если адреса не равны, то модуль должен передать сообщение другому модулю и единичный сигнал появится на выходе "Не равно" схемы сравнения 68, и поступит на первый вход элемента И 78. Одновременно схема 69 сравнивает вертикальные составляющие АС и ФА модуля, а схема 70 сравнивает горизонтальные составляющие этих адресов. По результатам сравнения на выходах блока формируются сигналы, определяющие способ передачи поступившего сообщения. Эти сигналы вырабатываются комбинационной схемой, состоящей из мультиплексора 71, шифратора 72, элементов И 73-78, элементов ИЛИ 79 и 80, в соответствии с табл. 5. Сигналы на втором и третьем выходах блока 57 кодируют направление передачи сообщения и, поступая затем на адресные входы демультиплексора 62, обеспечивают выдачу сообщения в соответствующем направлении. На четвертом выходе блока 57 формируется единичный сигнал при наличии ситуации фатального отказа (табл.5), т.е. модуль-приемник не был найден ни в одном из модулей по причине сбоев при перестройке. Этот сигнал поступает далее диспетчеру, который выключает распределенную систему. На пятом выходе блока 57 формируется бит обхода (табл.5).

Если на первом выходе блока 57 присутствует сигнал логической единицы, то операционное поле сообщения через блок элементов И 61.2 передается на первый информационный выход блока анализа для последующей обработки текущим модулем. В противном случае блок элементов И 61.2 закрывается и сообщение с выходов регистра 60 передается на один из четырех выходов демультиплексора 62 через блок элементов И 61.1 (к передаваемому сообщению добавляется бит обхода).

Одновременно с выбором направления передачи считанного сообщения производится сдвиг информации в выбранном блоке памяти сообщений (в нашем примере - в блоке 55.2). Сдвиг информации в блоках 55.1-55.5 синхронизируется импульсом с первого выхода распределителя 65.

Следующий импульс с третьего выхода распределителя 65 синхронизирует прием выдаваемого сообщения либо текущим модулем, либо одним из модулей-соседей, поступая соответственно через блок 61.2 на первый информационный выход блока анализа, либо через блок 61.1 и демультиплексор 62 на второй, третий, четвертый или пятый информационные выходы блока анализа. Одновременно этот импульс поступает на прямой вход элемента И 66 и в случае отсутствия сообщений в блоках 55.1-55.5 проходит на вход сброса триггера 59 и тем самым выключает распределитель 65.

Рассмотрим переназначение логических адресов модулей после останова, вызванного отказами модулей. Допустим отказавшим является модуль (i-1,j) - модуль находящийся сверху над текущим, а все остальные модули распределенной системы работоспособны. Исходя из логики работы системы текущий модуль должен принять на себя функции верхнего и в дальнейшем считывать команды из блока 13 (табл.4).

Диспетчер, обнаружив отказ, фиксирует его переводом триггера отказа модуля (i-1, j) в единичное состояние, осуществляет останов всех модулей системы и, тем самым, инициирует вычисление новых ЛА модулей. При этом на вход 26 модуля (i-1,j) поступает единичный сигнал о его отказе с триггера отказа. Указанный сигнал проходит через элемент ИЛИ 42, поступает на выход 36 модуля и передается нижнему модулю (i,j). Поступая на вход 27 модуля (i, j), рассматриваемый сигнал обеспечивает образование на четвертом и пятом выходах блока 16 кода "10" (табл.3). Этот код подается на управляющие входы мультиплексора 15 и коммутирует его выход с выходом блока 13 (табл.4). Одновременно данный код передается на первый и второй управляющие входы блока 3 анализа и инициирует изменение ЛА модуля (i,j).

С другой стороны, сообщение, размещенное в регистре 60 отказавшего модуля (i-1,j) и имеющее AC (i-1,j), будет передано не на выход блока элементов И 61.2, а через блок 61.1 на выход демультиплексора 62 для дальнейшей передачи модулю с ЛА (i-1,j) (которым стал модуль с ФА (i,j)).

Аналогично рассмотренному выше изменяются ЛА всех нижестоящих модулей, в том числе и резервного.

После осуществления перестройки диспетчер запускает работоспособные модули, подавая единичный сигнал на входы 23. (Следует подчеркнуть, что перед запуском элементы памяти всех модулей приводятся в исходное состояние).

Рассмотрим пример процесса обработки передаваемых сообщений в системе с отказавшими модулями. Пример передачи сообщения при наличии отказов в распределенной системе иллюстрируется на фиг.12. Сообщение должно быть передано от модуля-источника (5, 4) в модуль-приемник с ЛА (4, 2). На первом этапе сообщение из модуля (5, 4) сначала передается по вертикали в модуль (4, 4) откуда сразу поступает в модуль (4, 5), так как модуль (4, 4) отказавший. В модуле (4, 5) направление приема сообщения и направление выдачи в сообщении не совпадают и сообщение выдается в модуль (4, 4), откуда аналогично через модули (3, 4), (3, 3), (2, 3) (3, 2), (3, 3), (4, 3) поступает в модуль (4, 2) который является одним из четырех модулей, ЛА которых может принимать значение (4, 2). Так как ЛА модуля (4, 2) не равен АС, то первый этап на этом завершается. На втором этапе сообщение передается в модуль (4, 3), затем (5, 3) и (2, 2). ЛА модуля (5, 2) равен АС, поэтому модуль (5, 2) является модулем-приемником.

Таким образом, введение дополнительных технических средств позволяет существенно расширить область применения за счет сохранения работоспособности системы в целом при отказе ее модулей.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2133054C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| УСТРОЙСТВО СОРТИРОВКИ СЛОВ | 2002 |

|

RU2223538C2 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности. Техническим результатом является расширение функциональных возможностей. Устройство содержит четыре блока памяти программ, блок выбора алгоритма функционирования, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, мультиплексор выбора программ, блок синхронизации, блок элементов запрета, блок элементов И, элемент И. 3 з.п.ф-лы, 12 ил., 5 табл.

системы содержит первый блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, причем первый управляющий вход модуля соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен со входом первого блока памяти программ, синхронизирующий вход регистра команд соединен со вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторым информационным входом мультиплексора логических условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий модуля соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов запрета, выход которого соединен с первым информационным выходом модуля, второй управляющий вход модуля соединен с третьим входом блока синхронизации, информационный выход буферного запоминающего блока сообщений соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого и выход элемента И соединены с первым информационным входом блока анализа, управляющий выход которого соединен с первым управляющим входом буферного запоминающего блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход поля передачи управления регистра команд соединен с инверсным входом блока элементов запрета, управляющим входом блока элементов И и вторым входом элемента И, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса, вторым входом блока синхронизации и вторым управляющим входом буферного запоминающего блока сообщений, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, первый информационный вход модуля соединен со вторым информационным входом буферного запоминающего блока сообщений, второй и третий информационные входы модуля соединены соответственно со вторым и третьим информационными входами блока анализа, второй и третий информационные выходы которого соединены соответственно со вторым и третьим информационными выходами модуля, отличающаяся тем, что каждый модуль дополнительно содержит второй, третий и четвертый блоки памяти программ, мультиплексор выбора программ, блок выбора алгоритма функционирования, причем входы блоков памяти программ со второго по четвертый соединены с выходом регистра адреса, выходы блоков памяти программ с первого по четвертый соединены с информационными входами мультиплексора выбора программ с первого по четвертый соответственно, выход мультиплексора выбора программ соединен с информационным входом регистра команд, четвертый выход блока выбора алгоритма функционирования соединен с первым управляющим входом мультиплексора выбора программ и с первым управляющим входом блока анализа, пятый выход блока выбора алгоритма функционирования подключен ко второму управляющему входу мультиплексора выбора программ и ко второму управляющему входу блока анализа, четвертый и пятый информационные входы модуля соединены соответственно с четвертым и пятым информационными входами блока анализа, четвертый и пятый информационные выходы которого соединены соответственно с четвертым и пятым информационными выходами модуля, управляющие входы модуля с третьего по седьмой соединены со входами блока выбора алгоритма функционирования с первого по пятый соответственно, первый, второй и третий выходы блока выбора алгоритма функционирования соединены соответственно с первым, вторым и третьим управляющими выходами модуля, второй информационный выход j-гo

системы содержит первый блок памяти программ, буферный запоминающий блок сообщений, блок анализа, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов запрета, блок элементов И, элемент И, причем первый управляющий вход модуля соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен со входом первого блока памяти программ, синхронизирующий вход регистра команд соединен со вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторым информационным входом мультиплексора логических условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий модуля соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов запрета, выход которого соединен с первым информационным выходом модуля, второй управляющий вход модуля соединен с третьим входом блока синхронизации, информационный выход буферного запоминающего блока сообщений соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого и выход элемента И соединены с первым информационным входом блока анализа, управляющий выход которого соединен с первым управляющим входом буферного запоминающего блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход поля передачи управления регистра команд соединен с инверсным входом блока элементов запрета, управляющим входом блока элементов И и вторым входом элемента И, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса, вторым входом блока синхронизации и вторым управляющим входом буферного запоминающего блока сообщений, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, первый информационный вход модуля соединен со вторым информационным входом буферного запоминающего блока сообщений, второй и третий информационные входы модуля соединены соответственно со вторым и третьим информационными входами блока анализа, второй и третий информационные выходы которого соединены соответственно со вторым и третьим информационными выходами модуля, отличающаяся тем, что каждый модуль дополнительно содержит второй, третий и четвертый блоки памяти программ, мультиплексор выбора программ, блок выбора алгоритма функционирования, причем входы блоков памяти программ со второго по четвертый соединены с выходом регистра адреса, выходы блоков памяти программ с первого по четвертый соединены с информационными входами мультиплексора выбора программ с первого по четвертый соответственно, выход мультиплексора выбора программ соединен с информационным входом регистра команд, четвертый выход блока выбора алгоритма функционирования соединен с первым управляющим входом мультиплексора выбора программ и с первым управляющим входом блока анализа, пятый выход блока выбора алгоритма функционирования подключен ко второму управляющему входу мультиплексора выбора программ и ко второму управляющему входу блока анализа, четвертый и пятый информационные входы модуля соединены соответственно с четвертым и пятым информационными входами блока анализа, четвертый и пятый информационные выходы которого соединены соответственно с четвертым и пятым информационными выходами модуля, управляющие входы модуля с третьего по седьмой соединены со входами блока выбора алгоритма функционирования с первого по пятый соответственно, первый, второй и третий выходы блока выбора алгоритма функционирования соединены соответственно с первым, вторым и третьим управляющими выходами модуля, второй информационный выход j-гo  модуля k-гo

модуля k-гo  столбца соединен со вторым информационным входом (j+l)-гo модуля k-гo столбца, третий информационный выход (j+l)-гo модуля k-гo столбца соединен с третьим информационным входом j-гo модуля k-гo столбца, четвертый информационный выход р-го

столбца соединен со вторым информационным входом (j+l)-гo модуля k-гo столбца, третий информационный выход (j+l)-гo модуля k-гo столбца соединен с третьим информационным входом j-гo модуля k-гo столбца, четвертый информационный выход р-го  модуля q-й

модуля q-й  строки соединен с четвертым информационным входом (р+1)-го модуля q-й строки, пятый информационный выход (р+1)-го модуля q-й строки соединен с пятым информационным входом р-го модуля q-й строки, первый управляющий выход первого модуля k-гo столбца соединен с третьим управляющим входом модулей k-гo столбца с первого по n-й, первый управляющий выход (j+l)-гo модуля k-гo столбца соединен с пятым управляющим входом j-гo модуля k-гo столбца, второй управляющий выход р-го модуля q-й строки соединен с шестым управляющим входом (р+1)-го модуля q-й строки, второй управляющий выход р-го модуля s-й

строки соединен с четвертым информационным входом (р+1)-го модуля q-й строки, пятый информационный выход (р+1)-го модуля q-й строки соединен с пятым информационным входом р-го модуля q-й строки, первый управляющий выход первого модуля k-гo столбца соединен с третьим управляющим входом модулей k-гo столбца с первого по n-й, первый управляющий выход (j+l)-гo модуля k-гo столбца соединен с пятым управляющим входом j-гo модуля k-гo столбца, второй управляющий выход р-го модуля q-й строки соединен с шестым управляющим входом (р+1)-го модуля q-й строки, второй управляющий выход р-го модуля s-й  строки соединен с седьмым управляющим входом (р+1)-го модуля (s+1)-й строки, шестой управляющий вход модулей первого столбца с первого по n-й, пятый управляющий вход модулей n-й строки с первого по m-й, седьмой управляющий вход модулей первой строки с первого по m-й и первого столбца со второго по n-й предназначены для подачи сигнала логического нуля.

строки соединен с седьмым управляющим входом (р+1)-го модуля (s+1)-й строки, шестой управляющий вход модулей первого столбца с первого по n-й, пятый управляющий вход модулей n-й строки с первого по m-й, седьмой управляющий вход модулей первой строки с первого по m-й и первого столбца со второго по n-й предназначены для подачи сигнала логического нуля.

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Погружной насос | 1973 |

|

SU514972A1 |

| DE 3200761 A1, 14.10.1982. | |||

Авторы

Даты

2002-07-20—Публикация

2000-10-16—Подача