Изобретение относится к цифровой вычислительной технике и может найти применение при построении средств коммутации мультипроцессорных вычислительных систем, микроконтроллерных сетей, в том числе систем и сетей с динамической структурой, а также систем сбора информации, абонентских систем связи с децентрализованным управлением и коммутационных средств измерительных систем.

Известен модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, два элемента сравнения, два дешифратора, элемент И (а.с. 1575167 СССР, G 06 F 7/00, 15/16; опубл. 30.06.90, БИ N 24).

Недостатком известного модуля является невозможность построения на его основе коммутационных структур, реализующих множество различных маршрутов (траекторий) передачи сообщений для каждой пары взаимодействующих модулей. Следствием данного недостатка является резкое ограничение числа возможных межмодульных связей в коммутационной структуре при отказе незначительного числа модулей.

Наиболее близким к предлагаемому устройству по технической сущности является модуль матричного коммутатора, включающий с первого по третий блоки организации очередей сообщений, мультиплексор, блок анализа очередей сообщений, регистр, дешифратор, блок синхронизации, триггер, блок ретрансляции сообщений, с первого по восьмой элементы И, с первого по четвертый элементы ИЛИ и коммутатор (патент 2116664 РФ, G 06 F 7/00, 15/163; опубл. 27.07.98, БИ N 21).

Недостаток данного модуля состоит в отсутствии возможности динамического изменения маршрутов передачи сообщений (изменения маршрутов непосредственно в ходе перемещения сообщений) в формируемых на его основе коммутационных (коммуникационных) структурах. Следствием этого недостатка является невысокая гибкость и низкая отказоустойчивость коммуникационных структур на основе указанного модуля.

Технической задачей, на решение которой направлено заявляемое изобретение, является повышение гибкости и отказоустойчивости коммуникационных структур, формируемых на основе предлагаемого модуля, путем организации возможности динамического изменения маршрутов передачи сообщений.

Техническая задача решается тем, что в модуль матричной коммуникационной сети, содержащий блоки организации очереди сообщений с первого по третий, мультиплексор, блок анализа очередей сообщений, первый буферный регистр, дешифратор, блок синхронизации, триггер запуска, первый коммутатор, первый элемент И, второй элемент И, первый элемент ИЛИ, второй элемент ИЛИ, третий элемент ИЛИ, четвертый элемент ИЛИ, причем информационные входы модуля с первого по третий подключены к информационным входам блоков организации очереди сообщений с первого по третий соответственно, первые выходы которых соединены с информационными входами мультиплексора с первого по третий соответственно, первая группа разрядов выхода которого соединена с информационным входом первого буферного регистра, вторые выходы блоков организации очереди сообщений с первого по третий подключены к входам блока анализа очередей сообщений с первого по третий соответственно, выходы дешифратора с первого по третий соединены с входами опроса блоков организации очереди сообщений с первого по третий соответственно, второй выход блока анализа очередей сообщений подключен к входу установки триггера запуска и к инверсному входу первого элемента И, выход которого подключен к входу сброса триггера запуска, прямой выход которого соединен с входом блока синхронизации, первый выход которого соединен с входом синхронизации первого буферного регистра, второй выход блока синхронизации подключен к прямому входу первого элемента И, выход четвертого элемента ИЛИ соединен с первым входом второго элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, дополнительно введены четвертый и пятый блоки организации очереди сообщений, блок анализа ситуаций, блок модификации маршрутных кодов, второй буферный регистр, коммутатор кода текущей трансляции, мультиплексор отказа, демультиплексор, второй коммутатор, третий коммутатор, четвертый коммутатор, триггер отказа, первый блок элементов И, второй блок элементов И, третий буферный регистр, одновибратор, причем четвертый и пятый информационные входы модуля подключены к информационным входам четвертого и пятого блоков организации очереди сообщений соответственно, первые выходы которых соединены с четвертым и пятым информационными входами мультиплексора соответственно, а вторые выходы подключены к четвертому и пятому входам блока анализа очередей сообщений соответственно, четвертый и пятый выходы дешифратора подключены к входам опроса четвертого и пятого блоков организации очереди сообщений соответственно, группы разрядов выхода мультиплексора со второй по пятую соединены с первыми информационными входами первого, второго и третьего коммутаторов и с первым входом четвертого коммутатора соответственно, выходы первого-четвертого коммутаторов подключены к информационным входам второго буферного регистра с первого по четвертый соответственно, выход первого буферного регистра соединен с информационным входом первого блока элементов И, выход которого соединен с первым информационным выходом модуля, первый выход блока синхронизации подключен к входу синхронизации второго буферного регистра, выход признака следующего участка маршрута которого подключен к первому входу блока анализа ситуаций и к первому входу блока модификации маршрутных кодов, выход признака текущего участка маршрута второго буферного регистра соединен с вторым входом блока модификации маршрутных кодов и с входом первого элемента ИЛИ, выход которого подключен к управляющему входу мультиплексора отказа, выходы кодов трансляций группы выходов маршрутного кода второго буферного регистра с первого по z-й (где z - максимальная длина участка маршрута) соединены с второй, четвертой, шестой, и т.д., (2z-2)-й, (2z)-й группами разрядов третьего входа блока модификации маршрутных кодов соответственно, с четвертой, шестой, восьмой, и т.д., (2z)-й, (2z+2)-й группами разрядов информационного входа второго блока элементов И соответственно, а также с информационными входами коммутатора кода текущей трансляции с первого по z-й соответственно, выход первого буферного регистра в объединении с выходами признака следующего участка маршрута и признака текущего участка маршрута второго буферного регистра подключены к (2z+3)-й группе разрядов информационного входа второго блока элементов И, выход которого соединен с информационным входом демультиплексора, выходы с первого по четвертый которого соединены с информационными выходами модуля со второго по пятый соответственно, выход статуса сообщения второго буферного регистра подключен к первой группе разрядов информационного входа второго блока элементов И и к второму входу блока анализа ситуаций, первый выход которого соединен с управляющими входами первого и второго коммутаторов и с вторым входом четвертого коммутатора, третий и четвертый входы которого подключены к второму выходу блока анализа ситуаций, выход конца маршрутного кода группы выходов маршрутного кода второго буферного регистра подключен к первой группе разрядов третьего входа блока модификации маршрутных кодов, к первому управляющему входу коммутатора кода текущей трансляции и к третьей группе разрядов информационного входа второго блока элементов И, вторая группа разрядов информационного входа которого соединена с шиной логического нуля, выходы признаков активности группы выходов маршрутного кода второго буферного регистра с первого по (z-1)-й соединены с третьей, пятой, и т.д., (2z-1)-й группами разрядов третьего входа блока модификации маршрутных кодов соответственно, с пятой, седьмой, и т.д., (2z+1)-й группами разрядов информационного входа второго блока элементов И соответственно, а также с управляющими входами коммутатора кода текущей трансляции со второго по z-й соответственно, выход которого подключен к адресному входу демультиплексора и к адресному входу мультиплексора отказа, z-й выход признака активности группы выходов маршрутного кода второго буферного регистра соединен с входом первого элемента ИЛИ и с третьим входом блока анализа ситуаций, первый и второй выходы которого подключены к первому, четвертому, пятому и к второму, третьему, шестому управляющим входам третьего коммутатора соответственно, входы состояния модуля с первого по четвертый подключены к входам мультиплексора отказа с первого по четвертый соответственно, выход которого соединен с четвертым входом блока анализа ситуаций, третий выход которого соединен с управляющим входом первого блока элементов И, третий выход блока синхронизации подключен к первому входу синхронизации блока модификации маршрутных кодов и к первому входу синхронизации блока анализа ситуаций, четвертый и пятый выходы которого соединены с первым и вторым входами настройки блока модификации маршрутных кодов соответственно, выходы с первого по третий которого подключены к вторым информационным входам коммутаторов с первого по третий соответственно, четвертый выход блока синхронизации соединен с вторым входом синхронизации блока анализа ситуаций, шестой выход которого подключен к управляющему входу второго блока элементов И, четвертый выход блока синхронизации подключен к второму входу синхронизации блока модификации маршрутных кодов, четвертый выход которого соединен с третьим информационным входом третьего коммутатора, второй выход блока синхронизации соединен с третьим входом синхронизации блока модификации маршрутных кодов, выход фатальной ситуации которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с седьмым выходом блока анализа ситуаций, а выход подключен к выходу фатальной ситуации модуля, восьмой выход блока анализа ситуаций соединен с информационным входом первого блока элементов И, с (2z+3)-й группой разрядов информационного входа второго блока элементов И, а также с входами сдвига блоков организации очереди сообщений с первого по пятый, вход отказа модуля подключен к входу установки триггера отказа, прямой выход которого подключен к выходам состояния модуля с первого по четвертый, первый выход блока анализа очередей сообщений соединен с информационным входом третьего буферного регистра, выход которого подключен к адресному входу мультиплексора и к входу дешифратора, инверсный выход триггера запуска подключен к входу одновибратора, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого подключен к входу синхронизации третьего буферного регистра, второй выход блока синхронизации соединен с вторым входом второго элемента И, первый и второй входы четвертого элемента ИЛИ подключены к третьему и шестому выходам блока анализа ситуаций соответственно.

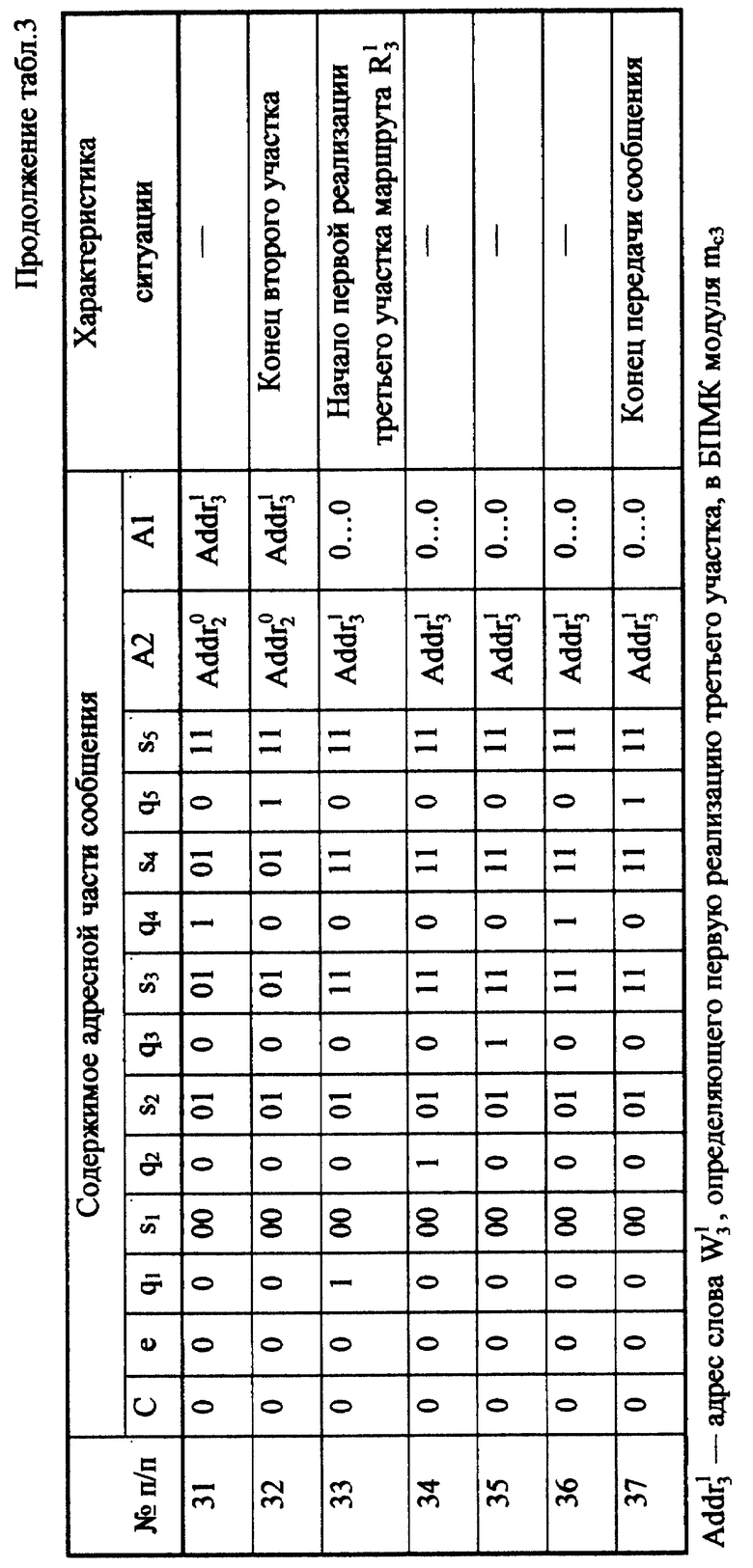

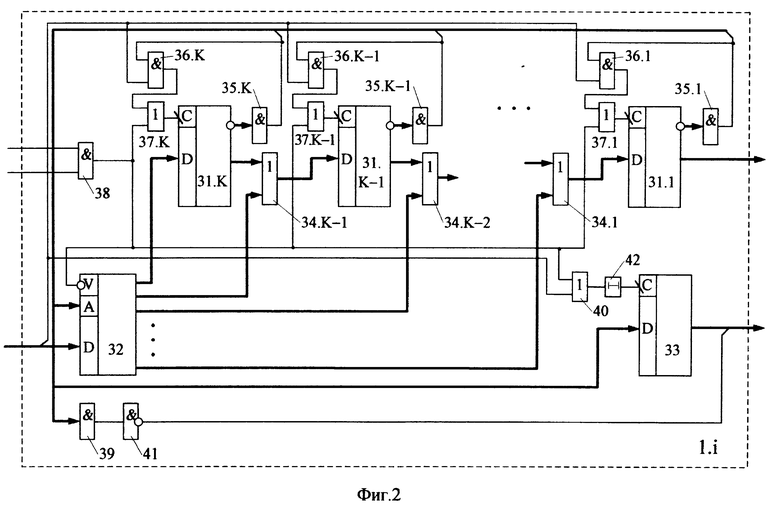

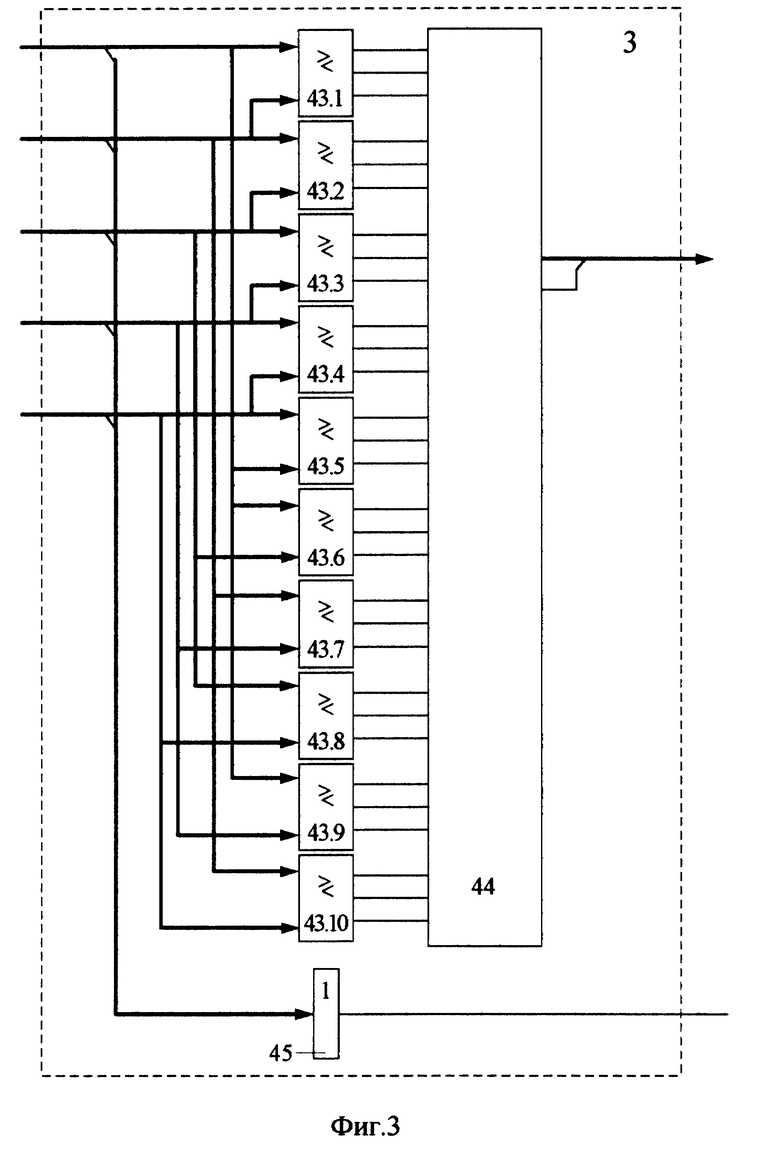

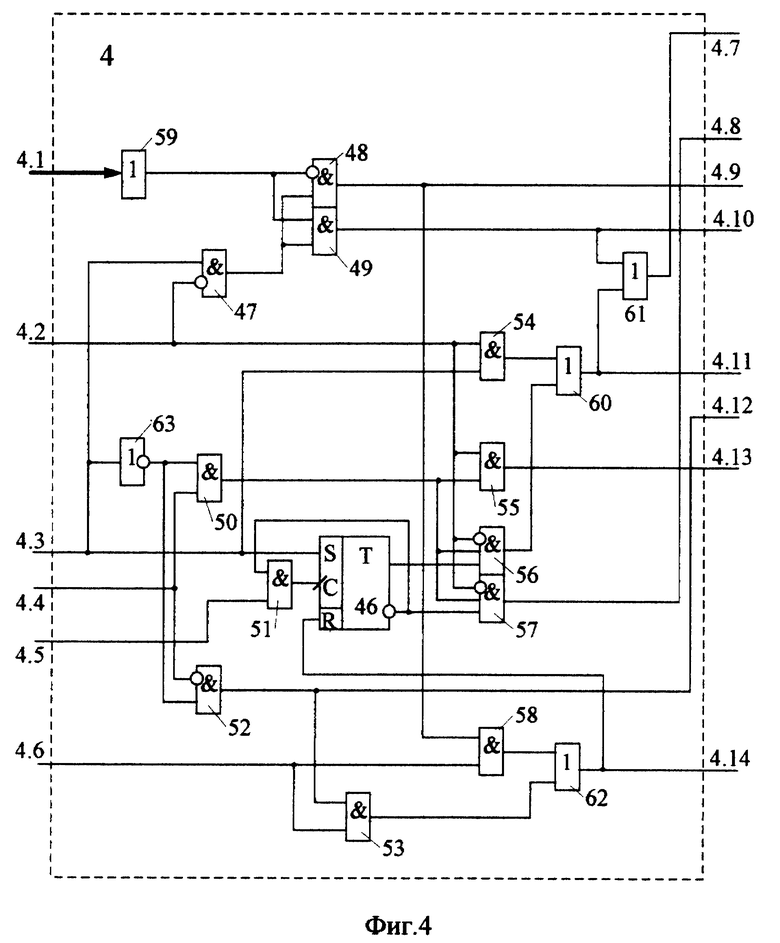

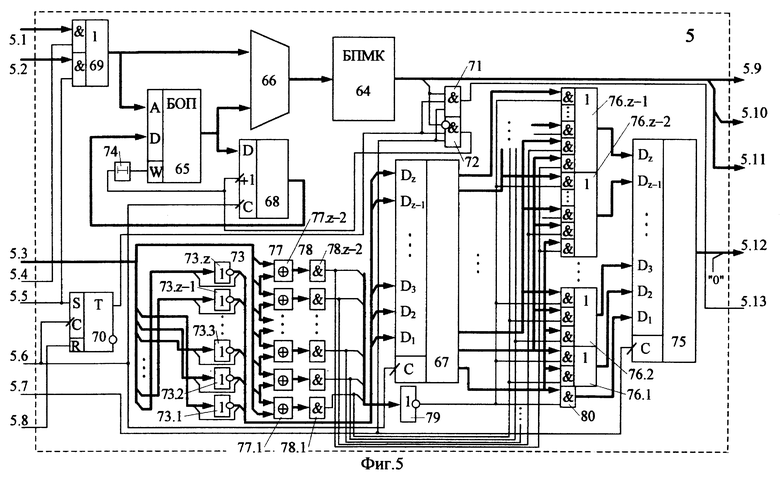

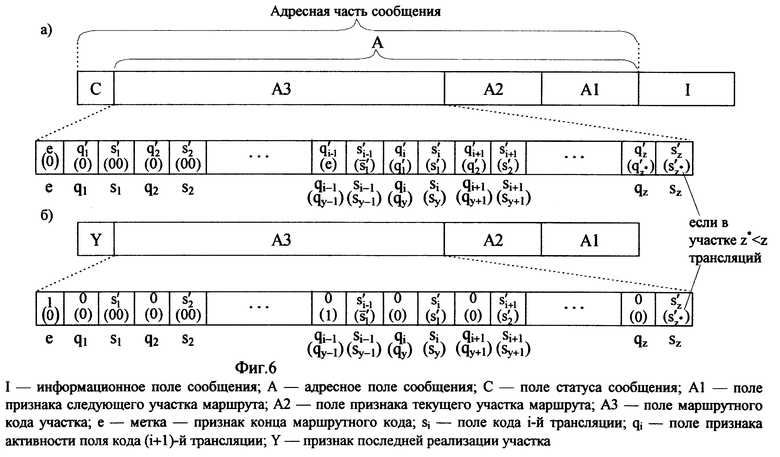

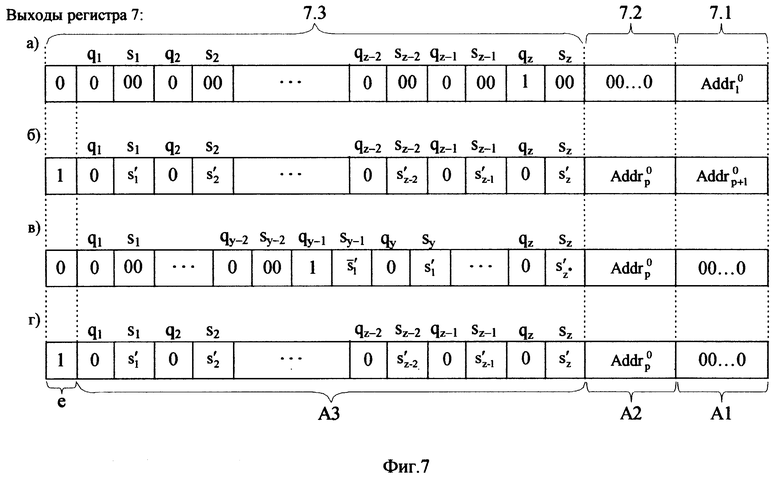

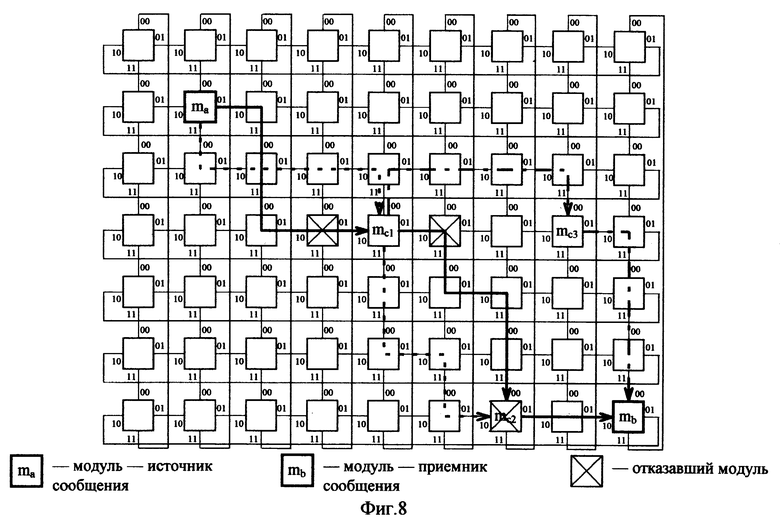

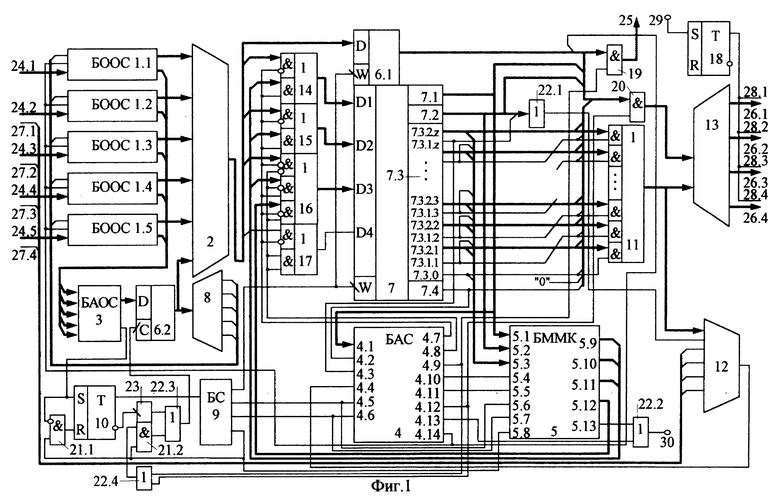

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема модуля матричной коммуникационной сети; на фиг. 2 представлена функциональная схема блока организации очереди сообщений; на фиг. 3 показана функциональная схема блока анализа очередей сообщений; на фиг. 4 приведена функциональная схема блока анализа ситуаций; на фиг. 5 изображена функциональная схема блока модификации маршрутных кодов; на фиг. 6а, 6б даны соответственно обобщенный формат сообщений и обобщенный формат слов, хранимых в блоке памяти маршрутных кодов; на фиг. 7 представлены форматы адресного поля сообщения в исходном состоянии (в начале передачи сообщения) (фиг. 7а), при переходе к промежуточному участку маршрута (фиг. 76), при переходе к конечному участку маршрута (фиг. 7в, 7г); на фиг. 8 отображен пример, поясняющий принципы формирования маршрута передачи сообщения в матричной коммуникационной сети при наличии отказавших модулей.

Общие особенности изобретения заключаются в следующем.

Предлагаемый модуль совместно с другими аналогичными модулями образует матричную коммуникационную сеть. Каждый модуль mj сети имеет 5 входных и 5 выходных (информационных) каналов. Один входной и один выходной каналы используются для подключения модуля к обслуживаемому им операционному устройству (ОУ). (В качестве ОУ может выступать произвольное устройство обработки информации, например процессорный элемент, микроконтроллер, терминал и т. п. ) Остальные каналы служат для обмена информацией с четырьмя соседними модулями сети.

Каждому из четырех выходных каналов модуля, используемых для подключения к соседним модулям, ставится в соответствие двухразрядный код (имя) вида x1x2 (x1x2= "00", "01", "10", "11"). При этом подключение информационных каналов различных модулей производится согласно следующему условию: выходной канал x1x2 текущего модуля подключается к тому входному каналу соседнего модуля, которому соответствует выходной канал  этого соседнего модуля. Иллюстрация данного условия представлена на фиг. 8. Каналы "00" модулей соответствуют направлению передачи информации "вверх" (по схеме фиг. 8), каналы "11" - направлению "вниз", каналы "01" и "10" - направлениям "вправо" и "влево" соответственно.

этого соседнего модуля. Иллюстрация данного условия представлена на фиг. 8. Каналы "00" модулей соответствуют направлению передачи информации "вверх" (по схеме фиг. 8), каналы "11" - направлению "вниз", каналы "01" и "10" - направлениям "вправо" и "влево" соответственно.

Взаимодействие модулей сети осуществляется на основе обмена сообщениями через другие (транзитные) модули. Маршруты передачи сообщений для каждой пары взаимодействующих модулей определяются заранее с учетом минимизации времени доставки сообщений, обеспечения равномерной загрузки каналов и транзитных модулей и т.д. Каждый маршрут R(ma--->mb) представляется в виде последовательности элементарных шагов (трансляций), каждый из которых соответствует передаче сообщения между двумя соседними модулями, входящими в маршрут.

Маршруты сообщений так же, как и в прототипе, отображаются в виде маршрутных кодов, которые включаются непосредственно в адресное поле сообщений и выполняют функцию идентификаторов модулей - приемников сообщений. Маршрутный код представляет собой последовательность трехразрядных полей T1•T2•...•Ti•...•Tr, где "•" - символ конкатенации. Поле Ti, i=1,2,.,r, соответствует i-й трансляции маршрута и содержит двухразрядное поле si и одноразрядное поле qi. Поле si (называемое полем кода i-й трансляции) задает направление выдачи сообщения на i-й трансляции (на i-м шаге передачи). Для этой цели в поле si фиксируется код ("00", "01", "10" или "11") выходного канала текущего модуля, канала, который соответствует требуемому направлению выдачи сообщения. Указанный код, обозначаемый через s'i, называется далее кодом i-й трансляции. Поле qi (именуемое полем признака активности поля кода (i+1)-й трансляции), в свою очередь, содержит признак q'i, который определяет активность поля кода (i+1)-й трансляции si+1: если qi="1", то следующий шаг передачи сообщения осуществляется в соответствии с кодом из поля si+1; если qi= "0", то поле si+1 на следующем шаге передачи сообщения не используется. Активность первой трансляции задается специальной меткой - признаком конца маршрутного кода. На каждом шаге передачи сообщения может быть использован только один из кодов полей {si}, поэтому единичное значение имеется не более чем в одном из полей {qi}. (В дальнейшем при отсутствии неоднозначности содержимое полей отождествляется с самими этими полями.)

Поскольку максимальная длина (число трансляций) маршрутов может быть произвольной, а максимальная разрядность маршрутного кода в формате сообщения ограничена некоторой величиной h, каждый маршрут R(ma--->mb) разбивается на участки. Каждый получаемый участок имеет длину не более  (включает не более z трансляций), где ] u [ - целая часть числа u. Число участков маршрута составляет

(включает не более z трансляций), где ] u [ - целая часть числа u. Число участков маршрута составляет  где r - длина маршрута R(ma--->mb);

где r - длина маршрута R(ma--->mb);  - ближайшее целое число, не меньшее числа u. Аналогичному разбиению на участки подвергается и код маршрута R(ma--->mb). Таким образом, каждый маршрут R = R(ma--->mb) представляется набором участков соответствующего ему маршрутного кода R(*)= R(*)(ma--->mb). Получаемые участки маршрутного кода R(*) распределяются между модулями, входящими в маршрут R. Распределение осуществляется таким образом, чтобы p-й участок R(*)p маршрутного кода R(*) соответствовал первому модулю p-го участка маршрута R. Для хранения участков маршрутных кодов в состав каждого модуля вводится блок памяти маршрутных кодов (БПМК).

- ближайшее целое число, не меньшее числа u. Аналогичному разбиению на участки подвергается и код маршрута R(ma--->mb). Таким образом, каждый маршрут R = R(ma--->mb) представляется набором участков соответствующего ему маршрутного кода R(*)= R(*)(ma--->mb). Получаемые участки маршрутного кода R(*) распределяются между модулями, входящими в маршрут R. Распределение осуществляется таким образом, чтобы p-й участок R(*)p маршрутного кода R(*) соответствовал первому модулю p-го участка маршрута R. Для хранения участков маршрутных кодов в состав каждого модуля вводится блок памяти маршрутных кодов (БПМК).

Процесс передачи сообщения по заданному маршруту R = R(ma--->mb) (когда необходимость динамической модификации маршрута отсутствует) в целом протекает так же, как и в прототипе, и включает два этапа.

На первом этапе осуществляется формирование адресного поля сообщения для очередного участка Rp+1 маршрута. Оно сводится к замене маршрутного кода R(*)p текущего (завершенного) участка Rp кодом R(*)p+1 очередного участка Rp+1 и определению признака участка Rp+2. Признак участка Rp+2 указывает на то, является ли участок Rp+1 последним участком реализуемого маршрута R или нет. Если этот признак нулевой, то участок Rp+1 считается последним (участок Rp+2 отсутствует). В противном случае существует участок Rp+2, и участок Rp+1, соответственно, не является последним. Маршрутный код R(*)p+1 вместе с признаком участка Rp+2 хранятся в БПМК текущего модуля в ячейке, адрес которой задается признаком (p+1)-го участка. В свою очередь, признак (p+2)-го участка определяет адрес ячейки БПМК первого модуля (p+2)-го участка, в которой содержится маршрутный код R(*)p+2 и признак (p+3)-го участка, и т.д. Адрес расположения маршрутного кода и признака первого (начального) участка маршрута задается в исходном формате сообщения.

На втором этапе происходит непосредственно передача сообщения в соответствии с маршрутным кодом R(*)p+1 участка Rp+1. На очередном ((i+1)-м) шаге передачи по значению поля qi="1" выделяется код очередной трансляции из поля si+1, в соответствии с которым сообщение выдается одному из соседних модулей. После выдачи сообщения поле qi становится нулевым, а единичное значение переносится в поле qi+1, определяющее активность поля кода (i+2)-й трансляции, и т.д. Участок Rp+1 считается завершенным после того, как единичное значение поступит в поле qz.

Если при передаче сообщения по маршруту R хотя бы один модуль некоторого участка оказывается отказавшим (передача сообщения через такой модуль невозможна), обмен информацией между модулями ma и mb становится невозможным. Восстановление такой возможности в прототипе может быть достигнуто только путем явного изменения и перепрограммирования маршрута R, что требует прекращения работы коммуникационной сети (а следовательно, и обслуживаемой этой сетью системы). Сказанное обусловливает резкое снижение гибкости и отказоустойчивости коммуникационной сети.

Предлагаемое изобретение позволяет осуществлять динамическое изменение маршрутов передачи сообщений при появлении отказавших модулей, не требуя прекращения работы сети и перепрограммирования маршрутов. С этой целью для каждого участка (или некоторых участков) каждого маршрута (или некоторых маршрутов) задаются несколько альтернативных реализаций (вариантов). Реализации участка выбираются таким образом, чтобы они содержали как можно меньше общих модулей. В этом случае отказ некоторого модуля текущей реализации p-го участка не будет нарушать возможность передачи сообщения в соответствии с другой реализацией p-го участка и для успешной доставки сообщения на p-м участке достаточно будет выполнить переход к новой реализации.

Каждой реализации p-го участка маршрута соответствует собственный маршрутный код. Коды реализаций p-го участка размещаются в БПМК первого модуля p-го участка, а обращение к ним осуществляется так же, как и к маршрутному коду p-го участка в прототипе - посредством признака p-го участка. Коды различных реализаций p-го участка могут закрепляться за различными модулями (разные реализации могут начинаться разными модулями).

Процесс передачи сообщения по некоторому маршруту R в сети на основе предлагаемого модуля при отсутствии на данном маршруте отказавших модулей практически не отличается от аналогичного процесса в прототипе. Передача сообщения на p-м участке, p=1,2,..., δ , осуществляется в соответствии с кодом его основной (базовой) реализации, используемой при отсутствии отказов (по умолчанию) и обозначаемой в дальнейшем как Rop. Переход к базовой реализации (p+1)-го участка (Rop+1) производится путем считывания ее маршрутного кода Ro(*)p+1 из БПМК ее первого модуля. Адресом при обращении к БПМК является признак (p+1)-го участка.

Если же при передаче сообщения на p-м участке обнаруживается отказавший модуль, то выполняются следующие действия.

1. Сообщение возвращается начальному модулю p-го участка как квитанция о невозможности доставки сообщения в соответствии с кодом текущей (k-й) реализации Rkp p-го участка.

Для того чтобы обеспечить возврат сообщения требуемому модулю, используется маршрутный код k-й реализации p-го участка (Rk(*)p), в котором порядок следования полей {si} изменен на обратный, а соответствующие этим полям коды трансляций взяты с инверсией ("инвертированный" маршрутный код). Учитывая условие подключения информационных каналов различных модулей, инвертирование кода в поле si обеспечивает передачу сообщения в обратном направлении. Если, например, сообщение было передано от некоторого модуля mj соседнему модулю ml в соответствии с кодом s'i="10" ("00", "01", "11"), то выдача сообщения модулем ml в соответствии с кодом  ="01" ("11", "10", "00") приведет к возврату сообщения в модуль mj, (см. фиг. 8).

="01" ("11", "10", "00") приведет к возврату сообщения в модуль mj, (см. фиг. 8).

2. Производится обращение к БПМК первого модуля p-го участка.

В результате из БПМК считывается маршрутный код следующей, т.е. (k+1)-й реализации p-го участка (Rk+1(*)p). Адрес расположения этого кода в БПМК Addrk+1p образуется в результате суммирования адреса для базовой реализации p-го участка (признака p-го участка) Addrop и номера текущей (активной) реализации (k) p-го участка, предварительно увеличенного на 1:

Addrk+1p = Addrop + k + 1.

Адрес Addrop фиксируется непосредственно в формате сообщения на p-м участке маршрута (будучи считанным из БПМК вместе с маршрутным кодом p-го участка и признаком (p+1)-го участка). Для хранения номеров активных реализаций различных участков в состав каждого модуля вводится блок оперативной памяти (БОП).

3. Выполняется попытка передачи сообщения в соответствии с кодом Rk+1(*)p.

В случае если эта попытка удачна, осуществляется переход к (p+1)-му участку маршрута, при этом активной для p-го участка в дальнейшем становится (k+1)-я реализация (ее номер сохраняется в БОП первого модуля p-го участка). Если же попытка передачи сообщения снова является неудачной, то сообщение вновь возвращается первому модулю p-го участка и производится переход к (k+2)-й реализации p-го участка. Если обнаруживается отказ второго модуля очередной реализации, то возврат сообщения не требуется: в этом случае сразу осуществляется переход к следующей реализации p-го участка. Подобные переходы будут выполняться до тех пор, пока не будет удовлетворено одно из двух следующих условий:

1) найдена реализация p-го участка, не содержащая отказавших модулей;

2) исчерпаны все возможные реализации.

В случае нахождения некоторой реализации Rk+wp, обеспечивающей доставку сообщения на p-м участке маршрута, в БОП первого модуля p-го участка будет зафиксирован номер этой реализации (k+w) и все последующие сообщения от модуля ma модулю mb при прохождении p-го участка будут использовать маршрутный код (k+w)-й реализации по умолчанию. Таким образом будет обеспечена динамическая модификация p-го участка маршрута. Если в дальнейшем на (k+w)-й реализации p-го участка появится отказавший модуль, то аналогично рассмотренному будет выполнен переход к некоторой (k+u)-й реализации (u>w), и т.д., до исчерпания возможных реализаций. В случае исчерпания возможных реализаций будет индицирована фатальная ситуация (передача сообщения невозможна). При возникновении фатальной ситуации аналогично прототипу необходим останов коммуникационной сети (и обслуживаемой ей системы) и перепрограммирование некоторых маршрутов взаимодействия модулей. После перепрограммирования возможно возобновление работы сети.

Для исключения фатальной ситуации в случае отказа модуля - приемника сообщения каждое ОУ может быть одновременно подключено к двум (или более) модулям. В этом случае при отказе одного из них обслуживание ОУ будет осуществляться другим модулем, операционное устройство которого, в свою очередь, может быть передано для обслуживания третьему модулю, и т.д. Доставка сообщения новому модулю - приемнику может быть организована с использованием дополнительной реализации конечного участка маршрута (конечный модуль которой соответствует новому модулю - приемнику сообщения).

Модуль матричной коммуникационной сети (фиг. 1) содержит первый 1.1, второй 1.2 и третий 1.3 блоки организации очереди сообщений, мультиплексор 2, блок 3 анализа очередей сообщений, первый буферный регистр 6.1, дешифратор 8, блок 9 синхронизации, триггер 10 запуска, первый коммутатор 14, первый элемент И 21.1, второй элемент И 21.2, первый элемент ИЛИ 22.1, второй элемент ИЛИ 22.2, третий элемент ИЛИ 22.3, четвертый элемент ИЛИ 22.4, причем информационные входы 24.1-24.3 модуля подключены к информационным входам блоков 1.1-1.3 организации очереди сообщений соответственно, первые выходы которых соединены с информационными входами мультиплексора 2 с первого по третий соответственно, первая группа разрядов выхода которого соединена с информационным входом буферного регистра 6.1, вторые выходы блоков 1.1-1.3 организации очереди сообщений подключены к входам блока 3 анализа очередей сообщений с первого по третий соответственно, выходы дешифратора 8 с первого по третий соединены с входами опроса блоков 1.1-1.3 организации очереди сообщений соответственно, второй выход блока 3 анализа очередей сообщений подключен к входу установки триггера 10 запуска и к инверсному входу элемента И 21.1, выход которого подключен к входу сброса триггера 10 запуска, прямой выход которого соединен с входом блока 9 синхронизации, первый выход которого соединен с входом синхронизации буферного регистра 6.1, второй выход блока 9 синхронизации подключен к прямому входу элемента И 21.1, выход элемента ИЛИ 22.4 соединен с первым входом элемента И 21.2, выход которого подключен к первому входу элемента ИЛИ 22.3, а также дополнительно введенные четвертый 1.4 и пятый 1.5 блоки организации очереди сообщений, блок 4 анализа ситуаций, блок 5 модификации маршрутных кодов, 4 второй буферный регистр 7, коммутатор 11 кода текущей трансляции, мультиплексор 12 отказа, демультиплексор 13, второй коммутатор 15, третий коммутатор 16, четвертый коммутатор 17, триггер 18 отказа, первый блок элементов И 19, второй блок элементов И 20, третий буферный регистр 6.2, одновибратор 23, причем информационные входы 24.4 и 24.5 модуля подключены к информационным входам блоков 1.4 и 1.5 организации очереди сообщений соответственно, первые выходы которых соединены с четвертым и пятым информационными входами мультиплексора 2 соответственно, а вторые выходы подключены к четвертому и пятому входам блока 3 анализа очередей сообщений соответственно, четвертый и пятый выходы дешифратора 8 подключены к входам опроса блоков 1.4 и 1.5 организации очереди сообщений соответственно, группы разрядов выхода мультиплексора 2 со второй по пятую (пятая группа - одноразрядная) соединены с первыми информационными входами коммутаторов 14, 15 и 16 и с первым входом коммутатора 17 соответственно, выходы коммутаторов 14-17 подключены к информационным входам буферного регистра 7 с первого по четвертый соответственно, выход буферного регистра 6.1 соединен с информационным входом блока элементов И 19, выход которого соединен с информационным выходом 25 модуля, первый выход блока 9 синхронизации подключен к входу синхронизации буферного регистра 7, выход 7.1 признака следующего участка маршрута которого подключен к первому входу (4.1) блока 4 анализа ситуаций и к первому входу (5.1) блока 5 модификации маршрутных кодов, выход 7.2 признака текущего участка маршрута буферного регистра 7 соединен с вторым входом (5.2) блока 5 модификации маршрутных кодов и с входом элемента ИЛИ 22.1, выход которого подключен к управляющему входу мультиплексора 12 отказа, выходы 7.3.2.1, 7.3.2.2, 7.3.2.3,..., 7.3.2.z-1, 7.3.2.z кодов трансляций группы выходов 7.3 маршрутного кода буферного регистра 7 (где z - максимальная длина участка маршрута) соединены с второй, четвертой, шестой, и т.д., (2z-2)-й, (2z)-й группами разрядов третьего входа (5.3) блока 5 модификации маршрутных кодов соответственно, с четвертой, шестой, восьмой, и т.д., (2z)-й, (2z+2)-й группами разрядов информационного входа блока элементов И 20 соответственно, а также с информационными входами коммутатора 11 кода текущей трансляции с первого по z-й соответственно, выход буферного регистра 6.1 в объединении с выходами 7.1 признака следующего участка маршрута и 7.2 признака текущего участка маршрута буферного регистра 7 подключены к (2z+3)-й группе разрядов информационного входа блока элементов И 20, выход которого соединен с информационным входом демультиплексора 13, выходы с первого по четвертый которого соединены с информационными выходами 26.1-26.4 модуля соответственно, выход 7.4 статуса сообщения буферного регистра 7 подключен к первой (одноразрядной) группе разрядов информационного входа блока элементов И 20 и к второму входу (4.2) блока 4 анализа ситуаций, первый выход (4.7) которого соединен с управляющими входами коммутаторов 14, 15 и с вторым входом коммутатора 17, третий и четвертый входы которого подключены к второму выходу (4.8) блока 4 анализа ситуаций, выход 7.3.0 конца маршрутного кода группы выходов 7.3 маршрутного кода буферного регистра 7 подключен к первой (одноразрядной) группе разрядов третьего входа (5.3) блока 5 модификации маршрутных кодов, к первому управляющему входу коммутатора 11 кода текущей трансляции и к третьей (одноразрядной) группе разрядов информационного входа блока элементов И 20, вторая (одноразрядная) группа разрядов информационного входа которого соединена с шиной логического нуля, выходы 7.3.1.1, 7.3.1.2,. . . , 7.3.1.z-1 признаков активности группы выходов 7.3 маршрутного кода буферного регистра 7 соединены с третьей, пятой, и т.д., (2z-1)-й (одноразрядными) группами разрядов третьего входа (5.3) блока 5 модификации маршрутных кодов соответственно, с пятой, седьмой, и т. д. , (2z+1)-й (одноразрядными) группами разрядов информационного входа блока элементов И 20 соответственно, а также с управляющими входами коммутатора 11 кода текущей трансляции со второго по z-й соответственно, выход которого подключен к адресному входу демультиплексора 13 и к адресному входу мультиплексора 12 отказа, выход 7.3.1.z признака активности группы выходов 7.3 маршрутного кода буферного регистра 7 соединен с входом элемента ИЛИ 22.1 и с третьим входом (4.3) блока 4 анализа ситуаций, первый (4.7) и второй (4.8) выходы которого подключены к первому, четвертому, пятому и к второму, третьему, шестому управляющим входам коммутатора 16 соответственно, входы 27.1-27.4 состояния модуля подключены к входам мультиплексора 12 отказа с первого по четвертый соответственно, выход которого соединен с четвертым входом (4.4) блока 4 анализа ситуаций, третий выход (4.9) которого соединен с управляющим входом блока элементов И 19, третий выход блока 9 синхронизации подключен к первому входу (5.6) синхронизации блока 5 модификации маршрутных кодов и к первому входу (4.5) синхронизации блока 4 анализа ситуаций, четвертый (4.10) и пятый (4.11) выходы которого соединены с первым (5.4) и вторым (5.5) входами настройки блока 5 модификации маршрутных кодов соответственно, выходы с первого по третий (5.9-5.11) которого подключены к вторым информационным входам коммутаторов 14-16 соответственно, четвертый выход блока 9 синхронизации соединен с вторым входом (4.6) синхронизации блока 4 анализа ситуаций, шестой выход (4.12) которого подключен к управляющему входу блока элементов И 20, четвертый выход блока 9 синхронизации подключен к второму входу (5.7) синхронизации блока 5 модификации маршрутных кодов, четвертый выход (5.12) которого соединен с третьим информационным входом коммутатора 16, второй выход блока 9 синхронизации соединен с третьим входом (5.8) синхронизации блока 5 модификации маршрутных кодов, выход (5.13) фатальной ситуации которого подключен к первому входу элемента ИЛИ 22.2, второй вход которого соединен с седьмым выходом (4.13) блока 4 анализа ситуаций, а выход подключен к выходу 30 фатальной ситуации модуля, восьмой выход (4.14) блока 4 анализа ситуаций соединен с информационным входом блока элементов И 19, с (2z+3)-й группой разрядов информационного входа блока элементов И 20, а также с входами сдвига блоков 1.1-1.5 организации очереди сообщений, вход 29 отказа модуля подключен к входу установки триггера 18 отказа, прямой выход которого подключен к выходам 28.1-28.4 состояния модуля, первый выход блока 3 анализа очередей сообщений соединен с информационным входом буферного регистра 6.2, выход которого подключен к адресному входу мультиплексора 2 и к входу дешифратора 8, инверсный выход триггера 10 запуска подключен к входу одновибратора 23, выход которого соединен с вторым входом элемента ИЛИ 22.3, выход которого подключен к входу синхронизации буферного регистра 6.2, второй выход блока 9 синхронизации соединен с вторым входом элемента И 21.2, первый и второй входы элемента ИЛИ 22.4 подключены к третьему (4.9) и шестому (4.12) выходам блока 4 анализа ситуаций соответственно.

Блок 1. i организации очереди сообщений, i=1,2,3,4,5, (фиг. 2) содержит регистры 31.1- 31. K (где K - максимальная длина очереди сообщений), демультиплексор 32, регистр 33 длины очереди, блоки элементов ИЛИ 34.1-34.K-1, элементы И 35.1-35.K, 36.1-36.K, элементы ИЛИ 37.1-37.K, элементы И 38, 39, элемент ИЛИ 40, элемент НЕ 41, элемент 42 задержки, причем старшие разряды информационного входа блока подключены к информационному входу демультиплексора 32, выходы с первого по (K-1)-й которого соединены с первыми входами блоков элементов ИЛИ 34.1-34.K-1 соответственно, выходы которых соединены с информационными входами регистров 31.1-31.K-1 соответственно, младший разряд информационного входа блока подключен к первому входу элемента ИЛИ 40 и к первым входам элементов И 36.1-36.K, выходы которых подключены к первым входам элементов ИЛИ 37.1-37. K соответственно, выходы которых соединены с входами синхронизации регистров 31.1-31.K соответственно, инверсные выходы которых соединены с входами элементов И 35.1-35.K соответственно, выходы которых подключены к вторым входам элементов И 36.1-36.K соответственно, к адресному входу демультиплексора 32, к информационному входу регистра 33 длины очереди и к входу элемента И 39, выход которого соединен с входом элемента НЕ 41, выход которого соединен с (K+1)-м (старшим) разрядом второго выхода блока, входы опроса и сдвига которого подключены соответственно к первому и второму входам элемента И 38, выход которого соединен с вторыми входами элементов ИЛИ 37.1-37.K и с управляющим входом (V) демультиплексора 32, K-й выход которого соединен с информационным входом регистра 31.K, прямые выходы регистров 31.2-31.K подключены к вторым входам блоков элементов ИЛИ 34.1 -34.K-1 соответственно, выход элемента И 38 соединен с вторым входом элемента ИЛИ 40, выход которого подключен к входу элемента 42 задержки, выход которого соединен с входом синхронизации регистра 33 длины очереди, выход которого соединен с К младшими разрядами второго выхода блока, первый выход которого подключен к прямому выходу регистра 31.1.

Блок 3 анализа очередей сообщений (фиг. 3) содержит первый 43.1, второй 43.2, третий 43.3, четвертый 43.4, пятый 43.5, шестой 43.6, седьмой 43.7, восьмой 43.8, девятый 43.9, десятый 43.10 элементы сравнения, узел 44 постоянной памяти, элемент ИЛИ 45, причем K младших разрядов первого входа блока подключены к первым входам элементов 43.1, 43.5, 43.6, 43.9 сравнения, K младших разрядов второго входа блока подключены к первым входам элементов 43.2, 43.7, 43.10 сравнения и к второму входу элемента 43.1 сравнения, K младших разрядов третьего входа блока подключены к первым входам элементов 43.3, 43.8 сравнения и к вторым входам элементов 43.2, 43.6 сравнения, K младших разрядов четвертого входа блока подключены к первому входу элемента 43.4 сравнения и к вторым входам элементов 43.3, 43.7, 43.9 сравнения, K младших разрядов пятого входа блока подключены к вторым входам элементов 43.4, 43.5, 43.8, 43.10 сравнения, группы выходов элементов 43.1-43.10 сравнения соединены с соответствующими группами входов узла 44 постоянной памяти, выход которого соединен с первым выходом блока, (K+1)-е (старшие) разряды входов блока с первого по пятый подключены к входу элемента ИЛИ 45, выход которого соединен с вторым выходом блока.

Блок 4 анализа ситуаций (фиг. 4) содержит триггер 46, первый 47, второй 48, третий 49, четвертый 50, пятый 51, шестой 52, седьмой 53, восьмой 54, девятый 55, десятый 56, одиннадцатый 57, двенадцатый 58 элементы И, первый 59, второй 60, третий 61, четвертый 62 элементы ИЛИ и элемент НЕ 63, причем третий вход (4.3) блока подключен к первому входу элемента И 47, выход которого подключен к первым входам элементов И 48, 49, выходы которых соединены с третьим (4.9) и четвертым (4.10) выходами блока соответственно, первый вход (4.1) блока подключен к входу элемента ИЛИ 59, выход которого соединен с вторыми входами элементов И 48, 49, третий вход (4.3) блока соединен с входом установки (S-входом) триггера 46 и с входом элемента НЕ 63, выход которого подключен к первому входу элемента И 50, первый вход (4.5) синхронизации блока соединен с первым входом элемента И 51, выход которого подключен к входу синхронизации триггера 46, инверсный выход которого подключен к второму входу элемента И 51, выход элемента НЕ 63 соединен с первым входом элемента И 52, выход которого соединен с шестым выходом (4.12) блока и с первым входом элемента И 53, второй вход (4.2) блока подключен к второму входу элемента И 47 и к первому входу элемента И 54, выход которого подключен к первому входу элемента ИЛИ 60, выход которого соединен с первым входом элемента ИЛИ 61, второй вход и выход которого подключены соответственно к выходу элемента И 49 и к первому выходу (4.7) блока, второй вход (4.2) блока соединен с первыми входами элементов И 55-57, третий вход (4.3) блока подключен к второму входу элемента И 54, четвертый вход (4.4) блока соединен с вторым входом элемента И 52 и с вторым входом элемента И 50, выход которого соединен с вторыми входами элементов И 56, 57 и с вторым входом элемента И 55, выход которого подключен к седьмому выходу (4.13) блока, второй вход (4.6) синхронизации блока подключен к первому входу элемента И 58 и к второму входу элемента И 53, выход которого соединен с первым входом элемента ИЛИ 62, выход которого соединен с восьмым выходом (4.14) блока, выход элемента И 48 подключен к второму входу элемента И 58, выход которого подключен к второму входу элемента ИЛИ 62, выход которого соединен с входом сброса (R) триггера 46, инверсный выход которого соединен с третьим входом элемента И 57, выход которого подключен к второму выходу (4.8) блока, прямой выход триггера 46 соединен с третьим входом элемента И 56, выход которого соединен с вторым входом элемента ИЛИ 60, выход которого соединен с пятым выходом (4.11) блока.

Блок 5 модификации маршрутных кодов (фиг. 5) содержит блок 64 памяти маршрутных кодов (БПМК), блок 65 оперативной памяти (БОП), сумматор 66, первый регистр 67, счетчик 68, коммутатор 69, триггер 70, первый 71 и второй 72 элементы И, группу блоков элементов НЕ 73.1-73.z (73), элемент 74 задержки, второй регистр 75, группу коммутаторов 76.1-76.z-1, группу блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 77.1-77. z-2, группу элементов И 78.1-78.z-2, элемент ИЛИ-НЕ 79, блок элементов И 80, причем первый (5.1) и второй (5.2) входы блока соединены с первым и вторым информационными входами коммутатора 69 соответственно, выход которого подключен к первому входу сумматора 66 и к адресному входу блока 65 оперативной памяти, выход которого соединен с информационным входом счетчика 68 и с вторым входом сумматора 66, выход которого соединен с адресным входом блока 64 памяти маршрутных кодов, первая, вторая и третья группы разрядов выхода которого подключены к первому (5.9), второму (5.10) и третьему (5.11) выходам блока соответственно, старший разряд выхода блока 64 памяти маршрутных кодов соединен с первым входом элемента И 71 и с первым входом элемента И 72, выход которого соединен с входом элемента 74 задержки и с входом инкремента счетчика 68, выход которого подключен к информационному входу блока 65 оперативной памяти, вход записи которого, подключен к выходу элемента 74 задержки, первый (5.4) и второй (5.5) входы настройки блока соединены с первым и вторым управляющими входами коммутатора 69 соответственно, вторая, четвертая, и т.д., (2z-2)-я, (2z)-я группы разрядов третьего входа (5.3) блока подключены к входам блоков элементов НЕ 73. z, 73.z-1,..., 73.2, 73.1 соответственно, выходы которых соединены с z-м, (z-1)-M, и т.д., вторым, первым информационными входами регистра 67 соответственно, первая, третья, и т.д., (2z-3)-я, (2z-1)-я (одноразрядные) группы разрядов третьего (5.3) входа блока подключены к z-му, (z-1)-му, и т. д., второму, первому информационным входам регистра 67 соответственно, второй вход (5.5) настройки блока соединен с входом установки (S-входом) триггера 70, прямой выход которого соединен с вторыми входами элементов И 71, 72, первый вход (5.6) синхронизации блока подключен к входу синхронизации триггера 70, к входу синхронизации счетчика 68 и к входу синхронизации регистра 67, второй вход (5.7) синхронизации блока подключен к третьему входу элемента И 72 и к третьему входу элемента И 71, выход которого соединен с выходом (5.13) фатальной ситуации блока, третий вход (5.8) синхронизации которого подключен к входу сброса (R-входу) триггера 70, вторая, четвертая, шестая, и т.д., (2z-4)-я группы разрядов третьего (5.3) входа блока подключены к первым входам блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 77.1, 77.2, 77.3, ..., 77.z-2 соответственно, четвертая, шестая, восьмая, и т.д., (2z-2)-я группы разрядов третьего (5.3) входа блока соединены с вторыми входами блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 77.1, 77.2, 77.3,..., 77.z-2 соответственно, выходы которых подключены к входам элементов И 78.1, 78.2, 78.3, . . . , 78. z-2 соответственно, выходы которых соединены с входом элемента ИЛИ-НЕ 79, выход которого соединен с первыми управляющими входами коммутаторов 76.1-76.z-1 и с управляющим входом блока элементов И 80, выход которого подключен к первому информационному входу регистра 75, выход которого соединен с младшей группой разрядов четвертого выхода (5.12) блока, старший разряд четвертого выхода (5.12) блока подключен к шине логического нуля, второй вход (5.7) синхронизации блока соединен с входом синхронизации регистра 75, выходы элементов И 78.1, 78.2, 78.3,..., 78.z-2 соединены соответственно с вторыми управляющими входами коммутаторов 76.1-76.z-1, с третьими управляющими входами коммутаторов 76.2- 76.z-1, с четвертыми управляющими входами коммутаторов 76.3-76. z-1, и т.д., с (z-1)-ми управляющими входами коммутаторов 76. z-2, 76. z-1, первый выход регистра 67 подключен к первым информационным входам коммутаторов 76.1-76. z-2 и к информационному входу блока элементов И 80, второй, третий, и т.д., (z-2)-й, (z-1)-й выходы регистра 67 соединены соответственно с вторыми информационными входами коммутаторов 76.1-76.z-2, с третьими информационными входами коммутаторов 76.2-76. z-2, и т.д., с (z-2)-ми информационными входами коммутаторов 76.z-3, 76.z-2, с (z-1)-м информационным входом коммутатора 76.z-2, выходы регистра 67 со второго по z-й подключены к информационным входам коммутатора 76.z-1 с первого по (z-1)-й соответственно, выходы коммутаторов 76.1-76.z-1 соединены с информационными входами регистра 75 со второго по z-й соответственно.

Назначение элементов и блоков модуля матричной коммуникационной сети состоит в следующем.

Блоки 1.1-1.5 организации очереди сообщений (БООС) предназначены для приема сообщений с входов 24.1-24.5 модуля соответственно, временного хранения и выдачи сообщений в порядке поступления на первый-пятый информационные входы мультиплексора 2 соответственно.

Мультиплексор 2 служит для передачи сообщений из БООС 1.1-1.5 в регистры 6.1 и 7 через коммутаторы 14-17.

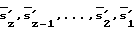

Блок 3 анализа очередей сообщений (БАОС) обеспечивает выбор БООС, содержащего наибольшую очередь сообщений. Функционирование БАОС описывается табл. 1, где через Li, i=1,2,3,4,5, обозначены длины очередей сообщений в БООС 1. i.

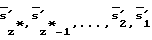

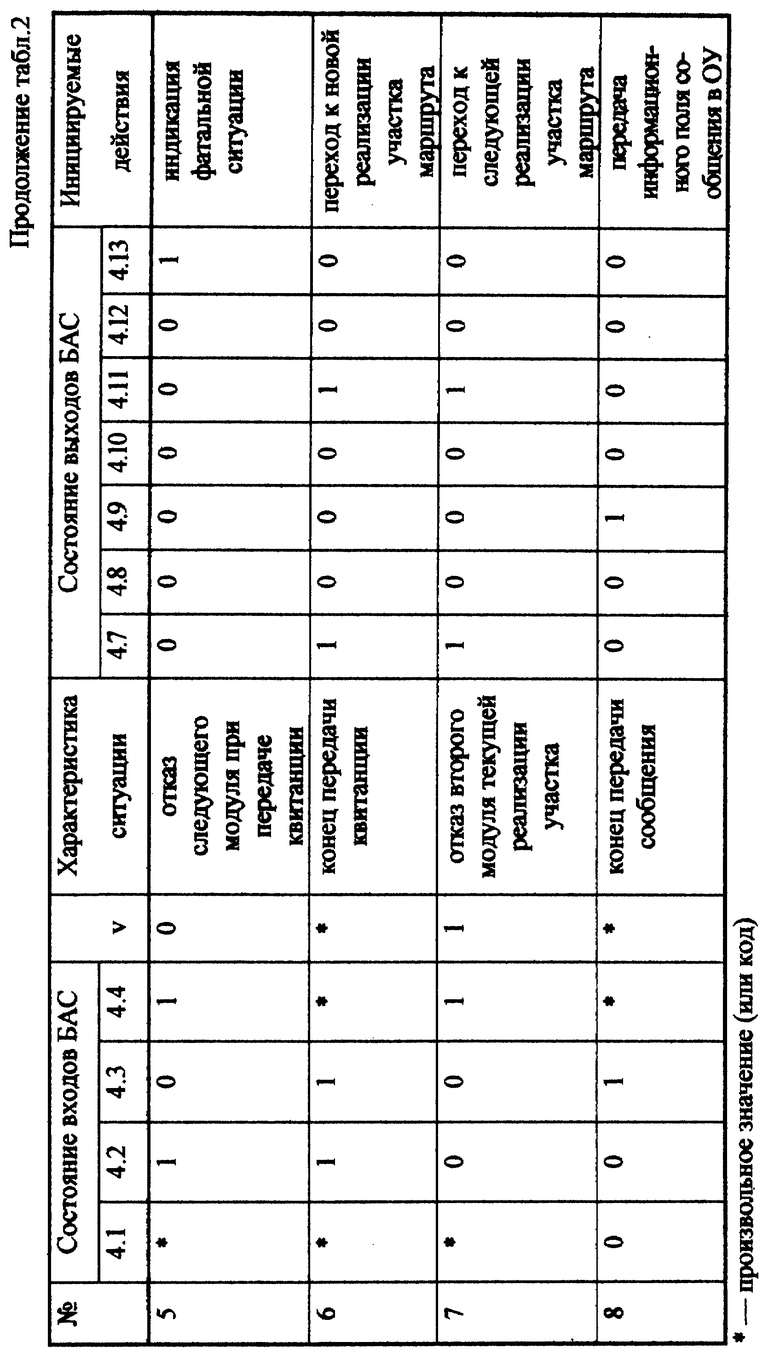

Блок 4 анализа ситуаций (БАС) предназначен для анализа адресной части сообщений и организации работы модуля в соответствии со значениями ее полей. Функционирование БАС определяется табл. 2, где через v обозначен сигнал - признак перехода к следующему участку маршрута, формируемый на прямом выходе триггера 46 (фиг. 4).

Блок 5 модификации маршрутных кодов (БММК) служит для формирования маршрутного кода p-го участка и признаков p-го и (p+1)-го участков маршрута при переходе к p-му участку или к очередной реализации p-го участка, а также для формирования инвертированного маршрутного кода, обеспечивающего возврат сообщения первому модулю p-го участка при отказе очередного модуля.

Буферный регистр 6.1 обеспечивает хранение информационного поля сообщения во время его обработки.

Буферный регистр 6.2 служит для фиксации кода выбора БООС, формируемого в БАОС 3, на время обработки сообщения.

Буферный регистр 7 введен для хранения адресной части сообщения во время его обработки.

Дешифратор 8 служит для преобразования кода выбора БООС, поступающего с выхода регистра 6.2, в соответствующий унитарный код.

Блок 9 синхронизации (БС) предназначен для формирования четырех сдвинутых друг относительно друга последовательностей импульсов синхронизации t1, t2, t3 и t4, синхронизирующих работу различных узлов модуля. Формирование импульсов синхронизации на выходах БС 9 разрешено при наличии на его входе единичного сигнала. При нулевом сигнале на входе работа БС 9 запрещена. Первый импульс t1 появляется на соответствующем выходе блока 9 с задержкой Δτ1 относительно момента подачи единичного сигнала на его вход. Величина Δτ1определяется длительностью промежутка от момента возникновения единичного сигнала на втором выходе БАОС 3 до момента поступления полей обрабатываемого сообщения на информационные входы регистров 6.1 и 7.

Триггер 10 запуска использован для управления блоком 9 синхронизации.

Коммутатор 11 кода текущей трансляции введен с целью выделения кода очередной трансляции s'i из маршрутного кода текущего участка.

Мультиплексор 12 отказа служит для передачи сигналов состояния соседних модулей с входов 27.1-27.4 модуля на вход 4.4 блока 4. Передача сигналов с первого-четвертого входов мультиплексора 12 на его выход возможна только при наличии единичного сигнала на его управляющем входе. Если же на управляющем входе мультиплексора 12 присутствует сигнал логического нуля, то на его выходе будет нулевой сигнал независимо от уровня сигналов на его первом-четвертом входах.

Демультиплексор 13 предназначен для передачи сообщений на один из выходов 26.1-26.4 модуля и далее одному из соседних модулей в зависимости от кода текущей трансляции на выходе коммутатора 11.

Коммутатор 14 обеспечивает подключение первого информационного входа регистра 7 к выходу мультиплексора 2 или к выходу 5.9 блока 5 в зависимости от уровня сигнала на выходе 4.7 блока 4.

Коммутатор 15 обеспечивает подключение второго информационного входа регистра 7 к выходу мультиплексора 2 или к выходу 5.10 блока 5 в зависимости от уровня сигнала на выходе 4.7 блока 4.

Коммутатор 16 служит для подключения третьего информационного входа регистра 7 либо к выходу мультиплексора 2, либо к выходу 5.11 блока 5, либо к выходу 5.12 блока 5 в зависимости от уровня сигнала на выходах 4.7 и 4.8 блока 4.

Коммутатор 17 предназначен для передачи сигнала статуса сообщения (С) с выхода мультиплексора 2 на четвертый информационный вход регистра 7 при приеме сообщения в регистры 6.1 и 7, а также для формирования нового значения сигнала статуса С в режимах возврата сообщения и перехода к следующему участку или к очередной реализации участка маршрута.

Триггер 18 отказа служит для индикации текущего состояния модуля. Нулевое состояние триггера 18 индицирует работоспособность модуля, единичное состояние указывает на отказ модуля. Контроль работоспособности модуля и, соответственно, переключение триггера 18 в единичное состояние обеспечивается внешними средствами контроля, воздействующими на этот триггер через вход 29 модуля. Организация указанных средств с точки зрения функционирования предлагаемого модуля не является существенной и поэтому они не отражены на фиг. 1.

Блок элементов И 19 предназначен для блокировки передачи информационного поля сообщения из регистра 6.1 на выход 25 модуля.

Блок элементов И 20 служит для блокировки выдачи сообщения с выходов регистров 6.1 и 7 на информационный вход демультиплексора 13.

Элемент И 21.1 служит для запрещения передачи импульса синхронизации t4 со второго выхода блока 9 на вход сброса триггера 10.

Элемент И 21.2 введен с целью блокировки передачи импульса синхронизации t4 со второго выхода блока 9 на первый вход элемента ИЛИ 22.3.

Элемент ИЛИ 22.1 служит для формирования сигнала, индицирующего наличие адресной части сообщения в регистре 7 и управляющего мультиплексором 12 отказа.

Элемент ИЛИ 22.2 необходим для объединения сигналов с выходов 4.13 блока 4 и 5.13 блока 5.

Элемент ИЛИ 22.3 обеспечивает передачу импульсов с выхода одновибратора 23 и с выхода элемента И 21.2 на вход синхронизации буферного регистра 6.2 с целью фиксации очередного кода выбора БООС с первого выхода БАОС 3.

Элемент ИЛИ 22.4 предназначен для объединения сигналов с выходов 4.9 и 4.12 блока 4.

Одновибратор 23 служит для формирования импульса, обеспечивающего запись кода выбора БООС в регистр 6.2 после поступления в БООС 1.1-1.5 первого сообщения. Одновибратор 23 срабатывает в момент перехода триггера 10 из нулевого состояния в единичное и формирует импульс с задержкой Δτ2, достаточной для установления кода выбора БООС на первом выходе БАОС 3.

Информационные входы 24.1-24.5 модуля служат для приема сообщений от ОУ и соседних модулей: 24.1 - от ОУ; 24.2 - от соседнего сверху; 24.3 - от соседнего справа; 24.4 - от соседнего слева; 24.5 - от соседнего снизу.

Информационный выход 25 модуля предназначен для подключения модуля к обслуживаемому им ОУ.

Информационные выходы 26.1-26.4 модуля служат для передачи сообщений соседним модулям: 26.1 - соседнему сверху; 26.2 - соседнему справа; 26.3 - соседнему слева; 26.4 - соседнему снизу.

Входы 27.1-27.4 состояния модуля предназначены для приема сигналов состояния соседних модулей с соответствующих триггеров 18: 27.1 - от соседнего сверху; 27.2 - от соседнего справа; 27.3 - от соседнего слева; 27.4 - от соседнего снизу.

Выходы 28.1-28.4 состояния модуля служат для выдачи сигнала состояния текущего модуля с прямого выхода триггера 18 соседним модулям: 28.1 - соседнему сверху; 28.2 - соседнему справа; 28.3 - соседнему слева; 28.4 - соседнему снизу.

Вход 29 отказа модуля предназначен для приема сигнала отказа модуля от внешних средств контроля.

Выход 30 фатальной ситуации модуля служит для выдачи сигнала (импульса), индицирующего возникновение фатальной ситуации.

Назначение элементов и блоков введенного блока 5 модификации маршрутных кодов (фиг. 5) состоит в следующем.

Блок 64 памяти маршрутных кодов предназначен для хранения маршрутных кодов и признаков участков для всех маршрутов, участки которых начинаются данным модулем. БПМК 64 не имеет специальных управляющих входов, и информация на его выходе появляется непосредственно после подачи на адресный вход соответствующего адреса. В ячейку блока 64, имеющую нулевой адрес, записывается нулевой код.

Блок 65 оперативной памяти используется для хранения кодов номеров активных реализаций для каждого участка, начинающегося данным модулем. Запись информации в БОП 65 обеспечивается путем подачи импульса на его вход записи (W).

Сумматор 66 служит для суммирования признака p-го участка маршрута (адреса) Addrop с выхода коммутатора 69 с кодом номера (k) активной реализации участка с выхода БОП 65 и формирования адреса Addrkp для обращения к БПМК 64.

Регистр 67 предназначен для временной фиксации инвертированного маршрутного кода участка.

Счетчик 68 введен для увеличения на единицу кодов номеров активных реализаций участков.

Коммутатор 69 обеспечивает подключение первого входа сумматора 66 и адресного входа БОП 65 либо к первому (5.1), либо к второму (5.2) входу БММК в зависимости от уровня сигнала на входах 5.4 и 5.5 БММК.

Триггер 70 используется с целью управления прохождением импульса с входа 5.7 БММК через элементы И 71 и 72.

Элемент И 71 служит для блокировки передачи импульса с входа 5.7 БММК на выход 5.13 фатальной ситуации БММК.

Элемент И 72 служит для блокировки распространения импульса с входа 5.7 БММК на вход инкремента счетчика 68 и - через элемент 74 задержки - на вход записи W БОП 65.

Группа блоков элементов НЕ 73.1-73.z (73) предназначена для инвертирования кодов трансляций, входящих в маршрутный код текущего участка.

Элемент 74 задержки обеспечивает задержку поступления импульса записи модифицированного кода номера активной реализации участка маршрута на время срабатывания счетчика 68.

Регистр 75 служит для временного хранения инвертированного маршрутного кода текущего участка после его прохождения с выходов регистра 67 через коммутаторы 76.1-76.z-1 и блок 80.

Коммутаторы 76.1-76.z-1 и блок элементов И 80 обеспечивают передачу полей инвертированного маршрутного кода с выходов регистра 67 на информационные входы регистра 75. Передача указанных полей на информационные входы регистра 75 в общем случае осуществляется со сдвигом на Δ =3(y-1) разрядов в сторону поля sz, здесь y=z-z*+1 = 1,2,3,...,z-1, - номер поля, содержащего код s'1 первой трансляции в исходном ("неинвертированном") маршрутном коде, z* - длина текущего участка маршрута, z*=1,2,3,...,z. Сдвиг инвертированного маршрутного кода фактически происходит только в том случае, когда текущий участок маршрута является конечным и при этом имеет длину z*<z; в этом случае y>1 и, значит, Δ >0.

Блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 77.1-77.z-2 совместно с элементами И 78.1-78. z-2 и элементом ИЛИ-НЕ 79 предназначены для формирования сигналов управления коммутаторами 76.1-76.z-1 и блоком элементов И 80 и организации сдвига инвертированного маршрутного кода на требуемое число разрядов Δ.

Рассмотрим процесс функционирования предлагаемого модуля подробно. Поскольку модуль предназначен для включения в состав коммуникационной сети, его работу будем рассматривать во взаимосвязи с другими аналогичными модулями сети.

Исходное состояние всех регистров, триггеров и счетчиков модуля и всех входящих в его состав блоков является нулевым. В БПМК 64 (фиг. 5) в ячейках с ненулевыми адресами размещены маршрутные коды и признаки для всех участков, начинающихся данным модулем. Обобщенный формат слов, хранимых в блоке 64, показан на фиг. 6б (назначение отдельных полей этих слов подробно будет рассмотрено ниже). Все ячейки блока 65 (фиг. 5) находятся в нулевом состоянии. (Цепи приведения элементов модуля в исходное состояние на фиг. 1-5 для упрощения условно не показаны.)

Поскольку регистры 31.1-31.K БООС 1.1-1.5 (фиг. 2) находятся в нулевом состоянии, на выходах элементов И 35.1-35.K присутствуют сигналы логической единицы, что, в свою очередь, обусловливает наличие нулевого сигнала на выходе элемента НЕ 41, индицирующего отсутствие сообщений в соответствующем БООС. Нулевые сигналы с выходов элементов НЕ 41 БООС 1.1-1.5 обеспечивают нулевой уровень сигнала на втором выходе БАОС 3 (фиг. 1). Нулевой сигнал с прямого выхода триггера 10 запуска блокирует работу БС 9, запрещая формирование на его выходах импульсов синхронизации. Нулевой сигнал с прямого выхода триггера 18 отказа (признак работоспособности текущего модуля) через выходы 28.1-28.4 модуля передается соседним модулям сети и сообщает им о работоспособном состоянии текущего модуля. Аналогичные сигналы поступают на входы 27.1-27.4 модуля с прямых выходов триггеров 18 отказа соседних модулей. Нулевое состояние регистра 7 обусловливает наличие нулевого уровня сигнала на выходе элемента ИЛИ 22.1, что, в свою очередь, приводит к блокировке мультиплексора 12. На выходе мультиплексора 12 присутствует сигнал логического нуля (F="0") независимо от сигналов на его первом-четвертом входах.

Так как на всех выходах регистра 7 и на выходе мультиплексора 12 присутствуют сигналы логического нуля, при этом триггер 46 (фиг. 4) находится в нулевом состоянии и на его прямом выходе, соответственно, также присутствует нулевой сигнал v= "0", на выходах 4.7-4.13 блока 4 в соответствии с табл.2 (строка 1) будет код "0000010" (единичный сигнал на выходе 4.12 и нулевые сигналы на выходах 4.7-4.1 1, 4.13). Нулевые сигналы с выходов 4.7 и 4.8 блока 4 (фиг. 1) настраивают коммутаторы 14, 15, 16 и 17 на прием соответствующих полей адресной части сообщения с выхода мультиплексора 2. (Действие остальных сигналов с выходов блока 4 в исходном состоянии несущественно.)

Описанное выше исходное состояние характерно для каждого модуля коммуникационной сети.

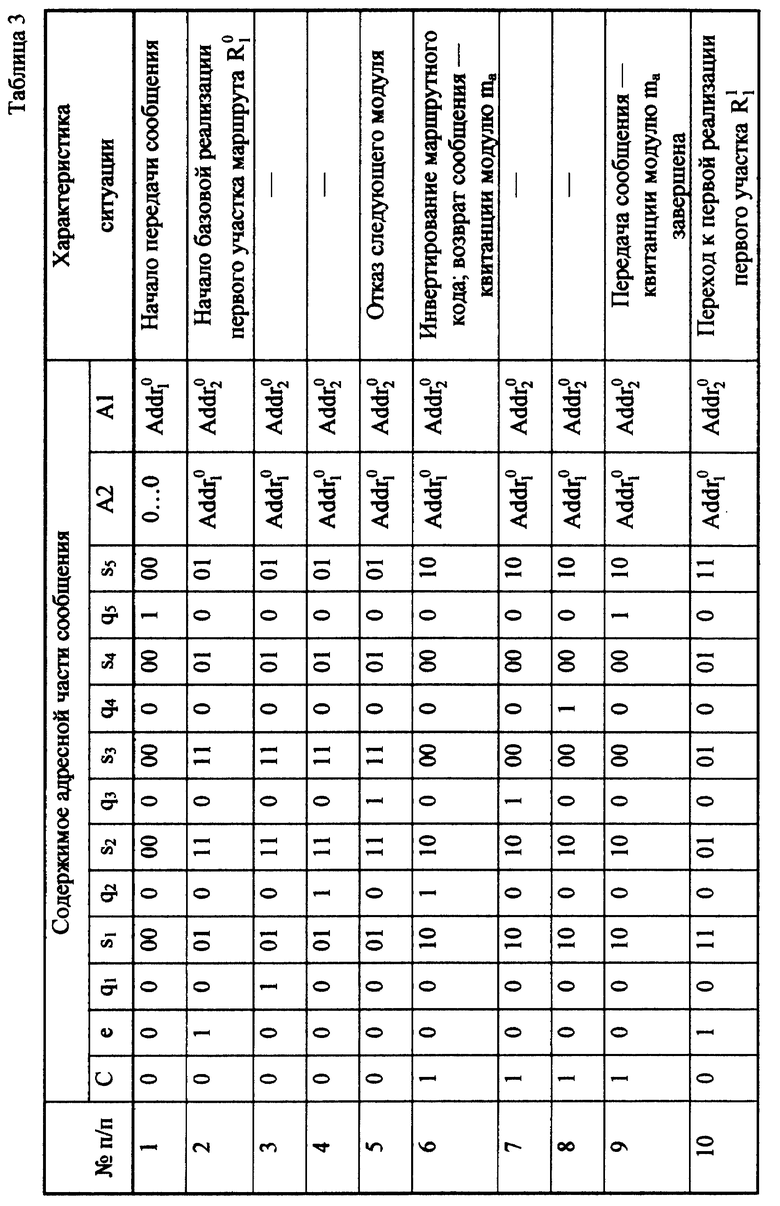

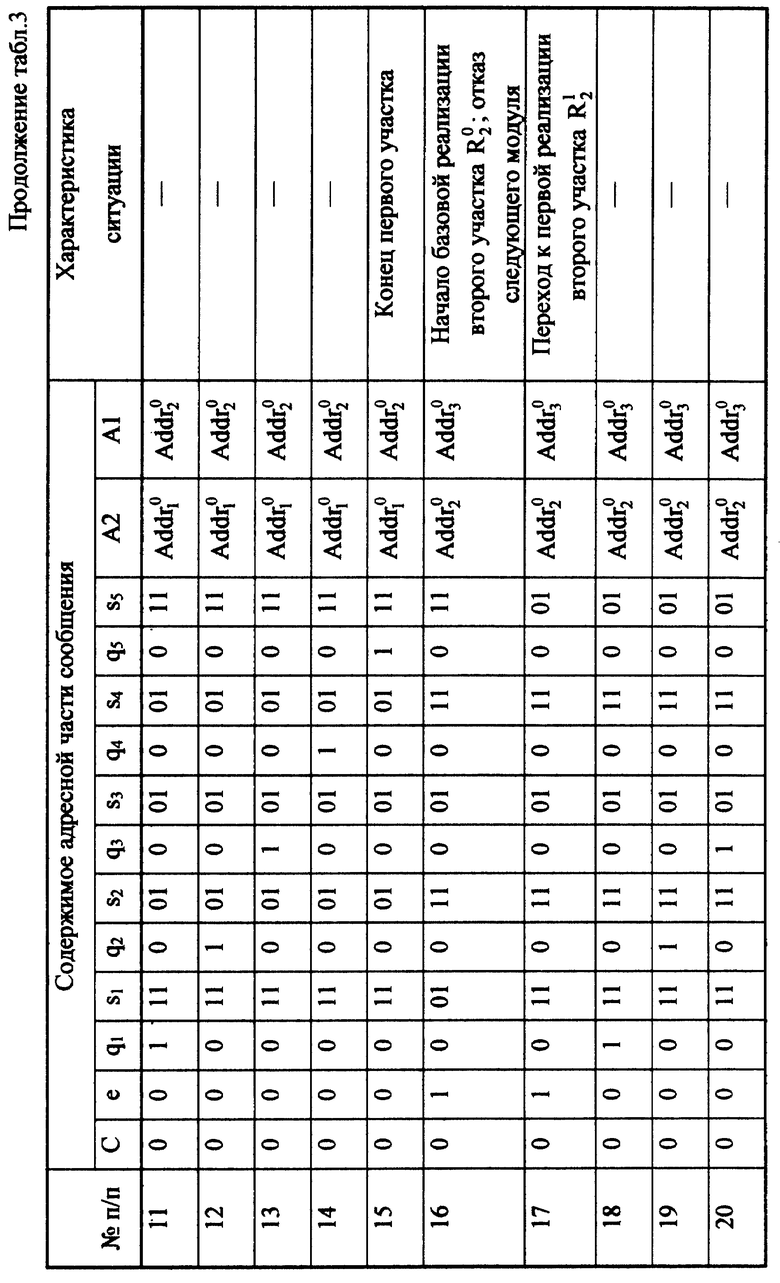

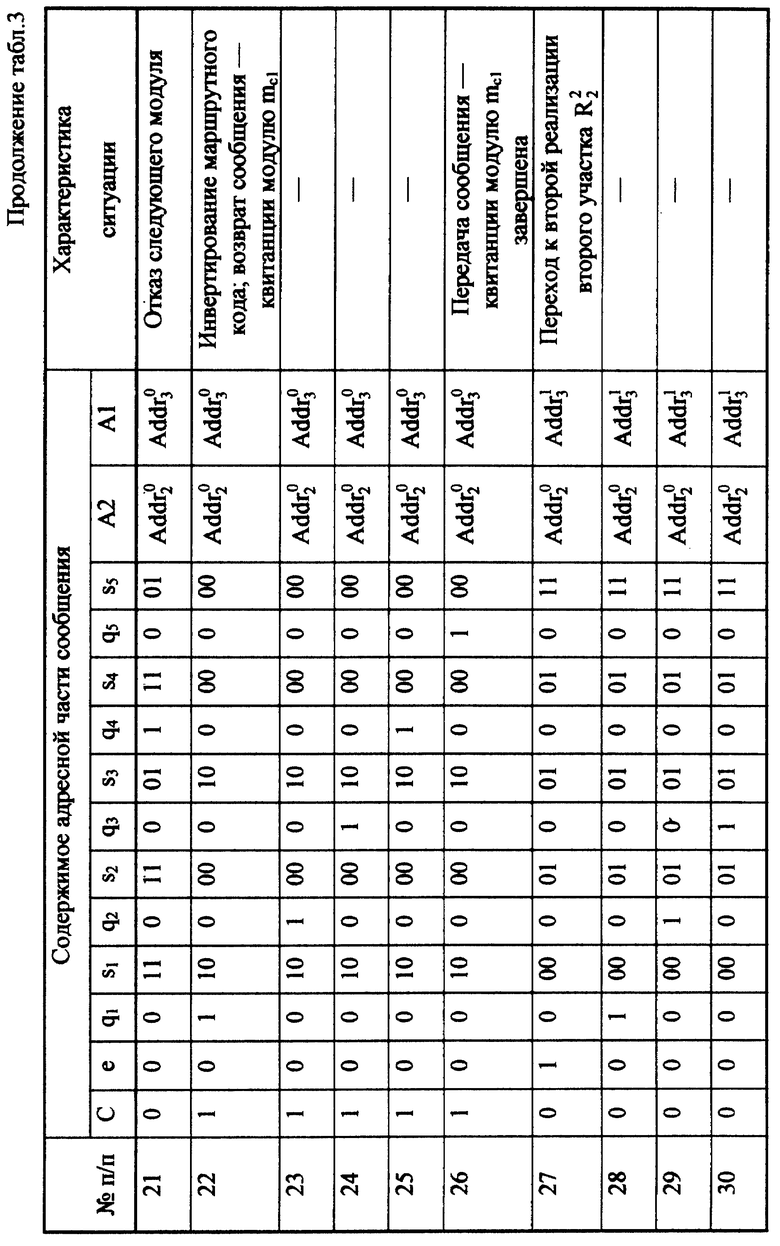

Работа коммуникационной сети в целом начинается с момента подачи сообщения на вход 24.1 одного из модулей от обслуживаемого этим модулем ОУ. Обобщенный формат сообщения показан на фиг. 6а. Сообщение включает информационное поле I и адресную часть. В информационном поле размещается информация, подлежащая передаче модулю - приемнику сообщения. В состав адресной части входят адресное поле A, содержащее маршрутный код текущего участка маршрута (поле A3), а также признаки следующего (поле A1) и текущего участка маршрута (поле A2), и одноразрядное поле статуса сообщения С, используемое для пометки сообщения как квитанции при его возврате в случае обнаружения отказавшего модуля. В момент подачи сообщения на вход 24.1 модуля его адресное поле имеет вид, представленный на фиг. 7а.

С входа 24.1 модуля сообщение подается на информационный вход БООС 1.1 (фиг. 1), с которого поступает на информационный вход демультиплексора 32 (фиг. 2). Так как на адресном входе демультиплексора 32 находится единичный код с выходов элементов И 35.1-35.K, сообщение проходит на первый выход демультиплексора 32, откуда через блок элементов ИЛИ 34.1 передается на информационный вход регистра 31.1.

Одновременно с сообщением на вход 24.1 модуля (фиг. 1) и, следовательно, на информационный вход БООС 1.1 поступает импульс синхронизации. Этот импульс проходит (фиг. 2) через элементы И 36.1-36.K, открытые единичными сигналами с выходов соответствующих элементов И 35.1-35.K, и далее через элементы ИЛИ 37.1-37.K поступает на входы синхронизации регистров 31.1-31.K соответственно. В результате задний фронт импульса фиксирует поступившее сообщение в регистре 31.1, подтверждая нулевое состояние регистров 31.2-31.K.

После записи сообщения в регистр 31.1 на выходе элемента И 35.1 появляется сигнал логического нуля. Этот сигнал совместно с единичными сигналами с выходов элементов И 35.2-35.K поступает на адресный вход демультиплексора 32 и коммутирует его информационный вход со вторым выходом, обеспечивая тем самым возможность записи очередного сообщения в регистр 31.2. Одновременно сигналы с выходов элементов И 35.1-35.K подаются на информационный вход регистра 33 и в виде кода длины очереди сообщений фиксируются в этом регистре по заднему фронту импульса синхронизации, проходящего с информационного входа БООС через элемент ИЛИ 40 и элемент 42 задержки. Кроме того, сигналы с выходов элементов 35.1-35. K поступают на вход элемента И 39, формируют на его выходе нулевой сигнал, который, в свою очередь, устанавливает единичный сигнал на выходе элемента НЕ 41.

Единичный сигнал с выхода элемента 41 БООС 1.1 через второй выход этого блока подается на первый вход БАОС 3 (фиг. 1, 3), откуда, в свою очередь, поступает на вход элемента ИЛИ 45 и формирует на его выходе сигнал логической единицы. Тем самым индицируется наличие сообщений по меньшей мере в одном из БООС. Получаемый сигнал через второй выход БАОС 3 (фиг. 1) передается на вход установки триггера 10 запуска и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 10 включает БС 9 и на выходах последнего спустя время Δτ1 начинается формирование четырех сдвинутых друг относительно друга последовательностей импульсов синхронизации t1, t2, t3 и t4.

Одновременно код длины очереди сообщений с выхода регистра 33 БООС 1.1 (фиг. 1, 2) совместно с нулевыми кодами с выходов регистров 33 БООС 1.2-1.5 поступают на соответствующие входы БАОС 3 и формируют на его первом выходе код выбора БООС (код номера БООС, содержащего наибольшую очередь сообщений). Формирование указанного кода происходит путем попарного сравнения кодов длин очередей сообщений L1, L2, L3, L4 и L5, соответствующих БООС 1.1, 1.2, 1.3, 1.4 и 1.5, на элементах сравнения 43.1-43.10 (фиг. 3) и преобразования кодов с выходов указанных элементов с помощью узла 44 постоянной памяти в соответствии с табл. 1. В рассматриваемом случае наибольшая очередь сообщений имеется в БООС 1.1 (L1=1, L2=0, L3=0, L4=0, L5=0), поэтому на первом выходе БАОС 3 в соответствии со строкой 1 табл. 1 образуется код "001".

В то же самое время переход уровня сигнала на инверсном выходе триггера 10 (фиг. 1) из единичного в нулевой воздействует на одновибратор 23, в результате чего на выходе последнего спустя время Δτ2 образуется импульс. Этот импульс через элемент ИЛИ 22.3 проходит на вход синхронизации регистра 6.2 и передним фронтом фиксирует в нем сформированный код выбора БООС с первого выхода БАОС 3.

Код выбора БООС "001" с выхода регистра 6.2 поступает на адресный вход мультиплексора 2 и коммутирует его выход с первым информационным входом, обеспечивая тем самым возможность считывания сообщения из БООС 1.1. Сообщение из регистра 31.1 БООС 1.1 (фиг. 1, 2) проходит через мультиплексор 2. С выхода мультиплексора 2 информационное поле I сообщения поступает на информационный вход регистра 6.1, а поля A1, A2, A3 и C адресной части (фиг. 6а) через коммутаторы 14, 15, 16 и 17 передаются на первый, второй, третий и четвертый информационные входы регистра 7 соответственно. Одновременно код с выхода регистра 6.2 подается на вход дешифратора 8 и преобразуется в соответствующий ему унитарный код (в данном случае в код "00001", соответствующий БООС 1.1), позволяя в дальнейшем произвести сдвиг очереди сообщений в выбранном БООС.

После завершения всех описанных действий на первом выходе БС 9 появляется импульс t1. Данный импульс поступает на входы синхронизации (W) регистров 6.1 и 7 и задним фронтом записывает поле I сообщения в регистр 6.1, а поля A1, A2, A3 и С - в регистр 7. В результате на выходах 7.2 и 7.4, а также на выходах 7.3.0, 7.3.1.1, 7.3.2.1, 7.3.1.2, 7.3.2.2,..., 7.3.1.z-1, 7.3.2. z-1 и 7.3.2.z группы выходов 7.3 регистра 7 появляются нулевые сигналы, на выходе 7.3.1.z регистра 7 образуется единичный сигнал qz="1" (признак окончания участка маршрута), а на выходе 7.1 формируется ненулевой адрес Addro1 - признак первого участка маршрута.

После фиксации сообщения в регистрах 6.1 и 7 процесс запуска модуля и коммуникационной сети в целом завершается и осуществляется переход к процессу передачи сообщения по требуемому маршруту R=R(ma--->mb). Запуск других модулей сети осуществляется аналогично рассмотренному и происходит либо в результате подачи сообщения на вход 24.1 модуля от ОУ, либо в результате поступления сообщения на вход 24.2, 24.3, 24.4 или 24.5 от одного из соседних модулей, уже начавшего обработку сообщений. При этом в последнем случае в отличие от случая, рассмотренного выше, будет иметь место одно из четырех следующих соотношений длин очередей сообщений в БООС: L1=0, L2=1, L3= 0, L4= 0, L5=0; L1=0, L2=0, L3=1, L4=0, L5=0; L1=0, L2=0, L3=0, L4=1, L5=0; L1= 0, L2=0, L3=0, L4=0, L5=1. Соответственно, на первом выходе БАОС 3 будет сформирован код выбора БООС "010", "011", "100" или "101" в соответствии со строкой 2, 3, 4 или 5 табл. 1 и на информационные входы регистров 6.1 и 7 будет передано сообщение из БООС 1.2, 1.3, 1.4 или 1.5 соответственно.

Передача сообщения начинается с формирования адресного поля, соответствующего первому участку R1 реализуемого маршрута R, путем замены исходного содержимого этого поля словом W1, содержащим маршрутный код первого участка, а также признаки первого и второго участков. Указанное слово размещается в БПМК 64 (фиг. 5) текущего модуля по адресу Addro1 - признаку первого участка, зафиксированному в поле A1 исходного сообщения (фиг. 7а).

Формирование адресного поля обеспечивается блоками 4 и 5 на основе анализа информации с выходов регистра 7 и происходит следующим образом.

Адрес Addro1 с выхода 7.1, единичный сигнал (qz="1") с выхода 7.3.1.z и нулевой сигнал (C="0") с выхода 7.4 регистра 7 поступают на входы 4.1, 4.3 и 4.2 блока 4 соответственно (фиг. 1) и в соответствии со строкой 4 табл.2 формируют на выходах 4.7-4.13 этого блока код "1001000" (единичные сигналы на выходах 4.7 и 4.10 и нулевые сигналы на остальных выходах блока 4). Единичный сигнал с выхода 4.7 блока 4 подается на управляющие входы коммутаторов 14, 15, 16 и на второй (инверсный) вход коммутатора 17 и совместно с нулевым сигналом, поступающим с выхода 4.8 БАС 4 на управляющие входы коммутатора 16 и на третий и четвертый входы коммутатора 17, настраивает коммутаторы 14, 15 и 16 на прием информации с выходов 5.9, 5.10 и 5.11 блока 5 и формирует нулевой уровень сигнала на выходе коммутатора 17. Единичный сигнал с выхода 4.10 и нулевой сигнал с выхода 4.11 блока 4 подаются на входы 5.4 и 5.5 блока 5 соответственно. Нулевые сигналы с выходов 4.9 и 4.12 БАС 4 через элемент ИЛИ 22.4 блокируют элемент И 21.2.

Одновременно адрес Addro1 с выхода 7.1 регистра 7 поступает на вход 5.1 БММК 5, откуда подается на первый информационный вход коммутатора 69 (фиг. 5). Поскольку на входе 5.4 БММК присутствует единичный сигнал, а на входе 5.5 - нулевой сигнал, адрес Addro1 проходит на выход коммутатора 69. Далее указанный адрес поступает на адресный вход БОП 65 и на первый вход сумматора 66. В результате на выходе БОП 65 появляется код номера k активной реализации участка R1. Этот код подается на второй вход сумматора 66 и суммируется с адресом Addro1, формируя на выходе сумматора 66 адрес Addrk1 для обращения к БПМК 64. В исходном состоянии для участка R1 активна базовая реализация Ro1, поэтому k=0 и адрес Addro1 фактически передается на выход сумматора 66 без изменений (Addrk1=Addro1). Далее адрес Addro1 подается на адресный вход БПМК 64. В результате на выходе блока 64 появляется слово W1, представляющее базовую реализацию первого участка (Ro1).

Слово W1 содержит адресное поле, состоящее из полей A1, A2 и A3, как и адресное поле сообщения (фиг. 6), а также дополнительно включает одноразрядное поле У признака последней реализации участка (поле Y используется только в режиме перехода к очередной реализации участка маршрута и поэтому его назначение будет рассмотрено ниже). В зависимости от расположения участка R1 в реализуемом маршруте адресное поле слова W1 может иметь либо формат фиг. 7б, либо формат фиг. 7в или фиг. 7г (где p=1). В первом случае участок R1 не является последним и в маршруте R за ним следует участок R2, признак которого (Addro2) записан в поле A1. Во втором случае участок R1 завершает маршрут R, поэтому поле A1 содержит нулевой код.

После появления на выходе блока 64 поля A1, A2 и A3 слова W1 передаются соответственно на выходы 5.9, 5.10 и 5.11 БММК и далее (фиг. 1) через открытые коммутаторы 14, 15 и 16 поступают на первый, второй и третий информационные входы регистра 7.

После формирования сигналов на выходах БАС 4 и БММК 5 на третьем, а затем на четвертом выходе БС 9 появляются импульсы синхронизации t2 и t3 соответственно. Импульс t2 через вход 4.5 блока 4 и далее (фиг. 4) через элемент И 51, открытый единичным сигналом с инверсного выхода триггера 46, проходит на вход синхронизации триггера 46 и передним фронтом устанавливает данный триггер в единичное состояние. На прямом выходе триггера 46 появляется единичный сигнал v="1". Однако поскольку в соответствии со строкой 4 табл. 2 значение сигнала v может быть произвольным (v="*"), переключение триггера 46 не влияет на дальнейший ход работы модуля. Одновременно импульс 12 через вход 5.6 БММК 5 (фиг. 1, 5) подается на вход синхронизации триггера 70 и, так как на S-входе этого триггера находится нулевой уровень сигнала с входа 5.5 БММК, подтверждает его нулевое состояние. В результате нулевой сигнал с прямого выхода триггера 70 по-прежнему блокирует элементы И 71, 72. Импульс 12, кроме триггера 70, поступает на счетчик 68 и регистр 67. Однако указанные счетчик и регистр в данном режиме не используются и поэтому воздействие на них импульса 12 несущественно.

Импульс t3 с четвертого выхода БС 9 (фиг. 1) через вход 4.6 блока 4 поступает (фиг. 4) на элементы И 53 и 58. Но элемент 53 закрыт нулевым сигналом с выхода элемента 52, который, в свою очередь, обусловлен нулевым сигналом с выхода элемента НЕ 63. В то же время элемент 58 закрыт нулевым сигналом с выхода элемента 48, который обусловлен ненулевым кодом на входе 4.1 БАС. Исходя из сказанного, импульс t3 не проходит ни через элемент 53, ни через элемент 58. Одновременно импульс t3 через вход 5.7 поступает в блок 5 (фиг. 1, 5). Поскольку элементы 71 и 72 закрыты, данный импульс не проходит на их выходы. Воздействие импульса t3 на регистр 75 также не оказывает никакого влияния на работу БММК 5.

После импульса t3 на втором выходе БС 9 появляется импульс t4. Однако этот импульс не выполняет никаких действий, так как элемент И 21.1 заблокирован единичным сигналом с второго выхода БАОС 3, а элемент И 21.2 закрыт нулевым сигналом с выхода элемента ИЛИ 22.4 и лишь подтверждает нулевое состояние триггера 70, проходя на его R-вход через вход 5.8 блока 5 (фиг. 5).

Очередной импульс t1 с первого выхода блока 9 (фиг. 1) поступает на входы синхронизации регистров 6.1 и 7. По заднему фронту этого импульса в регистр 7 заносятся поля А1, А2 и A3 слова W1 с выходов коммутаторов 14, 15 и 16 и нуль с выхода коммутатора 17. В то же время, поскольку на выходе мультиплексора 2 по-прежнему находится исходное сообщение, считываемое из блока 1.1, в регистр 6.1 производится повторная запись информационного поля I данного сообщения. Таким образом, на выходах регистров 6.1 и 7 появляется исходное сообщение с модифицированной адресной частью. Его адресное поле А определяет первый участок передачи, а в поле С (выход 7.4 регистра 7) зафиксирован нуль.

Далее осуществляется передача сообщения в соответствии с кодом R0(*)1 базовой реализации первого участка маршрута R, записанным в поле A3.

Ненулевой признак первого участка маршрута Addr01 с выхода 7.2 регистра 7 формирует единичный сигнал на выходе элемента ИЛИ 22.1 и тем самым разрешает работу мультиплексора 12. Коды трансляций с выходов 7.3.2.1, 7.3.2.2, . .., 7.3.2.z регистра 7 поступают соответственно на первый, второй, и т.д., z-й информационные входы коммутатора 11, на первый, второй, третий, и т.д., z-й управляющие входы которого подаются сигналы с выходов 7.3.0, 7.3.1.1, 7.3.1.2, . .., 7.3.1.z-1 регистра 7 соответственно, позволяющие выделить код активной трансляции.

Если участок R1 не является последним, то согласно фиг. 7б поля s1, s2,. . ., sz содержат коды s'1,s'2,...,s'z соответственно, a q1 = q'1 = "0", q2 = q'2, = "0",..., qz = q'z = "0" и e = "1". Единичный сигнал e = "1" коммутирует выход коммутатора 11 с его первым информационным входом и тем самым обеспечивает передачу на выход указанного коммутатора кода первой трансляции s'1 с выхода 7.3.2.1 регистра 7 (фиг. 1). Если участок R1 завершает маршрут R, причем длина этого участка z* < z, то в соответствии с фиг. 7в поля sy, sy+1,..., sz сообщения содержат коды s'1,s'2,..., , при этом qy-1 = "1", qy =q'1 = "0", q'y+1 = q'2 = "0",..., qz =

, при этом qy-1 = "1", qy =q'1 = "0", q'y+1 = q'2 = "0",..., qz =  = "0", e = q1 = q2 =...= qy-2 = "0", s1 = s2 = ... = sy-2 = "00", a sy-1 =

= "0", e = q1 = q2 =...= qy-2 = "0", s1 = s2 = ... = sy-2 = "00", a sy-1 =  (фиксация кода

(фиксация кода  в поле sy-1 необходима для корректной работы модуля в случае отказа модулей конечного участка длины z* < z; соответствующий режим анализируется ниже). В этом случае единичный сигнал с выхода 7.3.1. у-1 регистра 7 подключает выход коммутатора 11 к его y-му информационному входу и на выход коммутатора 11 проходит код s'1 с выхода 7.3.2.у регистра 7. Если же R1 является конечным участком маршрута R и при этом имеет длину z* = z, то выделение кода s'1 и настройка коммутатора 11 производится так же, как и для промежуточного участка (адресная часть сообщения для данного случая показана на фиг. 7г).

в поле sy-1 необходима для корректной работы модуля в случае отказа модулей конечного участка длины z* < z; соответствующий режим анализируется ниже). В этом случае единичный сигнал с выхода 7.3.1. у-1 регистра 7 подключает выход коммутатора 11 к его y-му информационному входу и на выход коммутатора 11 проходит код s'1 с выхода 7.3.2.у регистра 7. Если же R1 является конечным участком маршрута R и при этом имеет длину z* = z, то выделение кода s'1 и настройка коммутатора 11 производится так же, как и для промежуточного участка (адресная часть сообщения для данного случая показана на фиг. 7г).

Код s'1 с выхода коммутатора 11 (фиг. 1) поступает на адресный вход демультиплексора 13 и коммутирует его информационный вход с выходом 26.1, 26.2, 26.3 или 26.4 модуля (согласно значению s'1), обеспечивая возможность выдачи сообщения следующему модулю, входящему в реализацию R01. Одновременно код s'1 подается на адресный вход мультиплексора 12 и коммутирует его выход с входом 27.1, 27.2, 27.3 или 27.4 модуля, на который поступает сигнал с триггера 18 отказа следующего модуля. В результате на выходе мультиплексора 12 образуется сигнал F - признак состояния следующего модуля. Если F="0", следующий модуль считается работоспособным и, соответственно, сообщение может быть передано этому модулю. При F="1" следующий модуль рассматривается как отказавший. Будем сначала считать, что F="0" (случай F="1" детально анализируется ниже).

После формирования сигнала F происходит формирование сигналов на выходах БАС 4. Нулевые сигналы с выхода 7.4 и 7.3.1.z регистра 7 поступают соответственно на входы 4.2 и 4.3 блока 4, на вход 4.4 которого подается сигнал F= "0" с выхода мультиплексора 12, а на вход 4.1 - код с выхода 7.1 регистра 7 (признак второго участка маршрута или нулевой код). В соответствии со строкой 2 табл. 2 на выходах 4.7-4.13 блока 4 появляется код "0000010" (единичный сигнал на выходе 4.12). Нулевой сигнал с выхода 4.9 блока 4 закрывает блок элементов И 19. Единичный сигнал с выхода 4.12 блока 4 открывает блок элементов И 20 и одновременно через элемент ИЛИ 22.4 открывает элемент И 21.2. (Значения сигналов на выходах 4.7, 4.8, 4.10, 4.11 и 4.13 блока 4 несущественны). В результате сообщение с выходов регистров 6.1 и 7 проходит через блок 20 и далее через демультиплексор 13 передается следующему модулю.

Непосредственно при выдаче сообщения через блок 20 происходит модификация его поля A3, в результате которой единичное значение из поля e (или из поля qy-1, в случае если вид адресного поля сообщения соответствует фиг. 7в) переносится (сдвигается) в поле q1 (или qy). Перенос (сдвиг) указанного значения осуществляется монтажными средствами, путем соответствующего подключения выходов 7.3.0, 7.3.1.1, 7.3.1.2,..., 7.3.1.z-1 регистра 7 к информационному входу блока 20. После сдвига в поле e сообщения принудительно заносится логический нуль с шины логического нуля, а исходное поле qz исключается из адресного поля сообщения (замещается полем qz-1).

Очередной импульс t2 от БС 9 поступает на вход 4.5 блока 4, откуда подается (фиг. 4) на первый вход элемента И 51. Однако так как элемент 51 закрыт нулевым сигналом  ="0" с инверсного выхода триггера 46 (данный триггер все еще находится в состоянии логической единицы), импульс t2 не проходит на вход синхронизации триггера 46 и последний, соответственно, остается в единичном состоянии. Одновременно этот же импульс t2 поступает на вход 5.6 БММК 5 (фиг. 1, 5) и, поскольку на входе 5.5 БММК находится нулевой сигнал, подтверждает нулевое состояние триггера 70. Нулевой сигнал с прямого выхода триггера 70 по-прежнему блокирует элементы И 71 и 72. (Действие импульса t2 на другие элементы БММК в рассматриваемом случае несущественно).

="0" с инверсного выхода триггера 46 (данный триггер все еще находится в состоянии логической единицы), импульс t2 не проходит на вход синхронизации триггера 46 и последний, соответственно, остается в единичном состоянии. Одновременно этот же импульс t2 поступает на вход 5.6 БММК 5 (фиг. 1, 5) и, поскольку на входе 5.5 БММК находится нулевой сигнал, подтверждает нулевое состояние триггера 70. Нулевой сигнал с прямого выхода триггера 70 по-прежнему блокирует элементы И 71 и 72. (Действие импульса t2 на другие элементы БММК в рассматриваемом случае несущественно).

Следующий импульс t3 с блока 9 (фиг. 1) подается на вход 4.6 блока 4 и на вход 5.7 блока 5. В блоке 5 указанный импульс не вызывает никаких изменений. В блоке 4 импульс t3 выполняет следующие действия. Поскольку элемент И 53 (фиг. 4) открыт единичным сигналом с выхода элемента И 52, импульс t3 проходит через элемент 53. Далее рассматриваемый импульс через элемент ИЛИ 62 поступает на вход сброса (R) триггера 46 и восстанавливает его нулевое состояние; на прямом выходе триггера 46 образуется нулевой сигнал v="0". В то же время импульс t3 с выхода элемента ИЛИ 62 передается на выход 4.14 БАС. С указанного выхода импульс t3 поступает на информационный вход блока элементов И 20 (фиг. 1) и передается на выход блока 20. Далее этот импульс через демультиплексор 13 проходит на выход 26.1, 26.2, 26.3 или 26.4 модуля (на который поступает выдаваемое сообщение) и обеспечивает (синхронизирует) прием сообщения следующим модулем реализации R01.