Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределительных систем программного управления технологическими процессами, станками с числовым программным управлением, а также подсистем логического управления многоуровневых иерархических АСУ технологическими и роботехническими комплексами.

Известно модульное устройство для программного управления и контроля, содержащее блок памяти, счетчик адреса, регистр микроопераций, мультиплексоры адреса и логических условий, первый и второй регистры логических условий, регистр номера, первый и второй коммутаторы, первый и второй дешифраторы, шифратор, генератор тактовых импульсов, триггеры пуска и управления, демультиплексор, блок элементов ИЛИ, группу элементов ИЛИ, первый и второй элементы ИЛИ, первый и второй элементы И (а.с. 16477519 СССР G 05 B 19/18; опубл. 07.05.91, БИ N 17).

Недостатком данного устройства является значительное число внешних выводов, необходимых для организации взаимодействия с другими аналогичными устройствами, и как следствие резко ограниченная наращиваемость формируемых на его основе систем и узкая область применения устройства.

Наиболее близким к предлагаемому устройству по технической сущности является распределительная система для программного управления технологическими процессами, включающая m • n каналов, каждый из которых содержит блок памяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок анализа, буферный запоминающий блок, блок синхронизации, первый и второй блоки элементов И, элемент И (а.с. 1605212 СССР G 05 B 19/18; опубл. 07.11.90, БИ N 41).

Недостатком указанной системы является невысокое быстродействие и соответственно узкая область применения, что обусловлено следующим. Блок анализа, входящий в структуру каждого канала (модуля) системы, обеспечивает прием управляющих сообщений (посредством которых осуществляется взаимодействие различных модулей системы) с трех входов (от двух соседних модулей и собственного управляющего устройства), фиксирует их в соответствующих блоках памяти сообщений и осуществляет анализ с целью определения направления их дальнейшей передачи. Как анализ, так и передача сообщений в выбранных в результате анализа направлениях выполняются последовательно (в течение пяти фаз), что обусловливает невысокое быстродействие коммутационных средств модуля, а следовательно, и объясняет недостаточно высокое быстродействие и узкую область применения системы в целом.

Технической задачей изобретения является повышение быстродействия системы путем организации параллельного (одновременного) выполнения как анализа, так и передачи групп управляющих сообщений, поступающих на различные входы каждого из ее модулей, и расширение области целесообразного применения.

Техническая задача решается тем, что в блок анализа каждого модуля мультимикроконтроллерной системы, содержащий с первого по третий блоки памяти сообщений, элемент И и первый элемент ИЛИ, причем информационные входы блоков памяти сообщений с первого по третий подключены к входам блока анализа с первого по третий соответственно, выходы состояния блоков памяти сообщений с первого по третий соединены с соответствующими входами первого элемента ИЛИ, дополнительно введены второй элемент ИЛИ и кросс-коммутатор, причем выход первого элемента ИЛИ соединен с управляющим входом кросс-коммутатора, управляющий выход которого подключен к управляющим входам блоков памяти сообщений с первого по третий, информационные выходы которых соединены с информационными входами кросс-коммутатора с первого по третий соответственно, старшие разряды первого информационного выхода кросс-коммутатора соединены с первым выходом блока анализа и входами второго элемента ИЛИ, выход которого соединен с управляющим выходом блока анализа и первым входом элемента И, второй вход и выход которого подключены соответственно к младшему разряду первого информационного выхода кросс-коммутатора и первому выходу блока анализа, второй и третий выходы которого соединены с вторым и третьим информационными выходами кросс-коммутатора соответственно, а в каждом блоке памяти сообщений, включающем демультиплексор, L регистров (где L - максимальная длина очереди сообщений), группу из L-1 блоков элементов ИЛИ, первую и вторую группы из L элементов И, группу из L элементов ИЛИ и элемент И-НЕ, причем L-й выход демультиплексора соединен с информационным входом L-го регистра, выходы с первого по (L-1)-й демультиплексора подключены к вторым входам блоков элементов ИЛИ с первого по (L-1)-й соответственно, первые входы которых соединены с прямыми выходами регистров со второго по L-й соответственно, а выходы - с информационными входами регистров с первого по (L-1)-1 соответственно, инверсные выходы регистров с первого по L-й подключены к входам элементов И первой группы с первого по L-й соответственно, выходы которых соединены с адресным входом демультиплексора, с соответствующими входами элемента И-НЕ, а также с первыми входами элементов И второй группы с первого по L-й соответственно, выходы которых подключены к первым входам элементов ИЛИ с первого по L-й соответственно, выходы которых подключены к входам синхронизации регистров с первого по L-й соответственно, информационный вход демультиплексора подключен к информационному входу блока памяти сообщений, прямой выход первого регистра и выход элемента И-НЕ подключены соответственно к информационному выходу и выходу состояния блока памяти сообщений, управляющий вход которого дополнительно соединен с вторыми входами элементов ИЛИ с первого по L-й, а также с управляющим входом демультиплексора, а вторые входы элементов И второй группы с первого по L-й подключены к информационному входу блока памяти сообщений.

Сущность предлагаемого изобретения заключается в следующем.

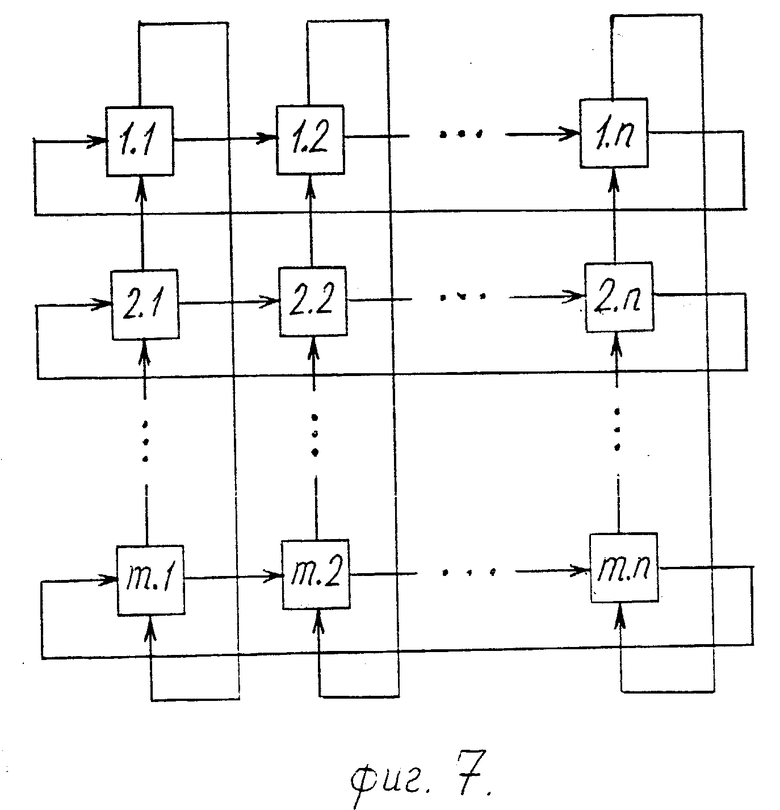

Мультимикроконтроллерная система (ММКС) состоит из множества однотипных модулей, объединенных в матричную структуру. Модули системы выполнены в виде СБИС и имеют по два входных и два выходных информационных канала, предназначенных для подключения к другим аналогичным модулям и обмена управляющей информацией. Каждому модулю ММКС присваивается номер (идентификатор) i.j, определяющий его расположение в пределах матричной структуры (где i и j - соответственно номера строки и столбца структуры, содержащих данный модуль, "." - символ конструктивного объединения (конкатенации)).

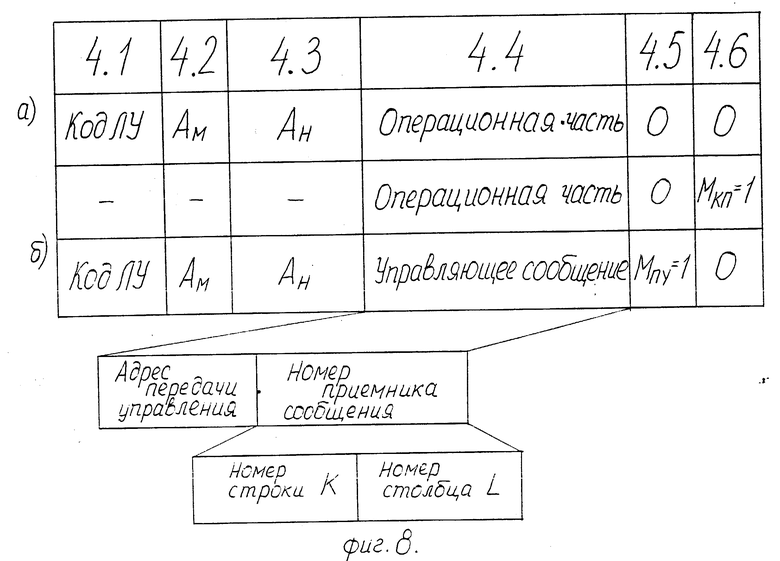

Множество команд, образующих программы управления, реализуемые системой, включает команды двух типов: операционные (K1) и передачи управления (K2). Команды типа K1 предназначены непосредственно для управления соответствующим объектом (инициирования требуемых операций), а команды типа K2 введены для организации взаимодействия различных модулей при реализации сложных комплексов программ управления. Выполнение команд типа K2 сводится к формированию и выдаче сообщений, обеспечивающих инициацию участков программ, закрепленных за определенными модулями ММКС.

Передача сообщений осуществляется транзитным способом на основе принципа фиксированной маршрутизации. Маршрут (траектория) передачи определяется кодом приемника сообщения k.l, указываемым в его адресной части (где k и l - соответственно номера строки и столбца матричной структуры, содержащих модуль-приемник информации). Первоначально сообщение транслируется по строке матричной структуры (вправо) до совпадения номера столбца j очередного модуля с номером столбца приемника l, далее направление передачи сообщения меняется на ортогональное и оно перемещается по столбцу (вверх) до совпадения номера строки i очередного модуля с номером строки k приемника.

Каждый модуль ММКС осуществляет прием сообщений, поступающих от двух соседних модулей (слева и снизу), и в процессе реализации собственной программы также вырабатывает управляющие сообщения, адресованные другим модулям. Принимаемые и вырабатываемые сообщения включаются в различные входные очереди и в порядке поступления подвергаются анализу, в ходе которого определяются направления их дальнейшей передачи. Выбор направления передачи сообщений производится исходя из соотношения номера текущего модуля i.j с номером приемника сообщения k.l и состоит в формировании кода направления, определяющего выдачу сообщений на один из выходов модуля.

В отличие от прототипа, где как анализ (определение направления передачи сообщений), так и передача сообщений, поступающих от различных источников, выполняются последовательно, что существенно ограничивает быстродействие устройства, модуль предлагаемой системы производит одновременный прием и анализ групп (троек) сообщений и осуществляет (в случае несовпадения определяемых в ходе анализа направлений передачи) их одновременную передачу на соответствующие выходы.

Для реализации перечисленных возможностей блок анализа включает кросс-коммутатор.

Управляющие сообщения, поступающие по двум входным каналам от соседних модулей, а также формируемые текущим модулем, размещаются в трех соответствующих блоках памяти сообщений. Кросс-коммутатор производит считывание сообщений из указанных блоков в порядке поступления и осуществляет их одновременный анализ. Анализ поступивших сообщений включает два этапа.

На первом этапе анализа кросс-коммутатор определяет направления передачи сообщений (формирует соответствующие коды направлений) и фиксирует сообщения в буферных регистрах, объединенных в группы, соответствующие различным напряжениям. На втором этапе кросс-коммутатор определяет соотношение направлений передачи (кодов), соответствующих различным сообщениям, и осуществляет передачу сообщений на соответствующие выходы модуля.

В зависимости от соотношения направлений передачи сообщений такт работы кросс-коммутатора может содержать от одного до трех микротактов. Если направления различны, то выдача сообщений на соответствующие выходы осуществляется одновременно (за один микроконтакт), после чего кросс-коммутатор приступает к анализу трех следующих сообщений; если все направления совпадают, то сообщения передаются последовательно и такт работы включает три микротакта; в случае совпадения двух направлений из трех процесс передачи сообщений реализуется за два микротакта.

Таким образом, предлагаемое устройство реализует потенциально существующую возможность повышения быстродействия на основе анализа соотношения направлений передачи сообщений, одновременно поступающих от различных источников, в то время как в прототипе такая возможность не реализована.

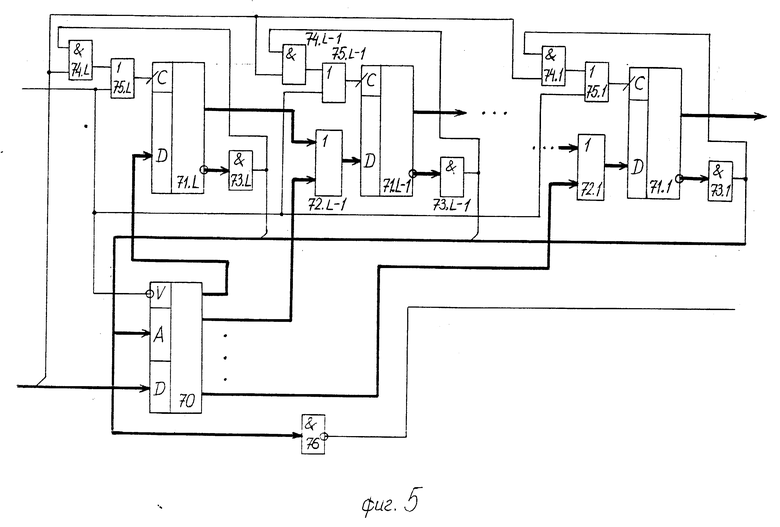

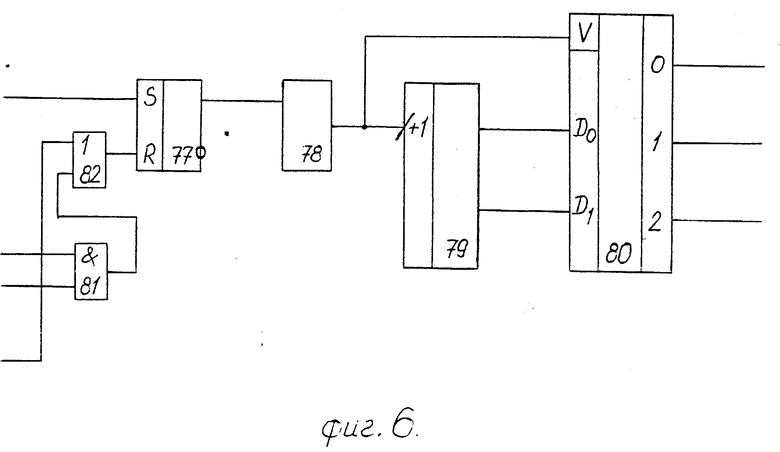

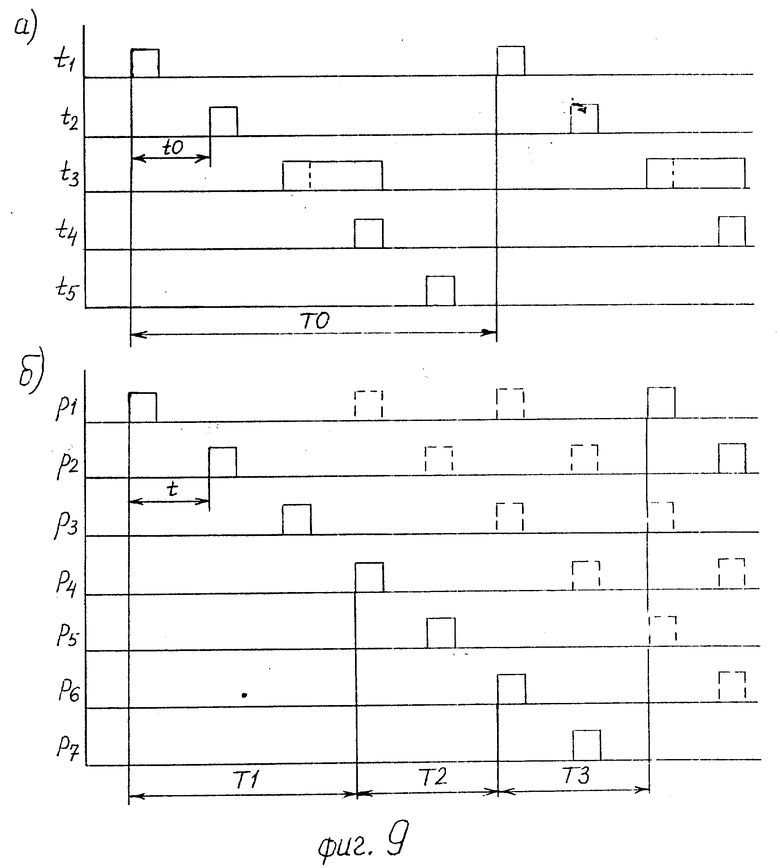

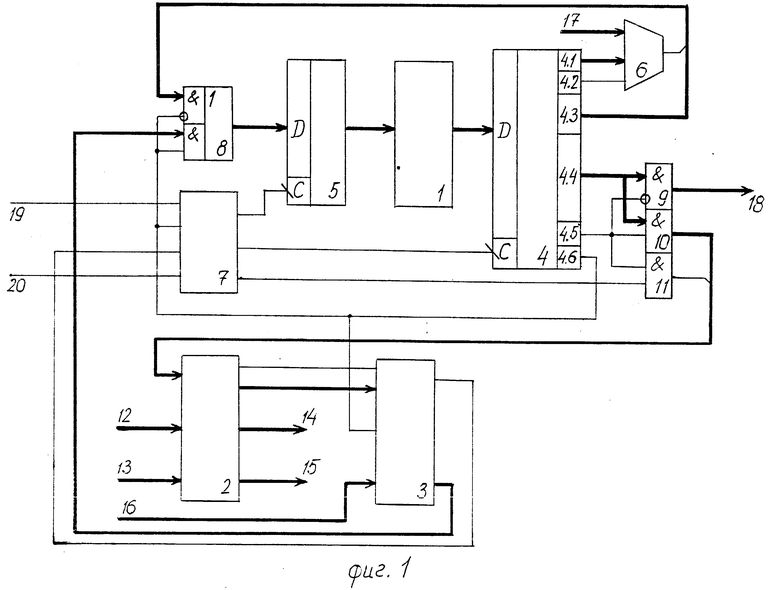

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема модуля мультимикроконтроллерной системы; на фиг. 2 - функциональная схема блока анализа; на фиг. 3 - функциональная схема кросс-коммутатора; на фиг. 4 - функциональная схема буферного запоминающего блока; на фиг. 5 - функциональная схема блока памяти сообщений; на фиг. 6 - функциональная схема блока синхронизации; на фиг. 7 - структурная схема мультимикроконтроллерной системы; на фиг. 8 представлены форматы команд, реализуемых системой; на фиг. 9 - временные диаграммы работы распределителей импульсов прототипа (фиг. 9а) и предлагаемого устройства (фиг. 9б).

Мультимикроконтроллерная система (ММКС) (фиг. 7) состоит из m•n однотипных модулей (фиг. 1), объединенных в матричную структуру, где m - число строк, n - число столбцов, причем первый информационный вход (i.j)-го модуля, где  подключен к второму информационному выходу (i.j-1)-го модуля, а первый информационный вход (i.1)-го модуля соединен с вторым информационным выходом (i.n)-го модуля, второй информационный вход (k<l)-го модуля, где

подключен к второму информационному выходу (i.j-1)-го модуля, а первый информационный вход (i.1)-го модуля соединен с вторым информационным выходом (i.n)-го модуля, второй информационный вход (k<l)-го модуля, где  подключен к первому информационному выходу (k+1. l)-го модуля, а второй информационный вход (m.l)-го модуля соединен с первым информационным выходом (1.l)-го модуля.

подключен к первому информационному выходу (k+1. l)-го модуля, а второй информационный вход (m.l)-го модуля соединен с первым информационным выходом (1.l)-го модуля.

Каждый модуль ММКС реализуется в виде СБИС и содержит (фиг. 1) блок 1 памяти программ, блок 2 анализа, буферный запоминающий блок 3, регистр 4 команд, регистр 5 адреса, мультиплексор 6 логических условий, блок 7 синхронизации, коммутатор 8 адреса, блок 9 элементов запрета, блок 10 элементов И, элемент И 11, причем выход коммутатора 8 адреса подключен к информационному входу регистра 5 адреса, выход которого подключен к адресному входу блока 1 памяти программ, выход которого соединен с информационным входом регистра 4 команд, выходы 4.1 кода логического условия (ЛУ) и 4.2 модифицируемого разряда адреса (Ам) которого подключены соответственно к адресному и первому информационному входам мультиплексора 6 логических условий, второй информационный вход которого соединен с входом 17 логических условий модуля, а выход в объединении с выходом 4.3 немодифицируемой части адреса (Ан) регистра 4 команд подключен к первому информационному входу коммутатора 8 адреса, выход 4.4 операционного поля регистра 4 команд соединен с первыми входами блока 9 элементов запрета и блока 10 элементов И, выход блока 9 элементов запрета подключен к операционному выходу 18 модуля, выход блока 10 элементов И в объединении с выходом элемента И 11 подключен к первому входу блока 2 анализа, выход 4.5 метки передачи управления регистра 4 команд соединен с вторыми входами блока 9 элементов запрета и блока 10 элементов И и с первым входом элемента И 11, первый вход блока 7 синхронизации соединен с первым управляющим входом 19 модуля, выход 4.6 метки конца программы регистра 4 команд подключен к входу сдвига буферного запоминающего блока 3, к второму входу блока 7 синхронизации и к управляющим входам коммутатора 8 адреса, первый, второй и третий выходы блока 7 синхронизации соединены соответственно с входом синхронизации регистра 5 адреса, с входом синхронизации регистра 4 команд и с вторым входом элемента И 11, второй и третий входы блока 2 анализа подключены соответственно к первому 12 и второму 13 информационным входам модуля, управляющий выход блока 2 анализа соединен с управляющим входом буферного запоминающего блока 3, выходы блока 2 анализа с первого по третий подключены соответственно к первому информационному входу буферного запоминающего блока 3, к первому 14 и второму 15 информационным выходам модуля, второй информационный вход и информационный выход буферного запоминающего блока 3 соединены соответственно с входом 16 кода операции модуля и с вторым информационным входом коммутатора 8 адреса, управляющий выход буферного запоминающего блока 3 подключен к третьему входу блока 7 синхронизации, четвертый вход которого соединен со вторым 20 управляющим входом модуля.

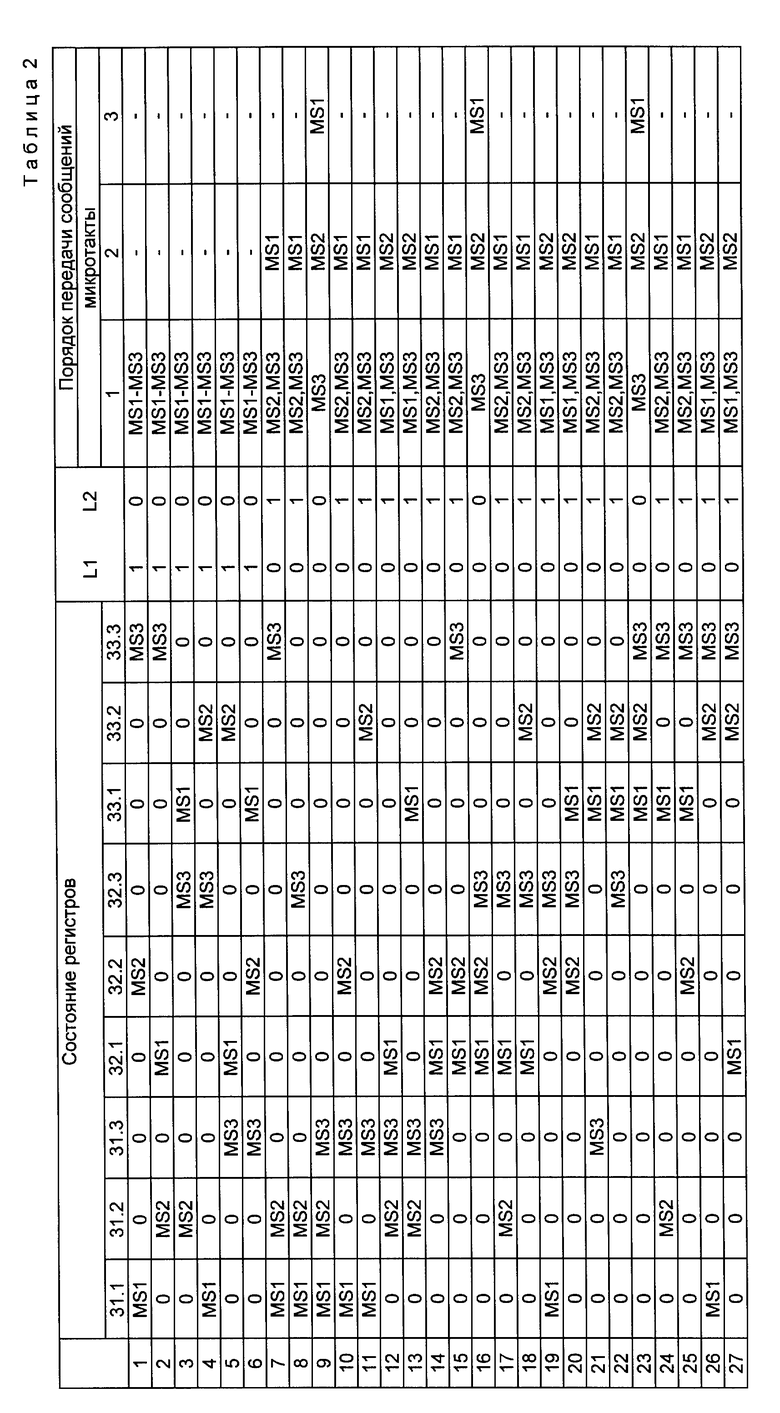

Блок анализа (фиг. 2) предназначен для приема, временного хранения и определения направлений передачи поступающих сообщений, а также для передачи сообщений в выбранных направлениях и содержит первый 21, второй 22 и третий 23 блоки памяти сообщений (БПС), первый элемент ИЛИ 25, элемент И 26.2, причем информационные входы БПС 21, 22, 23 подключены соответственно к первому, второму и третьему входам блока анализа, выходы состояния БПС 21, 22, 23 соединены с соответствующими входами элемента ИЛИ 25, а также дополнительно введенные второй элемент ИЛИ 26.1 и кросс-коммутатор 24, причем выход элемента ИЛИ 25 соединен с управляющим входом кросс-коммутатора 24, управляющий выход которого подключен к управляющим входам БПС 21-23, информационные выходы которых соединены с первым, вторым и третьим информационными входами кросс-коммутатора 24 соответственно, старшие разряды первого информационного выхода кросс-коммутатора 24 соединены с первым выходом блока анализа и входами элемента ИЛИ 26.1, выход которого соединен с управляющим выходом блока анализа и первым входом элемента И 26.2, второй вход и выход которого подключены соответственно к младшему разряду первого информационного выхода кросс-коммутатора 24 и первому выходу блока анализа, второй и третий выходы которого соединены с вторым и третьим информационными выходами кросс-коммутатора 24 соответственно.

Кросс-коммутатор (фиг. 3) предназначен для анализа поступающих сообщений на предмет установления направления их дальнейшей передачи и для распределения потоков сообщений между различными выходными каналами в зависимости от результатов анализа и содержит генератор 27 номера модуля, первую 28, вторую 29 и третью 30 схемы сравнения, первую 31.1-31.3 (31), вторую 32.1-32.3 (32) и третью 33.1-33.3 (33) группы регистров, генератор 34 тактовых импульсов, триггер 35 управления, счетчик 36, дешифратор 37, регистр 38, первый 39, второй 40 и третий 41 коммутаторы, первую 42.1-42.3, вторую 43.1-43.3 и третью 44.1-44.3 группы элементов И-НЕ, группу элементов запрета 45.1-45.3, группу элементов И 46.1-46.3, первый 47 и второй 48 элементы И-ИЛИ, первый 49 и второй 50 триггеры, блок элементов И 51, первый элемент запрета 52, первый 53 и второй 54 элементы И, второй элемент запрета 55, третий 56, первый 57 и второй 58 элементы ИЛИ и одновибратор 59, причем входы генератора 27 номера модуля являются входами настройки модуля, а выход подключен к первым входам схем сравнения 28-30, вторые входы которых подключены соответственно к первому, второму и третьему информационным входам кросс-коммутатора, первый, второй и третий информационные входы кросс-коммутатора соединены соответственно с информационными входами регистров 31.1, 32.1, 33.1, регистров 31.2, 32.2, 33.2 и регистров 31.3, 32.3, 33.3, управляющий вход кросс-коммутатора подключен к инверсному входу элемента запрета 52 и к входу установки триггера 35 управления, прямой выход которого соединен с входом генератора 34 тактовых импульсов, выход которого подключен к счетному входу счетчика 36 и к управляющему входу (V) дешифратора 37, информационные входы с первого по третий которого соединены с соответствующими выходами счетчика 36, первый, второй и третий выходы схемы сравнения 28 подключены к входам разрешения (V) регистров 31.1, 32.1 и 33.1 соответственно, первый, второй и третий выходы схемы сравнения 29 подключены к входам разрешения (V) регистров 31.2, 32.2 и 33.2 соответственно, первый, второй и третий выходы схемы сравнения 30 подключены к входам разрешения регистров 31.3, 32.3 и 33.3 соответственно, прямые выходы регистров 31.1, 31.2, 31.3 подключены соответственно к третьему, второму и первому информационным входам коммутатора 39, выход которого соединен с первым информационным выходом кросс-коммутатора, прямые выходы регистров 32.1, 32.2, 32.3 подключены соответственно к третьему, второму и первому информационным входам коммутатора 40, выход которого соединен с вторым информационным выходом кросс-коммутатора, прямые выходы регистров 33.1, 33.2, 33.3 подключены соответственно к третьему, второму и первому информационным входам коммутатора 41, выход которого соединен с третьим информационным выходом кросс-коммутатора, инверсные выходы регистров 31.1-31.3, 32.1-32.3, 33.1-33.3 подключены соответственно к входам элементов И-НЕ 42.1-42.3, 43.1-43.3 и 44.1-44.3, выход элемента И-НЕ 42.1 соединен с третьим входом элемента И 46.1, с третьим, шестым и седьмым входами элемента И-ИЛИ 47, а также с третьим, пятым и восьмым входами элемента И-ИЛИ 48, выход элемента И-НЕ 42.2 соединен с прямым входом элемента запрета 45.1, с первым входом элемента И 46.1, с вторым, четвертым и девятым входами элемента И-ИЛИ 47, а также с вторым, шестым и седьмым входами элемента И-ИЛИ 48, выход элемента И-НЕ 42.3 соединен с инверсным входом элемента запрета 45.1, с вторым входом элемента И 46.1, с первым разрядом информационного входа регистра 38, с первым, пятым и восьмым входами элемента И-ИЛИ 47, а также с первым, четвертым и девятым входами элемента И-ИЛИ 48, выход элемента И-НЕ 43.1 соединен с третьим входом элемента И 46.2, с двенадцатым, пятнадцатым и шестнадцатым входами элемента И-ИЛИ 47, а также с двенадцатым, четырнадцатым и семнадцатым входами элемента И-ИЛИ 48, выход элемента И-НЕ 43.2 соединен с прямым входом элемента запрета 45.2, с первым входом элемента И 46.2, с одиннадцатым, тринадцатым и восемнадцатым входами элемента И-ИЛИ 47, а также с одиннадцатым, пятнадцатым и шестнадцатым входами элемента И-ИЛИ 48, выход элемента И-НЕ 43.3 соединен с инверсным входом элемента запрета 45.2, с вторым входом элемента И 46.2, с четвертым разрядом информационного входа регистра 38, с десятым, четырнадцатым и семнадцатым входами элемента И-ИЛИ 47, а также с десятым, тринадцатым и восемнадцатым входами элемента И-ИЛИ 48, выход элемента И-НЕ 44.1 соединен с третьим входом элемента И 46.3, с двадцать первым, двадцать четвертым и двадцать пятым входами элемента И-ИЛИ 47, а также с двадцать первым, двадцать третьим и двадцать шестым входами элемента И-ИЛИ 48, выход элемента И-НЕ 44.2 соединен с прямым входом элемента запрета 45.3, с первым входом элемента И 46.3, с двадцатым, двадцать вторым и двадцать седьмым входами элемента И-ИЛИ 47, а также с двадцатым, двадцать четвертым и двадцать пятым входами элемента И-ИЛИ 48, выход элемента И-НЕ 44.3 соединен с инверсным входом элемента запрета 45.3, с вторым входом элемента И 46.3, с седьмым разрядом информационного входа регистра 38, с девятнадцатым, двадцать третьим и двадцать шестым входами элемента И-ИЛИ 47, а также с девятнадцатым, двадцать вторым и двадцать седьмым входами элемента И-ИЛИ 48, первый выход дешифратора 37 подключен к входам синхронизации регистров 31.1-31.3, 32.1-32.3 и 33.1-33.3, а также к управляющему выходу кросс-коммутатора, второй выход дешифратора 37 подключен к первому входу элемента ИЛИ 57, а также к входам синхронизации триггеров 49 и 50, третий выход дешифратора 37 подключен к первому входу элемента И 53 и к первому входу элемента ИЛИ 58, выход которого соединен с вторым входом блока элементов И 51 и информационными выходами с первого по третий кросс-коммутатора, четвертый выход дешифратора 37 подключен к второму входу элемента ИЛИ 57, пятый выход дешифратора 37 подключен к первому входу элемента И 54 и к второму входу элемента ИЛИ 58, шестой выход дешифратора 37 подключен к третьему входу элемента ИЛИ 57, выход которого соединен с входом синхронизации регистра 38, седьмой выход дешифратора 37 подключен к третьему входу элемента ИЛИ 58, выходы элементов запрета 45.1-45.3 и элементов И 46.1-46.3 подключены соответственно к второму, пятому, восьмому, третьему, шестому и девятому разрядам информационного входа регистра 38, выходы с первого по девятый которого соединены с первом, вторым, третьим управляющими входами коммутатора 39, первым, вторым, третьим управляющими входами коммутатора 40, первым, вторым, третьим управляющими входами коммутатора 41 соответственно и с первым входом блока элементов И 51, разряды выхода которого с первого по девятый подключены к входам сброса регистров 31.3, 31.2, 31.1, 32.3, 32.2, 32.1, 33.3, 33.2 и 33.1 соответственно, выход элемента И-ИЛИ 48 подключены к информационному (D) входу триггера 49, а также к инверсному входу элемента запрета 55, второй вход которого соединен с выходом элемента И-ИЛИ 47, а выход подключен к информационному (D) входу триггера 50, прямые выходы триггеров 49 и 50 подключены соответственно к вторым входам элементов И 54 и 53, выходы элементов И 53 и 54 соединены соответственно с первым и вторым входами элемента ИЛИ 56, третий вход которого подключен к седьмому выходу дешифратора 37, выход элемента ИЛИ 56 соединен с входом одновибратора 59, выход которого подключен к входу установки (S) счетчика 36 и к прямому входу элемента запрета 52, выход которого подключен к входу сброса (R) триггера 35 управления.

Буферный запоминающий блок (БЗБ) (фиг. 4) предназначен для приема, временного хранения и выдачи управляющих сообщений в порядке их поступления и включает коммутатор 60, демультиплексор 61, группу регистров 62.1-62.N (где N - максимальная длина очереди сообщений), группу блоков элементов ИЛИ 63.1-63. N-1, первую 64.1-64.N и вторую 65.1-65.N группы элементов И, группу элементов ИЛИ 66.1-66. N, элемент ИЛИ 67, элемент И 68 и одновибратор 69, причем выход коммутатора 60 соединен с информационным входом демультиплексора 61, N-й выход которого подключен к информационному входу регистра 62.N, а выходы с первого по (N-1)-й соединены с вторыми входами блоков элементов ИЛИ 63.1-63.N-1 соответственно, первые входы которых подключены к прямым выходам регистров 62.2-62.N соответственно, а выходы соединены с информационными входами регистров 62.1-62.N-1 соответственно, инверсные выходы регистров 62.1-62. N подключены к входам элементов И 64.1-64.N соответственно, выходы которых соединены с адресным входом демультиплексора 61, с входами элемента И 68, а также с первыми входами элементов И 65.1-65.N соответственно, вторые входы которых подключены к выходу элемента ИЛИ 67, а выходы - к первым входам элементов ИЛИ 66.1-66.N соответственно, выходы которых соединены с входами синхронизации регистров 62.1-62.N соответственно, управляющий вход БЗБ подключен к управляющему входу коммутатора 60, первый информационный вход которого в объединении с первым входом элемента ИЛИ 67 подключен к первому информационному входу БЗБ, а второй информационный вход в объединении с вторым входом элемента ИЛИ 67 - к второму информационному входу БЗБ, вход сдвига которого соединен с входом одновибратора 69, выход которого подключен к вторым входам элементов ИЛИ 66.1-66.N, а также к управляющему входу демультиплексора 61, прямой выход регистра 62.1 и выход элемента И 68 подключены соответственно к информационному выходу и управляющему выходу БЗБ.

Блок памяти сообщений (БПС) (фиг. 5) аналогично БЗБ предназначен для приема, временного хранения и выдачи управляющих сообщений в порядке их поступления и содержит демультиплексор 70, регистры 71.7-71.L (где L - максимальная длина очереди сообщений), группу блоков элементов ИЛИ 72.1-72.L-1, первую 73.1-73.L и вторую 74.1-74.L группы элементов И, группу элементов ИЛИ 75.1-75.L, элемент И-НЕ 76, причем L-й выход демультиплексора 70 подключен к информационному входу регистра 71.L, выходы демультиплексора 70 с первого по (L-1)-й соединены с вторыми входами блоков элементов ИЛИ 72.1-72.L-1 соответственно, первые входы которых подключены соответственно к прямым выходам регистров 71.2-71. L, а выходы - к информационным входам регистров 71.1-71. L-1 соответственно, инверсные выходы регистров 71.1-71.L соединены с входами элементов И 73.1-73.L соответственно, выходы которых подключены к адресному входу демультиплексора 70, к входам элемента И-НЕ 76, а также к первым входам элементов И 74.1-74.L соответственно, выходы которых подключены к первым входам элементов ИЛИ 75.1-75.L соответственно, выходы которых соединены с входами синхронизации регистров 71.1-71. L соответственно, информационный вход БПС подключен к информационному входу демультиплексора 70, а прямой выход регистра 71.1 и выход элемента И-НЕ 76 подключены соответственно к информационному выходу БПС и выходу состояния БПС, управляющий вход которого дополнительно соединен с управляющим входом демультиплексора 70 и с вторым входами элементов ИЛИ 75.1-75.L, а вторые входы элементов И 74.1-74.L соединены с информационным входом блока памяти сообщений.

Блок синхронизации (фиг. 6) обеспечивает формирование трех непересекающихся во времени импульсных последовательностей, синхронизирующих работу модуля ММКС, и включает триггер 77 управления, генератор 78 импульсов, счетчик 79, дешифратор 80, элемент И 81 и элемент ИЛИ 82, причем первый вход блока синхронизации подключен к входу установки триггера 77 управления, прямой выход которого соединен с входом генератора 78 импульсов, выход которого подключен к входу счетчика 79 и к управляющему входу (V) дешифратора 80, информационные входы которого подключены к соответствующим выходам счетчика 79, а выходы с первого по третий соединены с соответствующими выходами блока синхронизации, второй и третий входы которого подключены к входам элемента И 81, выход которого соединен с первым входом элемента ИЛИ 82, второй вход которого подключен к четвертому входу блока синхронизации, а выход соединен с входом сброса триггера 77 управления.

Назначение основных элементов кросс-коммутатора (фиг. 3) состоит в следующем.

Генератор 27 номера модуля предназначен для формирования кода логического номера i.j, определяющего расположение соответствующего модуля в пределах матричной структуры ММКС.

Регистры 31. t, 32.t, 33.t, t=1, 2, 3 предназначены для приема, временного размещения и выдачи сообщений, поступающих на различные входы кросс-коммутатора.

Схема сравнения 28 (29, 30) служит для формирования унитарного кода, определяющего направление передачи сообщений, поступающих с первого (второго, третьего) информационного входа кросс-коммутатора, и управляющего записью сообщений в регистры 31.1, 32.1, 33.1 (31.2, 32.2, 33.2; 31.3, 32.3, 33.3).

Элементы И-НЕ 42.1, 42.2 и 42.3 (43.1, 43.2 и 43.3; 44.1, 44.2 и 44.3) предназначены для формирования сигналов, характеризующих состояние регистров 31.1, 31.2 и 31.3 (32.1, 32.2 и 32.3; 33.1, 33.2 и 33.3) соответственно.

Коммутатор 39 (40, 41) служит для передачи сообщений с выходов регистров 31. t, (32.t, 33.t), t=1, 2, 3 на первый (второй, третий) информационный выход кросс-коммутатора в соответствии с кодом на его управляющих входах.

Элементы запрета 45.k, элементы И 46.k, k= 1, 2, 3, ИЛИ 57, регистр 38 и блок элементов И 51 предназначены для формирования и выдачи кода управления коммутаторами 39-41 и управления сбросом регистров 31.t, 32.t, 33.t, t=1, 2, 3.

Генератор 34 импульсов, триггер 35 управления, кольцевой счетчик 36, дешифратор 37, элемент И 52 и элемент ИЛИ 58 предназначены для синхронизации работы различных узлов кросс-коммутатора и передачи управляющих сообщений на выходы устройства.

Элементы И-ИЛИ 47,48 предназначены для формирования сигналов, характеризующих способ размещения групп поступающих сообщений в регистрах 31.t, 32. t, 33.t, t=1,2,3, и в объединении с триггерами 49, 50, элементами И 53, 54, запрета 55, ИЛИ 56 и одновибратором 59 служат для управления длительностью такта работы кросс-коммутатора.

Учитывая идентичность модулей, работу мультимикроконтроллерной системы рассмотрим на примере функционирования одного из модулей, например модуля с номером i.j.

Первоначально регистр 5 адреса и все разряды регистра 4 команд, за исключением разряда 4.6 метки конца программы, установленного в единичное состояние, находятся в состоянии логического нуля, а в ячейках блока 1 памяти программ с ненулевыми адресами размещаются команды участков программ, закрепленных за (i.j)-м модулем. Все регистры и триггеры, входящие в блоки 21-23 памяти сообщений, буферный запоминающий блок 3 и блок 7 синхронизации, также приведены в нулевое состояние, а счетчик 79 установлен в состояние "11" (цепи начальной установки на фиг. 1-6 для упрощения условно не показаны). Исходное состояние элементов кросс-коммутатора 24 (фиг. 2,3) рассматривается ниже.

Код операции (КОП), определяющий номер (тип) выполняемой операции и представляющий собой адрес первой команды соответствующей программы, формируется устройством управления верхнего уровня (УУВУ), в сопровождении импульса синхронизации подается на вход 16 кода операции модуля и поступает на второй информационный вход буферного запоминающего блока (БЗБ) 3 (фиг. 1,4). Далее КОП передается на второй информационный вход коммутатора 60 и, так как на его управляющем входе присутствует сигнал логического нуля, поступает на информационный вход демультиплексора 61. Так как все регистры 62.1-62.N установлены в нулевое состояние и на их инверсных выходах присутствуют единичные сигналы, на выходах элементов И 64.1-64.N также появляются сигналы логической единицы, которые, во-первых, обусловливают образование единичного сигнала на выходе элемента И 68, а во-вторых, поступают на адресный вход демультиплексора 61 и, так как на его управляющем входе присутствует сигнал логического нуля, обеспечивают передачу КОП с его информационного входа на первый выход. С первого выхода демультиплексора 61 КОП через блок элементов ИЛИ 63.1 поступает на информационный вход регистра 62.1.

Одновременно импульс синхронизации с второго информационного входа БЗБ поступает на второй вход элемента ИЛИ 67, проходит на его выход и через элементы И 65.1-65.N, на первых входах которых присутствуют единичные сигналы, а также элементы ИЛИ 66.1-66.N передается на входы синхронизации регистров 62.1-62. N. По переднему фронту данного импульса КОП фиксируется в регистре 62.1 и появляется на информационном выходе БЗБ; состояние остальных регистров не изменяется, так как на их информационных входах находятся нулевые коды. Так как КОП содержит по меньшей мере одну единицу, на выходе элемента И 64.1 образуется сигнал логического нуля, который блокирует элемент И 65.1, а также совместно с единичными сигналами с выходов элементов И 64.2-64.N поступает на адресный вход демультиплексора 61 и предопределяет запись очередного КОП или сообщения с первого информационного входа БЗБ в регистр 62.2. В дальнейшем запись сообщений в регистры БЗБ осуществляется аналогично.

Код 11...10 с выходов элементов И 64.1-64.N поступает на входы элемента И 68 и формирует на его выходе сигнал логического нуля. Данный сигнал передается на управляющий выход БЗБ и индицирует наличие поступивших сообщений или КОП. КОП с информационного выхода БЗБ поступает на второй информационный вход коммутатора 8 адреса (фиг. 1) и, так как на его управляющих входах присутствует единичный сигнал с выхода 4.6 метки конца программы регистра 4 команд, передается на информационный вход регистра 5 адреса.

Одновременно УУВУ вырабатывает импульс "Пуск", который подается на вход 19 модуля, поступает на первый вход блока 7 синхронизации (фиг. 6), передается на вход установки (S) триггера 77 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 77 включает генератор импульсов 78, на выходе которого начинается формирование импульсной последовательности T. Импульс T с выхода генератора 78 поступает на счетный вход счетчика 79 и управляющий вход (V) дешифратора 80 и обеспечивает переключение счетчика 79 (являющегося кольцевым с коэффициентом пересчета - 3) в следующее состояние. Сигналы, определяющие состояние счетчика 79, с его выходов подаются на соответствующие информационные входы дешифратора 80 и обеспечивают возбуждение единичного уровня сигнала на его соответствующем выходе. Длительность сигналов на выходах дешифратора 80 ограничивается временем наличия единичного уровня сигнала на его управляющем входе, т.е. длительностью импульса T на выходе генератора 78. Таким образом, на выходах дешифратора 80 (блока синхронизации) начинается формирование трех непересекающихся во времени импульсных последовательностей П1, П2 и П3, обеспечивающих синхронизацию работы различных узлов модуля.

По заднему фронту импульса П1 с первого выхода блока 7 синхронизации (фиг. 1) КОП, поступивший ранее на информационный вход регистра 5 адреса, фиксируется в регистре 5 и далее поступает на адресный вход блока 1 памяти программ, на выходе которого спустя некоторое время появляется первая команда программы, заданной кодом операции. По заднему фронту импульса П2 с второго выхода блока 7 синхронизации считанная команда заносится в регистр 4 команд. Дальнейший ход работы модуля определяется форматом считанной команды (фиг. 8).

Случай 1. Если считанная команда является операционной (фиг. 8а), то на выходе 4.5 метки передачи управления регистра 4 команд появляется нулевой сигнал, который поступает на второй вход блока элементов запрета 9 и обеспечивает передачу операционного поля команды с выхода 4.4 регистра 4 команд на операционный выход 18 модуля для управления соответствующим объектом. В то же время сигнал логического нуля с выхода 4.5 регистра 4 команд блокирует элемент И 11 и блок элементов И 10, на выходах которых соответственно сохраняется нулевой уровень сигнала.

Одновременно код логического условия (который, в частности, может быть нулевым) и модифицируемый разряд адреса с выходов 4.1 и 4.2 регистра 4 команд поступают соответственно на адресный и первый информационный входы мультиплексора 6 логических условий, на втором информационном входе которого формируются значения логических условий, закрепленных за данным модулем. Сигнал с выхода мультиплексора 6, определяемый значениями опрашиваемого логического условия и модифицируемого разряда адреса, в объединении с немодифицируемый частью адреса с выхода 4.3 регистра 4 команд образует полный исполнительный адрес следующей команды, который поступает на первый информационный вход коммутатора 8 адреса и, если на выходе 4.6 регистра 4 имеется нулевой сигнал, передается на информационный вход регистра 5 адреса. Очередной импульс П1 с первого выхода блока 7 синхронизации фиксирует полученный адрес в регистре 5 и инициирует, таким образом, начало цикла выполнения (обработки) следующей команды, аналогичного предшествующему.

Случай 2. Если считанная команда является командой передачи управления К2 (фиг. 8б), то на операционном выходе 4.4 регистра 4 команд формируется управляющее сообщение, содержащее координаты модуля приемника (адресата) k.l и соответствующий адрес передачи управления. На выходе 4.5 метки передачи управления регистра 4 команд появляется единичный сигнал (метка передачи управления), который поступает на второй вход блока элементов И 10 и первый вход элемента И 11 и обеспечивает передачу управляющего сообщения на первый вход блока 2 анализа. Импульс П3 с третьего выхода блока 7 синхронизации поступает на второй вход элемента И 11, проходит на его выход и, поступая на первый вход блока 2 анализа, обеспечивает запись управляющего сообщения в один из регистров блока памяти сообщений 21 (фиг. 2,5) с целью дальнейшей передачи адресату.

Адрес следующей по порядку команды, формируемый с использованием мультиплексора 6 логических условий, фиксируется в регистре 5 адреса по заднему фронту очередного импульса П1 с первого выхода блока 7 синхронизации и модуль переходит к считыванию следующей команды. Процедура формирования указанного адреса полностью совпадает с соответствующей процедурой, рассмотренной ранее для случая 1 (обработки команды типа K1).

Одновременно с выполнением программы (i.j)-й модуль осуществляет прием управляющих сообщений, поступающих от соседних модулей с номерами i.j-1 и i+1. j по входам 12 и 13 соответственно (фиг. 7), производит анализ содержимого адресных полей сообщений и их передачу в трех возможных направлениях: ретрансляцию соседним модулям с номерами i.j+1 и i-1.j соответственно на выходы 15 и 14 или передачу в БЗБ 3 для дальнейшей обработки.

Управляющие сообщения с выхода блока элементов И 10 (генерируемые данным модулем), а также с информационных входов 12 и 13 модуля одновременно поступают соответственно на первый, второй и третий входы блока 2 анализа в сопровождении импульсов синхронизации и передаются на информационные входы блоков памяти сообщений (БПС) 21, 22 и 23 соответственно, где фиксируются с целью дальнейших анализа и ретрансляции (фиг. 2).

Очередное сообщение с информационного входа БПС 21 (22, 23) поступает на информационный вход демультиплексора 70 (фиг. 5), на управляющем входе (V) которого находится разрешающий (нулевой) сигнал, а на адресном входе присутствует код 11. ..100...0 с выходов элементов И 73.1-73.L, характеризующий состояние очереди сообщений в данном БПС и определяющий регистр - приемник сообщения. Сообщение с информационного входа демультиплексора 70 передается на его (k+1)-й выход (где k - текущая длина очереди сообщений) и через блок элементов ИЛИ 72.k+1 поступает на информационный вход регистра 71.k+1.

Одновременно импульс синхронизации, сопровождающий сообщение, с информационного входа БПС через элементы И 74.k+1-74.L и элементы ИЛИ 75.k+1-75.L поступает на входы синхронизации регистров 71.k+1-71.L и обеспечивает фиксацию сообщения в регистре 71.k+1. На выходе элемента и 73.k+1 формируется нулевой уровень сигнала. Вновь образующийся код состояния очереди с выходов элементов 73.1-73. L подается на адресный вход демультиплексора 70 и обеспечивает передачу очередного поступающего на вход данного БПС сообщения на (k+2)-й выход демультиплексора и запись сообщения заносится в регистр 71.k+3 и т.д.

Код 11...100...0 с выходов элементов И 73.1-73.L подается на входы элемента И-НЕ 76 и формирует на его выходе сигнал логической единицы, индицирующий наличие сообщений в данном БПС. Единичный сигнал (сигнал состояния БПС) с выхода элемента И-НЕ 76 поступает на выход состояния БПС. Сигналы состояния с одноименных выходов БПС 21-23 передаются на входы элемента ИЛИ 25 (фиг.2) и устанавливают на его выходе обобщенный сигнал состояния, единичное значение которого соответствует наличию сообщений по меньшей мере в одном из БПС (21,22 или 23). Единичный сигнал с выхода элемента ИЛИ 25 поступает на управляющий вход кросс-коммутатора 24.

Очередная группа управляющих сообщений с информационных выходов БПС 21, 22, 23 передается на первый, второй и третий информационные входы кросс-коммутатора 24. Кросс-коммутатор 24 принимает указанные сообщения на обработку и вырабатывает импульс сдвига, который с его управляющего выхода поступает на управляющие входы БПС 21-23 и обеспечивает сдвиг очередей сообщений.

Импульс сдвига с управляющего входа БПС 21 (22, 23) поступает на управляющий вход демультиплексора 70 (фиг.5) и формирует на его выходах нулевой уровень сигнала. Одновременно этот же импульс через элементы ИЛИ 75.1-75.L передается на входы синхронизации регистров 71.1-71.L, на информационных входах которых присутствует информация соответственно с прямых выходов регистров 71.2-71.L и нулевой код с L-го выхода демультиплексора 70, и передним фронтом обеспечивает сдвиг очереди сообщений в БПС.

Кросс-коммутатор 24 (фиг.2) анализирует поступившие из БПС 21-23 сообщения, определяет направления их дальнейшей передачи и выдает в выбранных направлениях (на соответствующие выходы модуля), причем сообщения, направления передачи которых не совпадают, транслируются на соответствующие выходы одновременно. После передачи группы (тройки) сообщений цикл работы кросс-коммутатора 24 повторяется.

Рассмотрим процесс функционирования кросс-коммутатора.

Первоначально регистры 31.1-31.3, 32.1-32.3,.33.1-33.3, 38 и триггер 35 установлены в состояние логического нуля, состояние триггеров 49 и 50 не определено, счетчик 36 установлен в состояние "111", а на выходе генератора 27 сформирован код номера текущего модуля (цепи начальной установки на фиг.3 условно не показаны).

Единичный сигнал состояния с выхода элемента ИЛИ 25 (фиг.2) поступает на управляющий вход кросс-коммутатора, передается на вход установки (S) триггера 35 (фиг. 3) и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 35 поступает на вход генератора 34 импульсов и разрешает формирование на его выходе импульсной последовательности F.

Импульсы с выхода генератора 34 поступают на счетный вход счетчика 36, а также на управляющий вход дешифратора 37. По переднему фронту первого импульса F счетчик 36 (являющийся кольцевым) переводится в состояние "000" и нулевые сигналы с его выходов поступают на информационные входы дешифратора 37, возбуждая на его первом выходе сигнал логической единицы, длительность которого ограничивается временем присутствия единичного уровня сигнала на его управляющем входе. Таким образом, на первом выходе дешифратора 37 появляется импульс p1, длительность которого равна длительности импульсов, вырабатываемых генератором 34. Аналогичным образом при появлении на выходе генератора 34 очередного импульса осуществляется формирование импульса p2 на втором выходе, p3- на третьем и т.д., p7 - на седьмом выходах дешифратора 37.

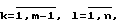

Управляющие сообщения с информационных выходов БПС 21, 22 и 23 одновременно поступают на первый, второй и третий информационные входы кросс-коммутатора соответственно. Сообщение, поступившее на первый информационный вход (далее условно обозначаемое как MS1), передается на информационные входы регистров 31.1, 32.1 и 33.1, а сообщения, поступившие на второй и третий информационные входы (MS2 и MS3 соответственно), - соответственно на информационные входы регистров 31.2, 32.2, 33.2, и 31.3, 32.3, 33.3 в частном случае возможно отсутствие сообщений на одном или двух информационных входах). Одновременно адресные части сообщений MS1, MS2 и MS3 (содержащие номера приемников k1.l1, k2.l2, и k3.l3) подаются на вторые входы схем сравнения 28, 29 и 30 соответственно и сопоставляются с номером текущего (i. j)-го модуля, поступающим на первые входы схем сравнения 28-30 с выхода генератора 27. В результате сопоставления на выходе каждой из схем сравнения 28, 29, 30 образуется трехразрядный унитарный код, устанавливающий направление дальнейшей передачи для каждого из сообщений (код направления) и определяемый в соответствии с табл.1.

С выходом схем сравнения 28, 29, 30 коды направления поступают на входы разрешения регистров 31.1, 32.1, 33.1; 31.2, 32.2, 33.2 и 31.3, 32.3, 33.3 соответственно и, будучи унитарными, разрешают запись информации только в один из регистров в каждой из выделенных групп (троек). Зависимость способа размещения сообщений MS1-MS3 в регистрах 31.t, 32.t и 33.t, t=1,2,3 от кодов направления представлена в табл.1.

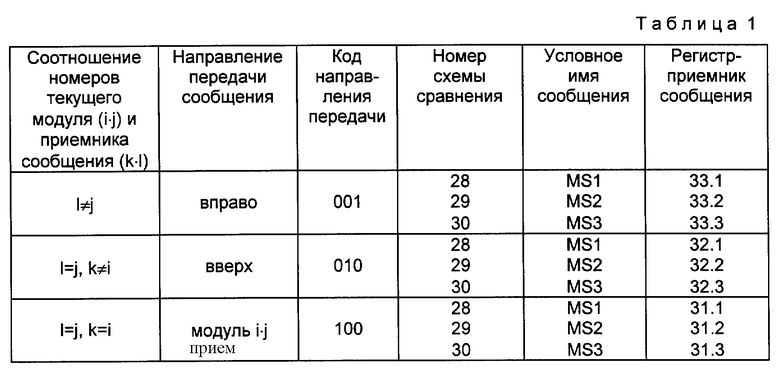

Пусть для сообщения MS1 получен код направления "001", для MS2 получен код "100", а для MS3 - "010". Указанные коды поступают на входы разрешения регистров 31.1, 32.1, 33.1; 31.2, 32.2, 33.2 и 31.3, 32.3, 33.3 соответственно и согласно табл.1 определяют запись сообщения MS1 в регистр 33.1, MS2 - в регистр 31.2, а MS3 - в регистр 32.3. Импульс p1 с первого выхода дешифратора 37 подается на входы синхронизации регистров 31.t, 32.t, 33.t, t= 1,2,3 и передним фронтом фиксирует сообщения MS1-MS3 в регистрах 33.1, 31.2 и 32.3 соответственно. Состояние остальных регистров не меняется, так как на их входах разрешения находятся нулевые сигналы. Одновременно импульс p1 поступает на управляющий выход кросс-коммутатора подается на управляющие входы БПС 21-23 и осуществляет сдвиг очередей сообщений (процесс сдвига описан выше).

Сообщения MS1, MS2, MS3 с прямых выходов регистров 33.1, 31.2, 32.3 поступают соответственно на третий информационный вход коммутатора 41, на второй информационный вход коммутатора 39 и на первый информационный вход коммутатора 40, а сигналы с инверсных выходов этих же регистров подаются соответственно на входы элементов И-НЕ 44.1, 42.2, 43.3 и так как среди этих сигналов неизбежно имеются нулевые, на выходах указанных элементов появляются сигналы логической единицы. В то же время на выходах элементов И-НЕ 42.1, 42.3, 43.1, 43.2, 44.2 и 44.3 сохраняется нулевой уровень сигнала, что обусловлено нулевым состоянием регистров 31.1, 31.3, 32.1, 32.2, 33.2, 33.3 соответственно.

Далее сигналы с выходов элементов И-НЕ 42.s, 43.s, 44.s, s=1,2,3 используются для формирования кода, управляющего коммутаторами 39-41 и обеспечивающего передачу управляющих сообщений из регистров 31.2, 32.3, 33.1 на информационные выходы кросс-коммутатора. В случае наличия в одной из групп регистров 31, 32 или 33 более одного сообщения код управления коммутаторами 39-41 формируется исходя из приоритета регистров, а передача сообщений осуществляется в порядке убывания его уровня. Приоритет регистров в группах 31-33 является фиксированным, а его уровень определяется индексами регистров, задающими их порядковые номера в соответствующих группах (например, уровень приоритета регистров в группе 32 растет от минимального для регистра 32.1 до наивысшего для регистра 32.2).

Сигнал логической единицы с выхода элемента И-НЕ 42.2 поступает на прямой вход элемента запрета 45.1, на инверсном входе которого присутствует сигнал логического нуля с выхода элемента И-НЕ 42.3, а также на первый вход И 46.1, на третьем входе которого присутствует нулевой сигнал с выхода элемента И-НЕ 42.1. На выходах элемента запрета 45.1 и элемента И 46.1 образуются соответственно единичный и нулевой сигналы, которые совместно с нулевым сигналом с выхода элемента И-НЕ 42.3 составляют код управления коммутатором 39 - "010". Аналогично на выходах элемента И-НЕ 43.3, элемента запрета 45.2, элемента И 46.2 и элемента И-НЕ 44.3, элемента запрета 45.3, элемента И 46.3 образуются коды "100" и "001" управления соответственно коммутаторами 40 и 41. Сформированный в результате объединения (конкатенации) рассмотренных кодов код управления коммутаторами 39-41 - "010100001" - поступает на информационный вход регистра 38.

Одновременно сигналы состояния регистров с выходов элементов И-НЕ 42.t, 43. t, 44.t, t=1,2,3 поступают на входы элементов И-ИЛИ 47 и 48, на выходах которых в соответствии с табл.2 формируются сигналы L1 и L2, определяющие число микротактов, требуемых для передачи сообщений MS1-MS3 на информационные выходы кросс-коммутатора. Так как в любой группе регистров 31-38 в рассматриваемом случае имеется по одному сообщению, то их передача на соответствующие выходы осуществляется одновременно в течение одного микротакта (табл.2, строка 3). Единичный сигнал с выхода элемента И-ИЛИ 47 поступает на прямой вход элемента запрета 55 и так как на инверсном входе этого элемента имеется нулевой сигнал с выхода элемента И-ИЛИ 48, передается на информационный (D) вход триггера 50. На D-входе триггера 49 образуется сигнал логического нуля.

Импульс p2 со второго выхода дешифратора 37 через элемент ИЛИ 57 поступает на вход синхронизации регистра 38 и передним фронтом фиксирует в этом регистре ранее полученный код управления коммутаторами 39-41. Этот же импульс поступает на входы синхронизации триггеров 49 и 50 и переводит их в состояния, определяемые уровнями сигналов на их D- входах (т.е. соответственно в нулевое и единичное). Единичный сигнал с прямого выхода триггера 50 поступает на второй вход элемента И 53, а нулевой сигнал с прямого выхода выхода триггера 49 - на второй вход элемента И 54.

Код управления коммутаторами "010100001" с выхода регистра 38 поступает на управляющие входы коммутаторов 39-41 и обеспечивает передачу сообщений с выходов регистров 31.2, 32.3 и 33.1 на первый, второй и третий информационные выходы кросс-коммутатора соответственно. Одновременно этот же код подается на первый вход блока элементов И 51.

Очередной импульс p3 с третьего выхода дешифратора 37 через элемент ИЛИ 58 поступает на первый-третий информационные выходы кросс-коммутатора и передним фронтом синхронизирует прием управляющих сообщений MS1-MS3 соответственно следующим модулем системы в строке (справа), Б3Б текущего модуля и следующим модулем в столбце (сверху). Если на выходе одного или двух коммутаторов 39-41 управляющие сообщения отсутствуют, т.е. имеются нулевые коды, то их запись в БПС соседних модулей (фиг.5) не вызывает изменения состояния соответствующих очередей и, таким образом, не приводит к нарушению корректности работы системы. Передача импульса синхронизации с первого информационного выхода кросс-коммутатора может быть заблокирована нулевым сигналом с выхода элемента ИЛИ 26.1 блока анализа (фиг.2).

Одновременно импульс p3 с выхода элемента ИЛИ 58 поступает на второй вход блока элементов И 51 и обеспечивает передачу на его выход кода управления с выхода регистра 38. Данный код подается на входы сброса (R) регистров 31.t, 32.t, 33.t, t=1,2,3 и осуществляет сброс тех регистров, из которых были считаны сообщения MS1-MS3, т.е. в рассматриваемом случае регистров 31.2, 32.3 и 33.1. На выходах элементов И-НЕ 42.2, 43.3, и 44.1 устанавливается нулевой уровень сигнала, при этом уровень сигнала на выходах остальных элементов И-НЕ остается неизменным.

Импульс p3 с третьего выхода дешифратора 37 также поступает на первый вход элемента И 53 и, так как на его втором входе имеется единичный сигнал с прямого выхода триггера 50, проходит через элемент И 53, через элемент ИЛИ 56, подается на вход одновибратора 59 и задним фронтом возбуждает на его выходе импульс Q. Данный импульс с выхода одновибратора 59 поступает на вход установки (S) счетчика 36 и переключает его в исходное состояние "111". Очередной импульс с выхода генератора 34 переводит счетчик 36 в состояние "000", инициируя, таким образом, начало следующего такта работы кросс-коммутатора, который аналогично предшествующему начинается с приема новой группы управляющих сообщений из БПС 21-23 в регистры групп 31-33. Если после сдвига очередей сообщений в БПС 21-23 на управляющем входе кросс-коммутатора появляется сигнал логического нуля, что свидетельствует об отсутствии сообщений в БПС 21-23, то импульс Q с выхода одновибратора 59 через открытый элемент запрета 52 поступает на вход сброса (R) триггера 35 управления и переводит его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 35 выключает генератор 34, кросс-коммутатор переходит в пассивное состояние и ожидает появления очередных управляющих сообщений на выходах БПС 21-23.

В случае если триггер 50 установлен в нулевое состояние (т.е. два или три из поступивших сообщений зафиксированы в регистрах одной группы 31, 32 или 33 и одновременная выдача всех сообщений невозможна (табл. 2)), на втором входе элемента И 53 образуется нулевой сигнал, в связи с чем импульс p3 с третьего выхода дешифратора 37 не проходит на выход элемента И 53 и кросс-коммутатор приступает к реализации второго микротакта для передачи оставшегося сообщения.

В этом случае очередной импульс p4 с четвертого выхода дешифратора 37 через элемент ИЛИ 57 поступает на вход синхронизации регистра 38 и фиксирует в нем новый код управления коммутаторами 39-41, который формируется аналогично ранее рассмотренному исходя из состояния регистров групп 31-33, т.е. уровня сигнала на выходах элементов И-НЕ 42.t, 43.t, 44.t, t=1,2,3. Код управления поступает на управляющие входы коммутаторов 39-41 и вновь обеспечивает передачу управляющих сообщений на информационные выходы кросс-коммутатора. Следующий импульс p5 с пятого выхода дешифратора 37 через элемент ИЛИ 58 поступает на информационные выходы кросс-коммутатора и на второй вход блока элементов И 51 и аналогично ранее рассмотренному обеспечивает прием сообщений и сброс соответствующих регистров групп 31-33.

Если триггер 49 установлен в состояние логической единицы (т.е. в регистрах одной из групп 31, 32 или 33 были сохранены ровно два из трех сообщений и, следовательно, для их выдачи необходимо два микротакта), то на втором входе элемента И 54 образуется сигнал логической единицы, в связи с чем импульс p5 проходит на выход этого элемента, через элемент ИЛИ 56 поступает на вход одновибратора 59 и, как было показано ранее, либо инициирует начало очередного такта работы кросс-коммутатора, либо выключает генератор 34. Если же оба триггера 49 и 50 установлены в нулевое состояние (что соответствует случаю, когда все три сообщения MS1, MS2 и MS3 сохранены в регистрах одной группы 31, 32 или 33 и для их выдачи требуется три микротакта (табл. 2, строки 9, 16 и 23), то на шестом выходе дешифратора 37 появляется импульс p6, который обеспечивает запись очередного кода управления в регистр 38. Следующий импульс p7 с седьмого выхода дешифратора 37 через элемент ИЛИ 58 поступает на информационные выходы кросс-коммутатора, второй вход блока элементов И 51, через элемент ИЛИ 56 передается на вход одновибратора 59 и осуществляет соответственно синхронизацию приема последнего сообщения, сброс соответствующего регистра в группе 31, 32 или 33 и аналогично ранее рассмотренному либо инициирует начало нового такта работы кросс-коммутатора, либо останавливает генератор 34.

Управляющее сообщение, поступающее на первый информационный выход кросс-коммутатора, передается на первый выход блока анализа (фиг. 2) и на входы элемента ИЛИ 26.1, а сообщения со второго и третьего информационных выходов - соответственно на второй и третий выходы блока анализа и соответственно на первый 14 и второй 15 информационные выходы текущего модуля (фиг. 1, 2), с которых транслируются (соседним) модулям с номерами i-1, j и i.j+1 соответственно (фиг. 7). Если информационный код на первом информационном выходе кросс-коммутатора 24 (фиг. 2) не является нулевым, то на выходе элемента ИЛИ 26.1 формируется единичный сигнал, который открывает элемент И 26.2 и тем самым разрешает прохождение импульса синхронизации с младшего разряда первого информационного выхода кросс-коммутатора 24 на первый выход блока анализа. В противном случае выдача импульса синхронизации на первый выход блока анализа не происходит.

Сообщение с первого выхода блока анализа совместно с сигналом (допустим, что этот сигнал единичный), образующимся на выходе элемента ИЛИ 26.1 и поступающим с управляющего выхода блока анализа, передаются на первый информационный вход и управляющий вход БЗБ 3 текущего модуля соответственно (фиг. 1). Единичный сигнал с управляющего входа БЗБ подается на управляющий вход коммутатора 60 (фиг. 4) и обеспечивает передачу сообщения с первого информационного входа БЗБ на информационный вход демультиплексора 61 с целью дальнейшей записи, временно блокируя прием информации с второго информационного входа. Импульс синхронизации, сопровождающий сообщение, через элемент ИЛИ 67 проходит на вторые входы элементов И 65.1-65.N и, поступая далее через открытые элементы И 65.H+1-65.N и элементы ИЛИ 66.H+1-66.N (где H - длина существующей в БЗБ очереди сообщений) на входы синхронизации регистров 62. H+1-62. N производит запись сообщения в существующую очередь (в регистр 62.H+1).

Для идентификации момента завершения очередной программы в формат команд, реализуемых системой, вводится единичная метка конца программы (Мкп) (фиг. 8). Если считанная в регистр 4 команда является последней в выполняемой программе, то единичный сигнал Мкп с выхода 4.6 регистра 4 команд поступает на второй вход блока 7 синхронизации (фиг. 1), на вход сдвига БЗБ 3, а также на управляющий вход коммутатора 8 адреса. Положительный перепад уровня сигнала, возникающий на входе сдвига БЗБ (фиг. 4), передается на вход одновибратора 69 и возбуждает на его выходе импульс, который поступает на управляющий вход демультиплексора 61, формируя на всех его выходах нулевой уровень сигнала, через элементы ИЛИ 66.1-66.N проходит на входы синхронизации регистров 62.1-62.N и производит сдвиг существующей очереди сообщений. Новый код состояния очереди сообщений с выходов элементов И 64.1-64.N поступает на входы элемента И 68 и формирует на его выходе соответствующий сигнал, который передается на управляющий выход БЗБ и далее подается на третий вход блока 7 синхронизации (фиг. 1).

Если сигнал состояния очереди на управляющем выходе БЗБ 3 принимает единичное значение (т.е. сообщения в регистрах БЗБ 3 отсутствуют), то на входах элемента И 81 (фиг. 6) происходит совпадение единиц и единичный сигнал с выхода данного элемента проходит через элемент ИЛИ 82 на вход сброса триггера 77 и переключает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 77 выключает генератор 78 и модуль переходит в состояние ожидания сигнала на реализацию очередной операции (программы) от УУВУ. Переход в данное состояние может быть также осуществлен (например, в случае аварии объекта управления) по сигналу "Стоп", подаваемому на четвертый вход блока 7 синхронизации с управляющего входа 20 модуля.

Если сигнал состояния очереди сохраняет нулевое значение, то код очередной операции с информационного выхода БЗБ 3 (с выхода регистра 62.1 (фиг. 4)) через коммутатор 8 адреса поступает на информационный вход регистра 5 адреса, где фиксируется задним фронтом очередного импульса П1 с первого выхода блока 7 синхронизации. Таким образом, (i.j)-й модуль переходит к выполнению очередной операции.

Оценим величину эффекта, получаемого при использовании предлагаемого изобретения.

Будем считать, что частоты генераторов тактовых импульсов (генератора 68 в прототипе и генератора 34 в предлагаемом устройстве) совпадают и длительности промежутков времени (фаз) между одноименными фронтами импульсов смежных импульсных последовательностей Ti, Ti+1 для прототипа (t0) (фиг. 9а) и pj, pj+1 для предлагаемого устройства (t) (фиг. 9б) равны (t0=t).

Длительность периода следования тактовых импульсов в прототипе T0=5t (фиг. 9а), а (среднее) время обработки группы из трех сообщений, поступающих с выходов первого, второго и третьего БПС, (включающей прием сообщений из БПС, анализ и передачу) равно TT0=3T0=15t (так как обработка сообщений осуществляется последовательно и производится за три такта).

Среднее время TT обработки группы из трех сообщений MS1-MS3 в предлагаемом устройстве определим следующим образом.

Будем считать, что все 27 вариантов размещения сообщений MS1-MS3 в регистрах групп 31-33 (фиг. 3), перечисленные в табл. 2, равновероятны. Очевидно, что указанные варианты образуют полную группу и несовместимы, в связи с чем вероятности обработки сообщений MS1-MS3 за один, два и три микротакта могут быть определены соответственно как

P1=6/27=0.22; P2=18/27=0.67 или P3=3/27=0.11.

Учитывая, что длительности микротактов 1, 2 или 3 равны соответственно T1= t=2t (фиг. 9б), среднее время обработки группы сообщений MS1-MS3 предлагаемым устройством

ТT=T1P1+(T1+T2)P2+(T1+T2+T3)P3=0.66t+3.35t+0.77t=4.78t.

Данное соотношение справедливо в случае, если в каждом такте работы кросс-коммутатора 24 осуществляется обработкa трех сообщений. При учете ситуаций, когда в некоторых тактах работы на входы кросс-коммутатора поступает менее трех сообщений, величина эффекта возрастает. Это объясняется увеличением общего числа вариантов размещения сообщений в регистрах групп 31, 32, 33, уменьшением вероятности появления каждого из вариантов и, следовательно, уменьшением вероятности обработки группы сообщений за два и три микротакта. Поэтому обработка сообщений блоком анализа предлагаемого устройства в среднем осуществляется более чем в 15/4.78=3.14 разa быстрее, чем в прототипе. Это позволяет сделать вывод о существенном повышении производительности коммутационных средств каждого модуля, а следовательно, и об увеличении быстродействия мультимикроконтроллерной системы в целом и расширении области ее целесообразного применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении распределенных систем программного управления, а также подсистем логического управления многоуровневых АСУ. Техническим результатом изобретения является повышение быстродействия системы путем организации параллельного (одновременного) выполнения анализа и передачи групп управляющих сообщений, поступающих на различные входы каждого из ее модулей. Система содержит множество однотипных модулей, объединенных в матричную структуру. Блок анализа каждого модуля содержит три блока памяти сообщений, элемент И, два элемента ИЛИ и кросс-коммутатор, включающий генератор номера модуля, три схемы сравнения, три группы регистров, триггер управления, генератор тактовых импульсов, счетчик, дешифратор, регистр, три коммутатора, три группы элементов И-НЕ, две группы элементов И, два элемента И-ИЛИ, два триггера, блок элементов И, четыре элемента И, три элемента ИЛИ и одновибратор. 2 з.п. ф-лы, 2 табл., 9 ил.

включает блок памяти программ, блок анализа, буферный запоминающий блок, регистр команд, регистр адреса, мультиплексор логических условий, блок синхронизации, коммутатор адреса, блок элементов запрета, блок элементов И, элемент И, причем выход коммутатора адреса подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом регистра команд, выходы кода логического условия и модифицируемого разряда адреса которого подключены соответственно к адресному и первому информационному входам мультиплексора логических условий, второй информационный вход которого соединен с входом логических условий модуля, а выход в объединении с выходом немодифицируемой части адреса регистра команд подключен к первому информационному входу коммутатора адреса, выход операционного поля регистра команд соединен с первыми входами блока элементов запрета и первыми входами блока элементов И, выход блока элементов запрета подключен к операционному выходу модуля, выход блока элементов И в объединении с выходом элемента И подключен к первому входу блока анализа, выход метки передачи управления регистра команд соединен с вторыми входами блока элементов запрета и блока элементов И и с первым входом элемента И, первый вход блока синхронизации соединен с первым управляющим входом модуля, выход метки конца программы регистра команд подключен к входу сдвига буферного запоминающего блока, к второму входу блока синхронизации и к управляющим входам коммутатора адреса, первый, второй и третий выходы блока синхронизации соединены соответственно с входом синхронизации регистра адреса, с входом синхронизации регистра команд и с вторым входом элемент И, второй и третий входы блока анализа подключены соответственно к первому и второму информационным входам модуля, управляющий выход блока анализа соединен с управляющим входом буферного запоминающего блока, выходы блока анализа с первого по третий подключены соответственно к первому информационному входу буферного запоминающего блока, к первому и второму информационным выходам модуля, второй информационный вход и информационный выход буферного запоминающего блока соединены соответственно с входом кода операции модуля и с вторым информационным входом коммутатора адреса, управляющий выход буферного запоминающего блока подключен к третьему входу блока синхронизации, четвертый вход которого соединен с вторым управляющим входом модуля, первый информационный вход (i, j)-го модуля, где

включает блок памяти программ, блок анализа, буферный запоминающий блок, регистр команд, регистр адреса, мультиплексор логических условий, блок синхронизации, коммутатор адреса, блок элементов запрета, блок элементов И, элемент И, причем выход коммутатора адреса подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом регистра команд, выходы кода логического условия и модифицируемого разряда адреса которого подключены соответственно к адресному и первому информационному входам мультиплексора логических условий, второй информационный вход которого соединен с входом логических условий модуля, а выход в объединении с выходом немодифицируемой части адреса регистра команд подключен к первому информационному входу коммутатора адреса, выход операционного поля регистра команд соединен с первыми входами блока элементов запрета и первыми входами блока элементов И, выход блока элементов запрета подключен к операционному выходу модуля, выход блока элементов И в объединении с выходом элемента И подключен к первому входу блока анализа, выход метки передачи управления регистра команд соединен с вторыми входами блока элементов запрета и блока элементов И и с первым входом элемента И, первый вход блока синхронизации соединен с первым управляющим входом модуля, выход метки конца программы регистра команд подключен к входу сдвига буферного запоминающего блока, к второму входу блока синхронизации и к управляющим входам коммутатора адреса, первый, второй и третий выходы блока синхронизации соединены соответственно с входом синхронизации регистра адреса, с входом синхронизации регистра команд и с вторым входом элемент И, второй и третий входы блока анализа подключены соответственно к первому и второму информационным входам модуля, управляющий выход блока анализа соединен с управляющим входом буферного запоминающего блока, выходы блока анализа с первого по третий подключены соответственно к первому информационному входу буферного запоминающего блока, к первому и второму информационным выходам модуля, второй информационный вход и информационный выход буферного запоминающего блока соединены соответственно с входом кода операции модуля и с вторым информационным входом коммутатора адреса, управляющий выход буферного запоминающего блока подключен к третьему входу блока синхронизации, четвертый вход которого соединен с вторым управляющим входом модуля, первый информационный вход (i, j)-го модуля, где  подключен к второму информационному выходу (i, j-1)-го модуля, а первый информационный вход (i.1)-го модуля соединен с вторым информационным выходом (i. n)-го модуля, второй информационный вход (k.l)-го модуля, где

подключен к второму информационному выходу (i, j-1)-го модуля, а первый информационный вход (i.1)-го модуля соединен с вторым информационным выходом (i. n)-го модуля, второй информационный вход (k.l)-го модуля, где  подключен к первому информационному выходу (k+1. l)-го модуля, а второй информационный вход (m/l)-го модуля соединен с первым информационным выходом (1.l)-го модуля, отличающаяся тем, что блок анализа содержит с первого по третий блоки памяти сообщений, кросс-коммутатор, первый и второй элементы ИЛИ, элемент И, причем информационные входы блоков памяти сообщений с первого по третий, подключены соответственно к входам блока анализа с первого по третий, информационные выходы блоков памяти сообщений с первого по третий соединены с первым, вторым и третьим информационными входами кросс-коммутатора соответственно, выходы состояния блоков памяти сообщений с первого по третий соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с управляющим входом кросс-коммутатора, управляющий выход которого подключен к управляющим входам блоков памяти сообщений с первого по третий, старшие разряды первого информационного выхода кросс-коммутатора соединены с первым выходом блока анализа и входами второго элемента ИЛИ, выход которого соединен с управляющим выходом блока анализа и первым входом элемента И, второй вход и выход которого подключены соответственно к младшему разряду первого информационного выхода кросс-коммутатора и первому выходу блока анализа, второй и третий выходы которого соединены с вторым и третьим информационными выходами кросс-коммутатора соответственно.

подключен к первому информационному выходу (k+1. l)-го модуля, а второй информационный вход (m/l)-го модуля соединен с первым информационным выходом (1.l)-го модуля, отличающаяся тем, что блок анализа содержит с первого по третий блоки памяти сообщений, кросс-коммутатор, первый и второй элементы ИЛИ, элемент И, причем информационные входы блоков памяти сообщений с первого по третий, подключены соответственно к входам блока анализа с первого по третий, информационные выходы блоков памяти сообщений с первого по третий соединены с первым, вторым и третьим информационными входами кросс-коммутатора соответственно, выходы состояния блоков памяти сообщений с первого по третий соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с управляющим входом кросс-коммутатора, управляющий выход которого подключен к управляющим входам блоков памяти сообщений с первого по третий, старшие разряды первого информационного выхода кросс-коммутатора соединены с первым выходом блока анализа и входами второго элемента ИЛИ, выход которого соединен с управляющим выходом блока анализа и первым входом элемента И, второй вход и выход которого подключены соответственно к младшему разряду первого информационного выхода кросс-коммутатора и первому выходу блока анализа, второй и третий выходы которого соединены с вторым и третьим информационными выходами кросс-коммутатора соответственно.

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| DE 4026871 A1, 28.03.91 | |||

| НОВЫЕ СОЕДИНЕНИЯ 707 И ИХ ПРИМЕНЕНИЕ | 2008 |

|

RU2472781C2 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

1998-10-10—Публикация

1997-03-25—Подача