(54) УСТРОЙСТВО ДЛЯ РЕШСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации сигналов неисправности | 1987 |

|

SU1495802A1 |

| Устройство для регистрации сигналов неисправности | 1982 |

|

SU1132291A1 |

| Устройство для контроля логического блока | 1986 |

|

SU1383361A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ | 1990 |

|

RU2010313C1 |

| Устройство для регистрации сигналов неисправности | 1985 |

|

SU1278859A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство контроля кода счетчика | 1979 |

|

SU815920A1 |

| Устройство для формирования пачки импульсов | 1983 |

|

SU1193784A1 |

| Устройство для поиска неисправностей | 1982 |

|

SU1059550A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

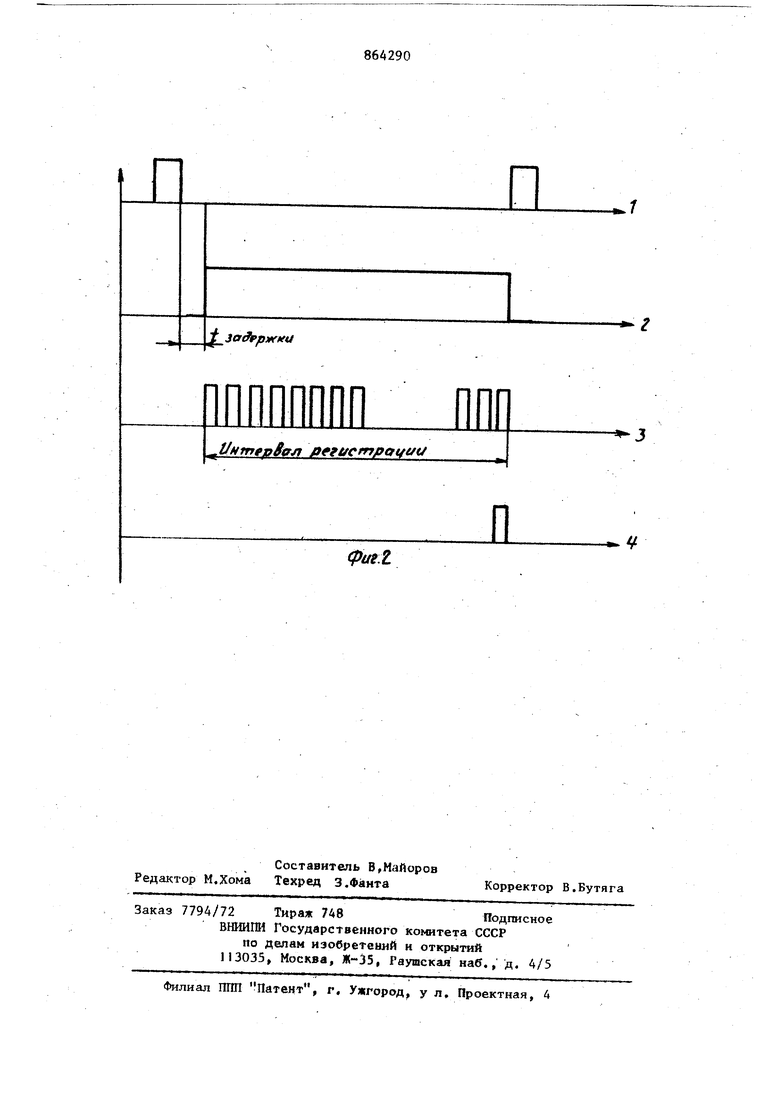

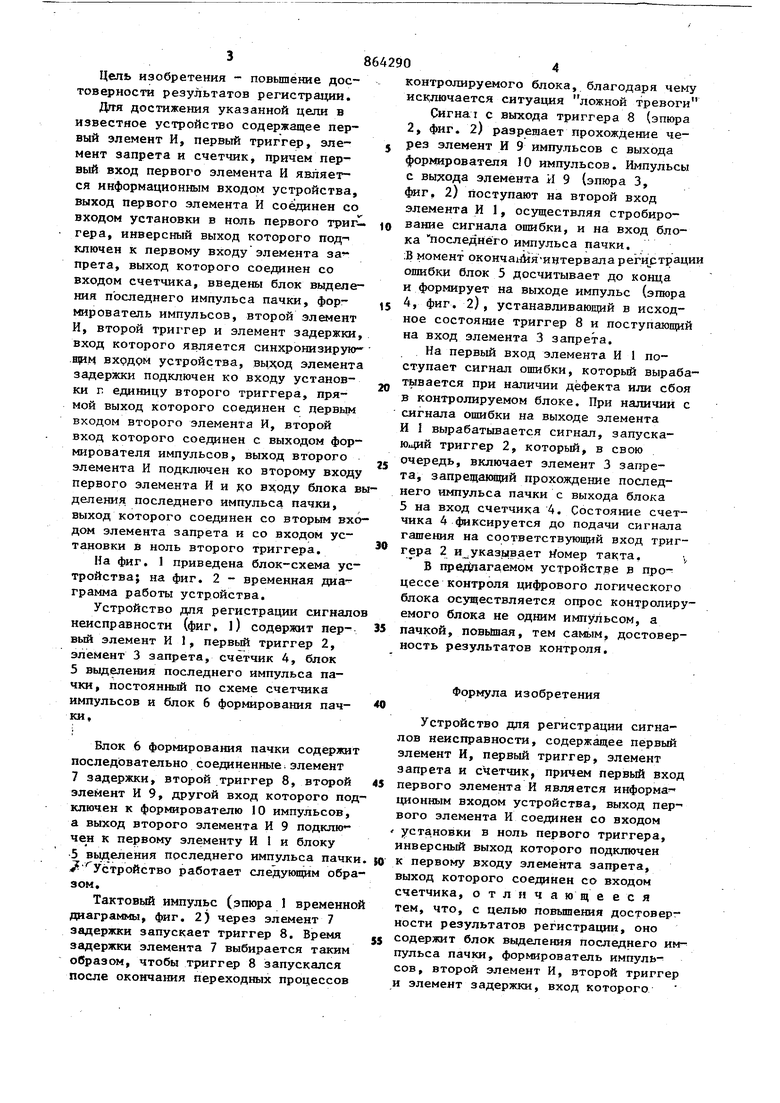

Изобретение относится к автоматике вычислительной технике и можетбыть использовано для регистрации сигналов Неисправности от логических блоков. Известны контрольшле устройства для проверки 1Ц{фровых логических блоков, содержлщие элементы И, НЕ, триггеры, которые позволяют фикси- ровать сигнал ошибки от момента опроса синхро-инпульсом до момента подачи сигнала гашения . Однако эти устройства характеризуются недостаточной разрешающей способностью, поскольку не фиксируют норм такта в момент возникновения ошибки. Наиболее близким к лредпагаемому является устройство, в которое введены элемент запрета и счетчик тактовых импульсов. Фиксируя состояние счетчика, удается найти номер такта и внутреннее состояние проверяемого логи ческого блока в момент возникновения ошибки. Оно содержит элемент И, подключенный к триггеру, выход которого подключен ко входу злемента запрета, другой вход которого объединен с . ответствукящ1н входом элемента И, а выход элемента запрета соединен со входом счетчика тактовых импулы сов Сз. Недостатком этого устройства является малая достоверность проверки логических блоков, поскольку оно не чувствительно к сигналг ошибки, не совпадакицим по времени с синхронизируняцим импульсом В частности, если синхронизирующий импульс совмещается с серединой интервала опроса контрсщирующего блока между двумя тактовыми импульсами, то известное устройство нечувствительно к сигналам ошибки у фронтов интервала. Если сйнхро низирующий импульс расположен у одного из фронтов интервала опроса, то устройство нечувствительно к сигналам ошибки у другого фронта и середины интервала. 38 Цель изобретения - повышение достоверности результатов регистрации. Дггя достижения указанной цели в известное устройство содержащее первый элемент И, первый триггер, элемент запрета и счетчик, причем первый вход первого элемента И является информационным входом устройства, выход первого элемента И соединен со входом установки в ноль первого триггера, инверсный выход которого подключен к первому входу элемента за прета, выход которого соединен со входом счетчика, введены блок выделения последнего импульса пачки, фор1«1рователь импульсов, второй элемент И, второй триггер и элемент задержки вход которого является синхронизирунг .ярм вхрдрм устройства, выдод элемента задержки подключен ко входу установки г. единицу второго триггера, прямой выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом формирователя импульсов, выход второго элемента И подключен ко второму входу первого элемента И и ко входу блока в деления последнего импульса пачки, выход которого соединен со вторым вх дом элемента запрета и со входом установки в ноль второго триггера. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - временная диаграмма работы устройства. Устройство для регистрации сигнал неисправности (фиг. l) содержит первый элемент И 1, первый триггер 2, элемент 3 запрета, счетчик 4, блок 5 выделения последнего импульса пачки, постоянный по схеме счетчика импульсов и блок 6 формирования пачки. Блок 6 формирования пачки содержи последовательно соединенные элемент 7 задержки, второй триггер 8, второй элемент И 9, другой вход которого по ключен к формирователю 10 импульсов, а выход второго элемента И 9 подклю че н к первому элементу И 1 и блоку 5 вьщеления последнего импульса пачк Устройство работает следующим обр зом. Тактовый импульс (эпюра 1 временн диаграммы, фиг. 2) через элемент 7 задержки запускает триггер 8. Бремя задержки элемента 7 выбирается таким образом, чтобы триггер 8 запускался после окончания переходных процессов контролируемого блока, благодаря чему исключается ситуация ложной тревоги Сигнат с выхода триггера 8 (эпюра 2, фиг. 2) разрешает прохождение через элемент И 9 импульсов с выхода фор14ирователя 10 импульсов. Импульсы с элемента И 9 (эпюра 3, фиг, 2) поступают на второй вход элемента И 1, осуществляя стробирование сигнала ошибки, и на вход блока последнего импульса пачки. :В момент oкoнчai я интepвaлaperи ;тpaции ошибки блок 5 досчитывает до конца и формирует на выходе импульс (эпюра 4, фиг. 2), устанавливающий в исходное состояние триггер 8 и поступающий на вход элемента 3 запрета. На первый вход элемента И 1 поступает сигнал ошибки, который вырабатывается при наличии дефекта или сбоя в контролируемом блоке. При наличии с сигнала ошибки на выходе элемента И 1 вырабатывается сигнал, запускаЮиЩЙ триггер 2, который, в свою очередь, включает элемент 3 запрета, запрещакищй прохождение последнего импульса пачки с выхода блока 5 на вход счетчика 4. Состояние счетчика 4 4иксируется до подачи сигнала гашения на соответствующий вход триггера 2 и указывает rfoMep такта. ,, В предлагаемом устройстве в процессе контроля цифрового логического блока осуществляется опрос контролируемого блока не одним импульсом, а пачкой, повышая, тем самым, достоверность результатов контроля. Формула изобретения Устройство для регистрации сигналов неисправности, содержащее первый элемент И, первый триггер, элемент запрета и счетчик, причем первый вход первого элемента И является информа ционным входом устройства, выход первого элемента И соединен со входом уста.новки в ноль первого триггера, инверсный выход которого подключен к первому входу элемента запрета, выход которого соединен со входом счетчика, отличающееся тем, что, с целью повьш1еш1я достоверг ностн результатов регистрации, оно содержит блок выделения последнего импульса пачки, формирователь импульсов, второй элемент И, второй триггер и элемент задержки, вход которого

является синхронизирующим входом , устройства, выход элемента задержки подключен ко входу установки в е;циницу второго триггера, прямой вьщод которого соединен с первым входом второ го элемента И, второй вход которого соединен с.выходом формирователя импульсов, выход второго элемента И подключен ко второму входу первого элемента И и ко входу вьщеления по следнего импульса пачки, выход но-торого соединен со вторым В2 :одом эле

мента запрета и со входом установки в ноль второго триггера.

Источники информации, принятые во BHHMaime при эксцертизе

1,Ав орское свидетельство СССР № 543895, кп. G 01 F 31/28, 1975,

2,Патент Японии W , кл, 97(7) (С 06 F П/ОО), опуилиц, 1977,

3,Патент Японии ff , кл, 97(7) G 01 (G 06F 11/00), опублик. 1977 (прототип).

3aA 3fffea

т

фиг1

Авторы

Даты

1981-09-15—Публикация

1979-01-16—Подача