Настоящее изобретение относится к схеме вычисления величины постоянного тока, подаваемого на устройство управления преобразованием кода, для использования в способе кодирования канала цифровой системы записи и воспроизведения.

Цифровая система записи и воспроизведения должна решать следующие проблемы, вызванные в основном видеоголовкой и лентой, а также вращающимся трансформатором. Именно: 1) Так как вращающийся трансформатор не может передавать или пропускать сигнал постоянного тока, компонент постоянного тока цифрового сигнала, т.е. уровни постоянного тока, которые представляют логические условия двоичных "1" и "0", отсекаются. Это означает, что цифровой сигнал записывается без своего первоначального компонента постоянного тока. 2) Если видеоголовка и лента функционируют в зоне высокой частоты, которая превышает заданную частоту, цифровой сигнал не может быть записан и воспроизведен из-за различных потерь. Соответственно минимальная величина длительности последовательности импульсов Tmin должна быть большой. 3) Так как магнитная система записи и воспроизведения имеет характеристику 6 дБ/окт по отношению к зоне низкой частоты, сигнал, имеющий компонент низкой частоты, не может быть записан. Соответственно максимальная величина длительности последовательности импульсов Tmax должна быть небольшой. 4) Ширина полосы пропускания частоты сигнала, который записывается и воспроизводится в соответствии с пунктами 2) и 3) выше, должен быть сужен до границ заданной полосы пропускания частот. Соответственно отношение Tmax/Tmin, т.е. максимальной длительности последовательности импульсов к минимальной длительности последовательности импульсов, должно быть небольшим. 5) В течение периода воспроизведения изменение уровней постоянного тока должно подавляться для пользы конструкции эквалайзера и предотвращения нелинейных искажений, т.е. предотвращения отклонения от линейной зоны кривой гистерезиса.

Поэтому для решения вышеназванных проблем цель настоящего изобретения состоит в создании схемы вычисления величины постоянного тока для использования в цифровой системе записи и воспроизведения безотносительно к увеличению или уменьшению количества бит кодового слова в устройстве управления преобразованием кода, чтобы выбрать оптимальное кодовое слово с помощью величины постоянного тока предшествующего кодового слова из множества кодовых слов, которые уже установлены в отношении информационного слова, чтобы снизить изменение уровня постоянного тока.

Для достижения вышеназванной цели настоящего изобретения предусматривается схема вычисления величины постоянного тока для использования в системе устройства управления преобразованием кода, имеющей первое запоминающее средство для преобразования множества кодовых слов (слов символов) в информационное слово, посланное заранее определенным блоком, и запоминания кодового слова, величина постоянного тока которого является положительной среди многих кодовых слов, соответствующих информационному слову, чтобы управлять преобразованием кода для выбора оптимального кодового слова в операции записи и воспроизведения; второе запоминающее средство для запоминания кодированного слова, величина постоянного тока которого среди многих кодовых слов, последовательных по отношению к средству параллельного преобразования, для преобразования сигнала, посланного от первого запоминающего средства или второго запоминающего средства на формат последовательных данных; средство выборки для селективной подачи сигналов, посылаемых из первого запоминающего средства и второго запоминающего средства на средство преобразования последовательного в параллельное. При этом схема вычисления величины постоянного тока для вычисления величины постоянного тока текущего выходного кодового слова использует сигнал, поданный от последовательного преобразователя на параллельный, и посылает управляющий сигнал на средство выборки, чтобы выбрать сигнал, который должен быть подан на средство последовательного преобразования в параллельное, среди многих кодовых слов, соответствующих информационному слову, следующих за текущим информационным словом. Схема вычисления величины постоянного тока согласно настоящему изобретению отличается тем, что включает в себя:

- средство генерирования импульса нагрузки для генерирования второго синхронизирующего сигнала и импульса нагрузки с частотой, деленной на заданную величину с помощью основного синхросигнала;

- счетное средство для загрузки опорной величины с помощью сигнала, посылаемого от средства генерирования сигнала нагрузки и реверсивного отсчета последовательных данных, посылаемых от средства последовательного преобразования в параллельное;

- средство детектирования для детектирования, является или нет величина, отсчитанная в счетном средстве, той же самой, что и опорная величина;

- третье запоминающее средство для запоминания предшествующей входной величины, когда опорная величина является такой же, как величина, отсчитанная в средстве отсчета, и запоминание величины, отсчитанной в средстве отсчета, когда опорная величина является такой же, как величина, отсчитанная в средстве отсчета;

- средство сравнения для сравнения величины сигнала, посланного от третьего запоминающего средства, с размером опорной величины, и подача результирующей величины как сигнала для управления операцией средства выборки.

Вышеназванная цель и другие преимущества настоящего изобретения станут более очевидны из подробного описания предпочитаемого варианта реализации его со ссылкой на прилагаемые чертежи, среди которых:

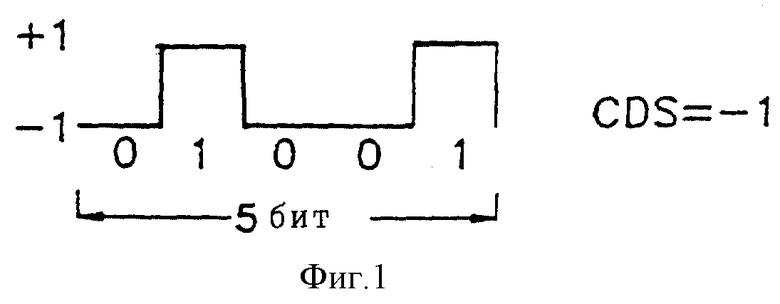

фиг. 1 - схема концепции цифровой суммы кодового слова (CDS);

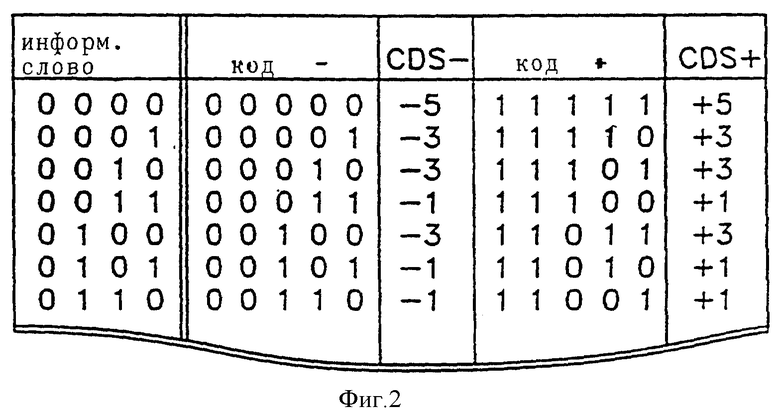

фиг. 2 - таблица, представляющая пример применяемых информационных слов и их величины CDS;

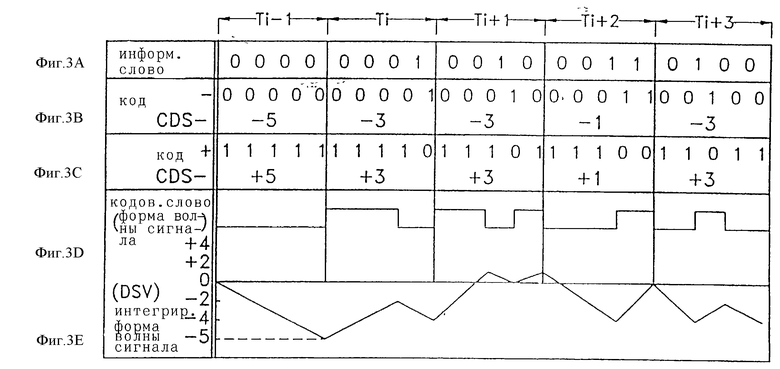

фиг. 3A - 3E схемы концепции относительно величины постоянного тока (DSV, изменение цифровой суммы), соответствующей величине CDS по отношению к информационному слову.

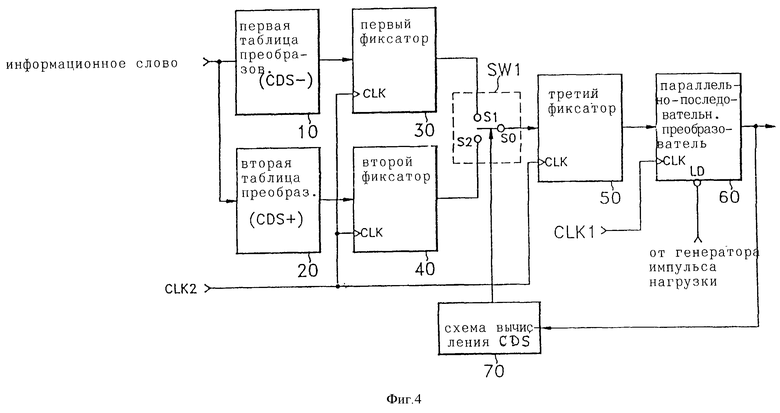

фиг. 4 - блок-схема варианта реализации устройства управления преобразованием кода, в которой схема вычисления величины постоянного тока согласно настоящему изобретению применена;

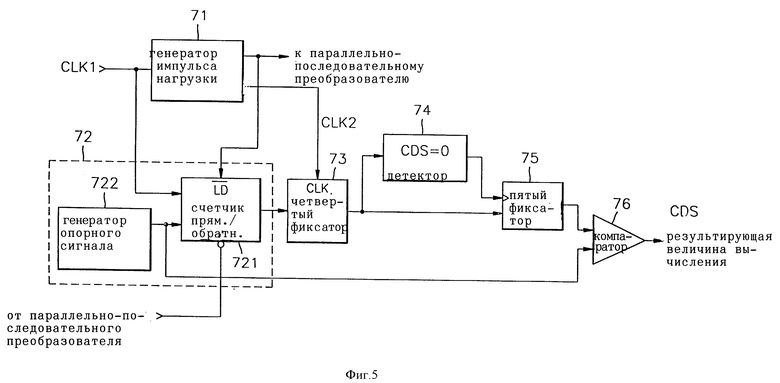

фиг. 5 - блок-схема схемы вычисления величины постоянного тока согласно настоящему изобретению;

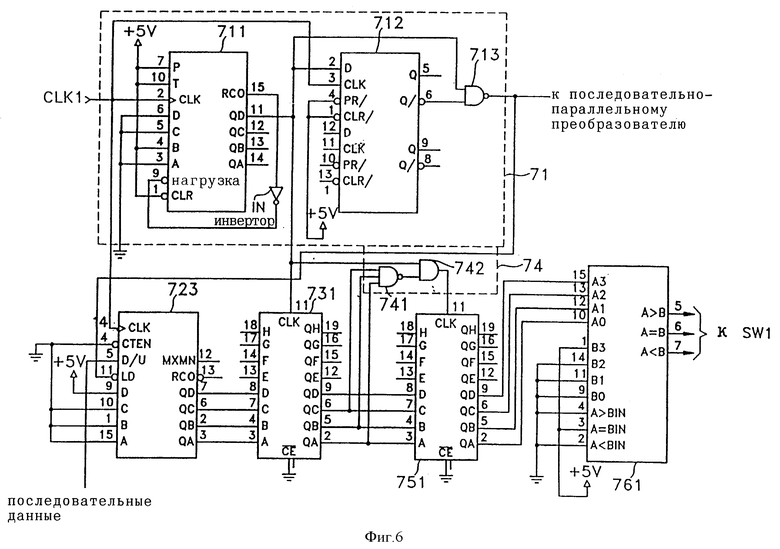

фиг. 6 - детальное схемное изобретение варианта реализации схемы вычисления величины постоянного тока согласно настоящему изобретению, показанной на фиг. 5;

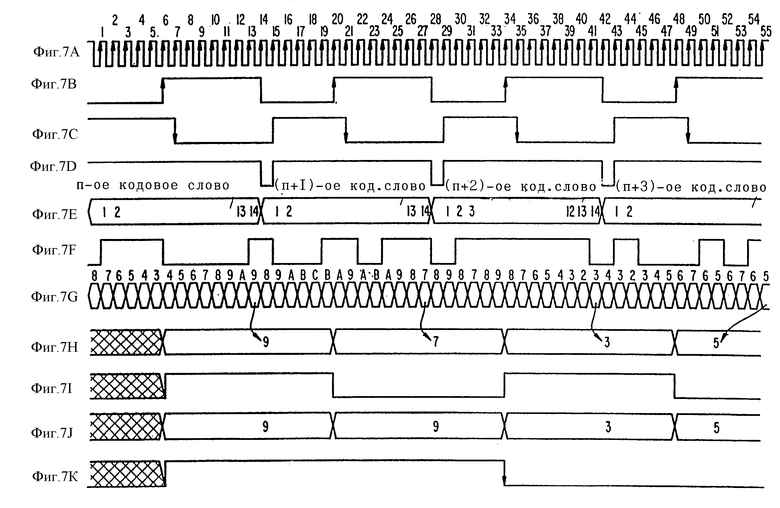

фиг. 7A-7K представляют графические изображения выходных форм волны соответствующих участков, показанных на фиг. 6;

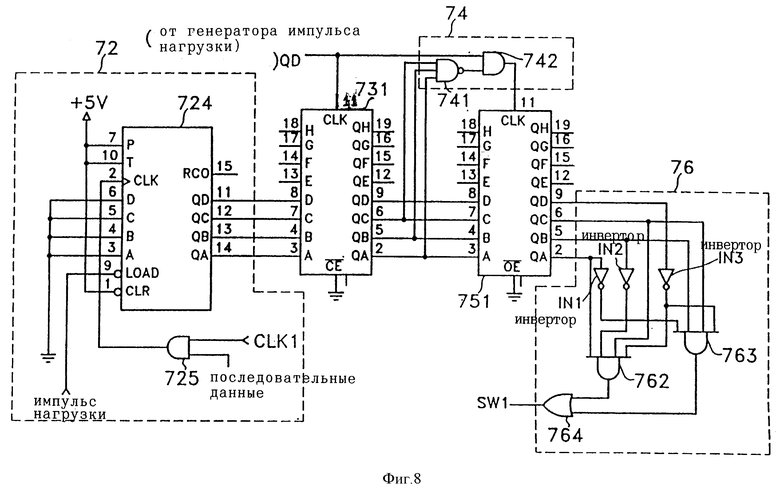

фиг. 8 - детальное схемное изображение другого варианта реализации схемы вычисления величины постоянного тока согласно настоящему изобретению, показанной на фиг. 5;

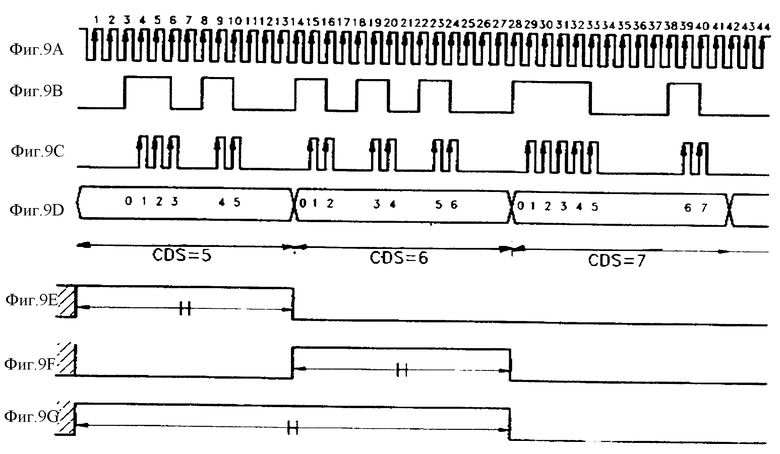

фиг. 9A-9G - графические изображения выходных форм волны соответствующих участков, показанных на фиг. 8.

Фиг. 1 является схемой концепции CDS, которая вычисляет величину постоянного тока кодового слова по отношению к одному информационному слову путем вычисления как величины постоянного тока - 1 В, когда бит, составляющий кодовое слово, представляет двоичный "0", и как величину постоянного тока +1 В, когда представляющий ее бит является двоичной "1". На фиг. 1 показано применение вышеназванной концепции вычисления, выбирая пример кодового слова "01001" (которое именуется как слово), в котором величина CDS равна "-1".

Фиг. 2 представляет пример кодового слова, которое должно быть преобразовано в информационное слово, где используют способ кодирования канала для преобразования информационного слова, применяемого как одиночная запись одного блока в отношении слова символа согласно заданному правилу. Здесь показаны четыре бита как одиночная запись одного блока в качестве примера, но вообще одиночная запись одного блока состоит из восьми бит. Также показано пятибитовое кодовое слово как одиночная запись, которая должна быть преобразована, в качестве примера, но вообще используется кодовое слово из десяти бит или четырнадцати бит. Иллюстрируемый способ кодирования в отношении такого условия бит имеет модуляцию от восьми до четырнадцати бит, (ЕГМ). Кодовое слово в отношении информационного слова зависит от заданной величины и представлено как два или больше чисел слова символа. Но здесь применяются два кодовых слова, имеющих характеристики, инвертированные относительно друг друга, и кодовое слово, величина постоянного тока которого очень близка в "0", выбирается и подается из числа других кодовых слов.

Иначе говоря, слово символа, соответствующее для преобразования по отношению к информационному слову "0000", может быть "00000" и "11111", и одно из них выбирается и подается как кодовое слово, соответствующее информационному слову. Но если первым подается вышеупомянутое информационное слово, любое одно из вышеупомянутых двух кодовых слов может быть выбрано без больших проблем. Если выбирается кодовое слово, величина CDS которого равна "-5", как показано на фиг. 3, это означает, что имеется большее количество двоичных "0", чем двоичных "1" в текущем выбранном кодовом слове. Соответственно, выбирается кодовое слово, которое имеет меньшее количество "0" в качестве кодового слова в отношении следующего информационного слова.

Соответственно кодовое слово "11110", величина CDS которого равна +3, выбирается среди "00001" и "11110" как таковое в отношении следующего информационного слова "0001". Такая выборка кодовых слов будет описываться подробно через схему вычисления, которая теперь описывается.

На фиг. с 3A по 3E показано рассмотрение уровня постоянного тока кодового слова, когда кодовое слово по отношению к информационному слову установлено, как показано на фиг. 2, и его величины DSV. DSV есть величина постоянного тока в некоторый момент времени, когда CDS кодовых слов, принимаемых последовательно, непрерывно накапливается.

На фиг. 4 показана блок-схема устройства управления преобразованием кода, в котором применяются схема вычисления CDS согласно настоящему изобретению и состав его компонентов.

На фиг. 4 устройство управления преобразованием кода содержит первую таблицу преобразования 10 для считывания отрицательного кодового слова, соответствующего информационному слову в отношении преобразования кода, вторую таблицу преобразования 20 для считывания положительного кодового слова, соответствующего информационному слову, посланного на первую таблицу преобразования 10, первое запоминающее средство, например, фиксатор 30 для синхронизации сигнала, посланного от первой таблицы преобразования 10, с сигналом, посланным от второй таблицы преобразования 20; второе запоминающее средство, например, фиксатор 40 для синхронизации сигнала, посланного от второй таблицы преобразования 20, с сигналом, посланным от первой таблицы преобразования 10, таким же образом, как в случае первого запоминающего средства, например, фиксатора 30; средство выборки SWI для выборочной подачи сигналов, посылаемых от первого фиксатора 30 и второго запоминающего средства, например, фиксатора 40; третье запоминающее средство, например, фиксатор 50 для временного запоминания сигналов, посылаемых от средства выборки SWI, чтобы посылать на выход загруженные сигналы, как в фиксаторах 30 и 40; параллельно-последовательный преобразователь 60 для преобразования параллельных данных, посылаемых от третьего фиксатора 50, в последовательные данные; схему выделения CDS 70 для приема последовательных данных, посылаемых от параллельно-последовательного преобразователя 60, и вычисления величины CDS, и подачи сигнала, управляющего функционированием средства выборки SWI посредством вычисленного результата.

Здесь первый, второй и третий фиксаторы 30, 40 и 50 синхронизированы синхросигналом CLK2, который получают путем деления четырнадцати основных синхросигналов CLK1. Синхросигнал параллельно-последовательного преобразователя 60 является основным синхросигналом CLK1, и параллельно-последовательный преобразователь 60 загружает синхросигнал посредством импульса нагрузки, посылаемого от генератора импульса нагрузки 71, о чем будет описано ниже.

Фиг. 5 является блок-схемой, показывающей схему вычисления CDS 70 согласно настоящему изобретению.

На фиг. 5 схема вычисления CDS 70 содержит генератор импульса нагрузки 71 для приема основного синхросигнала CLK1 и генерирования импульса нагрузки; счетное средство 72 для приема основного синхросигнала CLK1 как входного сигнала и приема сигнала, посылаемого от генератора импульса нагрузки 71 как управляющего сигнала, четвертое запоминающее средство, например, фиксатор 73 для временного запоминания сигнала, посланного от счетного средства 72, как в фиксаторах 30, 40 и 50 на фиг. 4; пятое запоминающее средство, например, фиксатор 75 для приема сигнала, посланного от четвертого фиксатора 73; детектор 74 для приема сигнала, посланного от четвертого фиксатора 73, и для определения является величина CDS, равная нулю, и подачи результирующей величины на пятый фиксатор 75; компаратор 76 для приема сигнала, посланного от пятого фиксатора 75, и для сравнения с заданной опорной величиной и подачи результирующей величины вычисления CDS на средство выборки SWI.

Здесь счетное средство 72 содержит генератор опорного сигнала 722 для генерирования заданной опорной величины, счетчик 721 с реверсивным включением сигнала, подаваемым от параллельно-последовательного преобразователя 60 на фиг. 4, и для загрузки сигнала, посылаемого от генератора опорного сигнала 722 посредством сигнала, посылаемого от генератора импульса нагрузки 71, и для отсчета основного синхросигнала CLK1. Опорное напряжение компаратора 76 также является сигналом, посылаемым генератором опорного сигнала 722.

Фиг. 6 представляет изображение подробной схемы реализации схемы вычисления CDS 70 согласно настоящему изобретению.

На фиг. 6 генератор импульса нагрузки 71 содержит счетчик 711 для приема основного синхросигнала CLK1 как входного сигнала вывода синхронизации и для загрузки основного синхросигнала CLK1 посредством инвертированного сигнала выходного сигнала PCO, и для подачи сигнала, который получен в результате деления на четырнадцать основных синхросигналов CLK1, D-триггер 712 для приема выходного сигнала вывода QD счетчика 711, логическое устройство 713 для выполнения операции И-НЕ сигнала, посланного от вывода QD-триггера 712 и сигнала, посланного от вывода QD счетчика 711.

Счетное средство 72 содержит счетчик 723, опорным сигналом которого является семь, для отсчета основного синхросигнала CLK1, когда он загружается выходным сигналом логического устройства 713. Четвертый фиксатор 73 содержит схему фиксатора 731 для приема сигнала, посланного от выводов QA по QD счетчика 723 как входных сигналов входных выводов его с A по D соответственно.

Детектор 74 содержит логическое устройство 741 для выполнения операции И-НЕ выходных сигналов выводов с QA по QC схемы фиксатора 731 и логическую схему 742 для выполнения операции И выходного сигнала логического устройства 741 и деленного на четырнадцать синхросигнала CLK2.

Пятый фиксатор 75 содержит схему фиксатора 751 для приема сигнала, посылаемого от выводов с QA по QD схемы фиксатора 731 как входного сигнала выводов ее с A по D, для приема сигнала, посылаемого от логического устройства 742 как входного сигнала вывода синхронизации CLK.

Компаратор 76 на фиг. 5 содержит компаратор 761 для приема сигнала, посланного от выводов с QA по QD схемы фиксатора 751 как входного сигнала ее выводов с A3 по А0, входные выводы опорного сигнала которых B3-B0 применяются с величиной десятичной 7, как в счетчике 723, и для подачи на выход величины с выходного вывода как сигнала высокого уровня по отношению к соответствующему уравнению операции путем сравнения величины, посланной на вывод A, и величины, посланной на вывод D.

На фиг. с 7A по 7K представлены изображения выходных форм волны сигнала соответствующих частей, показанных на фиг. 6. Фиг. 7A представляет основной синхросигнал CLK1. Фиг. 7B представляет синхросигнал CLK2, который получен в результате деления частоты на четырнадцать выходного сигнала QD счетчика 711. Фиг. 7C представляет выходной сигнал Q/, посланный от D-триггера 712. Фиг. 7D представляет выходной сигнал логического устройства 713. Фиг. 7E представляет последовательные данные, посланные от параллельно-последовательного преобразователя 60. Фиг. 7F представляет пример последовательных данных как на фиг. 7E. Фиг. 7G показывает выходные сигналы выводов QA-QD счетчика 723. Фиг. 7H представляет изображение выходной формы волны схемы фиксатора 731. Фиг. 71 представляет изображение входной формы волны логического устройства 741. Фиг. 7J представляет изображение выходной формы волны схемы фиксатора 751, и фиг. 7K представляет изображение выходной формы волны компаратора 761.

Фиг. 8 представляет блок-схему другого варианта реализации схемы вычисления CDS согласно настоящему изобретению, показанной на фиг. 5.

На фиг. 8 генератор импульса нагрузки 71, четвертый фиксатор 73, пятый фиксатор 75, детектор 74 имеют одну и ту же композицию, которая показана на фиг. 6.

Счетное средство 72 содержит логическое устройство 725 для выполнения операции И основного синхросигнала CLK1 и сигнала, посланного от параллельно-последовательного преобразователя 60, счетчик 724 для приема выходного сигнала логического устройства 725 как входного сигнала вывода синхронизации, и для загрузки импульсом нагрузки, подаваемым генератором импульса нагрузки 71, и для установки опорного сигнала, посланного на выводы с A по D на величину десятичного 0.

Компаратор 76 содержит инвертор IN1 для инвертирования выходного сигнала QA схемы фиксатора 751, инвертор IN2 для инвертирования выходного сигнала QB, инвертор IN3 для инвертирования выходного сигнала QD, логическое устройство 762 для выполнения операции И выходных сигналов QA и QC фиксатора 751 и выходных сигналов инверторов IN2 и IN3, логическое устройство 761 для выполнения операции И выходных сигналов инверторов IN2 и IN3 и выходных сигналов QP и QC, и логическое устройство 764 для выполнения операции ИЛИ выходных сигналов логических устройств 762 и 763.

Фиг. с 9A по 9G представляют выходные формы волн соответствующих частей, показанных на фиг. 8. Фиг. 9A представляет основной синхросигнал CLK1. Фиг. 9B - последовательные данные, посланные от последовательно-параллельного преобразователя 761. Фиг. 9C - сигнал, посланный от логического устройства 725. Фиг. 9D - сигнал, посланный от счетчика 724. Фиг. 9E - выходной сигнал логического устройства 762. Фиг. 9F - выходной сигнал логического устройства 763 и фиг. 9G - выходной сигнал логического устройства 764.

Операции вышеописанных вариантов реализации изложены ниже поочередно.

Прежде всего, устройство управления преобразованием кода, показанного на фиг. 4, функционирует следующим образом. Когда информационное слово послано как формат "0000", как показано на фиг. 3, соответствующее отрицательное кодовое слово будет выходным сигналом от первой таблицы преобразования 10, хранящей отрицательные кодовые слова в отношении соответствующих информационных слов, тем самым считывает величину "00000", тогда как соответствующее положительное кодовое слово, т.е. величина "11111", считывается из второй таблицы преобразования 20, хранящей положительные кодовые слова.

Произведенные величины, как описано выше, синхронизируются посредством первого фиксатора 30 и второго фиксатора 40 соответственно, как они должны быть поданы на контактные точки S1 и S2 средства выборки SWI. Функционирование средства выборки SWI управляется сигналами, образованными в схеме вычисления CDS 70, но образуется "безразличное" состояние в случае первоначального информационного слова, как описано выше, так что любой из сигналов, образованных в первом и втором фиксаторах 30 и 40, может быть выбран. Здесь средство выборки SWI управляется для выборки отрицательного кодового слова, как показано на фиг. 3. Соответственно точка опорного контакта .0 средства выборки SWI переключается на первую контактную точку S1. Таким образом, сигналы, образованные в первом фиксаторе 30, образуются посредством третьего фиксатора 50 и параллельно-последовательного преобразователя 60.

Параллельно-последовательный преобразователь 60 преобразует параллельные данные в последовательные данные, и сигналы, образованные в параллельно-последовательном преобразователе 60, записываются посредством усилителя записи (не показано) и одновременно подаются обратно на схему вычисления CDS 70.

Схема вычисления CDS 70 вычисляет величины постоянного тока последовательных данных, поданных на схему, и когда поданные последовательные данные составляют "00000", как показано на фиг. 3, соответствующие величины CDS вычисляются как величина десятичного знака -5. Соответственно текущие производимые величины CDS кодового слова включаются в отрицательную величину, так что управляющий сигнал подается на средство выборки SWI, чтобы выбрать кодовое слово следующего информационного слова как положительное кодовое слово. Как следствие, положительное кодовое слово "11110" двух кодовых слов, соответствующих следующему информационному слову "00001", подается через второй фиксатор 40 и средство выборки SWI на третий фиксатор 50.

Кодовое слово, поданное на третий фиксатор 50, преобразуется в формат последовательных данных таким же образом, как описано выше, чтобы подать на усилитель записи (не показан) и схему вычисления CDS 70, так что вышеназванные операции выполняются в них многократно. Соответственно кодовое слово, соответствующее информационному слову, выбирается, и как результат, величина DSV приближается к "нулю", как показано на фиг. 3E. Иначе говоря, оно управляется, чтобы выбрать настоящее кодовое слово, соответствующее величине CDS предшествующего кодового слова.

На фиг. 5 показана схема вычисления CDS 70 согласно настоящему изобретению, функционирование которой протекает следующим образом.

Прежде всего генератор импульса нагрузки управляет нагрузкой параллельно-последовательного преобразователя 60, когда параллельное слово символа преобразуется в последовательное слово символа, и также управляет счетчиком 721 в отношении загрузки опорных сигналов, образованных в генераторе опорных сигналов 722.

Счетное средство 72 отсчитывает в прямом и обратном направлениях кодовое слово, посланное как последовательные данные от параллельно-последовательного преобразователя 60 через реверсивный счетчик 721 по принципу вычисления величин CDS как описано со ссылкой на фиг. 1. Опорная величина, определяющая пуск реверсивного счетчика, соответствует величине, образованной в генераторе опорных сигналов 722. В результате счетчик 721 загружает опорную величину перед пуском реверсивного счетчика в зависимости от импульса нагрузки, образованного в генераторе импульса нагрузки 71. Величина CDS, вычисляемая на каждое одно кодовое слово, подается на четвертый фиксатор 73, который временно запоминает вычисленную величину CDS и затем подает на выход загруженную величину.

Выходной сигнал четвертого фиксатора 73 подается на пятый фиксатор 75 и детектор 74. Когда выход величины от четвертого фиксатора 73 идентичен величине выхода опорного сигнала от генератора опорных сигналов 722, это означает, что величины DSV кодового слова идентичны "нулю" (т.е. количество двоичных "1" количество двоичных "0" в кодовом слове является одинаковым). Соответственно величина CDS кодового слова перед предшествующим кодовым словом должна быть сохранена. Для этой цели в случае, когда величина CDS равна "нулю" в детекторе 74, синхросигнал пятого фиксатора 75 не управляется в отношении функционирования, так что выходной сигнал пятого фиксатора 75 является постоянным. Выходной сигнал пятого фиксатора 75 подается на компаратор 76.

Компаратор 76 сравнивает выходной сигнал пятого фиксатора 75 с величиной опорного сигнала, идентичной величине опорного сигнала, используемого в счетчике 721. Если выходной сигнал пятого фиксатора 75 больше, чем величина опорного сигнала, CDS кодового слова определяется как положительная, в противном случае CDS определяется как отрицательная величина. Соответственно, если величина CDS предшествующего кодового слова положительная, переключение в средстве выборки SWI управляется таким образом, что выбирается отрицательное кодовое слово в качестве текущего кодового слова, и если величина CDS предшествующего кодового слова отрицательная, переключение его управляется таким образом, что выбирается положительное кодовое слово в качестве текущего кодового слова. Средство выборки SWI переключается на первую контактную точку S1, когда выбрано отрицательное кодовое слово, и переключается на вторую контактную точку S2, когда выбирается положительное кодовое слово.

На фиг. 6 подробно показана схема варианта реализации схемы согласно настоящему изобретению, как показано на фиг. 5 и вариант реализации поясняется со ссылкой на фиг. 7А -7К. Здесь посылаемое информационное слово образовано в формате восьми бит, и преобразованное кодовое слово образовано в формате 14 бит.

Прежде всего генератор импульсов нагрузки производит величины для отсчета с многократным повторением из сигналов основной синхронизации с 2 по F, как показано на фиг. 7А, которые подаются на счетчик через выходные выводы QA, QB, QC и QD. Здесь сигнал от выходного вывода QD подается на входной вывод DD - триггера 712. Сигнал выходного вывода QD образуется, как показано на фиг. 7B.

D-триггер 712 образует высокий логический сигнал на своем выходном выводе Q/, так как сигнал, поданный на входной вывод D, является низким логическим сигналом, пока не будет произведен пятый основной синхросигнал, и затем, так как логика сигнала, поданного на входной вывод D, преобразуется на высокую логику в соответствии с отсчетом шестого синхросигнала. Соответственно, когда импульс седьмого основного синхросигнала CLK1 образован, логика выходного сигнала от выходного вывода Q/ преобразуется в низкую логику. Таким образом, сигнал, образованный на выходном выводе Q/D-триггера 712, является сигналом, в котором сигнал, образованный в счетчике 711, задерживается циклом синхронизации основного синхросигнала CLK1, как показано на фиг. 7C.

Логическое устройство 713 выполняет операцию И-НЕ выходного сигнала Q/ (фиг. 7C) в D-триггере 712 и выходных сигналов QD (фиг. 7B) в счетчике 711. Сигнал, образованный логическим устройством 713, представлен как показано на фиг. 7D. На фиг. 7D импульс нагрузки произведен как интервал синхросигнала CLK1 на каждый срез импульса выходного сигнала QD счетчика 711. Импульс нагрузки подается на параллельно-последовательный преобразователь 60, чтобы загрузить кодовое слово из четырнадцати бит, поданного в течение низкого периода, и затем, чтобы сдвигать кодовое слово его, пока не будет образовано тринадцать синхроимпульсов, и затем, когда параллельные данные поданы на параллельно-последовательный преобразователь 60, импульс нагрузки выполняет загрузку соответственно.

Последовательно преобразованные данные подаются на реверсивный управляющий вывод счетчика 723, и счетчик 723 загружает заданную опорную величину в срезе импульса, произведенного в генераторе импульса нагрузки 71, и также отсчитывает в прямом и обратном направлениях загруженную величину в соответствии с условием поданных последовательных данных. Здесь заданные величины подаются на выводы A, B, C и D равные величине десятичной 7.

Затем кодовое слово из 14 бит, произведенное в параллельно-последовательном преобразователе 60, генерируется в том, же периоде, как показано на фиг. 7E, и когда величина генерированного кодового слова является такой же, как показано на фиг. 7E, счетчик 723 отсчитывает в прямом и обратном направлениях величину последовательно-параллельных данных, поданных на реверсивный управляющий вывод, в отношении загруженной величины десятичной 7. Здесь в противоположность вышеприведенному описанию, когда величина кодового слова равна "0", отсчет производится для дополнительной операции "0", и когда равна "1", отсчет производится в отношении операции вычитания "1". Соответственно когда поданные последовательные данные есть "0111110000000", как показано на фиг. 7F, результирующая величина в счетчике 723 будет такой же, как показано на фиг. 7G.

Схема фиксатора 731 запоминает временно результирующую величину конечного отсчета десятичной 9, которая синхронизируется поделенным на 14 синхросигналом CLK2, образованного в генераторе импульса нагрузки 71, и производится, как показано на фиг. 7G, и посылает загруженную величину на схему фиксатора 751 и детектор 74.

Детектор 74 управляет сигналом, посланным от схемы фиксатора 731, чтобы не передавать на схему фиксатора 751, когда сигнал от схемы фиксатора 731 идентичен "нулю". Иначе говоря, логическое устройство, выполняющее операцию И-НЕ сигналов QA, QB и QC в схеме фиксатора 731, образует низкий логический сигнал, если все вышеназванные сигналы от схемы фиксатора 731 являются высокими, и в противном случае логическое устройство 741 производит высокий логический сигнал. Когда все вышеназванные выходные сигналы в схеме фиксатора 731 являются высокими, выходная величина равна десятичной 7. Однако, как показано на фиг. 7H, так как величина, отсчитанная для предшествующего кодового слова, является десятичной 9, логическое устройство 741 производит высокий логический сигнал. Соответственно, логическое устройство 741, принимающее выходной сигнал логического устройства 741 и поделенный на 14 синхросигнал CLK2 с тем, чтобы выполнять операцию И, производит поделенный на 14 синхросигнал CLK2 как таковой.

Соответственно схема фиксатора 751 сохраняет выходной сигнал от схемы фиксатора 731, и также посылает удерживаемый сигнал на входные выводы A3, A2, A1 и A0 компаратора 761. Текущие величины, поданные на A3, A2, A1 и A0, равны десятичной 9. Компаратор 751 имеет ту же опорную величину, как в счетчике 723 на его входном выводе B, так что величина, поданная на входной вывод A, больше, чем поданная на входной вывод B. Как следствие следует, что величина CDS предшествующего кодового слова больше, чем "0", и это означает, что количество двоичных "0" больше, чем количество двоичных "1".

Таким образом, управляющий сигнал подается на средство выборки SWI для того, чтобы выбрать отрицательное кодовое слово, генерированное в первой таблице преобразований 10 как кодовое слово, соответствующее текущему информационному слову. Первая контактная точка в средстве выборки SWI устанавливается как высокий логический вывод, так что высокий сигнал подается от схемы вычисления CDS 70 для управления операцией, как описано выше и показано на фиг. 7K.

С другой стороны, когда величина, отсчитанная в счетчике 723 является десятичной 7 идентичной второй отсчитанной результирующей величине на фиг. 7H, устройство И-НЕ 741 в детекторе 74 генерирует низкий логический сигнал, так что устройство И 742 отсекает синхросигнал, поданный на другие входные выводы, и как результат, схема фиксатора 751 сохраняет величину кодового слова перед предшествующим кодовым словом. Соответственно величина подается на компаратор как таковая, и средство выборки SWI управляется в соответствии с вышеописанным заключением.

Однако отсчитанная величина в счетчике 723 является десятичной 3, как в третьем кодовом слове, выходной сигнал от устройства И-НЕ 741 в детекторе 74 генерирует высокий логический сигнал, так что поделенный на 14 синхросигнал CLK2 генерируется как таковой. Соответственно схема фиксатора 751 сохраняет выходной сигнал от схемы фиксатора 731, и также посылает удерживаемый сигнал на компаратор 761. Компаратор 761 определяет, что величина CDS предшествующего кодового слова меньше "нуля", так как величина сигнала, поданного на входной вывод A, идентична опорной величине, поданной на входной вывод B, с тем, чтобы управлять операцией средства выборки SWI путем образования низкого логического сигнала, как показано на фиг. 7K, чтобы выбрать положительное кодовое слово в качестве текущего кодового слова.

Иначе говоря, в варианте реализации, показанном на фиг. 6, в случае, когда количество бит, составляющих кодовое слово, возрастает, все могут использоваться, как они есть, за исключением, что только один счетчик может быть еще добавлен.

На фиг. 8 показана подробная схема другого варианта реализации схемы вычисления CDS 70 согласно настоящему изобретению, как показано на фиг. 5, и этот вариант реализации поясняется со ссылкой на фиг. 9A - 9G.

На фиг. 8 детектор 74, схемы фиксаторов 731 и 751, показанные на фиг. 6, могут применяться, как они есть. Соответственно более подробное пояснение их может быть опущено, и будут пояснены только части/участки, отличающиеся от фиг. 6.

Счетное средство 72 передает основной синхросигнал CLK1, как показано на фиг. 9C в интервале, когда последовательные данные, образованные в параллельно-последовательном преобразователе 60 логическим устройством 725, подаются как высокий логический сигнал, как на фиг. 9B. Переданный сигнал подается на счетчик 724. Счетчик 724 загружает опорный сигнал с помощью сигнала импульса нагрузки как в счетчике 723, показанном на фиг. 6. Однако опорная величина, требуемая для загрузки, равна величине "нуль", так как входные выводы A, B, C и D соединены с землей. Счетчик 724, загруженный как "нуль", отсчитывает отсчетную величину, поданную на вывод синхросигнала, как показано на фиг. 9D.

Соответственно, когда первая отсчитанная величина равна десятичной 5, как показано на фиг. 9D, схема фиксатора 731 производит величину. Поэтому детектор 74 и схема 751 функционируют таким же образом, как описано выше, так что выходной сигнал подается на компаратор 76. Величина, образованная в схеме фиксатора 751, является десятичной 5, и тогда выходные сигналы на выходных выводах QA, QB, QP и QD являются "1010", так что логическое устройство 762 производит высокий логический сигнал, как показано на фиг. 9E. С другой стороны, логическое устройство 763 производит низкий логический сигнал, как показано на фиг. 9F. Поэтому логическое устройство 764 управляет средством выборки SWI для переключения на вторую контактную точку, так как сигнал, образованный логическим устройством 762, является высоким, и это означает, что в ранее произведенном кодовом слове количество двоичных "0" больше, чем двоичных "1", так что логическое устройство 764 передает положительное кодовое слово в качестве текущего кодового слова на третий фиксатор 50.

Однако когда отсчитанная результирующая величина образована как в третьей форме волны на фиг. 9D, каждая величина QA, QB, QC и QD, образованная в схеме фиксатора 751, является "1110". Соответственно логическое устройство 762 производит низкий логический сигнал, логическое устройство 763 производит низкий логический сигнал, и логическое устройство 764 производит низкий логический сигнал, так что в противоположность вышеописанному средство выборки SWI управляется для выбора отрицательного кодового слова. Иначе говоря, в варианте реализации, показанном на фиг. 8, есть преимущество в том, что даже если количество смещений, образующих кодовое слово, возрастает, функционирование возможно без добавления компонентов.

Как описано выше, схема вычисления величин постоянного тока согласно настоящему изобретению имеет преимущество в том, что вычисление CDS происходит легко, и элементы, составляющие схему, не изменяются в соответствии с увеличением и уменьшением количества бит, так как количество бит кодового слова, используемых для вычисления величины CDS, является небольшим, когда кодовое слово, соответствующее информационному слову, поданному способом кодирования канала на цифровую систему записи и воспроизведения, преобразуется.

Хотя настоящее изобретение описано и изложено со ссылкой на два предпочитаемых варианта реализации, но должно быть понятно, что специалист в области техники, к которой относится настоящее изобретение, может разнообразно модифицировать состав и монтаж изобретения без отклонения от идеи этого описания и объема формулы изобретения.

Изобретение относится к технике магнитной записи и воспроизведения. Два запоминающих средства преобразуют информационное слово во множества кодовых слов и запоминают слово, величина постоянного тока которого является положительной и отрицательной. Сигнал, выбранный от этих запоминающих средств средством выборки, с помощью средства преобразования параллельного кода в последовательный переводится в формат. Схема вычисления определяет ток текущего кодового слова по сигналу от средства преобразования и управляет средством выборки для выбора слова из множества. Генератор принимает основной синхросигнал и генерирует второй синхросигнал и импульс нагрузки с частотой основного синхросигнала, поделенной на заданную величину. Счетчик загружает опорную величину и отсчитывает в прямом/обратном направлении последовательные данные. Детектор определяет равенство или неравенство отсчитанной и опорной величин. Третье запоминающее средство сохраняет предшествующую входную величину при равенстве и загружает отсчитанную величину при неравенстве. Компаратор сравнивает сигнал третьего запоминающего средства с опорным и управляет средством выборки. Предложенная схема вычисления обеспечивает упрощенные измерения и некритична к количеству бит. 4 з.п. ф-лы, 9 ил.

| US 5270714 A, 14.12.93 | |||

| Устройство для цифровой магнитной записи-воспроизведения | 1988 |

|

SU1509991A1 |

| Устройство для цифровой магнитной записи-воспроизведения | 1985 |

|

SU1304065A1 |

Авторы

Даты

2000-02-10—Публикация

1993-08-30—Подача