Изобретение относится к устройствам передачи дискретной информации и может быть использовано, например, в вычислительных системах, в устройствах высокоскоростного обмена данными.

Известно устройство, содержащее элементы И с первого по четвертый, первый и второй инверторы. Недостатком является недостаточная скорость передачи дискретной информации и отсутствие возможности выборочного обновления данных при быстрой передаче информационных сигналов [1].

Наиболее близким к рассматриваемому решению является устройство, содержащее элементы И с первого по шестой, первый и второй инверторы, триггеры с первого по третий, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три блока задержки, счетчик, элемент ИЛИ-НЕ, блок оперативной памяти. Недостатком является отсутствие возможности выборочного обновления передаваемых информационных сигналов [2].

Технической задачей, решаемой изобретением, является расширение области применения за счет обеспечения возможности выборочного обновления данных при быстрой передаче информационных сигналов.

Поставленная задача решается тем, что в известное устройство, содержащее элементы И с первого по шестой, первый и второй инверторы, триггеры с первого по третий, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три блока задержки, счетчик, элемент ИЛИ-НЕ, блок оперативной памяти, информационный вход которого подключен к выходу первого триггера, два входа которого объединены попарно с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и пятого элемента И и подключены к выходам первого и второго инверторов, вход первого из которых подключен в выходу второго элемента И, первый вход которого соединен с выходом первого элемента И, второй вход которого соединен со вторым входом второго элемента И, а первый вход подключен к первому входу третьего элемента И, выход которого присоединен к первому входу четвертого элемента И, а второй вход соединен со вторым входом четвертого элемента И, выход которого подключен ко входу второго инвертора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом элемента ИЛИ-НЕ непосредственно, а со вторым, третьим и четвертым его входами - через соответствующие первый, второй и третий блоки задержки, выход элемента ИЛИ-НЕ подключен к объединенным синхронизирующим входам второго и третьего триггеров, информационные входы которых объединены и подключены к нулевой шине, выход второго триггера подключен к входу "Запись/Чтение" блока оперативной памяти, адресный вход которого соединен с выходом счетчика, синхронизирующий вход которого подключен к выходу пятого элемента И, третий вход которого объединен с установочным входом третьего триггера, выход которого подключен ко второму входу шестого элемента И, выход которого подключен к установочному входу счетчика, а первый вход объединен с установочным входом второго триггера, введены элемент ЭКВИВАЛЕНТНОСТЬ, четвертый триггер и седьмой элемент И, выход которого подключен к синхронизирующему входу блока оперативной памяти, второй вход объединен с установочным входом третьего триггера, а первый вход подключен к выходу четвертого триггера, первый и второй входы которого присоединены соответственно к выходам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ЭКВИВАЛЕНТНОСТЬ, первый и второй входы которого подключены соответственно к выходам первого и второго инверторов.

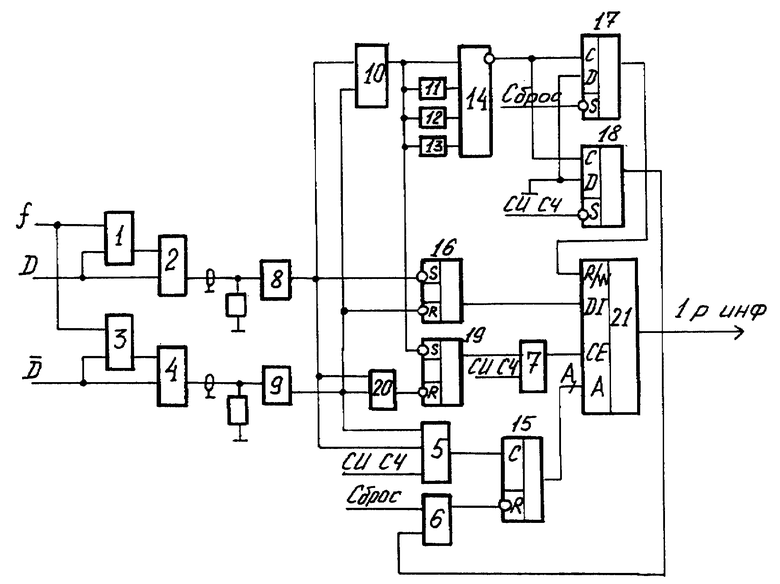

На чертеже представлена структурная электрическая схема устройства передачи цифровой информации.

Устройство содержит элементы И с первого 1 по седьмой 7, первый 8 и второй 9 инверторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, первый 11, второй 12 и третий 13 блоки задержки, элемент ИЛИ-НЕ 14, счетчик 15, триггеры с первого 16 по четвертый 19, элемент ЭКВИВАЛЕНТНОСТЬ 20, блок 21 оперативной памяти.

Устройство работает следующим образом. Первый 1, второй 2, третий 3 и четвертый 4 элементы И представляют собой кодер, после которого наличие импульса на выходе первого инвертора 8 означает единицу информации, наличие импульса на выходе второго инвертора 9 - нулевую информацию в канале, одновременное наличие импульсов на выходах этих инверторов - запрет обновления ранее поступившей информации по установленному адресу в блоке 21 оперативной памяти.

При записи "1" или "0" информация в виде импульсов с выходов первого 8 или второго 9 инверторов поступает на соответствующий установочный вход первого триггера 16, который преобразует ее в униполярную информацию и передает на запись в блок 21. На выходе элемента 20 при этом появляется сигнал, благодаря которому с выхода четвертого триггера 19 на синхронизирующий вход блока 21 подается импульс выборки этого блока. Пятый элемент И 5 формирует импульсы пересчета адресов блока 21 счетчиком 15. Переключение адреса в счетчике 15 происходит задним фронтом импульса. Тем самым обеспечивается предустановка адреса и задержка его переключения относительно этого сигнала.

Игнорирование записи в блок 21 по установленному счетчиком 15 адресу происходит при одновременном наличии импульсов на выходах первого 8 и второго 9 инверторов, что приводит к установке четвертого триггера 19 в единичное состояние. Таким образом, осуществляется блокировка выборки блока 21 и содержимое этого блока по установленному адресу не меняется. По заднему фронту импульсов осуществляется переключение адреса в счетчике.

Конец передачи информации по каналу фиксируется появлением сигнала на инверсном выходе третьего триггера 18, который вместе со вторым триггером 17, элементом ИЛИ-НЕ 14, блоками 11-13 и элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 10 составляет блок весового суммирования. При этом второй триггер 17 переключается в состояние "1" по инверсному выходу (положение "Чтение" для блока 21). Величины задержек первого 11, второго 12 и третьего 13 блоков составляют соответственно 1/4, 1/2 и 3/4 длительности такта частоты синхронизации устройства. Это позволяет выделить моменты начала и конца передачи информации. Таким образом, вся информация по каналу последовательно записывается в блок 21.

После окончания приема информации на выходе третьего триггера 18 появляется сигнал логической "1", после приема которого принимающий процессор начинает выдавать тактовую частоту СИ и СЧ, по которой импульсы через пятый элемент И 5 и седьмой элемент И 7 поступают на синхронизирующие входы соответственно счетчика 15 и блока 21. По окончании считывания информации из блока 21 принимающим процессором выдается импульс "Сброс" (конец считывания), который устанавливает второй триггер 17 и счетчик 15 через шестой элемент И 6 в исходное состояние. Устройство готово к передаче новой информации.

Используемая литература

1. Ларионов А.М. и др. Вычислительные комплексы, системы и сети. - Л.: Энергоатомиздат. 1987, 288 с.

2. А. с. N1700755, МКИ H 04 B 1/66. Устройство передачи цифровой информации /В.М. Константиновский, А.А. Мурафетов, В.И. Победин и И.М. Рыбаков. - Опубл. 23.12.91. Бюл. N 47 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| УСТРОЙСТВО СЕЛЕКЦИИ САМОНАВОДЯЩИХСЯ ПРОТИВОРАДИОЛОКАЦИОННЫХ РАКЕТ | 1998 |

|

RU2155353C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ИНВЕРСНЫМ СИНТЕЗИРОВАНИЕМ АПЕРТУРЫ И МНОГОЧАСТОТНЫМ ЗОНДИРУЮЩИМ СИГНАЛОМ | 1999 |

|

RU2152626C1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ВОЗДУШНЫХ ЦЕЛЕЙ ДВУХЧАСТОТНЫМ СПОСОБОМ | 1999 |

|

RU2144681C1 |

| МНОГОЧАСТОТНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ИНВЕРСНЫМ СИНТЕЗИРОВАНИЕМ АПЕРТУРЫ И ДВУХУРОВНЕВЫМ РАСПОЗНАВАНИЕМ ЦЕЛЕЙ | 2007 |

|

RU2358288C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПОПЕРЕЧНЫХ РАЗМЕРОВ РАДИОЛОКАЦИОННЫХ ОБЪЕКТОВ РЛС В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 1999 |

|

RU2150714C1 |

| ДАТЧИК ДАВЛЕНИЯ | 2000 |

|

RU2221228C2 |

| УРОВНЕМЕР | 1998 |

|

RU2161297C2 |

| СПОСОБ ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПРОТИВОРАДИОЛОКАЦИОННОЙ РАКЕТЫ НА ОСНОВЕ ИСПОЛЬЗОВАНИЯ ПЕРЕИЗЛУЧАЮЩЕГО ЭКРАНА | 2001 |

|

RU2210089C2 |

| СПОСОБ ЗАЩИТЫ РЛС ОТ ПРОТИВОРАДИОЛОКАЦИОННЫХ РАКЕТ | 1999 |

|

RU2153684C1 |

Изобретение относится к устройствам передачи дискретной информации и может быть использовано, например, в вычислительных системах, в устройствах высокоскоростного обмена данными. Технической задачей является расширение области применения за счет обеспечения возможности выборочного обновления данных при быстрой передаче информационных сигналов. Устройство содержит элементы И с первого 1 по седьмой 7, первый 8 и второй 9 инверторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, первый 11, второй 12 и третий 13 блоки задержки, элемент ИЛИ-НЕ 14, счетчик 15, триггеры с первого 16 по четвертый 19, элемент ЭКВИВАЛЕНТНОСТЬ 20, блок 21 оперативной памяти. 1 ил.

Устройство передачи цифровой информации, содержащее элементы И с первого по шестой, первый и второй инверторы, триггеры с первого по третий, элемент Исключающее ИЛИ, три блока задержки, счетчик, элемент ИЛИ - НЕ, блок оперативной памяти, информационный вход которого подключен к выходу первого триггера, два входа которого объединены попарно с входами элемента Исключающее ИЛИ и пятого элемента И и подключены к выходам первого и второго инверторов, вход первого из которых подключен к выходу второго элемента И, первый вход которого соединен с выходом первого элемента И, второй вход которого соединен со вторым входом второго элемента И, а первый вход подключен к первому входу третьего элемента И, выход которого присоединен к первому входу четвертого элемента И, а второй вход соединен со вторым входом четвертого элемента И, выход которого подключен к входу второго инвертора, выход элемента Исключающее ИЛИ соединен с первым входом элемента ИЛИ - НЕ непосредственно, а со вторым, третьим и четвертым его входами через соответствующие первый, второй и третий блоки задержки, выход элемента ИЛИ - НЕ подключен к объединенным синхронизирующим входам второго и третьего триггеров, информационные входы которых объединены и подключены к нулевой шине, выход второго триггера подключен к входу Запись/Чтение блока оперативной памяти, адресный вход которого соединен с выходом счетчика, синхронизирующий вход которого подключен к выходу пятого элемента И, третий вход которого объединен с установочным входом третьего триггера, выход которого подключен ко второму входу шестого элемента И, выход которого подключен к установочному входу счетчика, а первый вход объединен с установочным входом второго триггера, отличающееся тем, что введены элемент Эквивалентность, четвертый триггер и седьмой элемент И, выход которого подключен к синхронизирующему входу блока оперативной памяти, второй вход объединен с установочным входом третьего триггера, а первый вход подключен к выходу четвертого триггера, первый и второй входы которого присоединены соответственно к выходам элемента Исключающее ИЛИ и элемента Эквивалентность, первый и второй входы которого подключены соответственно к выходам первого и второго инверторов.

| Устройство передачи цифровой информации | 1989 |

|

SU1700755A1 |

| ЛАРИОНОВ А.М | |||

| и др | |||

| Вычислительные комплексы, системы и сети | |||

| - Л.: Энергоатомиздат, 1987, с | |||

| ДВОЙНОЙ ГАЕЧНЫЙ КЛЮЧ | 1920 |

|

SU288A1 |

| GB 1424525, 11.02.1976 | |||

| Стенд для испытания изделий на удар | 1983 |

|

SU1249364A1 |

| Способ производства газа и смолы из измельченного топлива | 1945 |

|

SU85820A1 |

Авторы

Даты

2000-06-10—Публикация

1998-12-07—Подача