Изобретение относится к области радиотехники и может быть использовано в системах связи, функционирующих в условиях неопределенных помех.

Известны радиолинии, использующие для повышения помехоустойчивости двухпозиционные фазоманипулированные шумоподобные сигналы (ФМ ШПС) с постоянной амплитудой и расширенным частотным спектром (см. АС СССР N 489254, кл. H 04 27/18 от 1973 г.; АС СССР N 509194, кл. H 04 В 9/00 от 1974 г.; АС СССР N 563730, кл. H 04 В 7/00 от 1976 г.; патент США N 3665472, кл. H 04 В 1/38 от 1972 г. ). Однако в условиях воздействия наихудших помех с неизвестной структурой и ограниченной средней мощностью (например, при пульсациях уровня мощности помех) помехоустойчивость радиолиний с ФМ ШПС существенно снижается.

Известны также радиолинии, использующие амплитудно-фазоманипулированные сигналы (АФМС) с изменяющейся амплитудой и фазой (см. заявку Великобритании N 1356179, кл. H 04 27/00 от 1974; заявку ФРГ N 2153376, кл. H 04 27/18 от 1976 г. ; заявку Японии N 55-24826, кл. H 04 27/00 от 1976 г.; заявку ФРГ N 3322954, кл. H 04 27/00 от 1985 г.; заявку ФРГ N 3243373, кл. H 04 27/00 от 1985 г.). Однако используемые в данных радиолиниях правила переключения фаз и амплитуд не рассчитаны на обеспечение помехоустойчивости в условиях воздействия наихудших помех с неизвестной структурой и ограниченной средней мощностью.

Наиболее близкой по своей сущности к заявляемому устройству является известная радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами (АФМ ШПС), описанная в АС СССР N 1635275 A1, кл. H 04 L 27/18 от 1991 г. /1/.

Ближайший аналог (прототип) содержит на передающей стороне источник информации, фазовый модулятор, модулятор, генератор несущей частоты, усилитель, усилитель мощности, антенное устройство, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь, причем выход источника информации подключен к первому входу фазового модулятора, выход которого соединен с первым входом модулятора, выход генератора несущей частоты подключен к второму входу модулятора, выход которого подключен к информационному входу усилителя, выход которого подключен к входу усилителя мощности, выход которого подключен к входу антенного устройства, первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига, а его второй выход - к тактовому входу регистра хранения, выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов регистра сдвига, где N ≥ 2, подключены к соответствующим (N+1) информационным входам регистра хранения, N информационных выходов регистра хранения подключены к соответствующим N информационным входам дешифратора, а дополнительный (N+1) выход регистра хранения подключен к второму входу фазового модулятора, N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя, а на приемной стороне прототип содержит антенное устройство, смеситель, усилитель промежуточной частоты, перемножитель, усилитель, интегратор, решающий блок, гетеродин, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь и приемник информации, причем выход антенного устройства подключен к первому входу смесителя, выход смесителя подключен к входу усилителя промежуточной частоты, выход которого подключен к информационному входу перемножителя, выход которого подключен к информационному входу усилителя, выход которого подключен к входу интегратора, выход которого подключен к входу решающего устройства и к входу блока синхронизации, первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига, второй выход блока синхронизации подключен к тактовому входу регистра хранения, третий выход блока синхронизации подключен к входу гетеродина, выход которого подключен к второму входу смесителя, выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов которого подключены к соответствующим (N+1) информационным входам регистра хранения, N информационных выходов которого подключены к соответствующим N информационным входам дешифратора, а дополнительный (N+1) выход регистра хранения подключен к управляющему входу перемножителя, N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя.

За счет дополнительного псевдослучайного изменения амплитуды субэлементов сигнала, манипулированного по фазе псевдослучайным сигналом, расширяющим спектр, указанная радиолиния - прототип по сравнению с радиолиниями - аналогами, использующими ФМ ШПС с фиксированной амплитудой субэлементов, обеспечивает повышенную устойчивость к прерывистым помехам с ограниченной средней мощностью, воздействующим на отдельные субэлементы ШПС. Теоретически энергетический выигрыш в такой радиолинии при заданных требованиях к качеству связи может достигать более 3 дБ /2/.

Указанный выигрыш обеспечивается при условии передачи однородной информации, качество приема которой может быть оценено по средней вероятности ошибки любого из передаваемых разрядов.

Однако устройство-прототип имеет ряд недостатков. Во-первых, устройство-прототип не обеспечивает высокого качества приема при передаче неоднородной информации в условиях неопределенных помех с ограниченной средней мощностью. При этом возможна концентрация энергии помех на отдельных разрядах информационного сигнала, которые более сильно, чем другие разряды, влияют на итоговое качество связи, оцениваемое по точности восстановления блоков информации, включающих много разрядов. В качестве подобных блоков информационных разрядов могут выступать пакеты данных с раздельно кодируемыми заголовками, циклы групповых сигналов с временным уплотнением оперативных и служебных каналов, оцифрованные отсчеты аналоговой информации и т.п. Во-вторых, реализуемый в устройстве алгоритм равномерного распределения энергетического ресурса является не рациональным в условиях однородных помех при одинаковой помехозащищенности отдельных разрядов и неоднородности структуры информационных блоков.

Целью изобретения является разработка радиолинии с АФМ ШПС, позволяющей повысить качество приема при передаче неоднородной информации и эффективность использования энергетического ресурса в условиях воздействия неопределенных помех с ограниченной средней мощностью.

Указанная цель достигается тем, что в известной радиолинии с АФМ ШПС, содержащей на передающей стороне источник информации, фазовый модулятор, модулятор, генератор несущей частоты, усилитель, усилитель мощности, антенное устройство, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь. Причем выход фазового модулятора соединен с первым входом модулятора. Выход генератора несущей частоты подключен к второму входу модулятора, выход которого подключен к информационному входу усилителя, выход которого подключен к входу усилителя мощности, выход которого подключен к входу антенного устройства. Первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига, а его второй выход - к тактовому входу регистра хранения. Выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов регистра сдвига, где N ≥ 2, подключены к соответствующим (N+1) информационным входам регистра хранения. N информационных выходов регистра хранения подключены к соответствующим N информационным входам дешифратора. Дополнительный (N+1) выход регистра хранения подключен к второму входу фазового модулятора. N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя. На приемной стороне радиолиния-прототип содержит: антенное устройство, смеситель, усилитель промежуточной частоты, перемножитель, усилитель, интегратор, решающий блок, гетеродин, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь и приемник информации. Причем выход антенного устройства подключен к первому входу смесителя. Выход смесителя подключен к входу усилителя промежуточной частоты, выход которого подключен к информационному входу перемножителя, выход которого подключен к информационному входу усилителя. Выход усилителя подключен к входу интегратора, выход которого подключен к входу решающего блока и к входу блока синхронизации. Первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига. Второй выход блока синхронизации подключен к тактовому входу регистра хранения. Третий выход блока синхронизации подключен к входу гетеродина, выход которого подключен к второму входу смесителя. Выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов которого подключены к соответствующим (N+1) информационным входам регистра хранения, N информационных выходов которого подключены к соответствующим N информационным входам дешифратора. Дополнительный (N+1) выход регистра хранения подключен к управляющему входу перемножителя. N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя.

Дополнительно введены на передающей стороне блок управления, блок перемежения, а на приемной стороне - блок управления и блок перемежения. При этом выход источника информации подключен к информационному входу блока перемежения. Выход блока перемежения подключен к первому входу фазового модулятора. Дополнительный (N+1) выход регистра хранения подключен к управляющему входу блока управления. Второй выход блока синхронизации подключен к тактовому входу блока управления. Первый и второй синхронизирующие выходы блока управления подключены к соответствующим синхронизирующим входам источника информации и блока перемежения, а третий синхронизирующий выход блока управления подключен к третьему синхронизирующему входу блока перемежения. К управляющих выходов блока управления, где K ≥ 2, подключены к соответствующим K управляющим входам блока перемежения. Выход блока перемежения подключен к входу фазового модулятора. На приемной стороне второй выход блока синхронизации подключен к тактовому входу блока управления. Дополнительный (N+1) выход регистра хранения подключен к управляющему входу блока управления. Первый, второй синхронизирующие выходы блока управления подключены к соответствующим синхронизирующим входам блока перемежения, а третий синхронизирующий выход блока управления подключен к третьему синхронизирующему входу блока перемежения и синхронизирующему входу решающего блока. K управляющих выходов блока управления подключены к соответствующим K управляющим входам блока перемежения. Выход решающего блока подключен к информационному входу блока перемежения, а выход блока перемежения подключен к входу приемника информации.

Благодаря новой совокупности признаков повышается качество приема передаваемой информации за счет выравнивания степени влияния искажений отдельных разрядов на итоговое качество приема k-разрядного информационного блока в целом при передаче отдельных разрядов i=1,..., k одинаковой мощностью Pc1,.. -Pck, но с различной длительностью T1...Tk. При этом ограничение суммарного энергетического ресурса радиолинии выражается в неизменности суммарной энергии излучаемых сигналов на длительности Т передачи k-разрядного информационного блока.

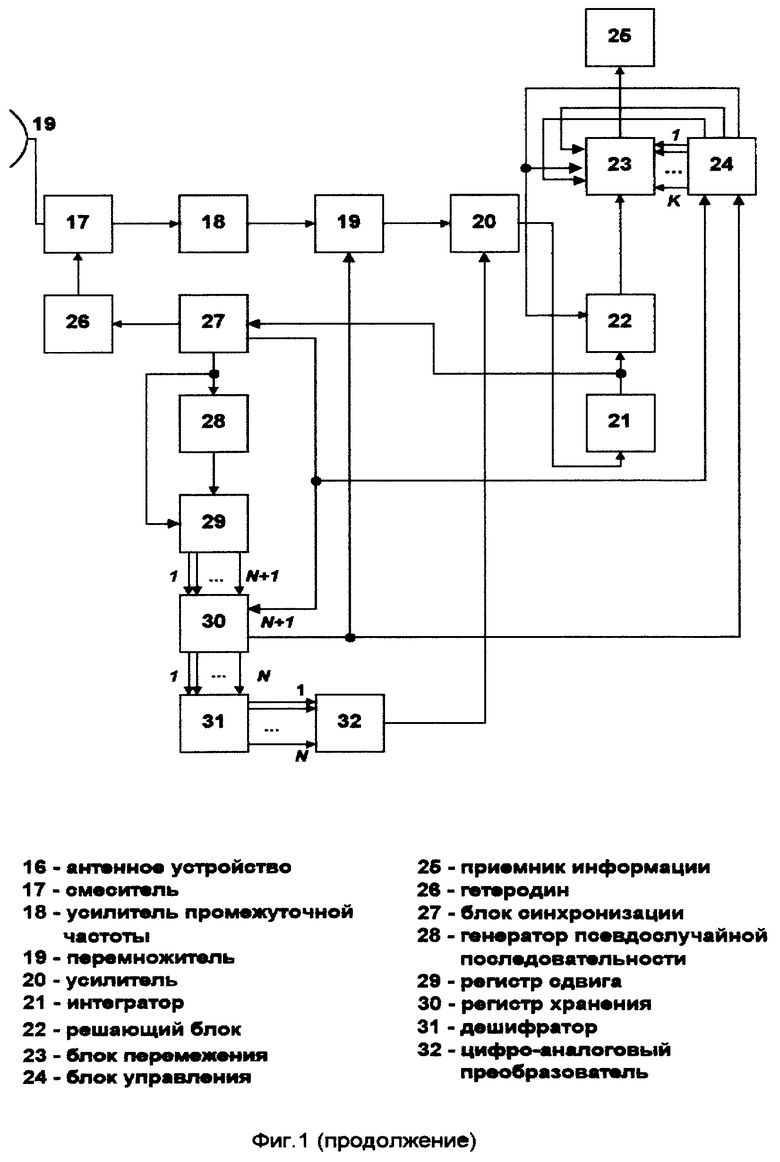

При заданной длительности Т передачи информационного блока из k двоичных разрядов неравномерное распределение энергетического ресурса ec=xEc, где x={ xi}k, xi ≥0, i=1,...,k, x1+...+xk=1, между отдельными разрядами можно реализовать, в общем случае, различными сочетаниями значений мощности Pci и длительности Ti, удовлетворяющих условию PciTi=xiEc. В заявляемом устройстве предлагается реализовать неравномерное распределение длительности Тi=x1T при фиксированной мощности Pc. На фиг.2 показан пример такого неравномерного распределения энергии сигналов Ec=PcT между k=4 информационными разрядами. Достоинством такой реализации является то, что при этом сохраняются амплитудные и спектральные характеристики излучаемых сигналов, а также упрощается реализация трактов управления, поскольку в данном случае не требуется вмешательство в работу радиотрактов.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявляемого технического решения, отсутствуют, что указывает на соответствие заявляемого устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижения указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

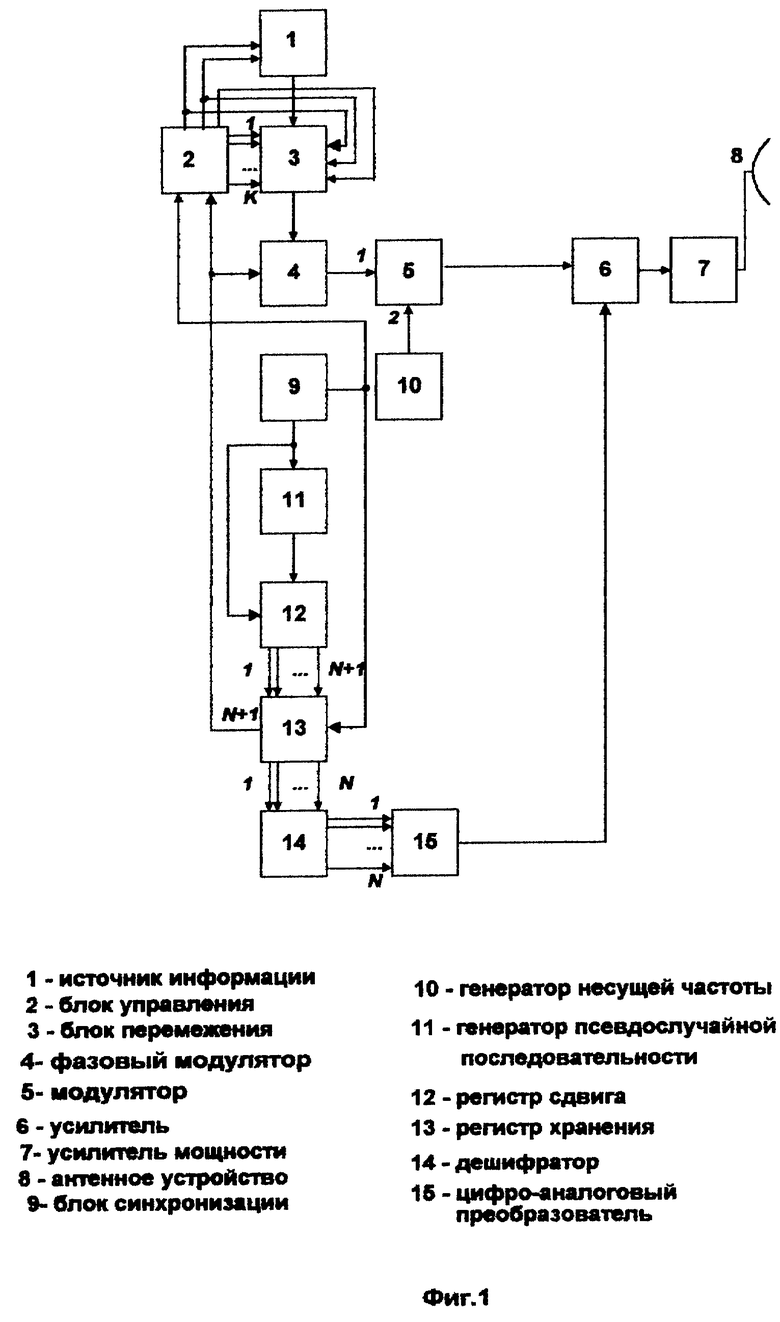

Заявляемое устройство поясняется чертежами, на которых показаны:

фиг. 1 - структурная схема радиолинии с амплитудно-фазоманипулированными шумоподобными сигналами;

фиг. 2 - пример неравномерного распределения энергии сигналов Ec=PcT между k=4 информационными разрядами;

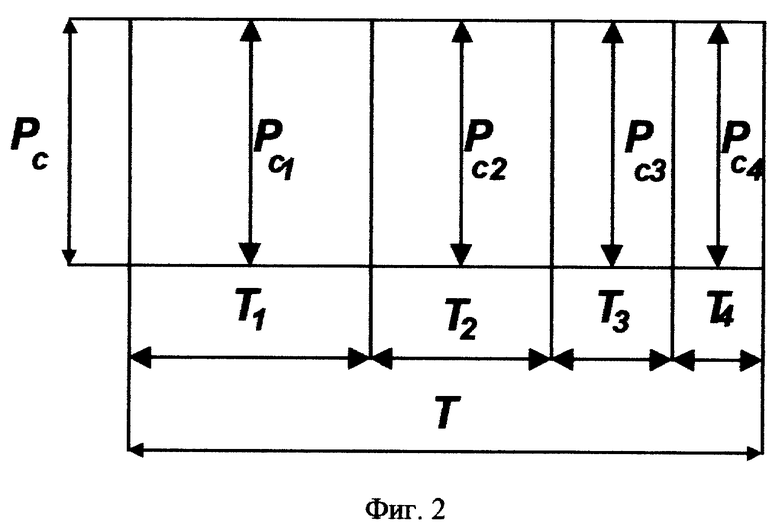

фиг. 3 - пример реализации источника информации;

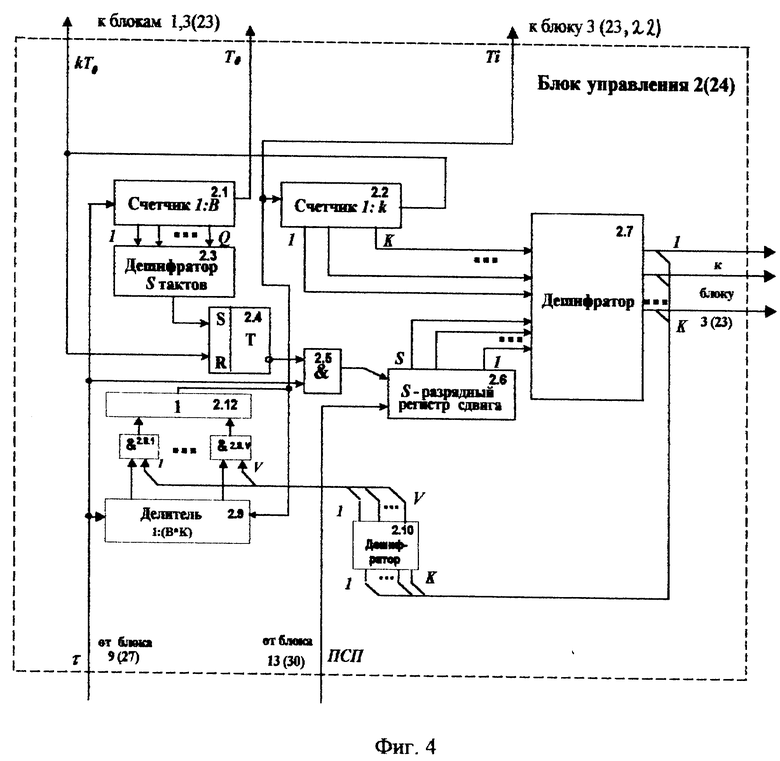

фиг. 4 - пример реализации блока управления;

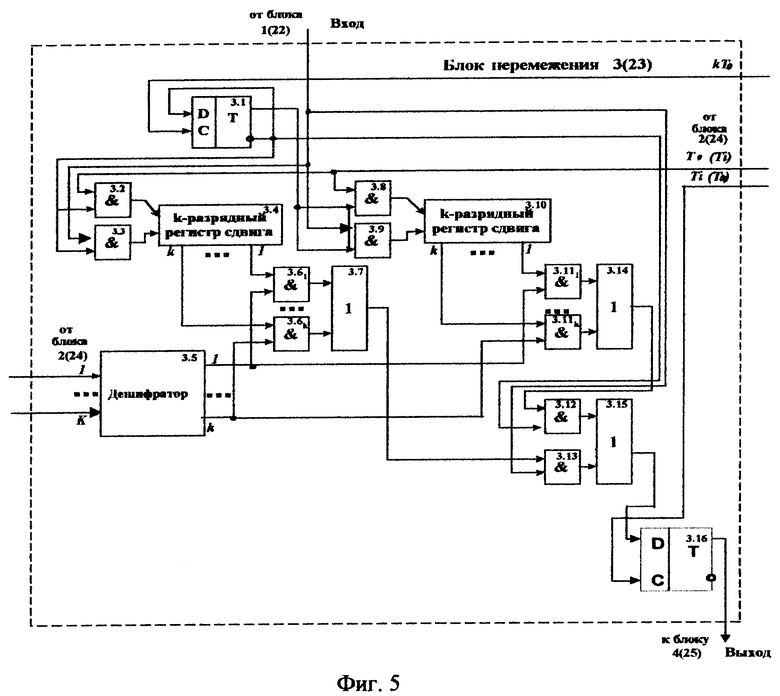

фиг. 5 - пример реализации блока перемежения;

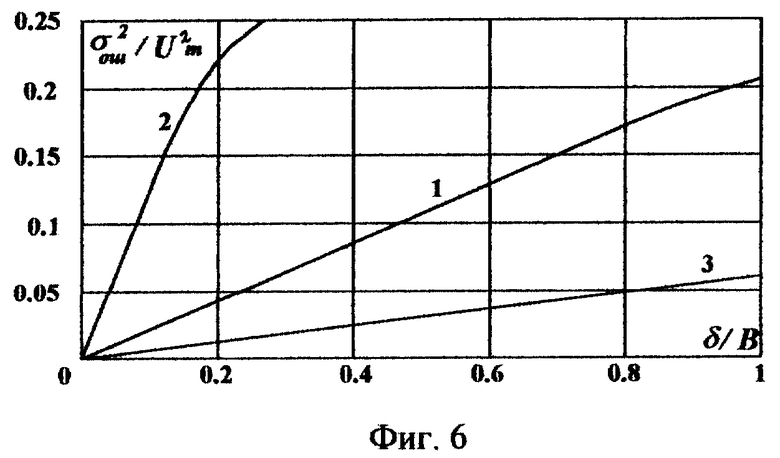

фиг. 6 - графики зависимости дисперсии ошибок от относительной мощности помех при различном распределении энергии сигналов и помех между разрядами оцифрованных аналоговых отсчетов.

Заявляемая радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами, представленная на фиг. 1, содержит на передающей стороне источник информации 1, блок управления 2, блок перемежения 3, фазовый модулятор 4, модулятор 5, усилитель 6, усилитель мощности 7, антенное устройство 8, блок синхронизации 9, генератор несущей частоты 10, генератор псевдослучайной последовательности 11, регистр сдвига 12, регистр хранения 13, дешифратор 14, цифроаналоговый преобразователь 15.

Выход источника информации 1 подключен к информационному входу блока перемежения 3. Выход блока перемежения 3 подключен к первому входу фазового модулятора 4. Выход фазового модулятора 4 соединен с первым входом модулятора 5. Дополнительный (n+1) выход регистра хранения 13 подключен к управляющему входу блока управления 2. Второй выход блока синхронизации 9 подключен к тактовому входу блока управления 2. Первый и второй синхронизирующие выходы блока управления 2 подключены к соответствующим синхронизирующим входам источника информации 1 и блока перемежения 3, а третий синхронизирующий выход блока управления 2 подключен к третьему управляющему входу блока перемежения 3. К управляющих выходов блока управления 2, где k ≥ 2, подключены к соответствующим k управляющим входам блока перемежения 3.

Выход генератора несущей частоты 10 подключен к второму входу модулятора 5, выход которого подключен к информационному входу усилителя 6, выход которого подключен к входу усилителя мощности 7, выход которого подключен к входу антенного устройства 8. Первый выход блока синхронизации 9 подключен к входу генератора псевдослучайной последовательности 11 и к тактовому входу регистра сдвига 12, а его второй выход - к тактовому входу регистра хранения 13. Выход генератора псевдослучайной последовательности 11 подключен к информационному входу регистра сдвига 12, (N+1) информационных выходов регистра сдвига 12, где N ≥ 2, подключены к соответствующим (N+1) информационным входам регистра хранения 13. N информационных выходов регистра хранения 13 подключены к соответствующим информационным входам дешифратора 14. Дополнительный (N+1) выход регистра хранения 13 подключен к второму входу фазового модулятора 4. N выходов дешифратора 14 подключены к соответствующим N входам цифроаналогового преобразователя 15, выход которого подключен к управляющему входу усилителя 6.

На приемной стороне радиолиния содержит: антенное устройство 16, смеситель 17, усилитель промежуточной частоты 18, перемножитель 19, усилитель 20, интегратор 21, решающий блок 22, блок перемежения 23, блок управления 24, приемник информации 25, гетеродин 26, блок синхронизации 27, генератор псевдослучайной последовательности 28, регистр сдвига 29, регистр хранения 30, дешифратор 31, цифроаналоговый преобразователь 32. Выход антенного устройства 16 подключен к первому входу смесителя 17. Выход смесителя 17 подключен к входу усилителя промежуточной частоты 18, выход которого подключен к информационному входу перемножителя 19. Выход перемножителя 19 подключен к информационному входу усилителя 20. Выход усилителя подключен к входу интегратора 21, выход которого подключен к входу решающего блока 22 и к входу блока синхронизации 27. Первый выход блока синхронизации 27 подключен к входу генератора псевдослучайной последовательности 28 и к тактовому входу регистра сдвига 29. Второй выход блока синхронизации 27 подключен к тактовому входу регистра хранения 30 и к тактовому входу блока управления 24. Третий выход блока синхронизации 27 подключен к входу гетеродина 26, выход которого подключен к второму входу смесителя 17. Дополнительный (N+1) выход регистра хранения 30 подключен к управляющему входу блока управления 24. Первый, второй синхронизирующие выходы блока управления 24 подключены к соответствующим синхронизирующим входам блока перемежения 23, а третий выход блока управления 24 подключен к третьему синхронизирующему входу блока перемежения 24 и синхронизирующему входу решающего блока 22. К управляющих выходов блока управления 24 подключены к соответствующим К управляющим входам блока перемежения 23. Выход решающего блока 22 подключен к информационному входу блока перемежения 23, а выход блока перемежения подключен к входу приемника информации 25. Выход генератора псевдослучайной последовательности 28 подключен к информационному входу регистра сдвига 29, (N+1) информационных выходов которого подключены к соответствующим (N+1) информационным входам регистра хранения 30, N информационных выходов которого подключены к соответствующим N информационным входам дешифратора 31. Дополнительный (N+1) выход регистра хранения 30 подключен к управляющему входу перемножителя 19. N выходов дешифратора 31 подключены к соответствующим N входам цифроаналогового преобразователя 32, выход которого подключен к управляющему входу усилителя 20.

Отдельные блоки заявляемого устройства имеют следующее назначение.

Источник информации 1 генерирует сам или воспринимает извне исходную информацию и преобразовывает ее в последовательность двоичных импульсов, сгруппированных в кодовые блоки, соответствующие различимым частям передаваемой информации. В частности, при передаче оцифрованной аналоговой информации каждый такой блок может представлять собой двоичный k-разрядный цифровой код очередного отсчета, квантуемого на 2k уровней.

Приемник информации 25 преобразовывает поступающую на вход последовательность двоичных импульсов к воспринимаемому (или необходимому для последующей передачи внешним устройствам) виду информации. В частности, при приеме оцифрованной аналоговой информации кодовые блоки могут преобразовываться в последовательность уровней напряжения, из которых при необходимости путем фильтрации формируется непрерывный аналоговый сигнал.

В качестве источника информации 1 и приемника информации 28 может выступать любое оконечное или промежуточное (кодирующее, каналообразующее, коммутационное и т.п.) цифровое устройство, позволяющее формировать и обрабатывать последовательность информационных блоков, поступающих, например, через цифровой стык С1-ФЛ-БИ (ГОСТ 24174-80, ГОСТ 26532-85)/14,15/. В качестве примера на фиг. 3 показан вариант реализации источника оцифрованной аналоговой информации.

Источник информации состоит из источника аналогового сигнала 1.1, аналого-цифрового преобразователя 1.2 и преобразователя параллельного кода в последовательный 1.3. Причем выход источника аналогового сигнала 1.1 подключен к входу аналого-цифрового преобразователя 1.2, a k выходов аналого-цифрового преобразователя 1.2 подключены к k входам преобразователя параллельного кода в последовательный 1.3. Выход преобразователя параллельного кода в последовательный 1.3 является выходом источника информации 1.

Входы kT0 и T0 источника информации 1 служат для синхронизации считывания разрядов на выход устройства.

В качестве источника аналогового сигнала может быть использован микрофон или звукосниматель /18/ стр. 671-687.

Вариант реализации аналого-цифрового преобразователя описан /5/ стр. 215 рис. 2.22.

Вариант реализации преобразователя параллельного кода в последовательный описан в /3/ стр. 208 рис. 5.4 (г).

В роли приемника информации может выступать устройство из последовательно включенных блоков преобразования последовательного кода в параллельный (см. /3/ стр. 208 рис. 5.4 (в)) и цифроаналогового преобразования, аналогичных описанным выше блокам 15(32).

Блок управления 2(24) служит для управления процессами: а) равномерного поразрядного считывания передаваемых кодовых блоков из источника информации 1 в блок перемежения 3 (неравномерного поразрядного считывания принимаемых кодовых блоков с выхода решающего блока 22 на вход блока перемежения 23), б) изменения очередности следования отдельных двоичных разрядов в кодовом блоке (восстановления исходной последовательности разрядов) и в) неравномерного поразрядного считывания кодовых блоков из блока перемежения 3 в фазовый модулятор 4 (равномерного поразрядного считывания передаваемых кодовых блоков с выхода блока перемежения 23 на вход приемника информации 25) в соответствии с последовательностями синхроимпульсов, формируемыми в блоках синхронизации 9, 27, и с псевдослучайными последовательностями, формируемыми генераторами псевдослучайных последовательностей 11, 28.

Вариант реализации блока управления 2(24) представлен на фиг.4. Блок управления состоит из двух счетчиков 2.1 (B-импульсов) и 2.2 (k-импульсов), дешифратора S тактов 2.3, RS-триггера 2.4, элемента И 2.5, 2.81-2.8k, S-разрядного регистра сдвига 2.6, дешифратора 2.7, 2.10 и делителя с максимальным коэффициентом деления 1:B·k 2.9. Причем синхронизирующий выход счетчика 2.1 является первым синхронизирующим выходом устройства 2. Синхронизирующий выход счетчика 2.2 является вторым синхронизирующим выходом устройства 2 и одновременно является R-входом триггера 2.4. Q выходов счетчика 2.1 подключены к Q входам дешифратора 2.3 на S тактов, где  . Выход дешифратора подключен к S входу триггера 2.4. Выход триггера 2.4 подключен к первому входу элемента И 2.5. Второй вход элемента И 2.5, вход счетчика 2.1 и вход делителя 2.9 являются тактовым входом блока управления 2 (24). Выход элемента И 2.5 подключен к первому входу S разрядного регистра сдвига 2.6. Второй вход S разрядного регистра сдвига 2.6 является управляющим входом блока управления 2 (24). S выходов регистра сдвига 2.6 подключены к S входам дешифратора 2.7, а K выходов счетчика 2.2 подключены к K входам дешифратора 2.7. K выходов дешифратора 2.7 являются выходами блока управления и K входами дешифратора 2.10. V выходов дешифратора 2.10 являются первыми входами V элементов И 2.81 - 2.8V. V выходов делителя 2.9 являются вторыми входами V элементов И 2.81 - 2.8V. V выходы элементов И 2.81 - 2.8V соединяются с V входами элемента ИЛИ 2.12. Выход элемента ИЛИ 2.12 является входом сброса делителя 2.9, входом счетчика 2.2 и третьим синхронизирующим выходом блока управления 2(24).

. Выход дешифратора подключен к S входу триггера 2.4. Выход триггера 2.4 подключен к первому входу элемента И 2.5. Второй вход элемента И 2.5, вход счетчика 2.1 и вход делителя 2.9 являются тактовым входом блока управления 2 (24). Выход элемента И 2.5 подключен к первому входу S разрядного регистра сдвига 2.6. Второй вход S разрядного регистра сдвига 2.6 является управляющим входом блока управления 2 (24). S выходов регистра сдвига 2.6 подключены к S входам дешифратора 2.7, а K выходов счетчика 2.2 подключены к K входам дешифратора 2.7. K выходов дешифратора 2.7 являются выходами блока управления и K входами дешифратора 2.10. V выходов дешифратора 2.10 являются первыми входами V элементов И 2.81 - 2.8V. V выходов делителя 2.9 являются вторыми входами V элементов И 2.81 - 2.8V. V выходы элементов И 2.81 - 2.8V соединяются с V входами элемента ИЛИ 2.12. Выход элемента ИЛИ 2.12 является входом сброса делителя 2.9, входом счетчика 2.2 и третьим синхронизирующим выходом блока управления 2(24).

Вариант реализации счетчиков 2.1 и 2.2, делителя 2.9 описан в /3, стр. 216, рис. 5.10/.

Вариант реализации дешифратора 2.3, 2.7, 2.10 описан /5, стр.131, рис. 1.95/.

Вариант реализации S-разрядного регистра сдвига 2.6 описан в /3, стр. 209, рис. 5.6/.

Вариант реализации элементов И, ИЛИ описан в /4, стр. 176 рис. 5.2/, а RS-триггера в /3, стр. 174, рис. 4.12/.

В представленной на фиг.4 схеме блока управления 2(24) для формирования различных вариантов перестановок k разрядов используется дешифратор, подобный дешифраторам 14 и 31, но с другим правилом преобразования двоичных кодов. Часть разрядов входного кода из S<<B символов, где B-база ШПС, формируется из начальных псевдослучайных двоичных символов ПСП, поступающих на управляющий вход блока управления в интервале между формированием последнего разряда предыдущего информационного блока и первым разрядом следующего. Данные разряды и определяют вариант псевдослучайного порядка следования номеров считываемых разрядов на  выходах блока управления в зависимости от номера такта, поступающего из счетчика данных тактов на остальные K входов дешифратора (в дополнение к указанным выше S входам) в блоке управления. Описанные функции дешифратора при больших значениях S и К более эффективно могут быть выполнены с помощью перепрограммируемого или постоянного запоминающего устройства (ПЗУ) по принципу, описанному в /16/ на стр. 328.

выходах блока управления в зависимости от номера такта, поступающего из счетчика данных тактов на остальные K входов дешифратора (в дополнение к указанным выше S входам) в блоке управления. Описанные функции дешифратора при больших значениях S и К более эффективно могут быть выполнены с помощью перепрограммируемого или постоянного запоминающего устройства (ПЗУ) по принципу, описанному в /16/ на стр. 328.

Дешифратор 2.10 служит для преобразования поступающего с выхода дешифратора 2.7 номера передаваемого разряда (в блоке 2) или принимаемого (в блоке 24) в двоичный код коэффициента деления делителя 2.9, формирующего совместно с элементами ИЛИ 2.12 и И 2.81 - 2.8k импульс считывания данного разряда в соответствии с используемым алгоритмом неравномерного распределения энергии сигналов между отдельными разрядами информационных блоков.

Блоки перемежения 3, 23 предназначены для периодического изменения порядка следования отдельных разрядов в передаваемых кодовых блоках (4) и восстановления их исходной последовательности (25) при приеме с учетом неравномерного считывания разрядов с выхода блока перемежения 3 на вход фазового модулятора 4 и с выхода решающего блока 22 на вход блока перемежения 23. В качестве основы реализации блоков перемежения 3, 23 (совместно с блоками управления 2, 24) могут выступать устройства, описанные в /16/ на стр. 327-330 рис. 8.11 и в /17/ на стр. 83-85 рис.2.10. Кроме того, вариант реализации данных блоков из типовых логических элементов /3, 4, 5/ показан на фиг. 5

Блок перемежения 3(23) состоит из d-триггера 3.1, 3,16 элементов И 3.2, 3.3, 3.61 - 3.6k, 3.8, 3.9, 3.111 - 3.11k, 3.12, 3.13, k-разрядных регистров сдвига 3.4 и 3.10, дешифратора 3.5, элементов ИЛИ 3.7, 3.14, 3.15. Входы дешифратора 3.5 являются управляющими входами устройства перемежения 3(23). Выходы дешифратора 3.5 являются вторыми входами элементов И 3.61 - 3.6k и 3.111 - 3.11k.

Прямой выход Л-триггера 3.1 подключен к вторым входам элементов И 3.8 и 3.9 и к второму входу элемента И 3.13. Инверсный выход D-триггера 3.1 подключен к информационному входу D-триггера 3.1, а также к вторым входам элементов И 3.2 и 3.3 и к второму входу элемента B 3.12. Синхронизирующий вход D-триггера 3.1 является первым синхронизирующим входом блока перемежения 3(23).

Первые входы элементов И 3.3 и 3.9, второй вход элемента И 3.13 являются информационным входом блока перемежения 3(23), а первые входы элементов И 3.2 и 3.8 являются вторым (третьим) синхронизирующим входом блока перемежения 3(23).

Выход элемента И 3.2 подключен к синхронизирующему входу k-разрядного регистра сдвига 3.4, а выход элемента И 3.3 подключен к информационному входу k-разрядного регистра сдвига 3.4, а его k выходов подключены к первым входам элементов И 3.61 - 3.6k. Выходы элементов И 3.61 - 3.6k подключены к соответствующим входам элемента ИЛИ 3.7. Выход элемента ИЛИ 3.7 подключен к первому входу элемента И 3.13. Выход элемента И 3.8 подключен к синхронизирующему входу k-разрядного регистра сдвига 3.10, а выход элемента И 3.9 подключен к информационному входу k-разрядного регистра сдвига 3.10, его k выходов - к первым входам элементов И 3.111 - 3.11k. Выходы элементов И 3.111 - 3.11k подключены к соответствующим входам элемента ИЛИ 3.14. Выход элемента ИЛИ 3.14 подключен к первому входу элемента И 3.12. Выходы элементов И 3.12 и 3.13 подключены к первому и второму входу соответственно элемента ИЛИ 3.15. Выход элемента ИЛИ 3.15 подключен к информационному входу D-триггера 3.16. Синхронизирующий вход D-триггера 3.16 является третьим (вторым) синхронизирующим входом блока перемежения 3(23). Прямой выход D-триггера 3.16 является выходом блока перемежения 3(23).

Вариант реализации элементов И 3.2, 3.3, 3.61 - 3.6k 3.8, 3.9, 3.111 - 3.11k, 3.12, 3.13 описан в /4, стр. 176 рис. 5.2/.

Вариант реализации D-триггера 3.1, 3.16 описан в /4, стр. 163, рис. 4.26/.

Вариант реализации k-разрядных регистров сдвига 3.4 и 3.10 описан в /3, стр. 209, рис. 5.6/.

Вариант реализации дешифратора 3.5 описан в /5, стр. 131, рис. 1.95/.

Вариант реализации элементов ИЛИ 3.7, 3.14, 3.15 описан в /5, стр. 35, рис. 1.19/.

В представленной на фиг.5 схеме блока перемежения 3(23) для совмещения процедуры равномерного считывания разрядов из источника информации 1 (неравномерного считывания из решающего блока 22) в порядке их поступления на информационный вход и процедуры неравномерного считывания данных разрядов с выхода блока перемежения 3 на вход фазового модулятора 4 (равномерного считывания данных разрядов с выхода блока перемежения 23 на вход приемника информации 25) в порядке, задаваемом последовательностью кодов на К управляющих входах, используются два регистра 3.4, 3.10. Данные регистры выполняют поочередно функции входного регистра сдвига (при открытых элементах И 3.2, 3.3 или 3.8 и 3.9) и выходного регистра хранения (совместно с дешифратором 3.5, элементами ИЛИ 3.15 и D-триггером 3.16 при открытых элементах И 3.12 или 3.13 совместно с используемыми при этом элементами И 3.61 - 3.6k, ИЛИ 3.7 или элементов И 3.111 - 3.11k и ИЛИ 3.14) за счет переключения D-тригера 3.1 тактируемого импульсами с периодом T=KT0).

Фазовый модулятор 4 предназначен для изменения полярности импульсов опорной псевдослучайной последовательности, образующей ШПС, в соответствии с полярностью очередных отсчетов передаваемой информационной последовательности. Вариант реализации фазового модулятора 4 описан в /8, рис. 11.3 и рис. 11.4, стр. 273-274/.

Генератор несущей частоты 10 формирует несущее высокочастотное колебание. Вариант реализации генератора несущей частоты 10 описан в /12, рис. 7.6 и рис. 7.7, стр. 212 и 217 соответственно/.

Модулятор 5 предназначен для изменения фазы несущего высокочастотного колебания в соответствии с полярностью передаваемых видеоимпульсов. Вариант реализации модулятора 5 описан в /12, рис. 5.13 стр. 157/.

Усилители 6,20 предназначены для реализации алгоритма амплитудной манипуляции субэлементов ШПС. Вариант реализации усилителей 6,20 описан в /4, рис. 2.2(д), стр.26-40/.

Усилитель мощности 7 предназначен для усиления высокочастотного сигнала до величины, необходимой для компенсации потерь в среде распространения радиоволн. Вариант реализации усилителя мощности 10 описан в /13, рис. 11.24, стр. 327/.

Антенные устройства 8, 16 предназначены для преобразования высокочастотного радиосигнала в радиоволны при передаче (8) и обратно при приеме (16). Вариант реализации антенных устройств 8, 16 описан в /8, рис. 7.2 и рис.7.4, стр. 169-172/.

Блоки синхронизации 9, 27 предназначены для согласования процессов функционирования генераторов псевдослучайной последовательности 10, 28, регистров сдвига 12, 29, регистров хранения 13, 33 и блоков управления 2, 24. Кроме того, блок синхронизации 27 на приемной стороне радиолинии управляет настройкой приемного тракта на принимаемый радиосигнал и определяет моменты регистрации принятых двоичных импульсов в решающем блоке 22. Вариант реализации блоков синхронизации 9, 27 описан в /9, стр.266-328/.

Генераторы псевдослучайной последовательности 11, 28 предназначены для формирования одинаковых на передающей (11) и приемной (28) сторонах радиолинии последовательностей равновероятных двоичных импульсов. Вариант реализации генераторов псевдослучайной последовательности 11, 28 описан в /11, рис. 20.20, стр. 357/.

Регистры сдвига 12, 29 предназначены для формирования последовательности (N+1)-разрядных псевдослучайных двоичных чисел и реализации процедуры преобразования последовательного кода данных чисел в параллельный. Вариант реализации регистров сдвига 12, 29 описан в /3, стр. 208-210, например, рис. 5.4 (в)/.

Регистры хранения 13, 30 предназначены для удержания параллельного кода очередного псевдослучайного числа в течение длительности формирования и обработки одного субэлемента ШПС. Вариант реализации регистров хранения 13,30 описан в /3, стр. 208-210, например, рис. 5.4 (а)/.

Дешифраторы 14, 31 предназначены для преобразования псевдослучайных чисел с равномерным распределением в псевдослучайные числа с заданным распределением в соответствии с используемым алгоритмом АФМ ШПС. Вариант реализации дешифраторов 14, 31 описан в /4, стр. 119-135/.

Цифроаналоговые преобразователи 15, 32 предназначены для преобразования двоичных кодов в аналоговые уровни напряжений, управляющих коэффициентами усиления соответственно усилителей 6, 20. Вариант реализации цифроаналоговых преобразователей 15,32 описан в /4, стр. 185- 193/.

Смеситель 17 предназначен для перенесения принимаемых радиосигналов на промежуточную частоту. Вариант реализации смесителя 17 описан в /12, стр. 151-159/.

Гетеродин 26 предназначен для формирования частоты смещения, являющейся разностью между частотой принимаемого радиосигнала и промежуточной частотой. Вариант реализации гетеродина 26 описан в /4, рис 2.2(ж) и рис.2.2 (к), стр. 27/.

Усилитель промежуточной частоты 18 предназначен для усиления принятого радиосигнала на промежуточной частоте до величины, необходимой для работы последующих блоков приемного тракта. Вариант реализации усилителя промежуточной частоты 18 описан в /4, рис. 2.2(ж) и рис. 2.2(к), стр. 27/.

Перемножитель 19 предназначен для снятия псевдослучайной манипуляции принимаемого радиосигнала. Вариант реализации перемножителя 19 описан в /6, рис.4, стр. 203/.

Интегратор 21 предназначен для узкополосной фильтрации принятого радиосигнала. Вариант реализации интегратора 21 описан в /12, рис. 6.6(д), стр. 191/.

Решающий блок 22 предназначен для регистрации очередного принятого двоичного информационного разряда. Вариант реализации решающего блока 22 показан в /3, стр. 363-371/.

Заявляемое устройство работает следующим образом.

В передающей части от источника информации 1 последовательность двоичных символов с постоянным периодом T0 (T0 - период следования тактовых импульсов на втором синхронизирующем выходе блока управления 2) поступает на вход перемножителя 3, в котором отслеживаются границы информационных блоков, включающих k двоичных символов (на основании временного положения тактовых импульсов на первом синхронизирующем выходе блока управления 2, следующих с периодом T=kT0), и в пределах данных границ осуществляется перестановка информационных символов (разрядов) в соответствии с очередностью номеров, поступающих в параллельном коде с  управляющих выходов блока управления 2. Синхронно (но с различным периодом следования тактовых импульсов Ti, i= 1, k, где Ti - текущий интервал времени между импульсами на третьем синхронизирующем выходе блока управления 2) с поступлением данных номеров соответствующий им двоичный символ считывается на вход фазового модулятора 4. Псевдослучайность последовательности номеров считываемых разрядов обеспечивается за счет соответствующего преобразования в блоке управления 2 двоичной псевдослучайной последовательности, поступающей на управляющий вход данного блока с дополнительного (N+1) выхода регистра хранения 13.

управляющих выходов блока управления 2. Синхронно (но с различным периодом следования тактовых импульсов Ti, i= 1, k, где Ti - текущий интервал времени между импульсами на третьем синхронизирующем выходе блока управления 2) с поступлением данных номеров соответствующий им двоичный символ считывается на вход фазового модулятора 4. Псевдослучайность последовательности номеров считываемых разрядов обеспечивается за счет соответствующего преобразования в блоке управления 2 двоичной псевдослучайной последовательности, поступающей на управляющий вход данного блока с дополнительного (N+1) выхода регистра хранения 13.

От генератора псевдослучайной последовательности (ГПСП) 11 с дополнительного (N+1) выхода регистра хранения 13 на второй вход фазового модулятора 4 поступает двоичный сигнал с длительностью импульсов τ = T0/B, где B - число субэлементов ШПС, приходящихся на один информационный символ. Фактически данное число характеризует базу ШПС. Период следования импульсов на выходе ГПСП 14 равен τ0= τ/(N+1) (N - целое число). Сигналами с первого выхода блока синхронизации 9, период следования которых равен τ0, последовательность двоичных импульсов с выхода ГПСП 14 записывается в регистр сдвига 12, а затем сигналами с второго выхода блока синхронизации 12, следующими с частотой f = 1/ τ - в регистр хранения 13. С первых N выходов регистра хранения 13 N разрядов двоичного случайного числа R∈[0,...,2N-1] поступают на N входов дешифратора 14. На N выходах первого дешифратора 14 появляется N-разрядное двоичное число, равное значению одной из m ≥ 2 псевдослучайных амплитуд, соответствующей номеру участка на единичном отрезке, в который попадает случайное число R/2N (в данном случае используется геометрическая интерпретация m-ступенчатого дискретного распределения вероятностей). Соотношение размеров данных участков должно соответствовать соотношению вероятностей m различных амплитуд субэлементов согласно используемому алгоритму АФМ ШПС /1/. Цифроаналоговый преобразователь (ЦАП) 15 преобразует входную двоичную комбинацию в аналоговый сигнал, соответствующий одной из m псевдослучайных амплитуд. С выхода первого ЦАП 15 сигнал поступает на управляющий вход усилителя 6.

Блок синхронизации 9 формирует две последовательности импульсов с частотами f и (N+1)f. Вторая из данных последовательностей синхронизирует работу ГПСП 11 и регистра сдвига 12, а первая синхронизирует работу регистра хранения 13 и блока управления 2.

Видеопоследовательность ШПС, переносящая информационные символы, с выхода фазового модулятора 4 поступает в модулятор 5, в котором осуществляется фазовая модуляция несущего колебания, поступающего на второй вход модулятора 5 от генератора несущей частоты 10. Фазоманипулированный шумоподобный сигнал с выхода модулятора 5 поступает на вход усилителя 6. С выхода усилителя 6 АФМ ШПС поступает на вход усилителя мощности 7, где сигнал усиливается до требуемого уровня и затем через передающую антенну 8 излучается в пространство.

В приемной части радиолинии сигнал, принятый приемной антенной 16, проходит через смеситель 17, переносится с помощью гетеродина 26 на промежуточную частоту, усиливается в усилителе промежуточной частоты (УПЧ) 18. С выхода УПЧ 18 сигнал поступает на перемножитель 19, на второй вход которого в качестве опорного подается сигнал от ГПСП 28 через дополнительный (N+1)-й выход регистра хранения 30. Результат перемножения входного и опорного сигналов поступает на усилитель 20, коэффициент усиления которого зависит от уровня сигнала, поступающего на управляющий вход усилителя 20 с выхода ЦАП 32. Формирование сигнала на выходе ЦАП 32 происходит с помощью ГПСП 28, регистра сдвига 29, регистра хранения 30, блока синхронизации 27, дешифратора 31 аналогично формированию сигнала на выходе ЦАП 15. С выхода усилителя 20 сигнал поступает на интегратор 21 и далее на блок синхронизации 27 и решающий блок 22.

Блок синхронизации 27 формирует две последовательности импульсов с частотами f и (N+1)f, управляет режимом работы решающего блока 22 и осуществляет поиск сигнала АФМ ШПС по частоте и по времени. Для поиска АФМ ШПС по частоте блок синхронизации 27 перестраивает гетеродин 26, а по времени задерживает или ускоряет работу ГПСП 28 и связанных с ним блоков. При этом наряду с совмещением во времени псевдослучайных последовательностей, формируемых в ГПСП 11 и 28, обеспечивается совмещение границ информационных блоков, отслеживаемых блоками управления 2 и 24. За счет этого блок перемежения 23 после считывания принятых символов с выхода решающего блока 22 с учетом различия их длительности Ti на основании последовательности номеров, поступающих с K выходов блока управления 24, восстанавливает исходную последовательность информационных разрядов и с постоянным периодом следования Т0 выдает их приемнику информации 25.

Положительный эффект от заявляемого устройства продемонстрируем на следующем примере.

Пусть в радиолинии осуществляется передача оцифрованной аналоговой информации в виде последовательности независимых отсчетов Ut∈ [-UM, + UM], преобразуемых в источнике информации 1 в k-разрядный двоичный код. В роли показателя качества передачи аналоговых отсчетов будем рассматривать дисперсию ошибки σ

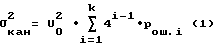

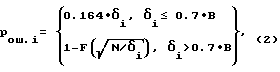

Итоговая дисперсия ошибки σ

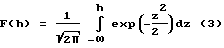

При использовании радиолинии с АФМ ШПС с базой B >> 1 действие помех с любым распределением оказывается асимптотически эквивалентным действию гауссовской помехи /2/. В худшем случае при воздействии на i-й разряд когерентных помех с относительной средней мощностью δi (допускающей прерывистое воздействие) вероятность ошибки pош.i может быть рассчитана по формуле

где

В выражении (2) учтено, что при δi<0,7B наихудшая помеха является прерывистой со скважностью l-δi/0,7B и относительной мощностью импульсов помех δпик= 0,7B.

Обозначим отношение средней мощности помех к средней мощности сигналов на длительности передачи k разрядов одного аналогового отсчета буквой δ. Тогда при распределении энергии помех y={yi}k и распределении энергии сигналов x= { xi}k получим δi= δyi/xi. На фиг. 6 приведены графики зависимости дисперсии ошибки σ

Линия 2 соответствует наихудшему распределению энергии помех y*={yi*}k при равномерном распределении энергии сигналов. Данное распределение y* зависит от величины δ и вычисляется, в общем случае, путем численного решения несколько громоздкой системы дифференциальных уравнений. При малой величине δ для данного распределения характерно выделение всей энергии помех на подавление только старшего разряда, т.е. y*k=1, y*1=...=y*k-1=0. С ростом величины δ все большая часть энергии помех выделяется для подавления более младших разрядов. В частности, (k-1)-й разряд начинает подавляться при  > 5·B/k.

> 5·B/k.

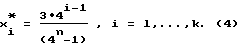

Путем введения перемежения разрядов можно исключить прицельное подавление старших разрядов, в результате чего зависимость дисперсии ошибки от относительной мощности помех будет гарантироваться не выше линии 1 на фиг.6. Однако, как следует из выражения (1), при равной вероятности ошибки приема отдельных разрядов вклад в дисперсию ошибки искажений старших разрядов намного превышает вклад искажений младших разрядов. В целом, при известном распределении энергии помех можно решить соответствующую оптимизационную задачу и найти наилучшее распределение энергии сигналов, а затем реализовать его в предлагаемой радиолинии с АФМ ШПС. Можно показать, что в худшем случае при неизвестном распределении помех с ограниченной средней мощностью наилучшее распределение энергии сигналов описывается выражением

Заметим, что из выражения (4) следует простое соотношение: xi/xi-1 = 4, i = 2,...k, упрощающее реализацию данного неравномерного распределения путем неравномерного распределения дискретных временных отрезков, кратных четырем. При использовании распределения энергии сигналов (4) гарантируется, что при любом распределении энергии помех зависимость дисперсии ошибок от относительной средней мощности помех не будет выше линии 3 на фиг.6.

На фиг. 6 показаны графики зависимости дисперсии ошибок от относительной мощности помех при различном распределении энергии сигналов и помех между разрядами оцифрованных аналоговых отсчетов. Как следует из графиков на фиг. 6, при использовании неравномерного распределения (4) энергии сигналов в линии с АФМ ШПС гарантируется энергетический выигрыш в области малых помех около 13 дБ по сравнению со случаем равномерного распределения без перемежения и около 5.5 дБ по сравнению со случаем равномерного распределения с перемежением.

Литература

1. Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами // АС СССР N 1635275, 1991.

2. Чуднов А.М. Помехоустойчивость корреляционного приема псевдослучайных сигналов, модулированных по амплитуде и фазе //Радиотехника и электроника, 1987. -т. XXXII. - N1, - С.62-68.

3. Алексеенко А.Г., Шагурин И.И. Микросхемотехника. М.: Радио и связь, 1982. - 414 с.

4. Батушев В.А. Микросхемы и их применение. М.: Радио и связь, 1983. - 271 с.

5. Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1988. - 352 с.

6. Папернов А.А. Логические основы ЦВТ. М.: Связь, 1973. - 352 с.

7. Чуднов А.М. О минимаксных алгоритмах формирования и приема сигналов. //Проблемы передачи информации, 1986, т. XXII. - вып.4, С. 49-54.

8. Дж.Спилкер. Цифровая спутниковая связь. М.:Связь, 1979. - 592 с.

9. Варакин Л. Е. Системы связи с шумоподобными сигналами. М.: Радио и связь, 1985. - 384 с.

10. Банкет В.А., Дорофеев В.М. Цифровые методы в спутниковой связи. М.: Радио и связь, 1988. -213 с.

11. У.Титце, К.Шенк. Полупроводниковая схемотехника: Справочное руководство. М.: Мир, 1982. - 512 с.

12. Радиоприемные устройства /Под ред. Л.Г.Барулина. М.: Радио и связь, 1984. - 272 с.

13. Каганов В.И. СВЧ полупроводниковые передатчики. М.: Радио и связь, 1981.-400 с.

14. Мячев А.А., Щерба В.Г. Интерфейсы систем обработки данных. М.: Радио и связь, 1989. - 416 с.

15. Порохов О. Н. Цифровой стык на основе относительного биимпульсного сигнала //Электросвязь, 1989. N12. С.10-15.

16. Кларк Дж, Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987- 392 с.

17. Лазарев В.Г. Интеллектуальные цифровые сети - М.: Статистика, 1996 - 224 с.

18. Полупроводниковые приемно-усилительные устройства: Справочник радиолюбителя /P. M. Терещук, К.М.Терещук, С.А.Седов. - Киев: Наукова думка, 1989. -800 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1999 |

|

RU2144272C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1996 |

|

RU2101871C1 |

| Радиолиния, защищенная от несанкционированного доступа | 2023 |

|

RU2820855C1 |

| РАДИОЛИНИЯ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273099C1 |

| Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами | 1989 |

|

SU1635275A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2207729C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2163027C2 |

Изобретение относится к области радиотехники и может быть использовано в системах связи, функционирующих в условиях неопределенных помех. Техническим решением является разработка радиолинии, позволяющей повысить качество приема при передаче неоднородной информации в условиях воздействия неопределенных помех с ограниченной средней мощностью, и достигается тем, что в радиолинию с АФМ ШПС дополнительно введены блоки управления и блоки перемежения. Дополнительно введенные элементы позволяют в линии с АФМ ШПС реализовать алгоритм перемежения и неравномерного распределения энергии сигналов путем изменения их длительности. При этом в случае передачи, например, независимых цифровых отсчетов аналоговой информации реализованный алгоритм обеспечивает энергетический выигрыш до 13 дБ по сравнению с алгоритмом равномерного распределения без перемежения и до 5,5 дБ по сравнению с алгоритмом равномерного распределения с перемежением. 6 ил.

Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами, содержащая на передающей стороне источник информации, фазовый модулятор, модулятор, генератор несущей частоты, усилитель, усилитель мощности, антенное устройство, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь, причем выход фазового модулятора соединен с первым входом модулятора, выход генератора несущей частоты подключен к второму входу модулятора, выход которого подключен к информационному входу усилителя, выход которого подключен к входу усилителя мощности, выход которого подключен к входу антенного устройства, первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига, а его второй выход подключен к тактовому входу регистра хранения, выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов регистра сдвига, где N ≥2, подключены к соответствующим (N+1) информационным входам регистра хранения, N информационных выходов регистра хранения подключены к соответствующим N информационным входам дешифратора, а дополнительный (N+1) выход регистра хранения подключен к второму входу фазового модулятора, N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя, а на приемной стороне содержащая антенное устройство, смеситель, усилитель промежуточной частоты, перемножитель, усилитель, интегратор, решающий блок, гетеродин, блок синхронизации, генератор псевдослучайной последовательности, регистр сдвига, регистр хранения, дешифратор, цифроаналоговый преобразователь и приемник информации, причем выход антенного устройства подключен к первому входу смесителя, выход смесителя подключен к входу усилителя промежуточной частоты, выход которого подключен к информационному входу перемножителя, выход которого подключен к информационному входу усилителя, выход которого подключен к входу интегратора, выход которого подключен к входу решающего блока и к входу блока синхронизации, первый выход блока синхронизации подключен к входу генератора псевдослучайной последовательности и к тактовому входу регистра сдвига, второй выход блока синхронизации подключен к тактовому входу регистра хранения, третий выход блока синхронизации подключен к входу гетеродина, выход которого подключен к второму входу смесителя, выход генератора псевдослучайной последовательности подключен к информационному входу регистра сдвига, (N+1) информационных выходов которого подключены к соответствующим (N+1) информационным входам регистра хранения, N информационных выходов которого подключены к соответствующим N информационным входам дешифратора, а дополнительный (N+1) выход регистра хранения подключен к управляющему входу перемножителя, N выходов дешифратора подключены к соответствующим N входам цифроаналогового преобразователя, выход которого подключен к управляющему входу усилителя, отличающаяся тем, что дополнительно введены на передающей стороне блок управления и блок перемежения, причем выход источника информации подключен к информационному входу блока перемежения, выход блока перемежения подключен к первому входу фазового модулятора, дополнительный (N+1) выход регистра хранения подключен к управляющему входу блока управления, второй выход блока синхронизации подключен к тактовому входу блока управления, первый и второй синхронизирующие выходы блока управления подключены к соответствующим синхронизирующим входам источника информации и блока перемежения, а третий синхронизирующий выход блока управления подключен к третьему синхронизирующему входу блока перемежения, К управляющих выходов блока управления, где К≥2, подключены к соответствующим К управляющим входам блока перемежения, а на приемной стороне дополнительно введены блок управления и блок перемежения, причем второй выход блока синхронизации подключен к тактовому входу блока управления, а дополнительный (N+1) выход регистра хранения подключен к управляющему входу блока управления, первый и второй синхронизирующие выходы блока управления подключены к соответствующим синхронизирующим входам блока перемежения, а третий синхронизирующий выход блока управления подключен к третьему синхронизирующему входу блока перемежения и синхронизирующему входу решающего блока, К управляющих выходов блока управления подключены к соответствующим К управляющим входам блока перемежения, выход решающего блока подключен к информационному входу блока перемежения, а выход блока перемежения подключен к входу приемника информации.

| Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами | 1989 |

|

SU1635275A1 |

| Делитель частоты периодических сигналов сложной формы | 1986 |

|

SU1356179A1 |

| СПОСОБ ПОЛУЧЕНИЯ ПИРОТЕХНИЧЕСКОГО АЭРОЗОЛЬОБРАЗУЮЩЕГО СОСТАВА ДЛЯ ТУШЕНИЯ ПОЖАРОВ | 1999 |

|

RU2153376C1 |

| US 665472 A, 23.05.1972. | |||

Авторы

Даты

2001-02-27—Публикация

1999-11-29—Подача