Настоящее изобретение относится к управляющему алгоритму системы фазовой автоподстройки частоты с цифровой обработкой (далее ЦФАПЧ) (DP-PLL) для сетевой синхронизации и, в частности, к способу и устройству для управления системой фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации для предотвращения разрывности фазы, так называемого "фазового скачка", вырабатываемого во время коммутации опорного синхросигнала и изменения рабочего режима.

Рассматриваемой сетью связи является интегральная сеть цифровой связи, которая состоит из цифровых телефонных станций, соединенных между собой с помощью средств цифровой передачи.

В такой интегральной сети цифровой связи необходима система для синхронизации всех тактовых генераторов телефонных станций. Из различных систем сетевой синхронизации мы выбрали свободно подключенную систему "ведущий - ведомый", в которой каждая ведомая телефонная станция имеет стабильный генератор, синхронизированный с ведущим тактовым генератором.

В качестве ключевой составляющей свободно подключенной системы "ведущий - ведомый" в IEEE TRANSACTIONS ON COMMUNICATIONS, vol. СОМ-31, N 12, December 1983, рассмотрена интеллектуальная ЦФАПЧ с использованием цифровой обработки (DP-PLL).

Такая ЦФАПЧ принимает единственный опорный синхросигнал и вырабатывает местный тактовый сигнал, отрегулированный так, чтобы быть синхронизированным с опорным синхросигналом.

Однако ЦФАПЧ требует точного управляемого напряжением кварцевого генератора для предотвращение свободного хода.

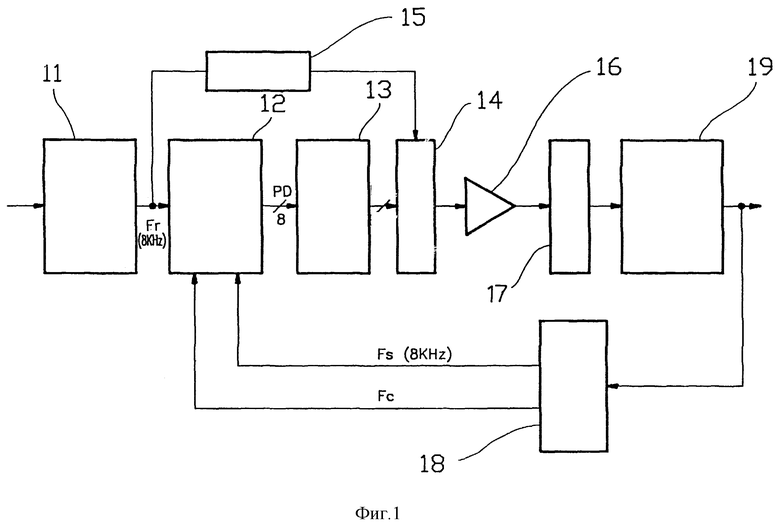

Фиг. 1 показывает другую известную ЦФАПЧ, имеющую структуру, сходную с вышеописанной ЦФАПЧ. Эта ЦФАПЧ включает в себя приемную часть 11 опорного синхросигнала, которая принимает опорный синхросигнал, вводимый извне, детектор 12 индекса фазовой модуляции для обнаружения данных индекса фазовой модуляции (далее ИФМ) (PD), который использует опорный тактовый сигнал Fr, полученный от приемной части 11 опорного синхросигнала, и тактовые сигналы Fs и Fc, полученные путем деления частоты системного тактового сигнала, общую память 13, которая хранит данные PD индекса фазовой модуляции, полученные от детектора 12 индекса фазовой модуляции, центральный процессор (далее ЦП) (CPU) 14, обрабатывающий данные индекса фазовой модуляции, считанные из общей памяти 13, в соответствии с управляющим алгоритмом для управления системным тактовым сигналом, подлежащим синхронизации с опорным тактовым сигналом, монитор 15, воспринимающий потерю опорного тактового сигнала для вывода его на ЦП 14, цифроаналоговый (D/A) преобразователь" (далее ЦАП) 16, преобразующий цифровой сигнал, выданный от ЦП 14, в аналоговый сигнал, генератор 17, управляемый напряжением (далее ГУН) (VCO), синхронизирующий системный тактовый сигнал с опорным тактовым сигналом в ответ на выходной сигнал ЦАП 16, делитель 18, делящий частоту тактового сигнала, выданного ГУН 17, и выдающий результат на детектор 12 индекса фазовой модуляции, и распределитель 19 частот, выдающий сигналы частоты, требуемой в системе, используя тактовый сигнал, полученный от ГУН 17.

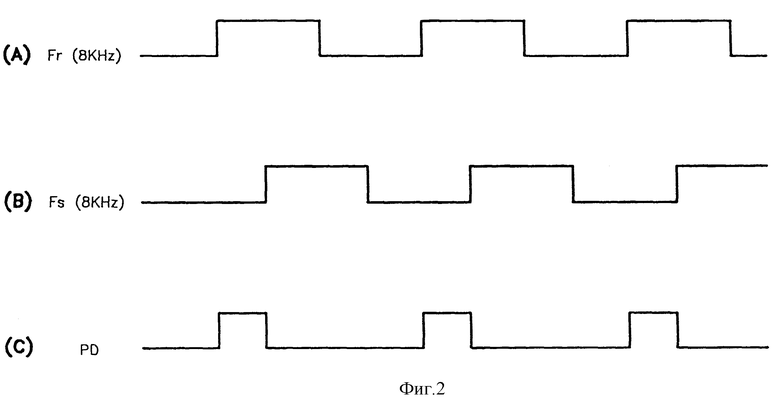

Работа обычной ЦФАПЧ для сетевой синхронизации описана со ссылками на колебания по фиг. 2.

Если система начинает работать и вводится опорный синхросигнал, то приемник 11 опорного синхросигнала вырабатывает опорный тактовый сигнал Fr в 8 кГц, как показано на фиг. 2A, и этот опорный тактовый сигнал подается на детектор 12 индекса фазовой модуляции. Детектор 12 индекса фазовой модуляции получает данные индекса фазовой модуляции между опорным тактовым сигналом, деленным по частоте тактовым сигналом Fs в 8 кГц, введенным от делителя 18 счетным тактовым сигналом Fc, подсчитывает период высокого уровня данных PD индекса фазовой модуляции, показанный на фиг. 2(С), и запоминает это подсчитанное значение в общей памяти 13 как квантованные данные индекса фазовой модуляции между опорным тактовым сигналом и тактовым сигналом.

ЦП 14 считывает данные PD индекса фазовой модуляции, хранящиеся в общей памяти 13, в течение 8,192 секунд в каждый период времени в 250 с и определяет, находятся ли считанные данные в действительном допуске. Если данные находятся в действительном допуске, то ЦП вычисляет среднее значение фазовой ошибки. ЦП 14 вырабатывает управляющее значение ГУН 17 путем умножения среднего значения на изменяющееся взвешенное значение согласно соответствующему режиму.

ЦП 14 выдает управляющее значение ГУН 17 путем изменения соответствующей пропорциональной постоянной и интегрирующей постоянной согласно быстрому и нормальному режиму. Если обнаружено, что данные превышают действительный допуск, то ЦП 14 определяет, потерян или нет опорный тактовый сигнал. Если опорный тактовый сигнал потерян, ЦП 14 входит в режим свободного хода и среднее управляющее значение ГУН 17 заменяется управляющим значением, измеренным в нормальном режиме.

Но известный аналог также требует точного кварцевого генератора, управляемого напряжением, хотя ЦФАПЧ вырабатывает системный тактовый сигнал, отрегулированный так, чтобы быть синхронизированным с единственным опорным синхросигналом.

Для решения вышеперечисленных проблем в патенте США N 5136617, выданном 4 августа 1992 Стенарду, рассмотрено устройство для выделения системного тактового сигнала с использованием двойных опорных синхросигналов.

Вышеупомянутое устройство предлагает недорогую и надежную систему синхронизации путем выбора одного из множества синхросигналов как опорного синхросигнала.

Однако, если это устройство применяется для сетевой синхронизации с использованием ЦФАПЧ, то может появиться разовый скачок согласно коммутации опорного сигнала синхронизации во время изменения рабочего режима.

Наиболее близким аналогом к предлагаемому изобретению является патент США N 4305045, кл. H 03 L 7/08, 08.12.81 г., в котором заявлен способ управления системой фазовой автоподстройки частоты с цифровой обработкой, включающий установку значения, соответствующего первоначальной центральной частоте в генераторе, управляемом напряжением, в исходном режиме и введение в режим свободного хода, преобразование режима свободного хода в быстрый режим и преобразование быстрого режима в нормальный режим, когда быстрый режим становится стабильным.

В патенте США N 4305045 заявлено также устройство для управления системой фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации, осуществляющее вышеуказанный способ и содержащее два интерфейса для приема двух опорных синхросигналов из устройства для подачи цифрового тактового сигнала и выделения двух опорных тактовых сигналов, средство выбора и деления опорных тактовых сигналов для деления по частоте двух опорных тактовых сигналов интерфейса, средство наблюдения за потерей выбранного опорного тактового сигнала, средство обнаружения и запоминания ошибки фазы для подсчета значения сравнением тактового сигнала, выделенного из системного тактового сигнала, и тактового сигнала, выбранного в средстве выбора и деления опорного тактового сигнала с помощью системного тактового сигнала с наибольшей частотой среди системных тактовых сигналов для запоминания его в качестве данных девиации фазы, управляющее средство для выработки управляющего значения для синхронизации системного тактового сигнала с выбранным тактовым сигналом синхронизации путем обработки данных, считанных из средства обнаружения и запоминания ошибки фазы в соответствии с управляющим алгоритмом, генерирующую схему, управляемую напряжением, на которую подается управляющее значение для преобразования его в аналоговый сигнал, подачи аналогового сигнала на генератор, управляемый напряжением, и выработки системного тактового сигнала и делитель для деления по частоте системного тактового сигнала и выработки множества поделенных системных тактовых сигналов, кадрового импульса и многокадрового импульса.

Однако вышеописанный способ и устройство для его осуществления не может предотвратить фазовый скачок, получающийся во время коммутации опорного синхросигнала во время изменения рабочего режима.

В основу настоящего изобретения была положена задача разработки способа управления системой фазовой автоподстройки частоты с цифровой обработкой и создания устройства для его осуществления, которое может предотвратить фазовый скачок, получающийся во время коммутации опорного синхросигнала и изменения рабочего режима и внезапной нестабильности фазы или частотных флуктуаций в переходном режиме.

Это достигается тем, что в способе управления системой фазовой автоподстройки частоты с цифровой обработкой, включающем установку значения, соответствующего первоначальной центральной частоте в генераторе, управляемом напряжением, в исходном режиме и введение в режим свободного хода, преобразование режима свободного хода в быстрый режим и преобразование быстрого режима в нормальный режим, когда быстрый режим становится стабильным, согласно изобретению преобразование режима свободного хода в режим быстрого хода осуществляют, если в режиме свободного хода, определенного как нормальный, не обнаружена ненормальность опорного тактового сигнала, запоминают данные девиации фазы для заранее заданного промежутка времени, вычисляют ее среднее значение для установки среднего значения в качестве опорной величины девиации фазы быстрого режима, вычисляют и управляют управляющим значением генератора, управляемого напряжением, для сведения данных девиации фазы в опорную величину девиации фазы, после преобразования быстрого режима в нормальный режим, когда быстрый режим становится стабильным, запоминают данные девиации фазы для заранее заданного промежутка времени, измеряют среднее значение для переустановки указанного среднего значения в качестве опорной величины девиации фазы в нормальном режиме, вычисляют и управляют управляющим значением генератора, управляемого напряжением, которое сводится в значение опорной величины девиации фазы, преобразуют быстрый режим или нормальный режим в режим удержания без изменения заранее заданной опорной величины девиации фазы в случае, если один и другой опорные тактовые сигналы аномальны, вычисляют и управляют управляющим значением генератора, управляемого напряжением, путем установки в качестве опорной величины девиации фазы значения, полученного путем вычитания среднего значения имеющихся данных девиации фазы, вычисленного из управляющего значения генератора, управляемого напряжением, в режиме удержания, из среднего значения данных девиации фазы для заранее заданного промежутка времени после преобразования из режима удержания в быстрый режим в случае, когда опорный тактовый сигнал нормально отслеживается в режиме удержания.

Целесообразно, чтобы способ дополнительно содержал операцию вычисления и управления управляющим значением генератора, управляемого напряжением, путем установки в качестве опорной величины девиации фазы значения, полученного путем вычитания среднего значения имеющихся данных девиации фазы, вычисленного из управляющего значения генератора, управляемого напряжением, в нормальном режиме, из среднего значения данных девиации фазы для заранее заданного периода времени после преобразования из нормального режима в быстрый режим в случае, когда упомянутый опорный тактовый сигнал находится в ненормальном состоянии.

Желательно, чтобы способ дополнительно содержал операции квантования среднего значения и прибавления значения сдвига к квантованному среднему значению.

Это достигается также тем, что в устройстве для управления системой фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации, содержащем два интерфейса для приема двух опорных синхросигналов из устройства для подачи цифрового тактового сигнала и выделения двух опорных тактовых сигналов, средство выбора и деления опорных тактовых сигналов для деления по частоте двух опорных тактовых сигналов интерфейса, средство наблюдения за потерей выбранного опорного тактового сигнала, средство обнаружения и запоминания ошибки фазы для подсчета значения сравнением тактового сигнала, выделенного из системного тактового сигнала, и тактового сигнала, выбранного в средстве выбора и деления опорного тактового сигнала с помощью системного тактового сигнала с наибольшей частотой среди системных тактовых сигналов для запоминания его в качестве данных девиации фазы, управляющее средство для выработки управляющего значения для синхронизации системного тактового сигнала с выбранным тактовым сигналом синхронизации путем обработки данных, считанных из средства обнаружения и запоминания ошибки фазы в соответствии с управляющим алгоритмом, генерирующую схему, управляемую напряжением, на которую подается управляющее значение для преобразования его в аналоговый сигнал, подачи аналогового сигнала на генератор, управляемый напряжением, и выработки системного тактового сигнала и делитель для деления по частоте системного тактового сигнала и выработки множества поделенных системных тактовых сигналов, кадрового импульса и многокадрового импульса, согласно изобретению указанное средство обнаружения и запоминания вычисляет значение, полученное путем подсчета интервалов от нарастающего фронта поделенного опорного тактового сигнала до нарастающего фронта поделенного системного тактового сигнала.

В устройстве управляющее средство может вводить в быстрый режим в случае, когда опорный тактовый сигнал нормален в режиме свободного хода, определенном на начальной стадии, запоминать данные девиации фазы для заранее заданного периода времени в первоначальном процессе, измерять среднее значение девиации фазы, устанавливать это среднее значение в качестве опорной величины девиации фазы быстрого режима для вычисления контрольного значения генератора, управляемого напряжением, и запоминать обнаруженные данные девиации фазы для заранее заданного периода времени после того, как быстрый режим преобразован в нормальный режим, когда быстрый режим стабилен, находить его среднее значение, а затем устанавливать это среднее значение в качестве опорной величины девиации фазы нормального режима для вычисления управляющего значения генератора, управляющего напряжением.

В устройстве управляющее средство может преобразовывать быстрый режим или нормальный режим в задержанный режим без вариаций найденного значения опорной величины девиации фазы в случае ненормальной работы, преобразовывать задержанный режим в быстрый режим, если опорный тактовый сигнал отслеживается нормальным в задержанном режиме, и вычислять управляющее значение генератора, управляемого напряжением, путем установки в качестве опорной величины девиации фазы значения, полученного путем вычитания среднего значения имеющихся данных опорной величины девиации фазы, вычисленных из управляющего значения генератора, управляемого напряжением, в задержанном режиме, из среднего значения данных девиации фазы для заранее заданного периода времени.

В устройстве управляющее средство может также вычислять управляющее значение генератора, управляемого напряжением, путем установки в качестве опорной величины девиации фазы значения, полученного путем вычитания среднего значения имеющихся данных опорной величины девиации фазы, вычисленных из управляющего значения генератора, управляемого напряжением, в нормальном режиме, из среднего значения данных девиации фазы для заранее заданного периода времени после преобразования из нормального режима в быстрый режим в случае, когда упомянутый опорный тактовый сигнал находится в ненормальном состоянии.

Далее изобретение поясняется описанием конкретного примера его выполнения и прилагаемыми чертежами на которых:

фиг. 1 изображает блок-схему традиционной системы фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации;

фиг. 2(A) - 2(C) изображают временные диаграммы фазового детектора по фиг. 1;

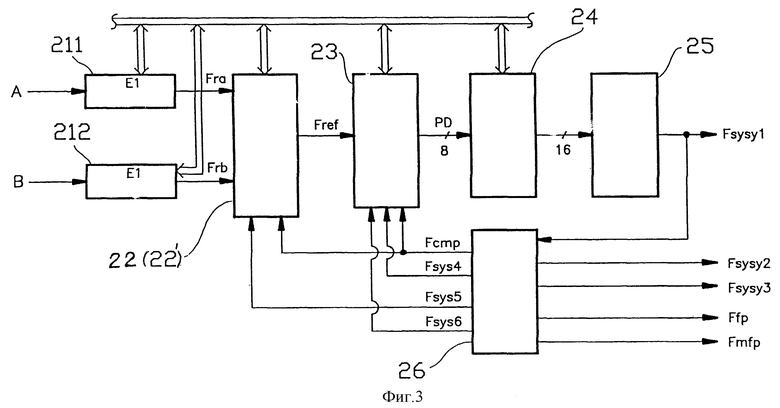

фиг. 3 изображает блок-схему устройства для управления фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации в соответствии с настоящим изобретением;

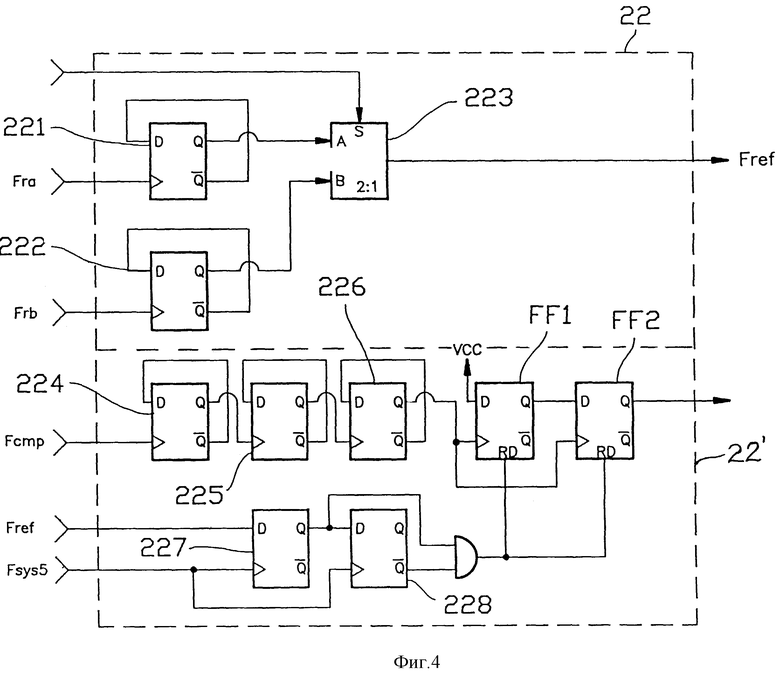

фиг. 4 - подробную блок-схему средства выбора и деления опорного тактового сигнала по фиг. 3;

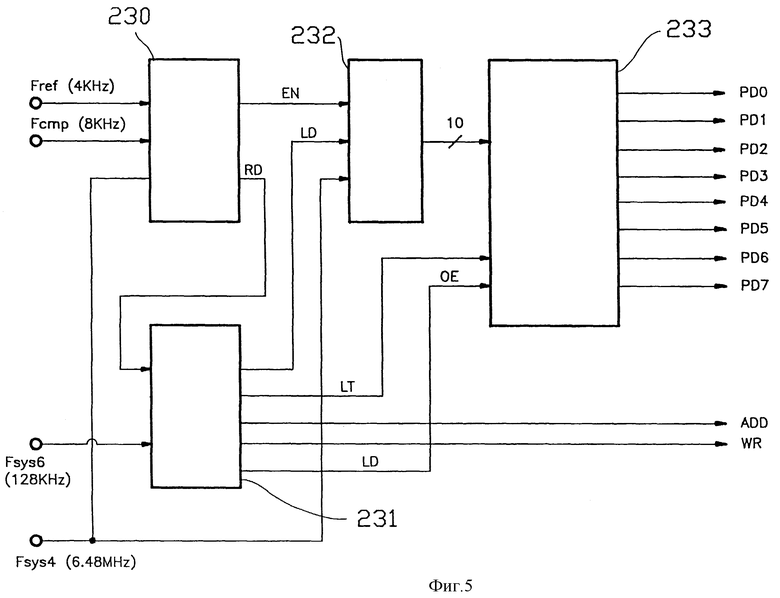

фиг. 5 - подробную блок-схему средства обнаружения и запоминания ошибки фазы по фиг. 3;

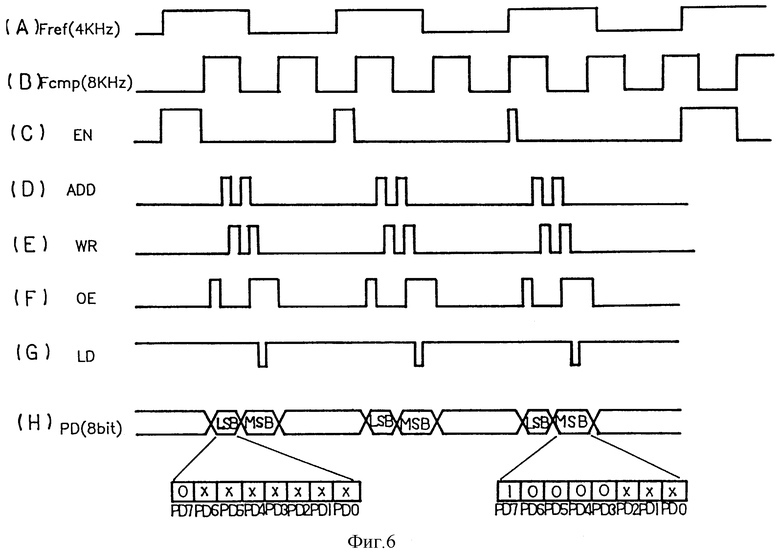

фиг. 6 (A) - 6 (Н) изображают временные диаграммы, показывающие ввод/вывод каждой части по фиг.5; и

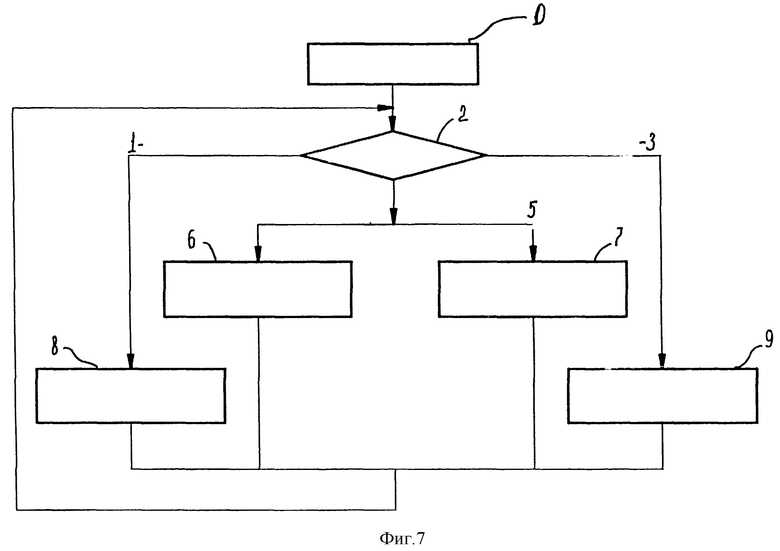

фиг. 7 изображает схему алгоритма выбора режима системы фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации в соответствии с настоящим изобретением.

Фиг. 3 изображает блок-схему предлагаемого устройства для управления системой фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации.

Это устройство включает в себя два интерфейса 211 и 212 El, которые принимают извне два опорных синхросигнала A и В для дискретизации двух опорных тактовых сигналов Fra и Frb в 8 кГц, средство 22 выбора и деления опорного тактового сигнала, которое делит каждый из двух опорных сигналов Fra и Frb интерфейсов 211 и 212 El и выбирает один из поделенных опорных тактовых сигналов Fra и Frb в 4 кГц на основании управляющего сигнала в качестве синхронизированного опорного тактового сигнала Fref, средство 22' наблюдения за потерей выбранного опорного тактового сигнала Fref с использованием тактового сигнала Fcmp сравнения в 8 кГц и системного тактового сигнала Fsys5 в 3,24 мГц, средство 23 обнаружения и запоминания ошибки фазы, которое подсчитывает данные девиации фазы между синхронизированным опорным тактовым сигналом, выбранным в средстве 22 выбора и деления опорного тактового сигнала, и поделенным системным тактовым сигналом в 8 кГц, с помощью системного тактового сигнала Fsys4 в 6,48 мГц, имеющего наиболее высокую частоту среди системных тактовых сигналов, и запоминает квантовые данные PD девиации фазы в двухпортовом ОЗУ на период 250 с, генерирующую схему, управляемую напряжением, в конкретном случае центральный процессор (далее ЦП) 24, который обрабатывает введенные средством 23 обнаружения и запоминания ошибки фазы данных девиации фазы в соответствии с управляющим алгоритмом для выработки управляющего значения кода ЦАП для синхронизации системного тактового сигнала Fsysl с выбранным синхронизированным опорным тактовым сигналом, генератор 25, управляемый напряжением (далее ГУН), который синхронизирует фазу системного тактового сигнала с выбранным синхронизированным опорным тактовым сигналом в ответ на управляющее значение из 16 разрядов из ЦП 24, которое преобразовано в аналоговый сигнал, и вырабатывает системный тактовый сигнал Psysl в 51,84 МГц, и делитель 26, который делит системный тактовый сигнал Fsysl, выработанный в ГУН 25, и вырабатывает множество тактовых сигналов, необходимых для средства 22 выбора и деления выработанного тактового сигнала и средства 23 обнаружения и запоминания.

Каждый из вышеуказанных интерфейсов Е1 состоит из линейного интерфейса, который обнаруживает потерю (LOS) сигнала, и кадрового блока, который обнаруживает выход из кадра (OOF), сигнал (AIS) тревоги и коэффициент (BER) ошибок в разрядах.

Эта информация подается от ЦП 24 и используется в качестве переключений для источника синхронизированного тактового сигнала.

Как показано на фиг.4, средство 22 выбора и деления опорного тактового сигнала делит два опорных тактовых сигнала Fra и Frb в 8 кГц на 2 двумя средствами 221 и 222 деления на 2, чтобы выработать тактовый сигнал в 4 кГц.

Затем в мультиплексоре 223 один из двух тактовых сигналов в 4 кГц выбирается как источник Fref синхронизированного тактового сигнала в соответствии с управляющим сигналом из ЦП 24.

Кроме того, тактовый сигнал Fcmp сравнения в 8 кГц делится на 8 с использованием делителей 224-226 средства 22' для выработки тактового сигнала в 1 кГц.

Из сигнала Fref в 4 кГц из системного тактового сигнала Fsys5 в 3,24 МГц получается также сигнал сброса в начальное состояние триггеров FFI и FF2 средства 22'.

Следовательно, если сигнал Fref не подан на триггер 227, состояние выхода Q триггера FF2 устанавливается на уровне "Н", тем самым обнаруживается потеря синхронизированного тактового сигнала.

Фиг. 5 показывает подробную блок-схему средства 23 обнаружения и запоминания ошибки фазы. Средство 230 выработки разрешающего сигнала счетчика вырабатывает разрешающий сигнал EN, индицирующий девиацию фазы между двумя тактовыми сигналами в ответ на синхронизированный тактовый сигнал Fref, тактовый сигнал Fcmp сравнения и системный тактовый сигнал Fsys4 в 6,48 МГц.

Средство 231 выработки управляющего сигнала выдает сигнал LD очистки, очищающий содержимое счетчика 232 девиации фазы с использованием сигнала RD считывания, выданного средством 230 выработки разрешающего сигнала счетчика, и системного тактового счетчика Fsys6 в 128 кГц.

Когда сигнал EN находится на уровне "Н", счетчик 232 ведет счет в соответствии с системным тактовым сигналом Fsys4 и очищается в соответствии с сигналом LD.

В этом случае максимальное число, которое можно подсчитать в счетчике 232, равно десяти двоичным разрядам.

Для передачи десяти разрядов данных девиации фазы на ЦП 24 эти данные девиации фазы разделяются на 3 разряда MSB и 7 разрядов LS6 и передаются на ЦП 24 в порядке, показанном на фиг. 6(Н).

Для этого случая, когда PD7 равно "0", остальные PD6 - PD0 соответствуют младшим 7 разрядам данных девиации фазы, когда PD7 равно "I", PD2 - PD0 соответствуют старшим 3 разрядам. Следовательно, ЦП 24 устанавливает 7 разрядов PD6 - PD0 и переупорядочивает данные девиации фазы.

На фиг. 5 LD обозначает сигнал фиксации, ADD - импульс счетчика приращения адреса двухпортового ОЗУ, a WR - это импульс записи двухпортового ОЗУ.

Далее со ссылками на фиг. 3-6 будет описан принцип работы предлагаемого устройства для управления системой фазовой автоподстройки частоты с цифровой обработкой для сетевой синхронизации.

Вначале, если два опорных синхросигнала введены извне, интерфейсы 211 и 212 El дискретизируют опорные тактовые сигналы Fra и Frb и посылают их на средство 22 выбора и деления опорных тактовых сигналов. Средство 22 выбора и деления опорных тактовых сигналов выбирает один из этих опорных тактовых сигналов, чтобы облегчить обнаружение девиации фазы и отследить потерю опорного тактового сигнала.

В средстве 23 обнаружения и запоминания ошибки фазы окончательно выбранный опорный тактовый сигнал Fref в 4 кГц сравнивается с системным тактовым сигналом в 8 кГц, поделенным в делителе 26. Сравниваемая девиация фазы подсчитывается системным тактовым сигналом Fsys4 в 6,48 МГц, имеющим наиболее высокую частоту среди системных тактовых сигналов, и вводится в ЦП 24 как данные PD девиации фазы.

Соответственно, ЦП 24 вычисляет управляющее значение DACW из 16 разрядов для управления ГУН 25 с использованием введенных данных PD девиации фазы.

То есть на начальной стадии ЦП 24 устанавливает значения 8000 Гц в соответствии с первоначальным значением центральной частоты в ГУН 25 и устанавливает текущий режим как режим свободного хода.

Если LOS, AIS, BER и OOF опорных тактовых сигналов A и В не обнаружены во время исполнения режима свободного хода, режим свободнго хода преобразуется в быстрый режим или нормальный режим. Если обнаружен любой из LOS, AIS, BER и OOF всякий раз, когда дискретизованная девиация фазы считана в течение 4 мс, нормальный режим преобразуется в задержанный режим.

Описание каждого режима таково.

ЦП 24 входит в режим свободного хода в нормальном состоянии, а затем преобразуется в быстрый режим. ЦП 24 запоминает данные PD девиации фазы на заранее заданный промежуток времени Tsf на начальном уровне быстрого режима и вычисляет среднее значение.

Затем среднее значение квантуется и к квантованному среднему значению добавляется смещение в 0,5000 для установки этого значения как опорной девиации фазы REF - PDW быстрого режима.

В течение быстрого режима ЦП 24 вычисляет и управляет управляющим значением DACW в ГУН 25 для сведения вышеупомянутых данных PD девиации фазы в значение REF - PDW опорной величины девиации фазы и, когда быстрый режим станет стабильным, режим преобразуется в нормальный режим.

Когда все готово к вводу нормального режима, ЦП 24 запоминает вышеупомянутые данные PD девиации фазы на заранее заданный промежуток времени Tsn и вычисляет среднее значение. Затем среднее значение квантуется и к квантованному среднему значению добавляется смещение в 0,5000 для установки этого значения в качестве значения опорной величины девиации фазы нормального режима. ЦП 24 вычисляет и управляет управляющим значением ГУН 25 для сведения вышеупомянутых данных PD девиации фазы в значение опорной величины девиации фазы.

Вышеприведенное описание относиться к процессу определения значения девиации фазы нормальной работы, а последующее описание относится к процессу определения значения опорной величины девиации фазы ненормальной работы.

В ненормальной работе, если быстрый режим или нормальный режим преобразуется в задержанный режим, установка значения девиации фазы не меняется. Значение опорной величины девиации фазы переустанавливается во время преобразования из нормального режима в быстрый режим, когда источник тактового сигнала, который выбран как источник синхронизированного тактового сигнала, меняется из-за ненормальности одного из опорных синхросигналов A и В.

Затем следует операция получения среднего значения девиации фазы, запомненного на заранее заданный период времени Tsf. Среднее значение квантуется и к квантованному среднему значению прибавляется значение сдвига в 0,5000, просуммированный результат устанавливается как значение опорной величины девиации фазы.

Если оба из двух опорных синхросигналов ненормальны, режим преобразуется в задержанный режим.

Когда любой из опорных синхросигналов нормально отслеживается в задержанном режиме, режим преобразуется в быстрый режим. В этом случае значение опорной величины девиации фазы устанавливается как квантованное значение, полученное путем вычитания среднего значения имеющихся данных девиации фазы, которое подсчитывается из управляющего значения ГУН 25 в задержанном режиме, из среднего значения данных девиации фазы, которое вычислено для заранее заданного периода времени. Далее к квантованному значению прибавляется значение сдвига в 0,5000.

В соответствии с настоящим изобретением, поскольку контрольный период в быстром режиме и в нормальном режиме различен, время вхождения в полосу затягивания частоты может быть уменьшено. Кроме того, прерывность фазы может быть предотвращена путем переустановки данных опорной величины девиации фазы, когда один рабочий режим преобразуется в другой. Настоящее изобретение также обеспечивает преимущества вследствие предотвращения резкой нестабильности фазы или частоты, которые могут появиться во время преобразования режима, и поддержания стабильного системного тактового сигнала, поскольку опорная величина девиации фазы может быть точно установлена даже в том случае, когда источник тактового синхросигнала коммутируется или находится в ненормальном состоянии.

Более того, при установке данных опорной величины девиации фазы, после того, как к квантованному среднему значению прибавлено значение сдвига в 0,5000, данные PD девиации фазы между опорным тактовым сигналом, полученным в состоянии синхронизации, и тактовым сигналом сравнения всегда включает в себя +/- сдвиг в качестве значения опорной величины девиации фазы, так что предлагаемое устройство работает так, чтобы компенсировать девиацию фазы.

Следовательно, поскольку девиация фазы из-за квантованной ошибки, появившейся путем обнаружения девиации фазы, уменьшена, может быть уменьшена максимальная ошибка временного интервала.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ПОДАВЛЕНИЯ ДЖИТТЕРА | 1995 |

|

RU2110158C1 |

| ВИРТУАЛЬНАЯ СОТОВАЯ СЕТЬ И СПОСОБ СВЯЗИ, ИСПОЛЬЗУЕМЫЙ В ЭТОЙ ВИРТУАЛЬНОЙ СОТОВОЙ СЕТИ | 1994 |

|

RU2123237C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОГО ПРИЕМНИКА | 1996 |

|

RU2138907C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| УСТРОЙСТВО И СПОСОБ СЛЕЖЕНИЯ ЗА РАДИОЧАСТОТОЙ И ЕЕ ЗАХВАТА | 2003 |

|

RU2321955C2 |

| СИНТЕЗАТОР ДРОБНЫХ КОГЕРЕНТНЫХ ЧАСТОТ С ФАЗОВОЙ СИНХРОНИЗАЦИЕЙ | 1998 |

|

RU2208904C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ВРЕМЕНИ, ЭЛЕКТРОННОЕ УСТРОЙСТВО, СИСТЕМА СИНХРОНИЗАЦИИ ПО ВРЕМЕНИ И СПОСОБ СИНХРОНИЗАЦИИ ПО ВРЕМЕНИ | 2019 |

|

RU2758838C1 |

| СПОСОБ КОМПЕНСАЦИИ СКАЧКОВ ОПОРНОГО СИГНАЛА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2006 |

|

RU2321167C2 |

| ОБНАРУЖЕНИЕ ЧАСТОТЫ | 1996 |

|

RU2156497C2 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

Изобретение раскрывает управляющий алгоритм системы фазовой автоподстройки частоты с цифровой обработкой (ЦФАПЧ) для сетевой синхронизации для обеспечения технического результата, заключающегося в предотвращении фазового скачка, вырабатываемого во время изменения рабочего режима. Этот алгоритм предусматривает в случае, если и один и другой опорные тактовые сигналы аномальны, преобразование быстрого или нормального режима в режим удержания, без изменения заранее заданной опорной величины девиации фазы, при восстановлении нормального отслеживания тактового сигнала в режиме удержания, в качестве опорной величины девиации фазы используют значение, полученное путем вычитания среднего значения данных девиации фазы в режиме удержания из среднего значения данных девиации фазы для заранее заданного промежутка времени после преобразования из режима удержания в быстрый режим. 2 с. и 5 з.п. ф-лы, 7 ил.

| US 4305045, 08.12.1981 | |||

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1338071A1 |

| US 4498059, 05.02.1985 | |||

| US 4600896, 15.06.1986 | |||

| US 4752748, 24.01.1988. | |||

Авторы

Даты

2000-08-20—Публикация

1995-09-14—Подача