Изобретение относится к вычислительной технике и может быть использовано для создания высокопроизводительных и отказоустойчивых однопроцессорных, многопроцессорных и многомашинных электронных, оптоэлектронных и оптических вычислительных комплексов и систем.

Известно устройство для обмена информацией с общей шиной [1], содержащее центральный процессор, оперативную память, два периферийных устройства для обмена информацией с общей шиной, линию передачи адреса, линию передачи сигналов управления и синхронизации, линию передачи данных внешней магистрали, линию запросов. Основным недостатком данной структуры является то, что в каждый момент через общую шину может происходить обмен данных только между одной парой присоединенных к ней модулей, которые разделяют во времени один общий интерфейс, что снижает производительность электронных вычислительных машин, использующих такой интерфейс.

Наиболее близкой к предлагаемому является система ввода-вывода с процессорами ввода-вывода [2], содержащая блоки памяти, интерфейс памяти, процессорный блок, процессорный интерфейс, процессорные блоки ввода-вывода, интерфейс ввода-вывода, узлы управления селекторными и мультиплексными блоками, оптические интерфейсы периферии, селекторные и мультиплексные периферийные блоки. Основными недостатками данной структуры является то, что в каждый момент через каждый интерфейс системы может происходить обмен данных только между одной парой присоединенных к ней модулей, которые разделяют во времени этот интерфейс, что снижает производительность электронных вычислительных машин, использующих такую структуру.

Техническим результатом является повышение производительности, помехозащищенности и надежности вычислительных машин, использующих систему раздельных интерфейсов.

Это достигается тем, что в оптоэлектронную вычислительную систему, содержащую блоки памяти, интерфейс памяти, процессорный блок, процессорный интерфейс, процессорные блоки ввода-вывода, интерфейс ввода-вывода, узлы управления селекторными и мультиплексными блоками, оптические интерфейсы периферии, селекторные и мультиплексные периферийные блоки, введены интерфейс памяти, процессорный интерфейс, интерфейсы ввода-вывода и интерфейсы периферии имеют оптическое выполнение, а в систему введены дополнительные процессорные блоки и процессорные блоки ввода-вывода, узлы формирования выходных оптических сигналов из блоков памяти, узлы ввода оптических сигналов из блоков памяти, узлы выборки оптических сигналов для блоков памяти, узлы формирования входных сигналов для блоков памяти, первые и вторые узлы выборки оптических сигналов для процессорных блоков, первые и вторые узлы формирования входных сигналов для процессорных блоков, первые и вторые узлы формирования выходных оптических сигналов из процессорных блоков, первые и вторые узлы ввода оптических сигналов из процессорных блоков, первые, вторые и третьи узлы выборки оптических сигналов для процессорных блоков, первые, вторые и третьи узлы формирования выходных оптических сигналов из процессорных блоков ввода-вывода, первые, вторые и третьи узлы ввода оптических сигналов из процессорных блоков ввода-вывода, первые, вторые и третьи узлы выборки оптических сигналов для процессорных блоков ввода-вывода, первые, вторые и третьи узлы формирования входных сигналов для процессорных блоков ввода-вывода, первые и вторые узлы выборки оптических сигналов для селекторных узлов управления, узлы формирования входных сигналов для селекторных узлов управления, узлы формирования выходных оптических сигналов из селекторных узлов управления, узлы ввода оптических сигналов из селекторных узлов управления, первые и вторые узлы выборки оптических сигналов для мультиплексных узлов управления, первые и вторые узлы формирования входных сигналов для мультиплексных узлов управления, первые и вторые узлы формирования выходных оптических сигналов из мультиплексных узлов управления, первые и вторые узлы ввода оптических сигналов из мультиплексных узлов управления, узлы выборки оптических сигналов для мультиплексных периферийных блоков, узлы формирования входных сигналов для мультиплексных периферийных блоков, узлы формирования выходных оптических сигналов из мультиплексных периферийных блоков, узлы ввода оптических сигналов из мультиплексных периферийных блоков, причем выход каждого блока памяти и первый выход каждого процессорного блока через соответствующие последовательно расположенные и оптически связанные одноименные узел формирования выходных оптических сигналов и узел ввода оптических сигналов для блока памяти и первый узел формирования выходных оптических сигналов и первый узел ввода оптических сигналов из процессорного блока оптически связан с соответствующим входом оптического интерфейса памяти, соответствующие выходы которого через соответствующие последовательно расположенные и оптически связанные одноименные узлы выборки оптических сигналов и узлы формирования входных сигналов связаны с входом соответствующего блока памяти или процессорного блока, второй выход каждого процессорного блока через последовательно расположенные и оптически связанные соответствующие второй узел формирования выходных оптических сигналов и второй узел ввода оптических сигналов оптически связан с соответствующим входом процессорного оптического интерфейса, соответствующий выход которого через соответствующие последовательно расположенные и оптически связанные второй узел выборки оптических сигналов и второй узел формирования входных сигналов связан со вторым входом одноименного процессорного блока, первый выход каждого процессорного блока ввода-вывода через последовательно расположенные и оптически связанные соответствующие первый узел формирования выходных оптических сигналов и первый узел ввода оптических сигналов оптически связан с соответствующим входом процессорного оптического интерфейса, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие первый узел выборки оптических сигналов и первый узел формирования входных сигналов связан с первым входом одноименного процессорного блока ввода-вывода, второй выход каждого процессорного блока ввода-вывода через последовательно расположенные и оптически связанные соответствующие второй узел формирования выходных оптических сигналов и второй узел ввода оптических сигналов оптически связан с соответствующим входом оптического интерфейса ввода-вывода, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие второй узел выборки оптических сигналов и второй узел формирования входных сигналов связан со вторым входом одноименного процессорного блока ввода-вывода, третий выход каждого процессорного блока ввода-вывода через последовательно расположенные и оптически связанные соответствующие третий узел формирования выходных оптических сигналов и третий узел ввода оптических сигналов оптически связан с оптическим интерфейсом памяти, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие третий узел выборки оптических сигналов и третий узел формирования входных сигналов связан с третьим входом одноименного процессорного блока ввода-вывода, каждый селекторный периферийный блок связан с соответствующим селекторным узлом управления, выход которого через последовательно расположенные и оптически связанные соответствующие узел формирования выходных оптических сигналов и узел ввода оптических сигналов оптически связан с соответствующим входом соответствующего оптического интерфейса ввода-вывода, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие узел выборки оптических сигналов и узел формирования входных сигналов связан со входом одноименного селекторного узла управления, первый выход каждого мультиплексного узла управления через последовательно расположенные и оптически связанные соответствующие первый узел формирования выходных оптических сигналов и первый узел ввода оптических сигналов оптически связан с одноименным входом соответствующего оптического интерфейса ввода-вывода, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие первый узел выборки оптических сигналов и первый узел формирования входных сигналов связан с первым входом одноименного мультиплексного узла управления, второй выход каждого мультиплексного узла управления через последовательно расположенные и оптически связанные соответствующие второй узел формирования выходных оптических сигналов и второй узел ввода оптических сигналов оптически связан с одноименным входом соответствующего оптического интерфейса периферии, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие второй узел выборки оптических сигналов и второй узел формирования входных сигналов связан с одноименным входом соответствующего мультиплексного узла управления, выход каждого периферийного блока через последовательно расположенные и оптически связанные соответствующие узел формирования оптических сигналов и узел ввода оптических сигналов оптически связан с одноименным входом соответствующего оптического интерфейса периферии, соответствующий выход которого через последовательно расположенные и оптически связанные соответствующие узел выборки оптических сигналов и узел формирования входных сигналов связан со входом соответствующего периферийного блока.

А также тем, что каждый его оптический интерфейс содержит только одну оптическую магистраль, выполненную в виде световода.

А также тем, что разные его оптические интерфейсы содержат одинаковое число K (где K = 1, 2, 3...) оптических магистралей, причем каждая из них выполнена в виде отдельного световода.

А также тем, что разные его оптические интерфейсы содержат неодинаковое число оптических магистралей, причем каждая из них выполнена в виде отдельного световода.

Данная совокупность существенных признаков и связей между ними позволяет получить устройство, обладающее более чем в 1000 раз большей производительностью, помехозащищенностью и надежностью.

Сущность изобретения заключается в том, что на основе использования оптических методов передачи сигналов и применения оригинальных схем организации оптического ввода/вывода сигналов как из электронных так и из оптических вычислительных блоков и структуры раздельных интерфейсов, использующей в качестве передающей среды свободное пространство и/или световоды (волоконные и/или интегральные), создана структура оптоэлектронной вычислительной системы с раздельными оптическими интерфейсами, позволяющей вести по ним обмен сигналами одновременно между парами, группами или всеми блоками вычислительной машины, комплекса или системы, а также сократить число магистралей в интерфейсах вплоть до одной оптической, за счет чего и достигаются повышение производительности, помехозащищенности и надежности вычислительных систем.

Таким образом, предложенная вычислительная система обладает свойствами, не присущими известным устройствам. Это объясняется новой совокупностью существенных признаков и новыми связями, изложенными выше.

Сравнение предлагаемого устройства с известными свидетельствует о соответствии его критерию "новизна", а отсутствие в аналогах отличительных признаков предлагаемого устройства - о соответствии критерию "изобретательский уровень".

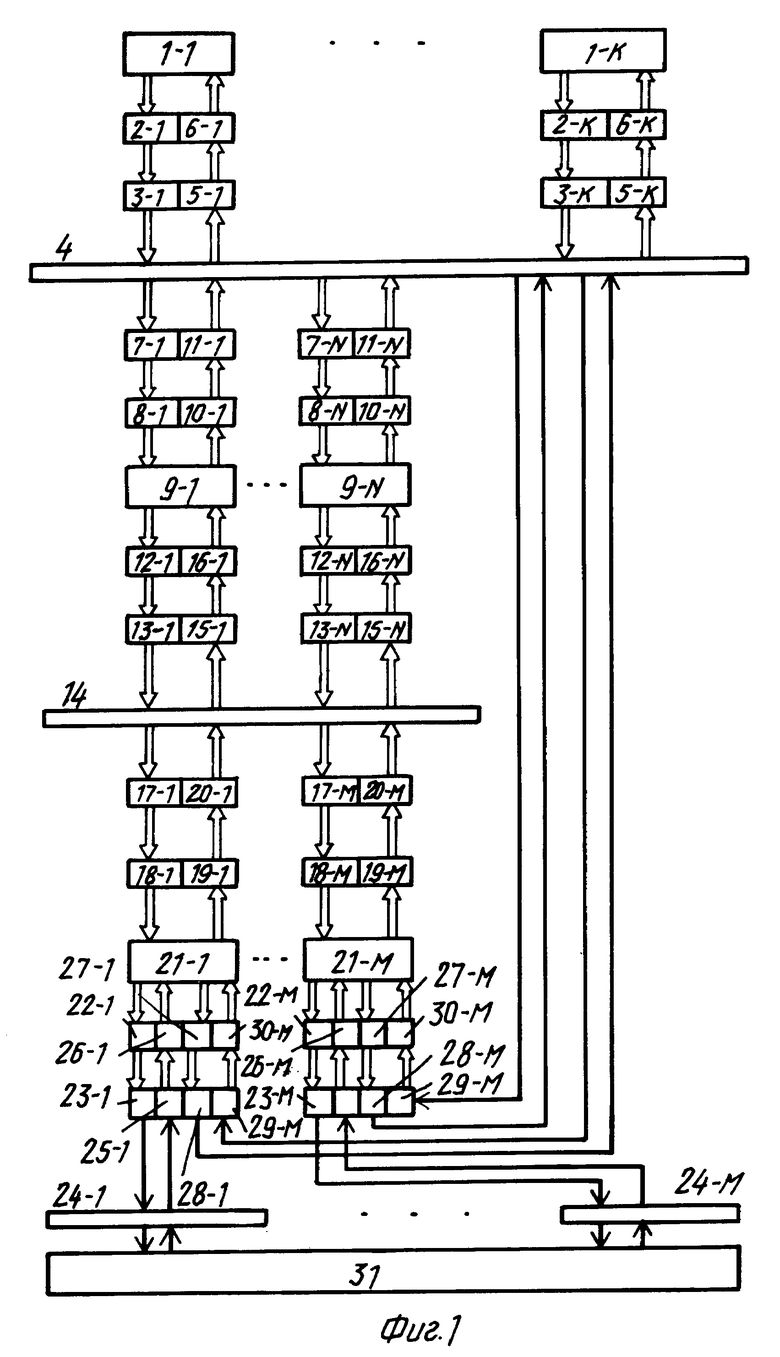

На фиг. 1 приведена функциональная схема оптоэлектронной вычислительной системы; на фиг. 2 - функциональная схема блока периферии.

Оптоэлектронная вычислительная система содержит блоки памяти 1-1...1-K, узлы 2-1. . .2-K формирования выходных оптических сигналов из блоков памяти 1-1. ..1-K, узлы 3-1...3-K ввода оптических сигналов из блоков памяти 1-1... 1-K, оптический интерфейс памяти 4, узлы 5-1...5-K выборки оптических сигналов для блоков памяти 1-1...1-K, узлы 6-1...6-K формирования входных сигналов в блоки памяти 1-1...1-K, узлы 7-1...7-N выборки оптических сигналов для процессорных блоков 9-1...9-N, узлы 8-1...8-N формирования входных сигналов для процессорных блоков 9-1...9-N, узлы 10-1...10-N формирования выходных оптических сигналов из процессорных блоков 9-1...9-N, узлы 11-1...11-N ввода оптических сигналов из процессорных блоков 9-1...9-N, узлы 12-1...12-N формирования выходных оптических сигналов процессорных блоков 9-1...9-N, узлы 13-1. ..13-N ввода оптических сигналов из процессорных блоков 9-1...9-N, процессорный оптический интерфейс 14, узлы 15-1...15-N выборки оптических сигналов для процессорных блоков 9-1...9-N, узлы 16-1...16-N формирования входных сигналов в процессорные блоки 9-1...9-N, узлы 17-1...17-М выборки оптических сигналов для процессорных блоков ввода-вывода 21-1...21-М, узлы 18-1. ..18-М формирования входных сигналов в процессорные блоки ввода-вывода 21-1. . .21-M, узлы 19-1...19-М формирования выходных оптических сигналов из процессорных блоков ввода-вывода 21-1...21-М, узлы 20-1...20-М ввода оптических сигналов из процессорных блоков ввода-вывода 21-1...21-М, узлы 22-1.. . 22-М формирования выходных оптических сигналов процессорных блоков ввода-вывода 21-1. . .21-М, узлы 23-1...23-М ввода оптических сигналов из процессорных блоков ввода-вывода 21-1...21 -М, оптические интерфейсы ввода-вывода 24-1. . .24-М, узлы 25-1...25-М выборки оптических сигналов для процессорных блоков ввода-вывода 21-1...21-М, узлы 26-1...26-М формирования входных сигналов для процессорных блоков ввода-вывода 21-1...21-М, узлы 27-1...27-М формирования выходных оптических сигналов из процессорных блоков ввода-вывода 21-1...21-М, узлы 28-1...28-M ввода оптических сигналов из процессорных блоков ввода-вывода 21-1....21-М, узлы 29- 1...29-М выборки оптических сигналов для процессорных блоков ввода-вывода 21-1...21-М, узлы 30-1...30-М формирования входных сигналов в процессорные блоки ввода-вывода 21-1...21-М, узлы 32-1...32-R выборки оптических сигналов для селекторных узлов управления 34-1...34-R, узлы 33-1...33-R формирования входных сигналов для селекторных узлов управления 34-1. ..34-R, селекторные периферийные блоки 35-1... 35-R, узлы 36-1...36-R формирования выходных оптических сигналов из селекторных узлов управления 34-1. . . 34-R, узлы 37-1...37-R ввода оптических сигналов из селекторных узлов управления 34-1...34-R, узлы 38-1...38-S выборки оптических сигналов для мультиплексных узлов управления 40-1...40-S, узлы 41-1...41-S формирования выходных оптических сигналов из мультиплексных узлов управления 40-1...40-S, узлы 42-1...42-S ввода оптических сигналов из мультиплексных узлов управления, узлы 43-1...43-S формирования выходных оптических сигналов из мультиплексных узлов управления 40-1...40-S, узлы 44-1. . .44-S ввода оптических сигналов из мультиплексных узлов управления 40-1... 40-S, узлы 45-1...45-S выборки оптических сигналов для мультиплексных узлов управления 40-1. ..40-S, узлы 46-1...46-S формирования входных сигналов для мультиплексных узлов управления, оптические интерфейсы периферии 47-1... 47-P, узлы 48-1. . .48-L выборки оптических сигналов для селекторных узлов управления 50-1. ..50-L, узлы 49-1...49-L формирования входных сигналов для селекторных узлов управления 50-1...50-L, периферийные блоки 51-1...51-L, узлы 52-1...52-L формирования выходных оптических сигналов селекторных узлов управления 50-1...50-L, узлы 53-1...53-М ввода оптических сигналов из селекторных узлов управления, узлы 54-1...54-V выборки оптических сигналов для мультиплексных узлов управления 56-1...56-V, узлы 55-1...55-V формирования входных сигналов для мультиплексных узлов управления 56-1...56-V, узлы 57-1. . . . 57-V формирования выходных оптических сигналов из мультиплексных узлов управления 56-1...56-V, узлы 58-1...58-V ввода оптических сигналов из мультиплексных узлов управления 56-1...56-V, узлы 58-1...58-V ввода оптических сигналов из мультиплексных узлов управления 56-1...56-V, узлы 59-1...59-V формирования выходных оптических сигналов из мультиплексных узлов управления 56-1. . . 56-V, узлы 60-1...60-V ввода оптических сигналов из мультиплексных узлов управления 56-1...56-V, узлы 61-1...61-V выборки оптических сигналов для мультиплексных узлов управления 56-1...56-V, узлы 62-1...62-V формирования входных сигналов для мультиплексных узлов управления 56-1...56-V, узлы 63-1...63-F выборки оптических сигналов для мультиплексных периферийных блоков 65-1. . . 65-F, узлы 64-1...64-F формирования входных сигналов мультиплексных периферийных блоков 65-1...65-F, узлы 66-1...66-F формирования выходных оптических сигналов из мультиплексных периферийных блоков 65-1...65-F, узлы 67-1. . .67-F ввода оптических сигналов из мультиплексных периферийных блоков 65-1...65-V, узлы 68-1...68-G выборки входных оптических сигналов для мультиплексных периферийных блоков 70-1...70-G, узлы 69-1...69-G формирования входных сигналов для мультиплексных периферийных блоков 70-1...70-G, узды 71-1...71-G формирования выходных оптических сигналов из мультиплексных периферийных блоков 70-1...70-G, узлы 72-1...72-G ввода оптических сигналов из мультиплексных периферийных блоков 70-1...70-G.

Блоки памяти 1-1...1-K могут состоять из групп, имеющих различное функциональное назначение, например групп оперативных памятей, постоянных памятей, массовых памятей, ассоциативных памятей, стековых памятей, буферных памятей и т.д., которые могут иметь различное физическое исполнение, например электронное, магнитное, оптоэлектронное, оптическое.

Узлы 2-1...2-K формирования выходных оптических сигналов из блоков памятей 1-1. ..1-K служат для преобразования, например, входных электронных или оптических сигналов в оптические. В случае входных электронных сигналов эти узлы могут быть выполнены, например, в виде линеек или матриц лазерных диодов, каждый из которых излучает, например, на своей длине волны λi, где i = 1, 2, 3,...p, при этом p - максимальное число сигналов, передаваемых параллельным кодом, а при передаче сигналов последовательно-параллельным кодом, последовательные оптические сигналы передаются, например, каждым лазерным диодом на различных длинах волн λj (где j = 1, 2, 3,...s, s - максимальное число сигналов, передаваемых последовательным кодом), отличных от длин волн оптических сигналов, которые передаются параллельным кодом. Сигналы каждого блока памяти могут преобразовываться и передаваться в виде оптических сигналов и на одной и той же длине волны, В случае, если на входы узлов поступают оптические сигналы, то на их входах дополнительно могут располагаться, напрмер, линейки фотоприемников или непосредственно поступать на выход.

Узлы 3-1. . . 3-K ввода оптических сигналов из блоков памятей 1-1...1-K предназначены для ввода оптических сигналов в оптический интерфейс памяти 4 и могут быть выполнены, например, на основе световодной (волоконной и/или интегральной) оптики с использованием дифракционных решеток или спектральных фильтров.

Оптический интерфейс памяти 4 служит для передачи оптических сигналов между различными блоками оптоэлектронной вычислительной системы и может содержать одну единственную или несколько оптических магистралей, выполненных в виде одного или нескольких световодов (волоконных и/или интегральных) или свободного пространства.

Узлы 5-1. ..5-K выборки оптических сигналов предназначены для выделения определенной группы спектральных оптических сигналов из множества групп спектральных оптических сигналов, распространяющихся по оптическому интерфейсу памяти 4 и соответствующих различным блокам, подключенным к этому интерфейсу. Эти узлы могут быть выполнены, например, на основе оптических конверторов или оптических фильтров.

Узлы 6-1. . . 6-K формирования входных сигналов для блоков памяти предназначены для ввода оптических сигналов в блоки памяти в виде электрических или оптических сигналов в зависимости от физического выполнения блока памяти и могут быть выполнены, например, на основе световодной (волоконной и/или интегральной) оптики с использованием дифракционных решеток или спектральных фильтров и линеек фотоприемников при электрическом выходе, или линеек лазерных диодов при оптическом выходе.

Процессорные блоки 9-1. . .1-N могут состоять, например, из групп процессоров различного функционального назначения, например центральных процессоров, скалярных процессоров, векторно-конвейерных процессоров, сервисных и т.д., которые могут иметь, например, различное физическое исполнение, например электронное, оптоэлектронное или оптическое.

Процессорный оптический интерфейс 14, оптические интерфейсы ввода-вывода 24-1. ..24-M и оптические интерфейсы периферии могут иметь то же выполнение, что и оптический интерфейс памяти.

Процессорные блоки ввода-вывода 21-1...21-M могут состоять из различных групп, которые отличаются как своими функциями, так и физическим исполнением, например, могут быть электронными, оптоэлектронными или оптическими.

Селекторные 34-1...34-R, 50-1...50-L и мультиплексные 40-1...40-S, 56-1. . .56-V узлы управления служат для управления соответствующими периферийными блоками и могут иметь электронное, магнитное, оптоэлектронное или оптическое выполнение.

Селекторные 35-1...35-R, 51-1...51-L и мультиплексные 65-1...65-F, 70-1. . .70-G периферийные блоки предназначены соответственно для монопольного или мультиплексного режима работы и могут состоять из групп периферийных устройств, имеющих различное функциональное назначение, например дисплеев, печатающих устройств, различных устройств отображения и т.д., которые могут быть электронными, оптоэлектронными и/или оптическими.

Остальные узлы оптоэлектронной вычислительной системы могут иметь то же назначение и выполнение, что и аналогичные узлы 2-1...2-K, 3-1...3-K, 5-1... 5-K, 6-1...6-K.

Оптоэлектронная вычислительная система работает следующим образом.

Каждый из передающих информацию активных блоков 1, 9, 21, 35, 51, 65, 70 передает ее, например, в виде электронных или оптических сигналов, которые через соответствующие узлы формирования выходных оптических сигналов и узлы ввода оптических сигналов 2, 3, 10, 11, 12, 13, 19, 20, 22, 23, 29, 30, 34, 36, 37, 50, 52, 53, 66, 67, 71, 72 поступают в соответствующий оптический интерфейс 4, 14, 24, 47, например, в виде спектральных оптических сигналов со спектральным уплотнением.

Спектральные оптические сигналы от всех передающих блоков 1, 9, 21, 35, 51, 65, 70 одновременно со спектральным уплотнением распространяются по соответствующим оптическим интерфейсам 4, 14, 24, 47 и поступают на входы всех узлов выборки оптических сигналов 5, 7, 15, 17, 25, 29, 32, 38, 48, 54, 63, 68, которые настраиваются управляющими сигналами на пропускание групп спектральных оптических сигналов, передаваемых от соответствующих передающих информацию блоков, с которыми они производят сеанс связи. Затем выделенные этими узлами 5, 7, 15, 17, 25, 29, 32, 38, 48, 54, 63, 68 спектральные оптические сигналы через соответствующие узлы 6, 8, 16, 18, 26, 30, 33, 34, 49, 50, 39, 40, 43, 44, 64, 65, 69 формирования входных сигналов поступают на входы соответствующих приемных блоков 1, 9, 21, 35, 51, 65, 70.

Следует отметить что передача информации по всем оптическим интерфейсам вычислительной системы может производится сигналами как только со спектральным уплотнением, так и одновременно со спектральным и временным уплотнением как параллельным, так и параллельно-последовательным или последовательным кодом, при этом сеансы связи блоков системы могут осуществляться как одновременно между всеми блоками системы так и между отдельными группами с разделением во времени.

Использование изобретения позволит реализовать оптическими методами связь между блоками оптоэлектронной вычислительной системы, увеличив более чем в 1000 раз ее производительность, помехозащищенность и надежность. Такие оптоэлектронные вычислительные системы могут широко применяться в разнообразных радиолокационных, радионавигационных системах как наземного, так и бортового базирования.

Литература

1. Авторское свидетельство СССР N 1322301, МКИ G 06 F 13/36, 07.07.87.

2. Каган Б.М. Электронные вычислительные машины и системы. М.: Энергоатомиздат, 1991, с. 352.

Изобретение относится к вычислительной технике и может быть использовано в оптоэлектронных вычислительных комплексах. Техническим результатом является повышение помехозащищенности и надежности. Система содержит блоки памяти, узлы формирования выходных оптических сигналов и ввода оптических сигналов из блоков памяти, узлы выборки оптических сигналов и формирования входных оптических сигналов в блоки памяти, узлы выборки и формирования входных сигналов для процессорных блоков, узлы ввода и формирования выходных оптических сигналов из процессорных блоков и селекторные блоки. 3 з.п.ф-лы, 2 ил.

| КАГАН Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиздат, 1991, с.352 | |||

| ОПТИЧЕСКИЙ ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ ДЕЛИТЕЛЬ | 1997 |

|

RU2115950C1 |

| ОПТОЭЛЕКТРОННЫЙ ЛОГИЧЕСКИЙ БЛОК | 1986 |

|

SU1396827A1 |

| US 05526298 A, 06.11.1996 | |||

| JP 10320896 A, 04.12.1998 | |||

| JP 6030245 A, 04.02.1994 | |||

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

Авторы

Даты

2000-08-27—Публикация

1999-08-05—Подача