13

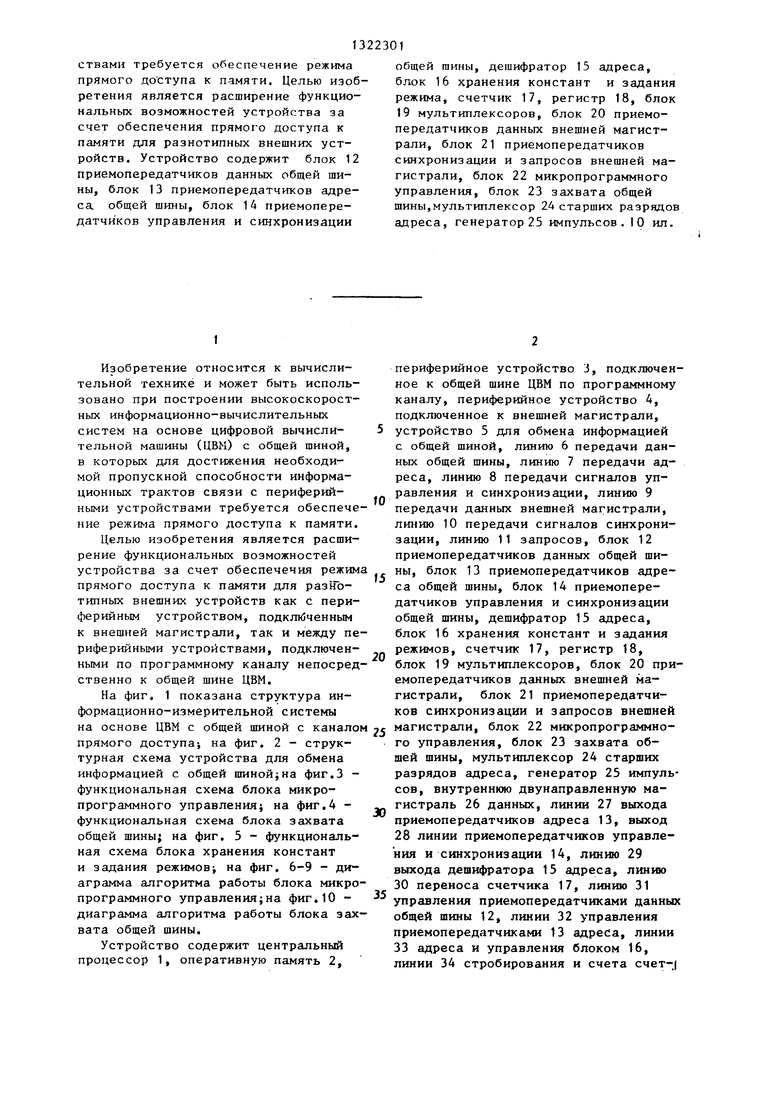

ствамн требуется обеспечение режима прямого доступа к памяти. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения прямого доступа к памяти для разнотипных внешних устройств. Устройство содержит блок 12 приемопередатчиков данных общей ши

ны, блок 13 приемопередатчиков адреса общей шины, блок 1А приемопередатчиков управления и синхронизации

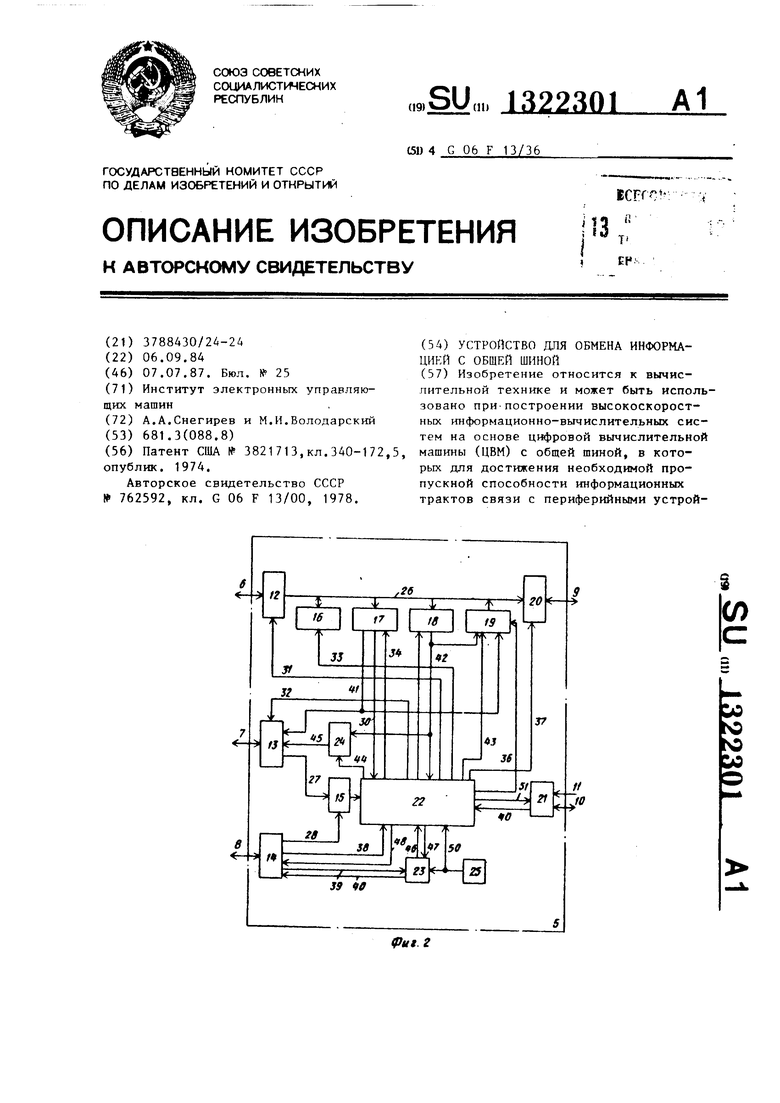

Изобретение относится к вычислительной технике и может быть использовано при построении высокоскоростных информационно-вычислительных систем на основе цифровой вычислительной машины (ЦВМ) с общей шиной, в которых для достижения необходимой пропускной способности информационных трактов связи с периферийными устройствами требуется обеспечение режима прямого доступа к памяти.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режим прямого доступа к памяти для разнотипных внешних устройств как с периферийным устройством, подклклченным к внешней магистрали, так и между периферийными устройствами, подключенными по программному каналу непосредственно к общей шине ЦВМ.

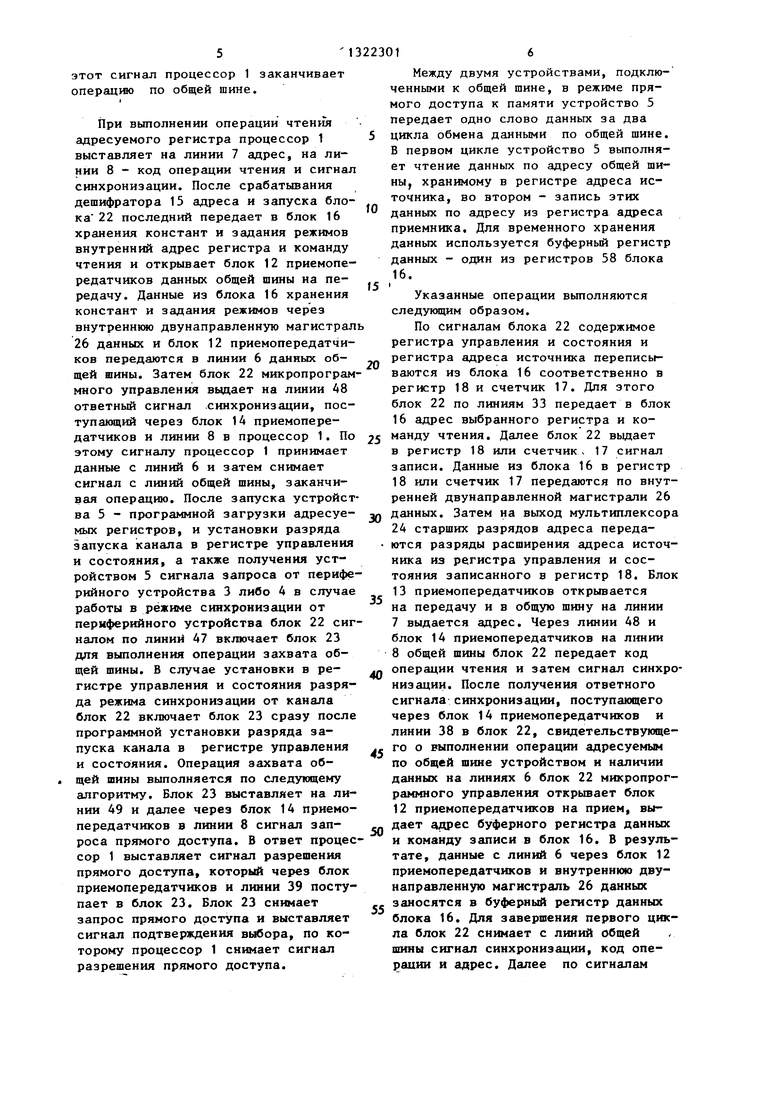

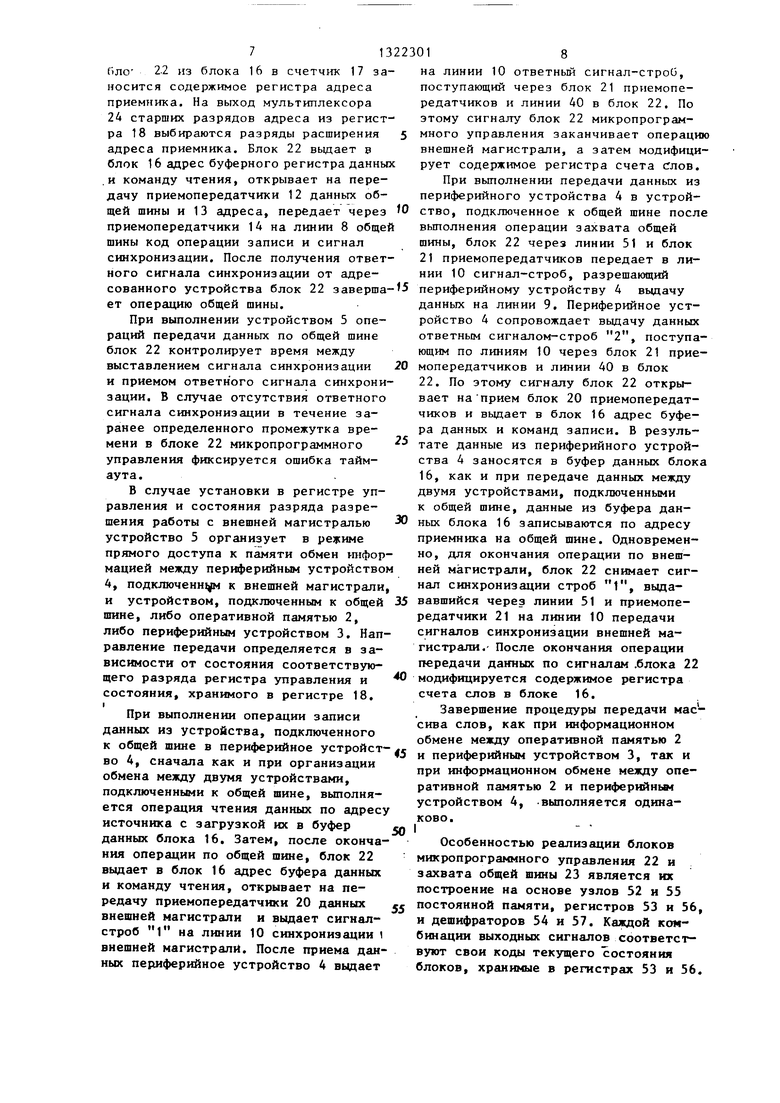

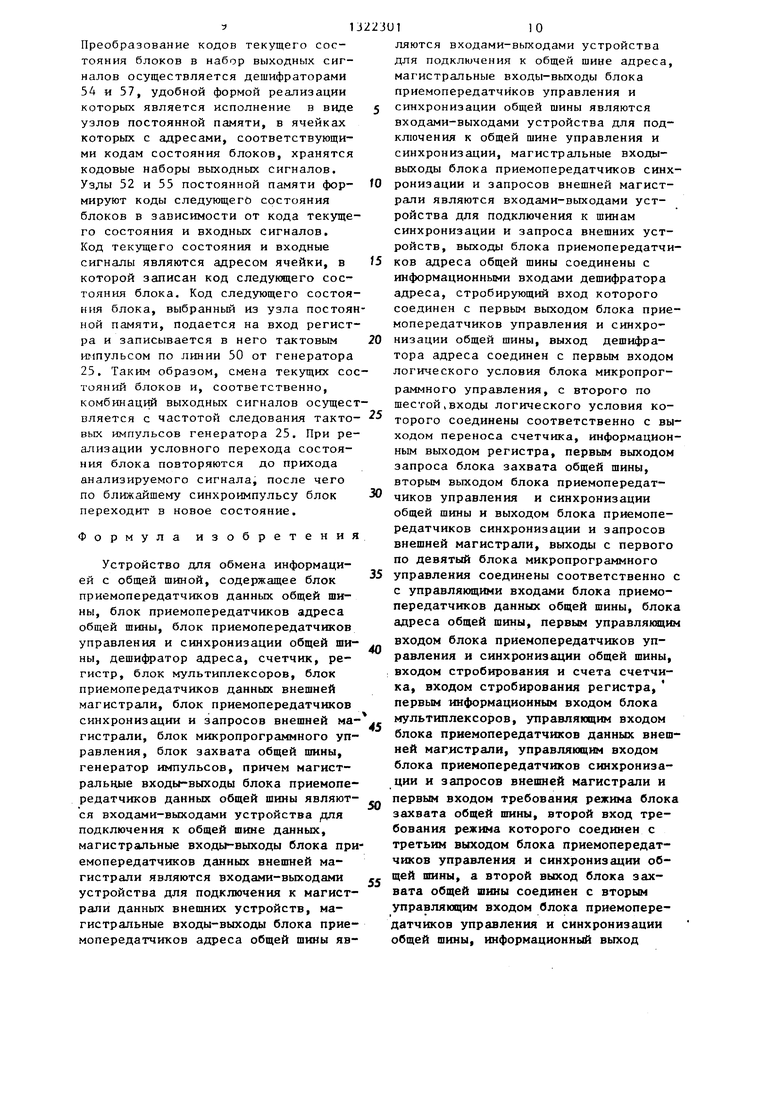

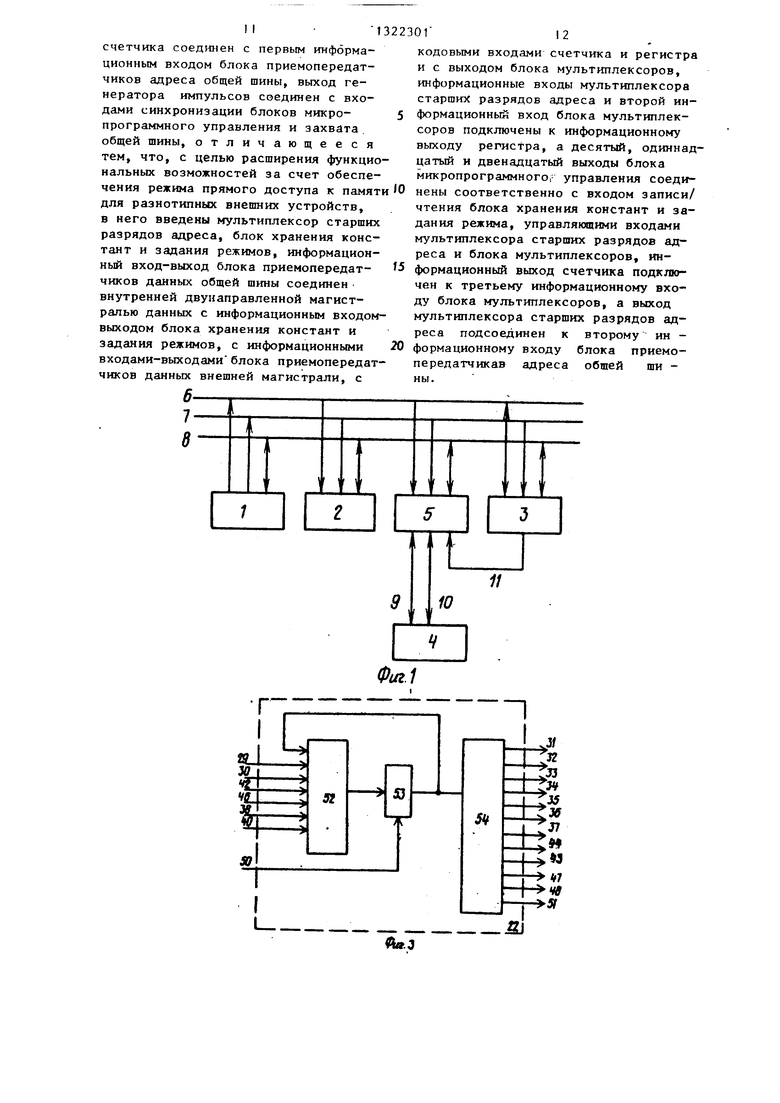

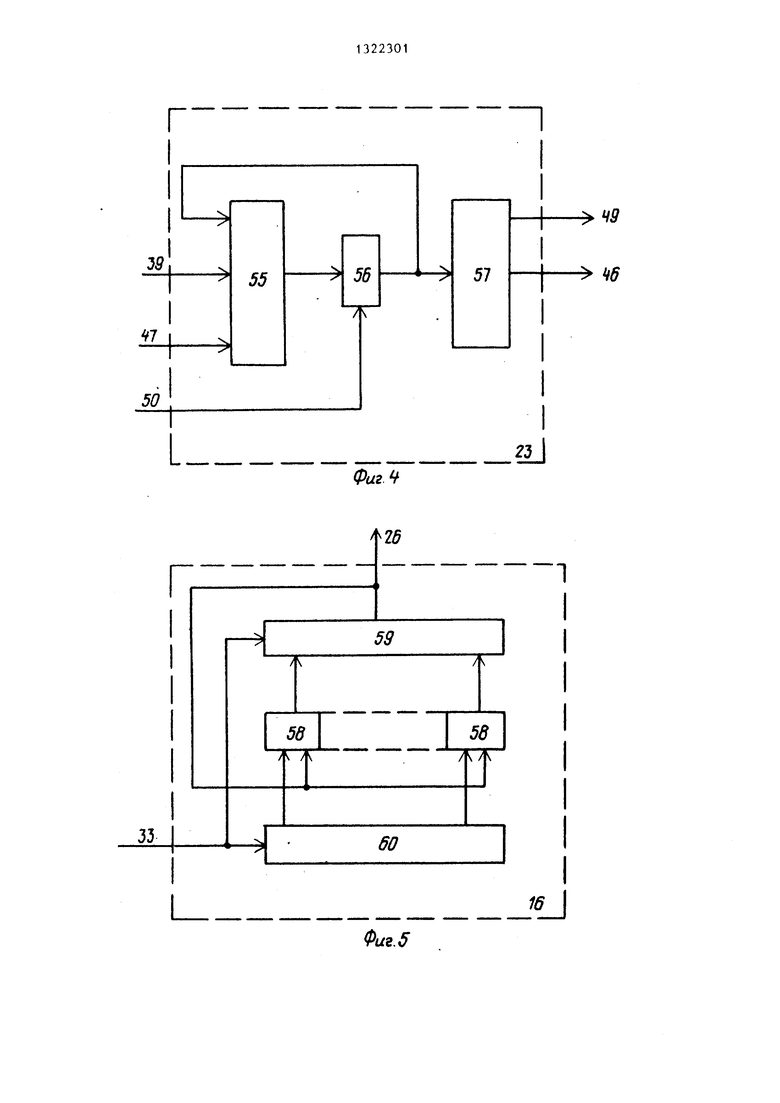

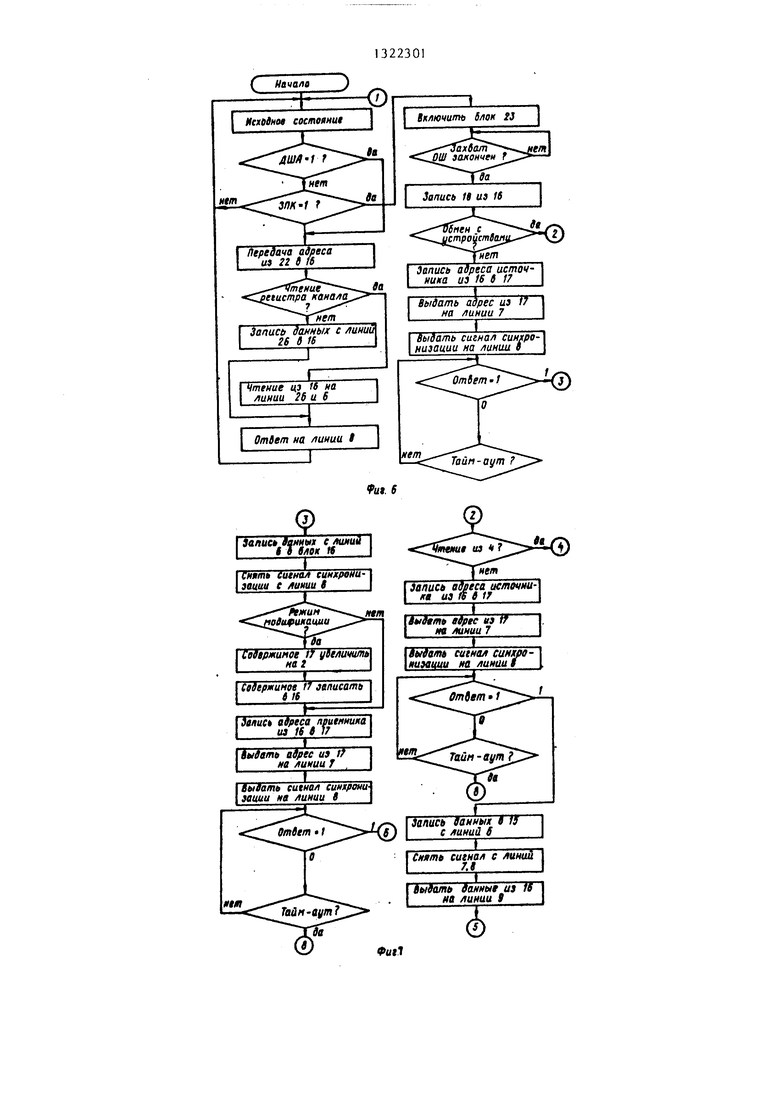

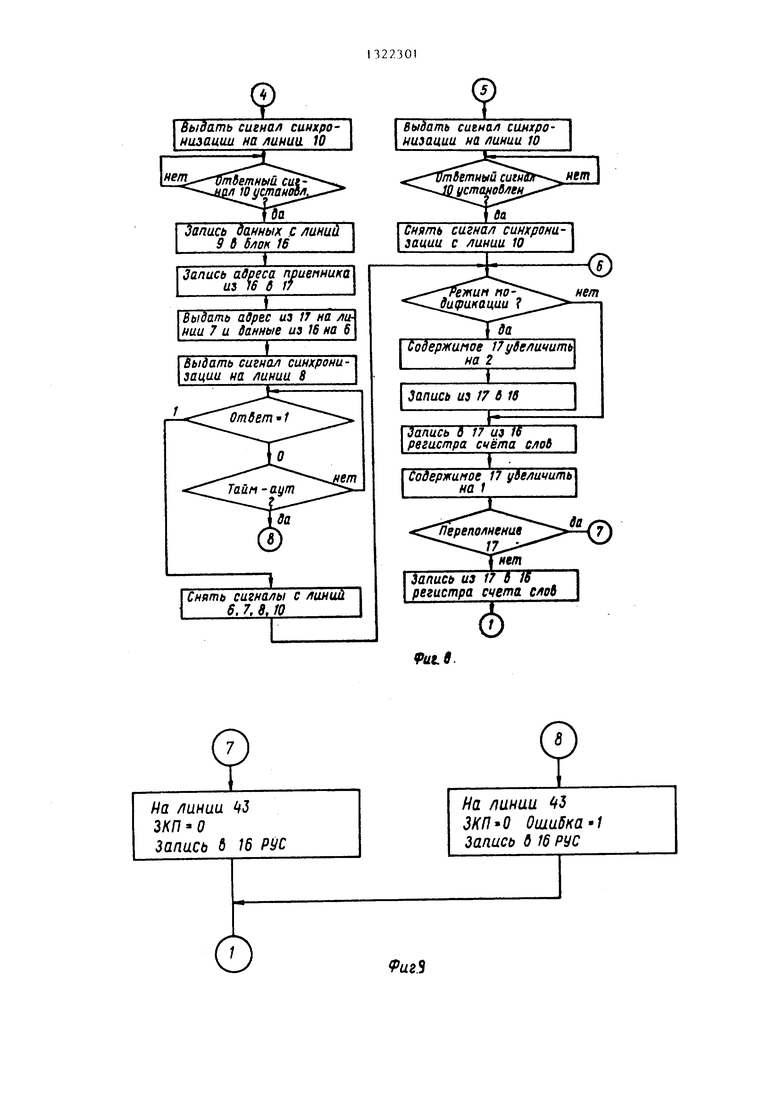

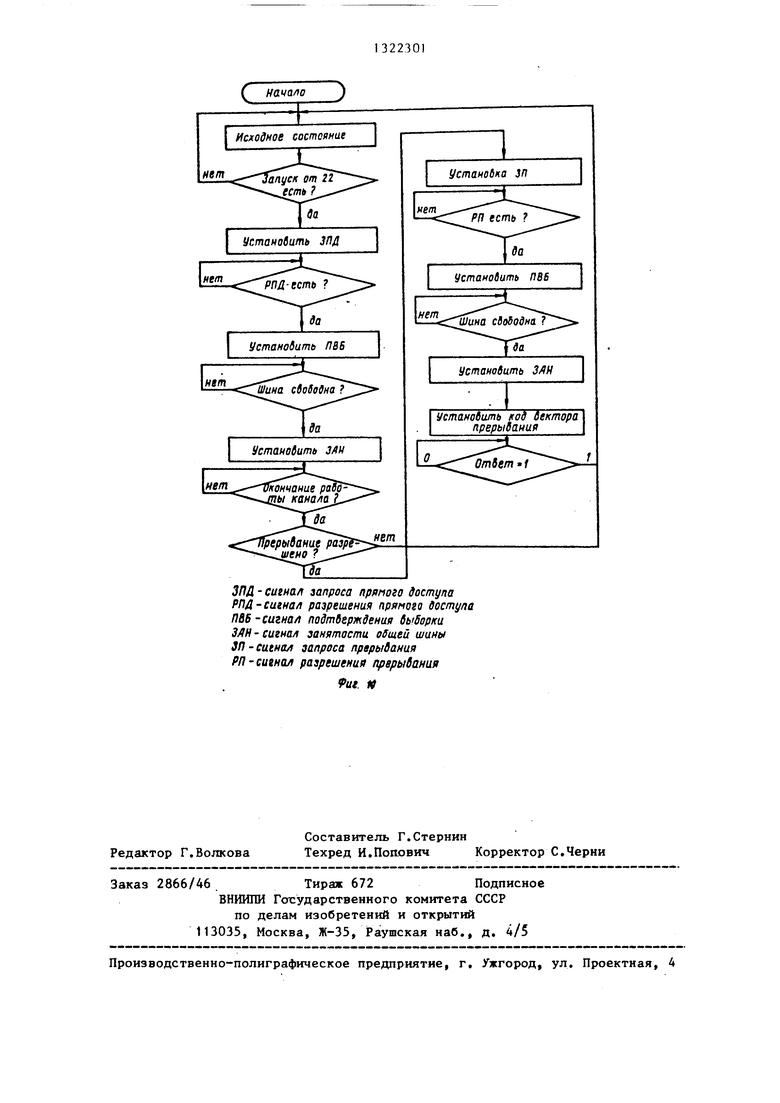

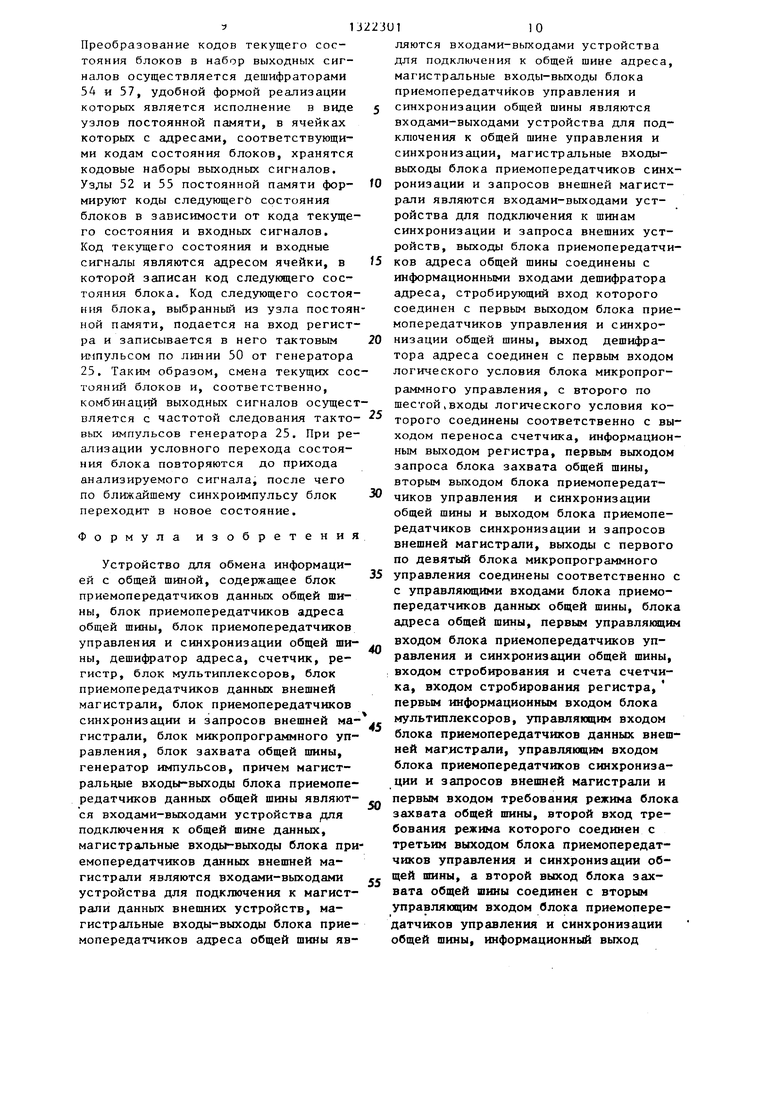

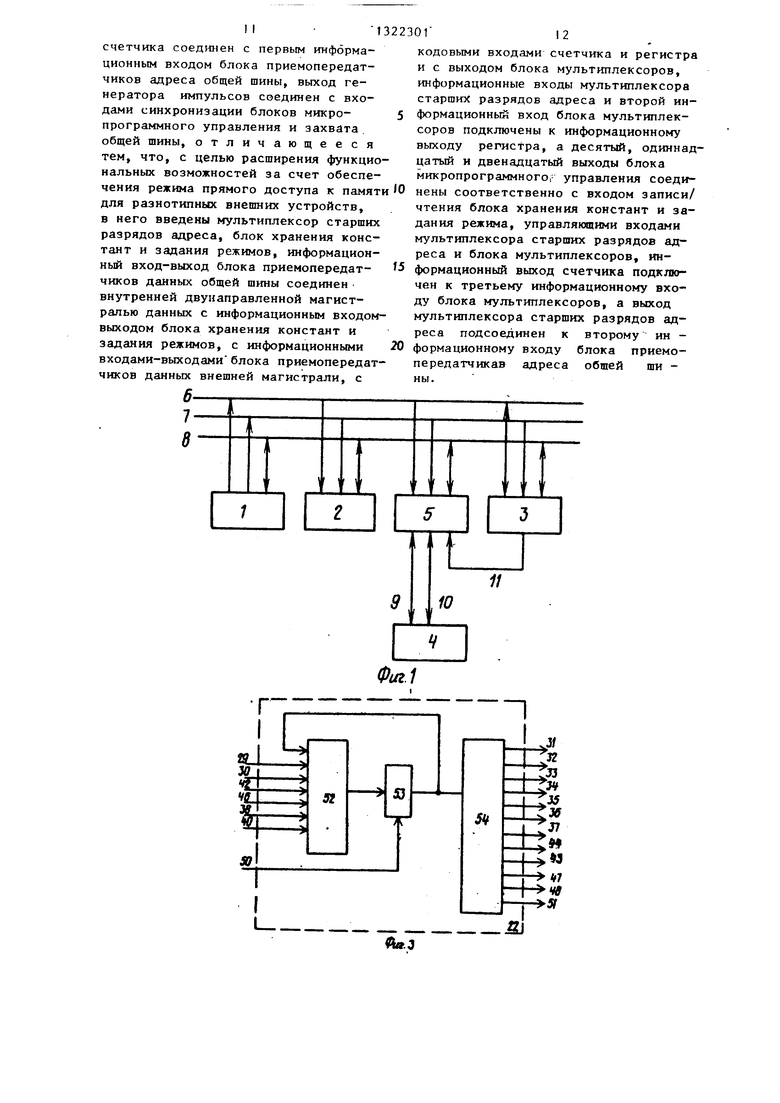

На фиг, 1 показана структура информационно-измерительной системы на основе ЦВМ с общей шиной с канало прямого дocтyпa на фиг. 2 - структурная схема устройства для обмена информацией с общей шинойjна фиг.З - функциональная схема блока микропрограммного управления; на фиг.4 - функциональная схема блока захвата общей шины; на фиг. 5 - функциональная схема блока хранения констант и задания режимовj на фиг. 6-9 - диаграмма алгоритма работы блока микропрограммного управления;на фиг.10 - диаграмма алгоритма работы блока захвата общей шины.

Устройство содержит центральный процессор 1, оперативную память 2,

общей гаины, дешифратор 15 адреса, блок 16 хранения констант и задания режима, счетчик 17, регистр 18, блок 19 мультиплексоров, блок 20 приемопередатчиков данных внешней магистрали, блок 21 приемопередатчиков синхронизации и запросов внешней магистрали, блок 22 микропрограммного управления, блок 23 захвата общей шины,мультиплексор 24 старших разрядов адреса, генератор 25 импульсов. 10 ил.

fO

f5

рс

0

0

периферийное устройство 3, подключенное к общей шине ЦВМ по программному каналу, периферийное устройство 4, подключенное к внешней магистрали, устройство 5 для обмена информацией с общей шиной, линию 6 передачи данных общей шины, линию 7 передачи адреса, линию 8 передачи сигналов управления и синхронизации, линию 9 передачи данных внешней магистрали, линию 10 передачи сигналов синхронизации, линию 11 запросов, блок 12 приемопередатчиков данных общей шины, блок 13 приемопередатчиков адреса общей шины, блок 14 приемопередатчиков управления и синхронизации общей шины, дешифратор 15 адреса, блок 16 хранения констант и задания режимов, счетчик 17, регистр 18, блок 19 мультиплексоров, блок 20 приемопередатчиков данных внешней магистрали, блок 21 приемопередатчиков синхронизации и запросов внешней магистрапи, блок 22 микропрограммного управления, блок 23 захвата обшей шины, мультиплексор 24 старших разрядов адреса, генератор 25 импульсов, внутреннюю двунаправленную магистраль 26 данных, линии 27 выхода приемопередатчиков адреса 13, выход 28 линии приемопередатчиков управления и синхронизации 14, линию 29 выхода дешифратора 15 адреса, линию 30 переноса счетчика 17, линию 31 управления приемопередатчиками данных общей шины 12, линии 32 управления приемопередатчиками 13 адреса, линии 33 адреса и управления блоком 16, линии 34 стробирования и счета счет-j

инка 17, линии 35 стробиропания регистра 18, линии 36 управления блоко 19 мультиплексоров, линии 37 управления приемопередатчиками данн1,1х внешней магистрали 2U, линию 38 ло- гического условия блока 22, линии 39 требования режима, линии 40 логического условия блока 22, информационный выхоп 41 счетчика 17. информационный выход 42 регистра 18,выход 43 блока 22, линии 44 управления мультиплексором старших разрядов адреса 24, выход 45 мультиплексора старших разрядов адреса 24, линии 46 и 47 связи блока 22 и блока 23, линии 48 связи блока 22 и приемопередатчиков 14, линии 49 связи блока 23 и приемопередатчиков |4, выход 50 генератора 25 импульсов, линии 51 связи блока 22 и приемопередатчиков

21,узел 52 постоянной памяти блока

22,регистр 53 блока 22, дешифратор 54 блока 22, узел 55 постоянной памяти блока 22, регистр 56 блока 23, дешифратор 57 блока 23, группу ре- гистров 58 блока 18, мультиплексор

59 блока 16, дешифратор 60 блока 16.

Устройство 5 обеспечивает два основных вида информационного обмена в режиме прямого доступа к памяти: между оперативной памятью 2 и пери- ферийньм устройством 4 и между оперативной памятью 2 и периферийным устройством 3.

Шина синхронизации и запросов внешней магистрали включает строб - от устройства 5 к периферийному устройству 4, строб - от периферийного устройства 4 к устройству 5, запрос

от периферийного устройства 4. I

Для выполнения операций передачи

данных в блоке 16 хранения констант и задания режимов имеются: регистр управления и состояния, регистр адреса источника, регистр адреса приемника, регистр счета слов. Все они хранятся;, в группе регистров 58.

В регистре управления и состояния имеются следующие разряды управления режимов обмена: разряды расширения адреса источника и приемника разрешение обмена по внешней магистрали, управление направлением передачи данных по внешней магистрали; разре- шение модификации адресов источника и приемника после выполнения передач одного слова, разрешение прерывания, установка режима синхронизации - ли

5 0

5

0

5

0

,

5

0

бо от периферн1 ного устройства, либо от устройства 5, запуск устройства 5. Кроме того, регистр управления и состояния содержит разряды состояния признаков режима.

Для запуска устройства 5 необходимо выполнить программную загрузку адресуемых регистров, причем последним должен загружаться регистр управления и состояния, в котором кроме необходимых разрядов режима устанавливается разряд запуска канала, переводящий устройство 5 в активное состояние.

Программное обращение к адресуемым регистрам устройства 5 выполняется следующим образом.

Для вьтолнения операции записи в адресуемый регистр процессор 1 выставляет адрес регистра, к которому выполняется обращение, данные, записываемые в регистр, - код операции записи и сигнал синхронизации. В исходном состоянии блоки приемопередатчиков 13 и 14 открыты на прием сигналов с линий общей шины. Адрес и сигнал синхронизации, принимаемые соответствующими блоком приемопередатчиков, по линиям 27 и 28 поступают на вход дешифратора 15 адреса. Код операции по линиям 38 передается в блок 23 микропрограммного управления 22. При совпадении принимаемого адреса с одним из адресов общей шины, присвоенных адресуемым регистрам устройства 5, дешифратор 15 адреса передает в блок 22 микропрограммного управления сигнал, запускающий в нем выполнение операции, и внутренний адрес регистра, к которому производится обращение. Блок 22 микропрограммного управления открывает приемопередатчики 12 данных общей шины на прием и данные с линий 6 передаются на внутреннюю двунаправленную магистраль 26 данных. В блок 16 хранения констант и задания режимов по линиям 33 блок 22 микропрограммного управления передает внутренний адрес соответствукмце- го адресуемого регистра и сигнал записи, по которым дешифратор 60 формирует нужный сигнал записи в соответствующий регистр 58. Затем блок 22 передает на линии 48 ответный сигнал синхронизации, который через блок 14 приемопередатчиков и линии 8 поступает в процессор 1. Приняв

этот сигнал процессор 1 заканчивает операцию по общей шине.

При выполнении операции чтения адресуемого регистра процессор 1 выставляет на линии 7 адрес, на линии 8 - код операции чтения и сигнал синхронизации. После срабатывания дешифратора 15 адреса и запуска блока 22 последний передает в блок 16 хранения констант и задания режимов внутренний адрес регистра и команду чтения и открывает блок 12 приемопередатчиков данных общей шины на передачу. Данные из блока 16 хранения констант и задания режимов через внутреннкио двунаправленную магистрал 26 данных и блок 12 приемопередатчиков передаются в линии 6 данных общей шины. Затем блок 22 микропрограммного управления выдает на линии 48 ответный сигнал .синхронизации, поступающий через блок 14 приемопередатчиков и линии 8 в процессор 1. По этому сигналу процессор 1 принимает данные с линий 6 и затем снимает сигнал с линий общей шины, заканчивая операцию. После запуска устройства 5 - программной загрузки адресуемых регистров, и установки разряда запуска канала в регистре управления и состояния, а также получения устройством 5 сигнала запроса от периферийного устройства 3 либо 4 в случае работы в режиме синхронизации от периферийного устройства блок 22 сигналом по линий 47 включает блок 23 для выполнения операции захвата общей шины. В случае установки в регистре управления и состояния разряда режима синхронизации от канала блок 22 включает блок 23 сразу после программной установки разряда запуска канала в регистре управления и состояния. Операция захвата общей шины выполняется по следующему алгоритму. Блок 23 выставляет на линии 49 и далее через блок 14 приемопередатчиков в линии 8 сигнал запроса прямого доступа. В ответ процессор 1 выставляет сигнал разрешения прямого доступа, который через блок приемопередатчиков и линии 39 поступает в блок 23. Блок 23 снимает запрос прямого доступа и выставляет сигнал подтверждения выбора, по которому процессор 1 снимает сигнал разрешения прямого доступа.

23016

Между двумя устройствами, подклю- чанными к общей шине, в режиме прямого доступа к памяти устройство 5 передает одно слово данных за два 5 цикла обмена данными по общей шине. В первом цикле устройство 5 выполняет чтение данных по адресу общей ши

5

0

5

5

0

5

0

5

ны, хранимому в регистре адреса источника, во втором - запись этих данных по адресу из регистра адреса приемника. Для временного хранения данных используется буферный регистр данных - один из регистров 58 блока 16.

Указанные операции выполняются следующим образом.

По сигналам блока 22 содержимое регистра управления и состояния и регистра адреса источника переписываются из блока 16 соответственно в регистр 18 и счетчик 17. Для зтого блок 22 по линиям 33 передает в блок 16 адрес выбранного регистра и команду чтения. Далее блок 22 выдает в регистр 18 или счетчик 17 сигнал записи. Данные из блока 16 в регистр 18 или счетчик 17 передаются по внутренней двунаправленной магистрали 26 Q данных. Затем на выход мультиплексора

24 старших разрядов адреса переда- ются разряды расширения адреса источника из регистра управления и состояния записанного в регистр 18. Блок 13 приемопередатчиков открывается на передачу и в общую шину на линии

7выдается адрес. Через линии 48 и блок 14 приемопередатчиков на линии

8общей шины блок 22 передает код операции чтения и затем сигнал синхронизации. После получения ответного сигнала синхронизации, поступающего через блок 14 приемопередатчиков и линии 38 в блок 22, свидетельствующего о выполнении операции адресуемым по общей шине устройством и наличии данных на линиях 6 блок 22 микропрограммного управления открывает блок

12 приемопередатчиков на прием, выдает адрес буферного регистра данных и команду записи в блок 16. В результате, данные с линий 6 через блок 12 приемопередатчиков и внутреннюю двунаправленную магистраль 26 данных заносятся в буферный регистр данных блока 16. Для завершения первого цикла блок 22 снимает с линий общей шины сигнал синхронизации, код операции и адрес. Далее по сигналам

5ло 2.2 из блока 16 в счетчик 17 заносится содержимое регистра адреса приемника. На выход мультиплексора 24 старших разрядов адреса из регистра 18 выбираются разряды расширения адреса приемника. Блок 22 выдает в блок 16 адрес буферного регистра данных .и команду чтения, открывает на передачу приемопередатчики 12 данных общей шины и 13 адреса, передает через приемопередатчики 14 на линии 8 общей шины код операции записи и сигнал синхронизации. После получения ответного сигнала синхронизации от адресованного устройства блок 22 завершает операцию общей шины.

При выполнении устройством 5 операций передачи данных по общей шине блок 22 контролирует время между выставлением сигнала синхронизации и приемом ответн ого сигнала синхронизации. В случае отсутствия ответного сигнала синхронизации в течение заранее определенного промежутка времени в блоке 22 микропрограммного управления фиксируется ошибка тайм- аута.

В случае установки в регистре управления и состояния разряда разрешения работы с внешней магистралью устройство 5 организует в режиме прямого доступа к памяти обмен т1фор- мацией между периферийным устройством 4, подключены к внешней магистрали, и устройством, подключенным к общей шине, либо оперативной памятью 2, либо периферийным устройством 3. Направление передачи определяется в зависимости от состояния соответствующего разряда регистра управления и состояния, хранимого в регистре 18.

При выполнении операции записи данных из устройства, подключенного к общей шине в периферийное устройст- во 4, сначала как и при организации обмена между двумя устройствами, подключенными к общей шине, выполняется операция чтения данных по адресу источника с загрузкой их в буфер данных блока 16. Затем, после окончания операции по общей шине, блок 22 выдает в блок 16 адрес буфера данных и команду чтения, открывает на передачу приемопередатчики 20 данных внешней магистрали и выдает сигнал- строб 1 на линии 10 синхронизации внешней магистрали. После приема данных периферийное устройство 4 выдает

на линии 10 ответный сигнал-строб, поступающий через блок 21 приемопередатчиков и линии 40 в блок 22. По этому сигналу блок 22 микропрограммного управления заканчивает операци внешней магистрали, а затем модифицирует содержимое регистра счета сглов.

При вьшолнении передачи данных из периферийного устройства 4 в устройство, подключенное к общей шине посл вьшолнения операции захвата общей шины, блок 22 через линии 51 и блок 21 приемопередатчиков передает в линии 10 сигнал-строб, разрешающий периферийному устройству 4 выдачу данных на линии 9, Периферийное устройство 4 сопровождает выдачу данных ответным сигналом-строб 2, поступающим по линиям 10 через блок 21 приемопередатчиков и линии 40 в блок 22. По этому сигналу блок 22 открывает на прием блок 20 приемопередатчиков и выдает в блок 16 адрес буфера данных и команд записи. В результате данные из периферийного устройства 4 заносятся в буфер данных блок 16, как и при передаче данных между двумя устройствами, подключенными к общей шине, данные из буфера данных блока 16 записываются по адресу приемника на общей шине. Одновременно, для окончания операции по внешней магистрали, блок 22 снимает сигнал синхронизации строб 1, выдававшийся через линии 51 и приемопередатчики 21 на линии 10 передачи сигналов синхронизации внешней магистрали.- После окончания операции передачи данных по сигналам .блока 22 модифицируется содержимое регистра счета слов в блоке 16.

Завершение процедуры передачи массива слов, как при информационном обмене между оперативной памятью 2 и периферийным устройством 3, так и при информационном обмене между оперативной памятью 2 и периферийньм устройством 4, -выполняется одинаково. I-

Особенностью реализации блоков микропрограммного управления 22 и захвата общей шины 23 является их построение на основе узлов 52 и 55 постоянной памяти, регистров 53 и 56 и дешифраторов 54 и 57. Каждой комбинации выходных сигналов соответствуют свои коды текущего состояния блоков, хранимые в регистрах 53 и 56

Преобразование кодов текущего состояния блоков в набор выходных сигналов осуществляется дешифраторами 54 и 57, удобной формой реализации которых является исполнение в виде узлов постоянной памяти, в ячейках которых с адресами, соответствующими кодам состояния блоков, хранятся кодовые наборы выходных сигналов. Узлы 52 и 55 постоянной памяти фор- мируют коды следующего состояния блоков в зависимости от кода текущего состояния и входных сигналов. Код текущего состояния и входные сигналы являются адресом ячейки, в которой записан код следующего состояния блока. Код следующего состояния блока, выбранный из узла постоянной памяти, подается на вход регистра и записывается в него тактовым игшульсом по линии 50 от генератора 25. Таким образом, смена текущих состояний блоков и, соответственно, комбинаций выходных сигналов осуществляется с частотой следования такто- вых импульсов генератора 25. При реализации условного перехода состояния блока повторяются до прихода анализируемого сигнала, после чего по ближайшему синхроимпульсу блок переходит в новое состояние.

Формула изобретения

Устройство для обмена информацией с общей шиной, содержащее блок приемопередатчиков данных общей шины, блок приемопередатчиков адреса общей шины, блок приемопередатчиков управления и синхронизации общей шины, дешифратор адреса, счетчик, регистр, блок мультиплексоров, блок приемопередатчиков данных внешней магистрали, блок приемопередатчиков

синхронизации и запросов внешней ма- .- мультиплексоров, управляющим входом

гистрали, блок микропрограммного управления, блок захвата общей шины, генератор импульсов, причем магистральные входы-выходы блока приемопередатчиков данных общей шины являются входами-выходами устройства рдя подключения к общей шине данных, магистральные входы-выходы блока при емопередатчиков данных внешней магистрали являются входами-выходами устройства для подключения к магистрали данных внешних устройств, магистральные входы-выходы блока приемопередатчиков адреса общей шины яв50

55

блока приемопередатчиков данных внеш ней магистрали, управляющим входом блока приемопередатчиков синхронизации и запросов внешней магистрали и первым входом требования режима блок захвата общей шины, второй вход требования режима которого соединен с третьим выходом блока приемопередатчиков управления и синхронизации общей шины, а второй выход блока захвата общей шины соединен с вторым управляющим входом блока приемопередатчиков управления и синхронизации общей шины, информационный выход

5 0 0

5

0

ляются входами-выходами устройства для подключения к общей шине адреса, магистральные входы-выходы блока приемопередатчиков управления и синхронизации общей шины являются входами-выходами устройства для подключения к общей шине управления и синхронизации, магистральные входы- вькоды блока приемопередатчиков синхронизации и запросов внешней магистрали являются входами-выходами устройства для подключения к шинам синхронизации и запроса внешних устройств, выходы блока приемопередатчиков адреса общей шины соединены с информационными входами дешифратора адреса, стробирующий вход которого соединен с первым выходом блока приемопередатчиков управления и синхронизации общей шины, выход дешифратора адреса соединен с первым входом логического условия блока микропрограммного управления, с второго по шестой,входы логического условия которого соединены соответственно с выходом переноса счетчика, информационным выходом регистра, первым выходом запроса блока захвата общей шины, вторым выходом блока приемопередатчиков управления и синхронизации общей шины и выходом блока приемопередатчиков синхронизации и запросов внешней магистрали, выходы с первого по девятый блока микропрограммного управления соединены соответственно с с управляющими входами блока приемопередатчиков данных общей шины, блока адреса общей шины, первым управлякяцим входом блока приемопередатчиков управления и синхронизации общей шины, входом стробирования и счета счетчика, входом стробирования регистра, первым информационным входом блока

0

5

блока приемопередатчиков данных внешней магистрали, управляющим входом блока приемопередатчиков синхронизации и запросов внешней магистрали и первым входом требования режима блока захвата общей шины, второй вход требования режима которого соединен с третьим выходом блока приемопередатчиков управления и синхронизации общей шины, а второй выход блока захвата общей шины соединен с вторым управляющим входом блока приемопередатчиков управления и синхронизации общей шины, информационный выход

II 1 счетчика соединен с первым информационным входом блока приемопередатчиков адреса общей шины, выход генератора импульсов соединен с входами синхронизации блоков микро- программного управления и захвата общей шины, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения режима прямого доступа к памят для разнотипных внешних устройств, в него введены мультиплексор старших разрядов адреса, блок хранения констант и задания режимов, информационный вход-выход блока приемопередатчиков данных общей шины соединен внутренней двунаправленной магистралью данных с информационным входом выходом блока хранения констант и задания режимов, с информационными

входами-выходами блока приемопередатчиков данных внешней магистрали, с

5J

.J

12

кодовыми входами счетчика и регистра и с выходом блока мультиплексоров, информационные входы мультиплексора старших разрядов адреса и второй информационный вход блока мультиплексоров подключены к информационному выходу регистра, а десятый, одиннадцатый и двенадцатый выходы блока микропрограммного,- управления соединены соответственно с входом записи/ чтения блока хранения констант и задания режима, управляющими входами мультиплексора старших разрядов адреса и блока мультиплексоров, информационный выход счетчика подключен к третьему информационному входу блока мультиплексоров, а выход мультиплексора старших разрядов адреса подсоединен к второму ин формациоиному входу блока приемопередатчиканы.

адреса обшей ши

/

58

33

«J

Фиг.

Фиг

59

/

5

/

60

нет

ва

Запись аореса источника из tS в 17

Выдать адрес из и на /IUHUU 7

Запись данных с линий 26 в 16

Выдать сигна/1 синхронизации на линии в

Запись ванных е линий I t влок №

снять сигнал еинхроми- заииа е линии t

fut. S

Запись аореса асточни- /га из tS в 17

Htm

Iettatmb еврее а t7 на линии 7

Сваврминое 17 ytti наг

вывать futfHu синял низании на линии

CioepmuHoe 17 зеписать 6 /6

Saauct авреса приенним из 16 в 17

I вывать аарес us 17 на линии Г

бывать сигнал сит заиии на линии 9

Снять сигнал с линий Л

бывать данные из 16 на линии I

9utt

Выдать сигнал синхро- низациш на /IUHUU. 10

Выдать сигнал синхронизации на линии Ю

- Т тбетный. саг Оустант/1

Оа

Запись данных с мний 9 б 6/IOK 16

снять сигна/г синхронизации с линии 10

±

Запись аОреса приепника из 16 в 17

1

Выдать адрес из /7 на /lu- нии 7 и данные из 16 на 6

да

I

Выдать сигна/1 синхронизации на /tUHUu 8

±

Снять сигналы с линий 6. 7, в. Ю

CooepfKUfioe 17убе/1ичить на 2

Запись из 17 б 1в

±

запись о 17 из 10 регистра счёта c/iob

Содержимое 17 у5е/1ичить на 1

Запись из 17 о 10 регистра счета с/юб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения процессора с периферийным устройством | 1984 |

|

SU1246102A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

Изобретение относится к вычислительной технике и может быть использовано при-построении высокоскоростных информационно-вычислительных систем на основе цифровой вычислительной машины (ЦВМ) с общей шиной, в которых для достижения необходимой пропускной способности информационных трактов связи с периферийными устройi (Л

На /IUHUU 3

ЗКП О

запись б 16 РУС

о

На линии 5 ЗКП О Ошибка 1 Запись б 16 РУС

аг.9

( начало 3

ЗПй - сигнал запроса пряного доступа РПД-сиена/1 разрешения прямого доступа ПВб -сигнал подтбертдения бь борки ЗЛН - сигнал занятости offiueu шины ЗП - cutHu/t запроса прврыОания РП-сигнал разрешений прерыбания

. it

Редактор Г.Волкова

Составитель Г.Стернин

Техред И.Попович Корректор С.Черни

Заказ 2866/46Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Патент США № 3821713,кл.340-172,5, опублик | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Авторское свидетельство СССР № 762592, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1984-09-06—Подача